# FAN5702 Configurable 180mA 6-LED Driver with I<sup>2</sup>C Control

## Features

- Six (6) Parallel LEDs (up to 30mA Each)

- Total Package Load Current Capability: 180mA

- Group from 2 to 6 LEDs for Flexible Backlighting

- I<sup>2</sup>C Interface for Easy Programming

- >600:1 Dimming Ratio for 100Hz PWM Frequency

- Logarithmically Controlled Dimming with 64 Steps

- Secondary Brightness Control Using PWM Dimming up to 20kHz in Conjunction with I<sup>2</sup>C Dimming

- Dynamic Backlight Control (DBC) to Reduce Current Consumption

- Up to 92% Efficiency

- Built-in 1.5x Charge Pump with Low Drop-Out Bypass Switch and automatic switching to 1x mode

- 1.2MHz Switching Frequency for Small-Sized Capacitors

- 16-Bump 1.6mm × 1.6mm WLCSP (0.6mm Height)

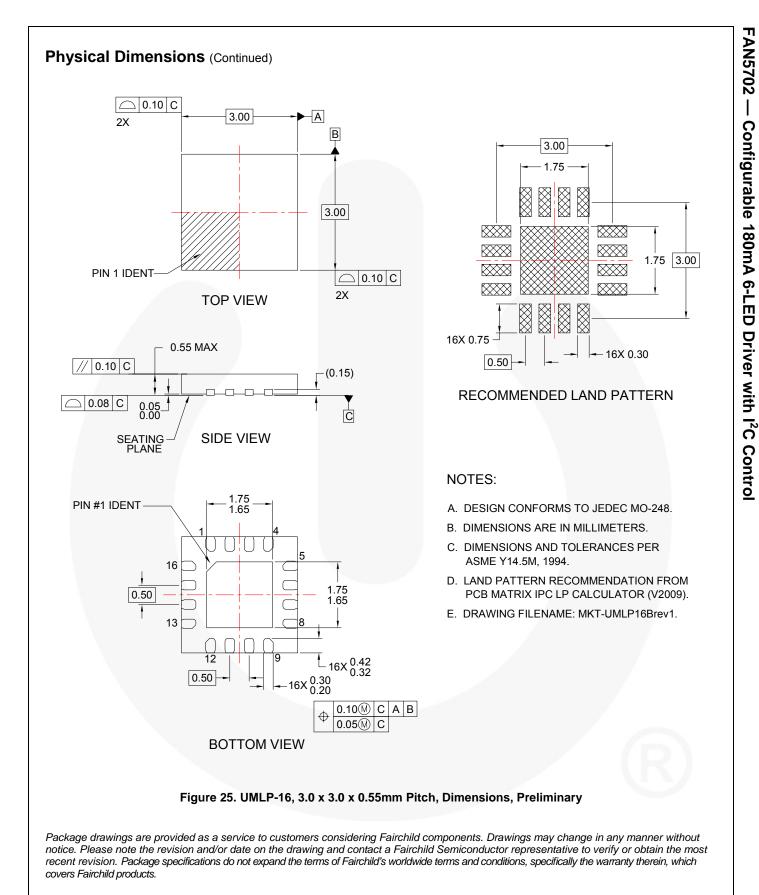

- 16-Lead 3.0mm x 3.0mm UMLP (0.55mm Height)

## Applications

- LCD Backlighting

- Mobile Handsets / Smartphones

- Portable Media Players

## Description

The FAN5702 is a highly integrated and configurable chargepump-based multi-LED driver. The device can drive up to six LEDs in parallel with a total output current of 180mA. Regulated internal current sinks deliver excellent current and brightness matching to all LEDs.

The FAN5702 has an I<sup>2</sup>C interface that allows the user to independently control the brightness with a default grouping of 2,1,1,1,1 for a maximum of five independent lighting channels. The LED driver can be programmed in a multitude of configurations to address broad lighting requirements for different platforms. Each LED can be configured through I<sup>2</sup>C as five independent channels (Group A has two LEDs by default) or any additional LEDs can join Group A to increase the backlighting needs as the display size increases. The device offers a second dimming control using the EN/PWM pin. Applying a PWM dimming signal to this pin allows control of the dimming of Group A LEDs so that the average current is the linear value multiplied by the PWM dimming duty-cycle.

The device provides excellent efficiency, without an inductor, by operating the charge pump in 1.5x or pass-through mode.

The FAN5702 can be ordered with default  $I_{SET}$  values of 30mA, 20mA, 15mA, or 8mA. The default  $I_{SET}$  is always determined by the  $I_{SET}$  ordered (see Ordering Information).

| Part Number   | LED Current         | Temperature | Package                     | Packing       |

|---------------|---------------------|-------------|-----------------------------|---------------|

| Fait Nulliber | (I <sub>SET</sub> ) | Range       | Fackage                     | Facking       |

| FAN5702UC30X  | 30mA                | -40 to 85°C | WLCSP-16, 0.4mm Pitch       | Tape and Reel |

| FAN5702UC20X  | 20mA                | -40 to 85°C | WLCSP-16, 0.4mm Pitch       | Tape and Reel |

| FAN5702UC15X  | 15mA                | -40 to 85°C | WLCSP-16, 0.4mm Pitch       | Tape and Reel |

| FAN5702UC08X  | 8mA                 | -40 to 85°C | WLCSP-16, 0.4mm Pitch       | Tape and Reel |

| FAN5702UMP30X | 30mA                | -40 to 85°C | UMLP-16, 3.0 x 3.0 x 0.55mm | Tape and Reel |

| FAN5702UMP20X | 20mA                | -40 to 85°C | UMLP-16, 3.0 x 3.0 x 0.55mm | Tape and Reel |

| FAN5702UMP15X | 15mA                | -40 to 85°C | UMLP-16, 3.0 x 3.0 x 0.55mm | Tape and Reel |

| FAN5702UMP08X | 8mA                 | -40 to 85°C | UMLP-16, 3.0 x 3.0 x 0.55mm | Tape and Reel |

#### **Ordering Information**

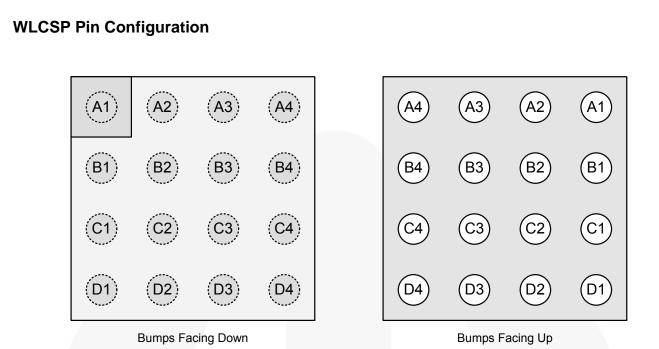

Figure 2. WLCSP-16, 0.4mm Pitch, 1.61 x 1.61mm

## **Pin Definitions**

| Pin #                   | Name                       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D2                      | VIN                        | Input Supply Voltage. Connect to 2.7 – 5.5V <sub>DC</sub> input power source.                                                                                                                                                                                                                                                                                                                                                                   |

| B4                      | GND                        | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| D1                      | VOUT                       | Charge Pump Output Voltage. Connect to LED anodes.                                                                                                                                                                                                                                                                                                                                                                                              |

| D3 ,D4                  | C1+, C1–                   | Charge pump flying capacitor #1                                                                                                                                                                                                                                                                                                                                                                                                                 |

| C3, C4                  | C2+, C2–                   | Charge pump flying capacitor #2                                                                                                                                                                                                                                                                                                                                                                                                                 |

| A1,A2<br>B1,B2<br>C1,C2 | D2A, D1A<br>D4,D3<br>D6,D5 | LED Outputs                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| A4                      | EN / PWM                   | <b>Enable / PWM</b> dimming input. By default, this pin acts as a simple enable / disable function.<br>When this pin is HIGH, normal operation is enabled. When LOW, the IC is reset and all functions (including $I^2C$ communications) are disabled. By setting General Purpose register bit 7 = 1, the pin functions as a PWM dimming input for Group A. To restore the Enable function, the General Purpose register bit 7 must be set LOW. |

| B3                      | SDA                        | I <sup>2</sup> C interface serial data                                                                                                                                                                                                                                                                                                                                                                                                          |

| A3                      | SCL                        | I <sup>2</sup> C interface serial clock                                                                                                                                                                                                                                                                                                                                                                                                         |

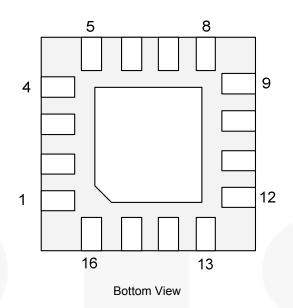

# **UMLP Pin Configuration**

## **Pin Definitions**

| Pin #                    | Name                       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11                       | VIN                        | Input Supply Voltage. Connect to 2.7 – 5.5V <sub>DC</sub> input power source.                                                                                                                                                                                                                                                                                                                                                                   |

| 6                        | GND                        | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 12                       | VOUT                       | Charge Pump Output Voltage. Connect to LED anodes.                                                                                                                                                                                                                                                                                                                                                                                              |

| 10,9                     | C1+, C1–                   | Charge pump flying capacitor #1                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 8,7                      | C2+, C2–                   | Charge pump flying capacitor #2                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1, 2<br>15, 16<br>13, 14 | D2A, D1A<br>D4,D3<br>D6,D5 | LED Outputs                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 4                        | EN / PWM                   | <b>Enable / PWM</b> dimming input. By default, this pin acts as a simple enable / disable function.<br>When this pin is HIGH, normal operation is enabled. When LOW, the IC is reset and all functions (including $I^2C$ communications) are disabled. By setting General Purpose register bit 7 = 1, the pin functions as a PWM dimming input for Group A. To restore the Enable function, the General Purpose register bit 7 must be set LOW. |

| 5                        | SDA                        | I <sup>2</sup> C interface serial data                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3                        | SCL                        | I <sup>2</sup> C interface serial clock                                                                                                                                                                                                                                                                                                                                                                                                         |

# **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol           |                                           | Para      | ameter                          | Min. | Max.                  | Units |  |

|------------------|-------------------------------------------|-----------|---------------------------------|------|-----------------------|-------|--|

| M                | VIN, VOUT Pins                            | -0.3      | 6.0                             | V    |                       |       |  |

| VCC              | V <sub>CC</sub> Other Pins <sup>(1)</sup> |           |                                 | -0.3 | V <sub>IN</sub> + 0.3 | V     |  |

| ESD              | Electrostatic Discharge                   | Humar     | n Body Model per JESD22-A114    |      | 3                     |       |  |

| ESD              | Protection Level                          | Charge    | ed Device Model per JESD22-C101 |      | 2                     |       |  |

| TJ               | Junction Temperature                      |           |                                 | -40  | +150                  | °C    |  |

| T <sub>STG</sub> | Storage Temperature                       |           |                                 | -65  | +150                  | °C    |  |

| TL               | Lead Soldering Temperatur                 | e, 10 Sec | conds                           |      | +260                  | °C    |  |

Note:

1. Lesser of  $V_{IN}$  + 0.3 or 6.0V.

## **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to absolute maximum ratings.

| Symbol           | Parameter            |     | Max. | Units |

|------------------|----------------------|-----|------|-------|

| V <sub>IN</sub>  | Supply Voltage       | 2.7 | 5.5  | V     |

| V <sub>LED</sub> | LED Forward Voltage  | 2   | 4    | V     |

| T <sub>A</sub>   | Ambient Temperature  | -40 | +85  | °C    |

| TJ               | Junction Temperature | -40 | +125 | °C    |

## **Thermal Properties**

| Symbol          | Parameter                              |       | Min. | Тур. | Max. | Units |

|-----------------|----------------------------------------|-------|------|------|------|-------|

| 0               | Junction to Ambient Thermal Desistance | WLCSP |      | 80   |      | °C/W  |

| Θ <sub>JA</sub> | Junction-to-Ambient Thermal Resistance | UMLP  |      | 49   |      | C/W   |

Note:

Junction-to-ambient thermal resistance is a function of application and board layout. This data is measured with four-layer 2s2p boards in accordance to JESD51-7 JEDEC standard. Special attention must be paid not to exceed junction temperature T<sub>J(max)</sub> at a given ambient temperate T<sub>A</sub>.

## **Electrical Specifications**

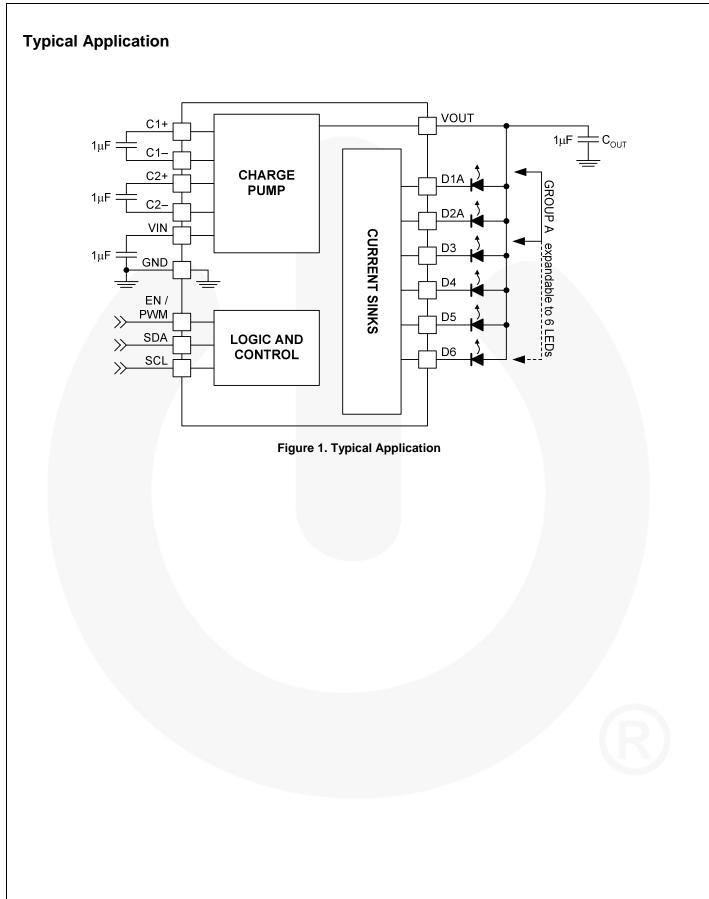

| Unless otherwise specified: V <sub>IN</sub> = 2.7V to 5.5V; T <sub>A</sub> = -40°C to +85°C; and ENA, EN3, EN4, EN5, and EN6 = 1. Typical values are        |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| V <sub>IN</sub> = 3.6V, T <sub>A</sub> = 25°C, I <sub>LED</sub> = 20mA, and LED cathode terminals = 0.4V. Circuit and components are according to Figure 1. |  |

| Symbol                                  | Parameter                               | Conditions                                                          | Min. | Тур.             | Max.   | Units |

|-----------------------------------------|-----------------------------------------|---------------------------------------------------------------------|------|------------------|--------|-------|

| Power Sup                               | plies and Thermal Protection            |                                                                     |      |                  |        |       |

| 1                                       | Outres and Outres to Outres at          | 1.5x Mode, No LEDs                                                  |      | 4.4              |        | mA    |

| I <sub>Q</sub> Quiescent Supply Current |                                         | 1x Mode, No LEDs                                                    |      | 0.3              |        | mA    |

| I <sub>SD</sub>                         | Shutdown Supply Current                 | $EN = 0$ , $V_{IN} = 4.5V$ , $T_A = -40^{\circ}C$ to $+85^{\circ}C$ |      | 0.1              | 2.0    | μA    |

|                                         |                                         | V <sub>IN</sub> Rising                                              |      | 2.55             | 2.70   | V     |

| V <sub>UVLO</sub>                       | Threshold                               | V <sub>IN</sub> Falling                                             | 2.20 | 2.40             |        | V     |

| VUVHYST                                 | Under-Voltage Lockout<br>Hysteresis     |                                                                     |      | 150              |        | mV    |

| T <sub>LIMIT</sub>                      | Thermal Shutdown                        |                                                                     |      | 150              |        | °C    |

| T <sub>HYST</sub>                       | Thermal Shutdown Hysteresis             |                                                                     |      | 20               |        | °C    |

| LED Curren                              | nt Sinks                                |                                                                     |      |                  |        |       |

| I <sub>LED</sub>                        | Absolute Current Accuracy               | V <sub>CATHODE</sub> =0.4V; see options for I <sub>SET</sub>        | -10% | I <sub>SET</sub> | +10%   | mA    |

| I <sub>LED(MAX)</sub>                   | Maximum Diode Current <sup>(3)</sup>    | I <sub>LED</sub> = I <sub>SET</sub>                                 |      | 30               |        | mA    |

| ILED_MATCH                              | LED Current Matching <sup>(4)</sup>     | $V_{CATHODE} = 0.4V, I_{LED} = I_{SET}$                             |      | 0.4              | 3.0    | %     |

| V <sub>DTH</sub>                        | 1x to 1.5x Gain Transition<br>Threshold | LED Cathode Voltage Falling                                         |      | 100              |        | mV    |

| V <sub>HR</sub>                         | Current Sink Headroom <sup>(5)</sup>    | I <sub>LED</sub> = 90% I <sub>LED(NOMINAL)</sub>                    |      | 65               |        | mV    |

| PWM Dimm                                | ing                                     |                                                                     |      | •                |        |       |

| <b>f</b> <sub>PWM</sub>                 | PWM Switching Frequency                 | t <sub>ON_LED(MINIMUM)</sub> = 15µs                                 |      |                  | 20     | kHz   |

| D <sub>PWM</sub>                        | PWM Duty-Cycle                          | f <sub>PWM</sub> = 100Hz                                            | 0.15 |                  | 100.00 | %     |

| Charge Pur                              | np                                      |                                                                     |      |                  |        |       |

| R <sub>out</sub>                        | Output Registeres                       | 1.5x Mode                                                           |      | 2.4              |        | Ω     |

| ROUT                                    | Output Resistance                       | 1x Mode                                                             |      | 0.9              |        | Ω     |

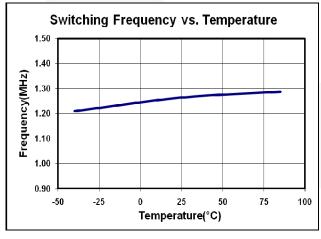

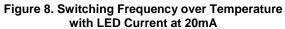

| f <sub>s₩</sub>                         | Switching Frequency                     |                                                                     | 0.9  | 1.2              | 1.5    | MHz   |

| t <sub>START</sub>                      | Startup Time                            | $V_{OUT}$ = 90% of $V_{IN}$                                         |      | 250              |        | μS    |

| Logic Input                             | s (EN, SDA, SCL)                        |                                                                     |      |                  |        |       |

| V <sub>IH</sub>                         | HIGH-Level Input Voltage                |                                                                     | 1.2  |                  |        | V     |

| V <sub>IL</sub>                         | LOW-Level Input Voltage                 |                                                                     |      |                  | 0.4    | V     |

| VIMAX                                   | Maximum Input Voltage                   |                                                                     |      | 1.8              | 5.5    | V     |

| I <sub>IN</sub>                         | Input Bias Current                      | Input Tied to GND or V <sub>IN</sub>                                |      | 0.01             | 1.00   | μA    |

|                                         |                                         |                                                                     |      |                  |        |       |

Notes:

The maximum total output current for the IC should be limited to 180mA. The total output current can be split between the two groups (IDxA = IDxB = 30mA maximum). Under maximum output current conditions, special attention must be given to input voltage and LED forward voltage to ensure proper current regulation. See the Maximum Output Current section of the datasheet for more information.

4. For the two groups of current sinks on a part (group A and group B), the following are determined: the maximum sink current in the group (MAX), the minimum sink current in the group (MIN), and the average sink current of the group (AVG). For each group, two matching numbers are calculated: (MAX-AVG)/AVG and (AVG-MIN)/AVG. The largest number of the two (worst case) is considered the matching value for the group. The matching value for a given part is considered to be the highest matching value of the two groups. The typical specification provided is the most likely norm of the matching value for all parts.

For each Dxx pin, headroom voltage is the voltage across the internal current sink connected to that pin. V<sub>HRx</sub> = V<sub>OUT</sub> - V<sub>LED</sub>. If headroom voltage requirement is not met, LED current regulation is compromised.

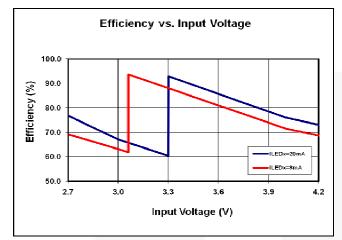

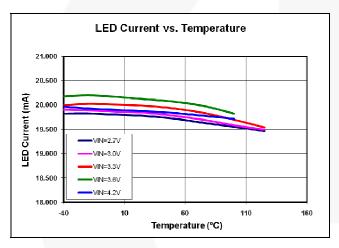

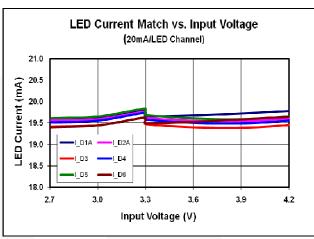

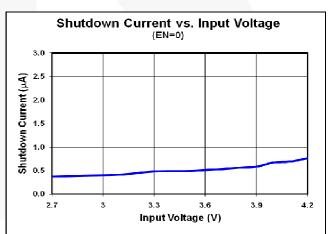

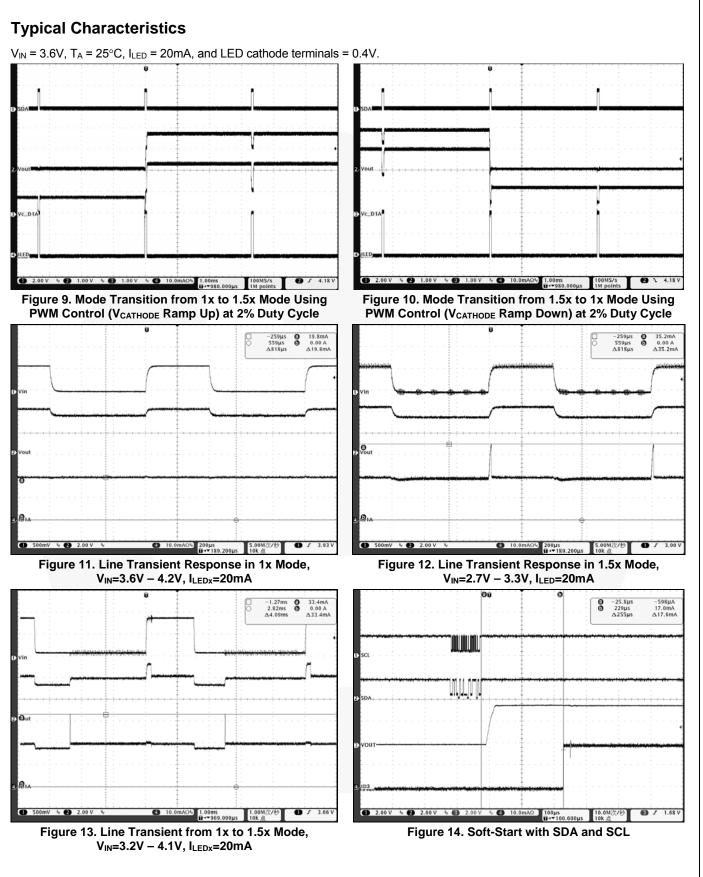

# **Typical Characteristics**

$V_{IN}$  = 3.6V,  $T_A$  = 25°C,  $I_{LED}$  = 20mA, and LED cathode terminals = 0.4V.

Figure 4. Efficiency with LED Current of 8mA and 20mA

Figure 6. LED Current Variation vs. Temperature

Figure 5. LED Current Match for all 6 LED Channels at I<sub>LED</sub>=20mA.

Figure 7. Shutdown Current vs. Input Voltage

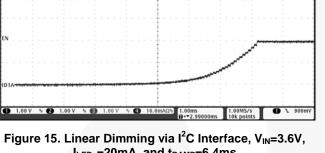

**Typical Characteristics**

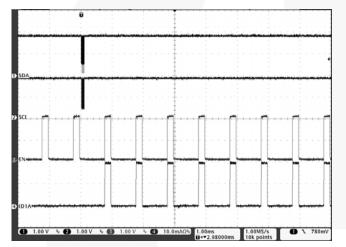

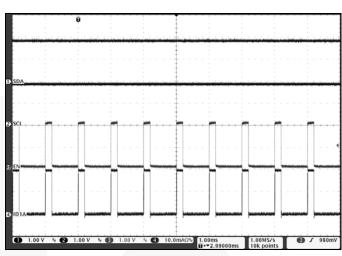

Figure 16. PWM Dimming,  $V_{IN}$ =3.6V,  $I_{LEDx}$ =20mA, and EN=1kHz with 20% Duty Cycle

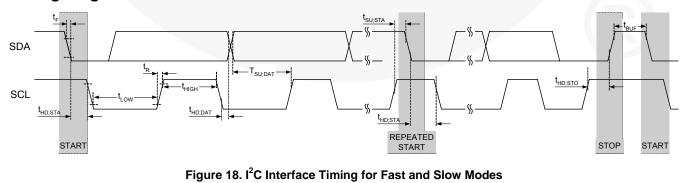

# I<sup>2</sup>C Timing Specifications

Guaranteed by design.

| Symbol              | Parameter                                        | Conditions    | Min.                 | Тур.            | Max.   | Units |  |

|---------------------|--------------------------------------------------|---------------|----------------------|-----------------|--------|-------|--|

| 4                   |                                                  | Standard Mode |                      |                 | 100    |       |  |

| f <sub>SCL</sub>    | SCL Clock Frequency                              | Fast Mode     |                      | 400             |        | kHz   |  |

| +                   | Bus-Free Time between STOP and START Conditions  | Standard mode |                      | 4.7             |        |       |  |

| t <sub>BUF</sub>    | Bus-Free fille between STOF and START Conditions | Fast Mode     | 1.3                  |                 |        | μS    |  |

| +                   | START or Repeated START Hold Time                | Standard Mode |                      | 4               |        | μS    |  |

| t <sub>hd;sta</sub> | START OF Repeated START Hold Hille               | Fast Mode     |                      | 600             |        | ns    |  |

| 4                   | SCL LOW Period                                   | Standard Mode |                      | 4.7             |        | μS    |  |

| t <sub>LOW</sub>    |                                                  | Fast Mode     |                      | 1.3             |        | ns    |  |

| +                   |                                                  | Standard Mode |                      | 4               |        | μs    |  |

| t <sub>HIGH</sub>   | SCL HIGH Period                                  |               | 600                  |                 | ns     |       |  |

| 4                   | Demosted CTADT Cature Time                       | Standard Mode |                      | 4.7             |        | μS    |  |

| t <sub>su;sta</sub> | Repeated START Setup Time                        | Fast Mode     |                      | 600.0           |        | ns    |  |

|                     | Data Catura Tima                                 | Standard Mode |                      | 250             |        | ns    |  |

| tsu;dat             | Data Setup Time                                  | Fast Mode     |                      | 100             |        | ns    |  |

|                     | Data Hald Time                                   | Standard Mode | 0                    |                 | 3.45   | μS    |  |

| thd;dat             | Data Hold Time                                   | Fast Mode     | 0                    |                 | 900.00 | ns    |  |

|                     | SCL Rise Time                                    | Standard Mode | 20+0.1C <sub>B</sub> |                 | 1000   | ns    |  |

| t <sub>RCL</sub>    | SCL RISE TIME                                    | Fast Mode     | 20+0.1C <sub>B</sub> |                 | 300    | ns    |  |

| tra                 | SCL Fall Time                                    | Standard Mode | 20+0.1C <sub>B</sub> |                 | 300    | ns    |  |

| t <sub>FCL</sub>    |                                                  | Fast Mode     | 20+0.1C <sub>B</sub> |                 | 300    | ns    |  |

|                     | SDA Rise Time <sup>(6)</sup>                     | Standard Mode | 20+0.1C <sub>B</sub> |                 | 1000   | ns    |  |

| t <sub>RDA</sub>    | SDA RISE TIME                                    | Fast Mode     | 20+0.                | 1C <sub>B</sub> | 300    | ns    |  |

|                     |                                                  | Standard Mode | 20+0.                | 1C <sub>B</sub> | 300    | ns    |  |

| t <sub>FDA</sub>    | SDA Fall Time                                    | Fast Mode     | 20+0.1C <sub>B</sub> |                 | 300    | ns    |  |

|                     | Stan Condition Satur Time                        | Standard Mode |                      | 4               |        | μS    |  |

| t <sub>su;sto</sub> | Stop Condition Setup Time                        | Fast Mode     |                      | 600             |        | ns    |  |

| CB                  | Capacitive Load for SDA and SCL                  |               |                      |                 | 400    | pF    |  |

6. Rise time of SCL after a repeated START condition and after an ACK bit.

# **Timing Diagram**

## **Circuit Description**

The FAN5702 is a white LED driver system based on an adaptive 1.5x charge pump capable of supplying up to 180mA of total output current. The tightly matched current sinks ensure uniform brightness between the LEDs. Each LED has a common anode configuration with its peak drive current set during manufacturing (see Ordering Information and I<sub>SET</sub>). An I<sup>2</sup>C-compatible interface is used to vary the brightness within the individual current sinks as well as configure the grouping. Each LED is controlled with 64 exponentially spaced analog brightness control levels through I<sup>2</sup>C, as indicated in Table 1. For maximum flexibility, the FAN5702 can be programmed with five independently controlled LED banks; by default, arranged as 2,1,1,1,1 (first two LEDs represent Group A). Through I<sup>2</sup>C, the device can be reconfigured to add up to six LEDs to Group A as needed by application requirements.

#### **Charge Pump**

The charge pump operates in either 1x mode, where V<sub>OUT</sub> is connected to V<sub>IN</sub> through a bypass switch, or in 1.5x mode. The circuit operates in 1x mode until the LED with the highest forward voltage (V<sub>LED(MAX)</sub>) can no longer maintain current regulation. At that point, 1.5x mode begins. If the lowest active cathode voltage is greater than 1.8V, the charge pump switches back to 1x mode.

## **IC Enable**

By default the General Purpose register bit 7 = 0, the EN pin functions as enable/disable. When the EN pin is LOW, all circuit functions, including  $l^2C$ , are disabled and the registers are set to their default values.

When the EN pin HIGH,  $I^2C$  interface is enabled. The LEDs can be turned on/off by writing to the General Purpose register. The user can always communicate via  $I^2C$  with the device to change register settings regardless of whether any LED is on or off.

#### **PWM Dimming**

By programming the General Purpose register bit 7 = 1, the EN pin is reappropriated to a PWM dimming input. Applying a PWM signal to this pin controls the LED current waveform to be ON when the PWM dimming pin is HIGH and OFF when the PWM dimming pin is LOW. By using this pin in conjunction with the  $1^{2}$ C register dimming, the part can achieve higher dimming resolution. For instance, an 8-bit PWM dimming signal applied along with the 6-bit register dimming yields better than 14 bits of resolution

To change the PWM dimming pin back to the EN function, set the General Purpose register bit 7 to 0.

#### **Register Controlled Brightness**

The DC value of the LED current is modulated according to the values in Table 1. Current is expressed as a percentage of the full scale current and is illustrated with a 20mA  $I_{SET}$ .

#### Table 1. Brightness Control

| Dimming Code (Bx5-Bx0) | Current Level    | $I_{m} = (m \Lambda) (I_{m} = 20 m \Lambda)$            |

|------------------------|------------------|---------------------------------------------------------|

| 000000                 | 0.125%           | I <sub>LED</sub> (mA) (I <sub>SET</sub> =20mA)<br>0.025 |

| 000000                 | 0.125 %          | 0.025                                                   |

| 000010                 | 0.249%           | 0.050                                                   |

|                        | 0.249%           |                                                         |

| 000011                 | 0.374%           | 0.063                                                   |

| 000100                 |                  | 0.075                                                   |

| 000101                 | 0.438%           | 0.088                                                   |

| 000110                 | 0.499%           | 0.100                                                   |

| 000111                 | 0.560%           | 0.113                                                   |

| 001000                 | 0.622%           | 0.125                                                   |

| 001001                 | 0.692%           | 0.138                                                   |

| 001010                 | 0.750%           | 0.150                                                   |

| 001011 001100          | 0.810%           | 0.163<br>0.175                                          |

|                        | 0.875%<br>0.938% | 0.175                                                   |

| 001101<br>001110       | 1.004%           | 0.100                                                   |

|                        |                  |                                                         |

| 001111<br>010000       | 1.124%<br>1.250% | 0.225                                                   |

|                        | 1.375%           | 0.250                                                   |

| 010001                 |                  |                                                         |

| 010010                 | 1.499%<br>1.625% | 0.300                                                   |

| 010011                 |                  | 0.325                                                   |

| 010100                 | 1.750%           | 0.350                                                   |

| 010101                 | 1.881%           | 0.375                                                   |

| 010110                 | 2.063%           | 0.413                                                   |

| 010111                 | 2.249%           | 0.450                                                   |

| 011000                 | 2.438%           | 0.488                                                   |

| 011001                 | 2.687%           | 0.538                                                   |

| 011010                 | 2.939%           | 0.588                                                   |

| 011011                 | 3.186%           | 0.638                                                   |

| 011100                 | 3.562%           | 0.713                                                   |

| 011101                 | 3.936%           | 0.788                                                   |

| 011110                 | 4.310%           | 0.863                                                   |

| 011111                 | 4.813%           | 0.963                                                   |

| 100000                 | 5.314%           | 1.063                                                   |

| 100001                 | 5.936%           | 1.188                                                   |

| 100010                 | 6.565%           | 1.313                                                   |

| 100011                 | 7.313%           | 1.463                                                   |

| 100100                 | 8.059%           | 1.613                                                   |

| 100101                 | 8.938%           | 1.788                                                   |

| 100110                 | 9.876%           | 1.975                                                   |

| 100111                 | 10.874%          | 2.175                                                   |

| 101000                 | 12.005%          | 2.400                                                   |

| 101001                 | 13.253%          | 2.650                                                   |

| 101010                 | 14.618%          | 2.925                                                   |

| 101011                 | 16.124%          | 3.225                                                   |

| 101100                 | 17.881%          | 3.575                                                   |

| 101101                 | 19.875%          | 3.975                                                   |

| 101110                 | 22.121%          | 4.425                                                   |

| 101111                 | 24.621%          | 4.925                                                   |

| 110000                 | 27.376%          | 5.475                                                   |

| 110001                 | 30.373%          | 6.075                                                   |

| 110010                 | 33.623%          | 6.725                                                   |

| 110011                 | 37.124%          | 7.425                                                   |

| 110100                 | 40.873%          | 8.175                                                   |

| 110101                 | 44.875%          | 8.975                                                   |

| 110110                 | 49.124%          | 9.825                                                   |

| 110111                 | 53.624%          | 10.725                                                  |

| 111000                 | 58.375%          | 11.675                                                  |

| 111001                 | 63.378%          | 12.675                                                  |

| 111010                 | 68.625%          | 13.725                                                  |

| 111011                 | 74.122%          | 14.825                                                  |

| 111100                 | 79.874%          | 15.975                                                  |

| 111101                 | 85.873%          | 17.175                                                  |

| 111110                 | 92.373%          | 18.475                                                  |

| 111111                 | 100.000%         | 20.000                                                  |

## **Brightness Ramp Control**

When changing the group A brightness, the IC steps through the brightness table at rate programmed by the RAMP register, indicated in Table 2.

#### Table 2. Group A Brightness Ramp Control

| RAMP[1:0] | Time per Step | Full-Scale Ramp Time |

|-----------|---------------|----------------------|

| 00        | 0.1ms         | 6.4ms                |

| 01        | 25ms          | 1600ms               |

| 10        | 50ms          | 3200ms               |

| 11 100ms  |               | 6400ms               |

|           |               |                      |

## **V**<sub>OUT</sub> Short-Circuit Protection

The FAN5702 has integrated protection circuitry to prevent the device from being short circuited when the output voltage falls below 2V. If this occurs, FAN5702 turns off the charge pump and the LED driver outputs, but a small bypass switch is left on. The device monitors the output voltage to determine if it is still in short circuit condition and, once it has passed, soft-starts and returns to normal operation.

## Vout Over-Voltage Protection

If the output voltage goes above 6V, the FAN5702 shuts down until this condition has passed. The charge pump and LED driver outputs are turned off. Once this condition has passed FAN5702 soft-starts into normal operation.

## I<sup>2</sup>C Interface

The FAN5702's serial interface is compatible with standard and fast  $I^2C$  bus specifications. The FAN5702's SCL line is an input and its SDA line is a bi-directional open-drain output, meaning that it can only pull down the bus when active. The SDA line only pulls LOW during data reads and when signaling ACK. All data is shifted in MSB (bit 7) first.

## **Slave Address**

The FAN5702's slave address is 6CH.

#### Table 3. I<sup>2</sup>C Slave Address

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

|---|---|---|---|---|---|---|-----|

| 0 | 1 | 1 | 0 | 1 | 1 | 0 | R/W |

#### **Register Addressing**

The FAN5702 has six user-accessible registers.

#### Table 4. I<sup>2</sup>C Register Addresses

|         | <u> </u>      |   |   |   |         |   |   |   |     |

|---------|---------------|---|---|---|---------|---|---|---|-----|

|         | Default Value |   |   |   | Address |   |   |   |     |

|         | 7             | 6 | 5 | 4 | 3       | 2 | 1 | 0 | HEX |

| GENERAL | 0             | 0 | 0 | 0 | 0       | 0 | 0 | 0 | 10  |

| CONFIG  | 0             | 0 | 0 | 0 | 0       | 0 | 0 | 0 | 20  |

| CHA     | 1             | 1 | 1 | 1 | 1       | 1 | 1 | 1 | A0  |

| CH3     | 1             | 1 | 1 | 1 | 1       | 1 | 1 | 1 | 30  |

| CH4     | 1             | 1 | 1 | 1 | 1       | 1 | 1 | 1 | 40  |

| CH5     | 1             | 1 | 1 | 1 | 1       | 1 | 1 | 1 | 50  |

| CH6     | 1             | 1 | 1 | 1 | 1       | 1 | 1 | 1 | 60  |

#### Note:

7. Bold identifies bits that cannot be overwritten.

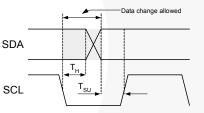

#### **Bus Timing**

As shown in Figure 19, data is normally transferred when SCL is LOW. Data is clocked in to the FAN5702 on the rising edge of SCL. Typically, data transitions shortly at or after the falling edge of SCL to allow ample time for the data to set up before the next SCL rising edge.

Figure 19. Data Transfer Timing

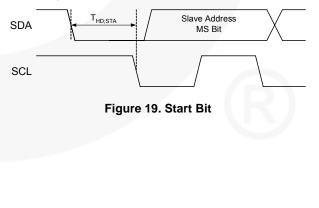

Each bus transaction begins and ends with SDA and SCL HIGH. A transaction begins with a START condition, which is defined as SDA transitioning from 1 to 0 with SCL HIGH, as shown in Figure 19.

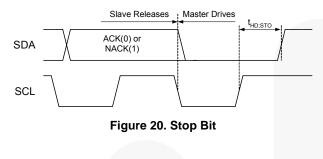

© 2010 Fairchild Semiconductor Corporation FAN5702 • Rev. 1.0.3 A transaction ends with a STOP condition, which is defined as SDA transitioning from 0 to 1 with SCL HIGH, as shown in Figure 20.

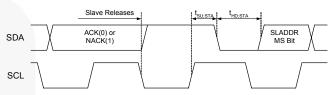

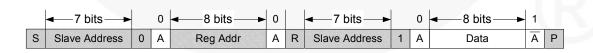

During a read from the FAN5702 (Figure 23), the master issues a "Repeated Start" after sending the register address and before resending the slave address. The "Repeated Start" is a 1-to-0 transition on SDA while SCL is HIGH, as shown in Figure 21.

Figure 21 Repeated Start Timing

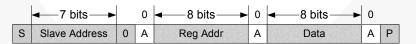

## **Read and Write Transactions**

The following figures outline the sequences for data read and write. Bus control is signified by the shading of the packet, defined as Master Drives Bus and Slave Drives Bus. All addresses and data are MSB first.

#### Table 5. I<sup>2</sup>C bit Definitions for Figure 22 and Figure 23.

| Symbol | Definition                                                          |  |  |

|--------|---------------------------------------------------------------------|--|--|

| S      | START. See Figure 19.                                               |  |  |

| A      | ACK. The slave drives SDA to 0 to acknowledge the preceding packet. |  |  |

| Ā      | NACK. The slave sends a 1 to NACK the preceding packet.             |  |  |

| R      | Repeated START. See Figure 21.                                      |  |  |

| Р      | STOP. See Figure 20.                                                |  |  |

Figure 23. Read Transaction

© 2010 Fairchild Semiconductor Corporation FAN5702 • Rev. 1.0.3

# **Register Descriptions**

The following tables define the operation of each register bit. **Bold** values are power-up defaults. These values apply only to  $l^2C$  version of the part.

| Bit     | Name         | Default<br>Value   | Description                                                                                                                                           |  |  |

|---------|--------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| GENERAL | Defa         | ult: 00H Ge        | neral Purpose Register ADDR = 10H                                                                                                                     |  |  |

| 7       | PWM          | 0                  | Setting this bit=1 changes the EN pin to function as a PWM dimming input for group A LEDs. This bit must be set to zero for the chip to be disabled.  |  |  |

| 6,5     | FS1, FS2     | 00                 | 00=20mA (default), 01=30mA, 10=15mA, 11=8mA when I <sup>2</sup> C is used.                                                                            |  |  |

| 4       | EN6          | 0                  | Default=0 (Off), LED Channel Active=1                                                                                                                 |  |  |

| 3       | EN5          | 0                  | Default=0 (Off), LED Channel Active=1                                                                                                                 |  |  |

| 2       | EN4          | 0                  | Default=0 (Off), LED Channel Active=1                                                                                                                 |  |  |

| 1       | EN3          | 0                  | Default=0 (Off), LED Channel Active=1                                                                                                                 |  |  |

| 0       | ENA          | 0                  | Default=0 (Off), LED Channel Active=1                                                                                                                 |  |  |

| CONFIG  | Defa         | ult: 00H Co        | nfiguration Register ADDR = 20H                                                                                                                       |  |  |

| 7       | T56          | 0                  | Tie channel 5 and 6 together. Default=0 (Separate). Group 5&6 =1. Both currents are set by CH5 register. T56 is overwritten by either S5A or S6A.     |  |  |

| 6       | T34          | 0                  | Tie channel 3 and 4 together. Default=0 (Separate). Group 3&4 =1. Both currents are set by the CH3 register. T34 is overwritten by either S3A or S4A. |  |  |

| 5       | S6A          | 0                  | CH6 group configuration. Independent=0 (default); part of group A=1.                                                                                  |  |  |

| 4       | S5A          | 0                  | CH5 group configuration. Independent=0 (default); part of group A=1.                                                                                  |  |  |

| 3       | S4A          | 0                  | CH4 group configuration. Independent=0 (default); part of group A=1.                                                                                  |  |  |

| 2       | S3A          | 0                  | CH3 group configuration. Independent=0 (default); part of group A=1.                                                                                  |  |  |

| 1,0     | RS1, RS0     | 00                 | Sets current ramp rate for group A channels                                                                                                           |  |  |

| СНА     | Defa         | ult: FFH Gr        | oup A Brightness Control ADDR = A0H                                                                                                                   |  |  |

| 7:6     | Reserved     | 11                 | Vendor ID bits. These bits can be used to distinguish between vendors via I <sup>2</sup> C. Writing to these bits does not change their value.        |  |  |

| 5:0     | Brightness A | 0 – 63<br>00 – 3FH | 6-bit value that controls group A brightness per values in Table 1                                                                                    |  |  |

| CH3     |              | Default: Ch        | annel 3 Brightness Control ADDR=30H                                                                                                                   |  |  |

| 7:6     | Reserved     | 11                 | Writing to these bits does not change their value.                                                                                                    |  |  |

| 5:0     | Brightness 3 | 0 – 63<br>00 – 3FH | 6-bit value that controls channel 3 brightness per values in Table 1                                                                                  |  |  |

| CH4     | Defa         | ult: FFH Ch        | annel 4 Brightness Control ADDR = 40H                                                                                                                 |  |  |

| 7:6     | Reserved     | 11                 | Writing to these bits does not change their value.                                                                                                    |  |  |

| 5:0     | Brightness 4 | 0 – 63<br>00 – 3FH | 6-bit value that controls channel 3 brightness per values in Table 1                                                                                  |  |  |

| CH5     | Defa         | ult: FFH Ch        | annel 5 Brightness Control ADDR = 50H                                                                                                                 |  |  |

| 7:6     | Reserved     | 11                 | Writing to these bits does not change their value.                                                                                                    |  |  |

| 5:0     | Brightness 5 | 0 – 63<br>00 – 3FH | 6-bit value that controls channel 3 brightness per values in Table 1                                                                                  |  |  |

| CH6     | Defa         | ult: FFH Ch        | annel 6 Brightness Control ADDR = 60H                                                                                                                 |  |  |

| 7:6     | Reserved     | 11                 | Writing to these bits does not change their value.                                                                                                    |  |  |

| 5:0     | Brightness 6 | 0 – 63<br>00 – 3FH | 6-bit value that controls channel 3 brightness per values in Table 1                                                                                  |  |  |

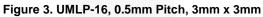

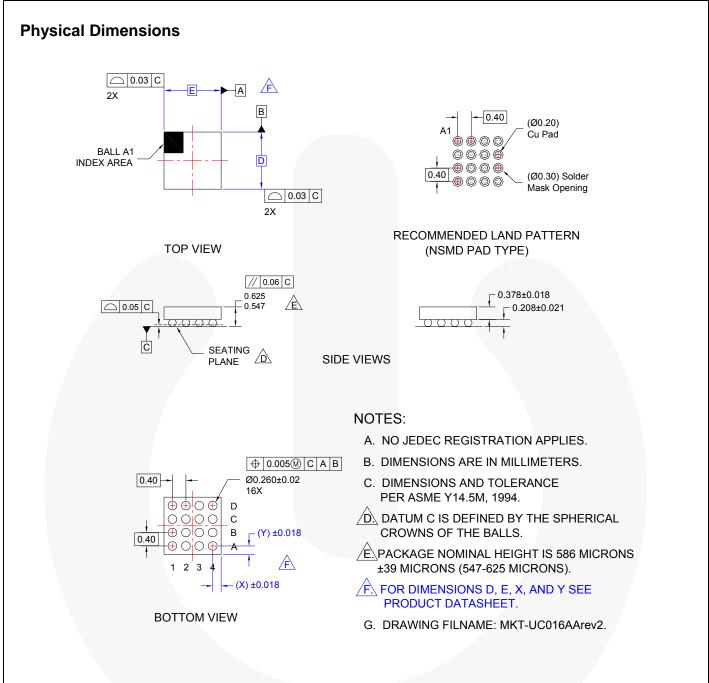

#### Figure 24. WLCSP-16, 0.4mm Pitch, Dimensions

## **Product-Specific Dimensions**

| Product     | D       | E       | Х       | Y       |

|-------------|---------|---------|---------|---------|

| FAN5702UCxx | 1.610mm | 1.610mm | 0.205mm | 0.205mm |

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor's online packaging area for the most recent package drawings: <u>http://www.fairchildsemi.com/packaging/</u>. FAN5702

I

Configurable 180mA 6-LED Driver with I<sup>2</sup>C Control

Always visit Fairchild Semiconductor's online packaging area for the most recent package drawings: <u>http://www.fairchildsemi.com/packaging/</u>.

\* Trademarks of System General Corporation, used under license by Fairchild Semiconductor.

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELABILITY, FUNCTION, OR DESIGN, FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

#### As used herein:

- Life support devices or systems are devices or systems which, (a) are

intended for surgical implant into the body or (b) support or sustain life,

and (c) whose failure to perform when properly used in accordance

with instructions for use provided in the labeling, can be reasonably

expected to result in a significant injury of the user.

- A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### ANTI-COUNTERFEITING POLICY

Fairchild Semiconductor Corporation's Anti-Counterfeiting Policy. Fairchild's Anti-Counterfeiting Policy is also stated on our external website, www.fairchildsemi.com, under Sales Support.

Counterfeiting of semiconductor parts is a growing problem in the industry. All manufacturers of semiconductor products are experiencing counterfeiting of their parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed applications, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly form Authorized Fairchild Distributors are genuine parts, have full traceability, meet Fairchild's quality standards for handling and storage and provide access to Fairchild's full range of up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address any warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.

#### PRODUCT STATUS DEFINITIONS

| Definition | of Terms |

|------------|----------|

|------------|----------|

| Deminuon or remis        |                       |                                                                                                                                                                                                        |  |  |  |

|--------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Datasheet Identification | Product Status        | Definition                                                                                                                                                                                             |  |  |  |

| Advance Information      | Formative / In Design | Datasheet contains the design specifications for product development. Specifications may change in<br>any manner without notice.                                                                       |  |  |  |

| Preliminary              | First Production      | Datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild<br>Semiconductor reserves the right to make changes at any time without notice to improve design. |  |  |  |

| No Identification Needed | Full Production       | Datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes<br>at any time without notice to improve the design.                                               |  |  |  |

| Obsolete                 | Not In Production     | Datasheet contains specifications on a product that is discontinued by Fairchild Semiconductor.<br>The datasheet is for reference information only.                                                    |  |  |  |

Rev. 149