### Features

- Supply Voltage up to 40V

- $R_{DSon}$  Typically 0.8 $\Omega$  at 25°C, Maximum 1.5 $\Omega$  at 150°C

- Up to 1.0A Output Current

- Three Half-bridge Outputs Formed by Three High-side and Three Low-side Drivers

- Capable of Switching Loads such as DC Motors, Bulbs, Resistors, Capacitors, and Inductors

- PWM Capability up to 25 kHz for Each High-side Output Controlled by External PWM Signal

- No Shoot-through Current

- + Very Low Quiescent Current  $I_{VS}$  < 5  $\mu A$  in Standby Mode over Total Temperature Range

- Outputs Short-circuit Protected

- Selective Overtemperature Protection for Each Switch and Overtemperature Prewarning

- Undervoltage Protection

- Various Diagnostic Functions such as Shorted Output, Open Load, Overtemperature and Power-supply Fail Detection

- Serial Data Interface, Daisy Chain Capable, up to 2 MHz Clock Frequency

- QFN18 Package

## 1. Description

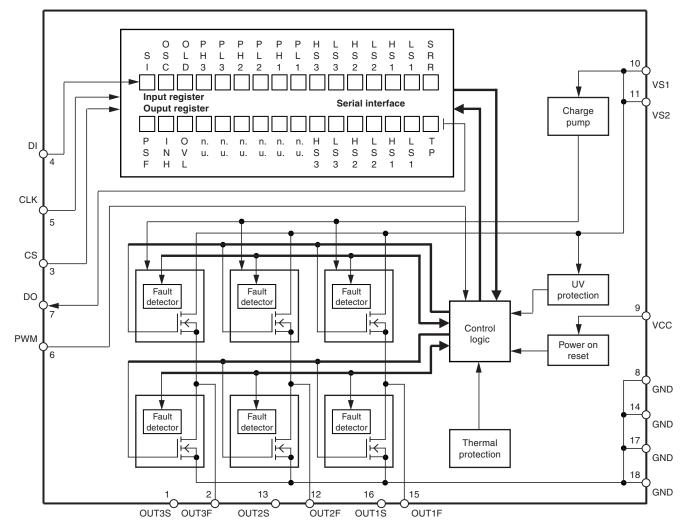

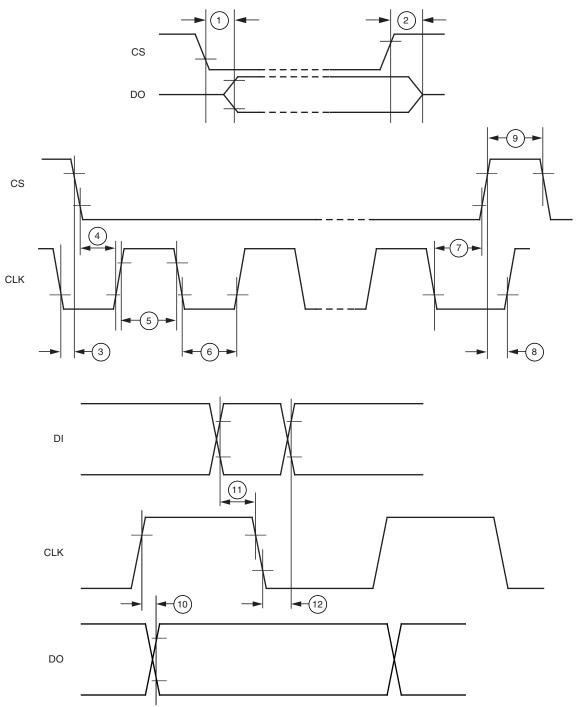

The ATA6831 provides fully protected driver interfaces designed in SOI technology. They are used to allow a microcontroller to control up to 3 different loads in automotive and industrial applications.

Each of the 3 high-side and 3 low-side drivers is capable of driving currents up to 1.0A. Due to the enhanced PWM signal (up to 25 kHz) it is possible to generate a smooth control of, for example, a DC motor without any noise. The drivers are internally connected to form 3 half-bridges and can be controlled separately from a standard serial data interface, enabling all kinds of loads, such as bulbs, resistors, capacitors and inductors, to be combined. The IC design especially supports the application of H-bridges to drive DC motors.

Protection is guaranteed with respect to short-circuit conditions, overtemperature and undervoltage. Various diagnostic functions and a very low quiescent current in standby mode enable a wide range of applications. Automotive qualification (protection against conducted interferences, EMC protection and 2-kV ESD protection) gives added value and enhanced quality for exacting requirements of automotive applications.

Triple Half-bridge Driver with SPI and PWM

# ATA6831

4908G-AUTO-07/10

#### Figure 1-1. Block Diagram

# 2. Pin Configuration

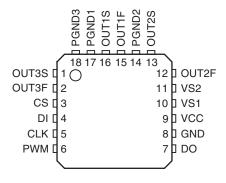

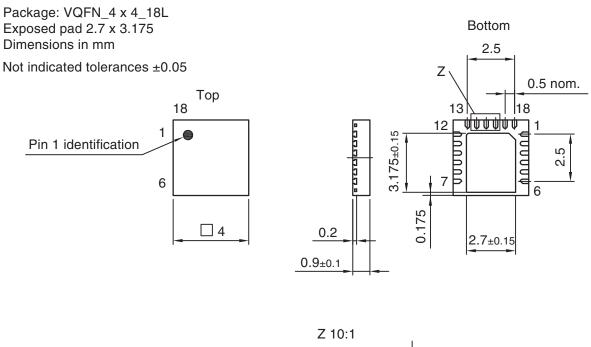

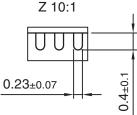

#### Figure 2-1. Pinning QFN18

#### Table 2-1.Pin Description

| Pin | Symbol | Function                                                                                                                                                                                                                                                                                                         |

|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | OUT3S  | Used only for final testing, to be connected to OUT3F                                                                                                                                                                                                                                                            |

| 2   | OUT3F  | Half-bridge output 3; formed by internally connecting power MOS high-side switch 3 and low-side switch 3 with internal reverse diodes; short circuit protection; overtemperature protection; diagnosis for short and open load                                                                                   |

| 3   | CS     | Chip select input; 5V CMOS logic level input with internal pull-up;<br>low = serial communication is enabled, high = disabled                                                                                                                                                                                    |

| 4   | DI     | Serial data input; 5V CMOS logic level input with internal pull-down; receives serial data from the control device; DI expects a 16-bit control word with LSB transferred first                                                                                                                                  |

| 5   | CLK    | Serial clock input; 5V CMOS logic level input with internal pull-down; controls serial data input interface and internal shift register (f <sub>max</sub> = 2 MHz)                                                                                                                                               |

| 6   | PWM    | PWM input; 5V CMOS logic level input with internal pull-down                                                                                                                                                                                                                                                     |

| 7   | DO     | Serial data output; 5V CMOS logic-level tri-state output for output (status) register data; sends 16-bit status information to the microcontroller (LSB transferred first); output will remain tri-stated unless device is selected by CS = low; this allows several ICs to operate on only one data-output line |

| 8   | GND    | Ground                                                                                                                                                                                                                                                                                                           |

| 9   | VCC    | Logic supply voltage (5V)                                                                                                                                                                                                                                                                                        |

| 10  | VS1    | Power supply for output stages OUT1 and OUT2; internal supply                                                                                                                                                                                                                                                    |

| 11  | VS2    | Power supply for output stages OUT2 and OUT3; internal supply                                                                                                                                                                                                                                                    |

| 12  | OUT2F  | Half-bridge output 2; formed by internally connected power MOS high-side switch 2 and low-side switch 2 with internal reverse diodes; short circuit protection; overtemperature protection; diagnosis for short and open load                                                                                    |

| 13  | OUT2S  | Used only for final testing, to be connected to OUT2F                                                                                                                                                                                                                                                            |

| 14  | PGND2  | Power ground OUT2                                                                                                                                                                                                                                                                                                |

| 15  | OUT1F  | Half-bridge output 1; formed by internally connected power MOS high-side switch 1 and low-side switch 1 with internal reverse diodes; short circuit protection; overtemperature protection; diagnosis for short and open load                                                                                    |

| 16  | OUT1S  | Used only for final testing, to be connected to OUT1F                                                                                                                                                                                                                                                            |

| 17  | PGND1  | Power ground OUT1                                                                                                                                                                                                                                                                                                |

| 18  | PGND3  | Power ground OUT3                                                                                                                                                                                                                                                                                                |

#### 3. **Functional Description**

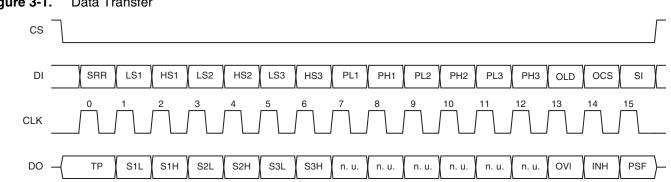

#### 3.1 **Serial Interface**

Data transfer starts with the falling edge of the CS signal. Data must appear at DI synchronized to CLK and is accepted on the falling edge of the CLK signal. The LSB (bit 0, SRR) has to be transferred first. Execution of new input data is enabled on the rising edge of the CS signal. When CS is high, pin DO is in tri-state condition. This output is enabled on the falling edge of CS. Output data will change their state with the rising edge of CLK and stay stable until the next rising edge of CLK appears. LSB (bit 0, TP) is transferred first.

#### Figure 3-1. Data Transfer

| ble 3-1 | I. Input Data Pro | 00000                                                                                                                                                           |

|---------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit     | Input Register    | Function                                                                                                                                                        |

| 0       | SRR               | Status register reset (high = reset; the bits PSF and OVL in the output data register are set to low)                                                           |

| 1       | LS1               | Controls output LS1 (high = switch output LS1 on)                                                                                                               |

| 2       | HS1               | Controls output HS1 (high = switch output HS1 on)                                                                                                               |

| 3       | LS2               | See LS1                                                                                                                                                         |

| 4       | HS2               | See HS1                                                                                                                                                         |

| 5       | LS3               | See LS1                                                                                                                                                         |

| 6       | HS3               | See HS1                                                                                                                                                         |

| 7       | PL1               | Output LS1 additionally controlled by PWM Input                                                                                                                 |

| 8       | PH1               | Output HS1 additionally controlled by PWM Input                                                                                                                 |

| 9       | PL2               | See PL1                                                                                                                                                         |

| 10      | PH2               | See PH1                                                                                                                                                         |

| 11      | PL3               | See PL1                                                                                                                                                         |

| 12      | PH3               | See PH1                                                                                                                                                         |

| 13      | OLD               | Open load detection (low = on)                                                                                                                                  |

| 14      | OCS               | Overcurrent shutdown (high = overcurrent shutdown is active)                                                                                                    |

| 15      | SI                | Software inhibit; low = standby, high = normal operation<br>(data transfer is not affected by the standby function because the digita<br>part is still powered) |

#### nut Data Protocol 1- 0

| Bit | Output (Status)<br>Register | Function                                                                                                                                                                                                                            |

|-----|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | TP                          | Temperature prewarning: high = warning                                                                                                                                                                                              |

| 1   | Status LS1                  | Normal operation: high = output is on, low = output is off<br>Open-load detection: high = open load, low = no open load<br>(correct load condition is detected if the corresponding output is<br>switched off); not affected by SRR |

| 2   | Status HS1                  | Normal operation: high = output is on, low = output is off<br>Open-load detection: high = open load, low = no open load<br>(correct load condition is detected if the corresponding output is<br>switched off); not affected by SRR |

| 3   | Status LS2                  | Description see LS1                                                                                                                                                                                                                 |

| 4   | Status HS2                  | Description see HS1                                                                                                                                                                                                                 |

| 5   | Status LS3                  | Description see LS1                                                                                                                                                                                                                 |

| 6   | Status HS3                  | Description see HS1                                                                                                                                                                                                                 |

| 7   | n. u.                       | Not used                                                                                                                                                                                                                            |

| 8   | n. u.                       | Not used                                                                                                                                                                                                                            |

| 9   | n. u.                       | Not used                                                                                                                                                                                                                            |

| 10  | n. u.                       | Not used                                                                                                                                                                                                                            |

| 11  | n. u.                       | Not used                                                                                                                                                                                                                            |

| 12  | n. u.                       | Not used                                                                                                                                                                                                                            |

| 13  | OVL                         | Over-load detected: set high, when at least one output is switched off<br>by a short-circuit condition or an overtemperature event. Bits 1 to 6 car<br>be used to detect the affected switch                                        |

| 14  | INH                         | Inhibit: this bit is controlled by software (bit SI in input register)<br>High = standby, low = normal operation                                                                                                                    |

| 15  | PSF                         | Power-supply fail: undervoltage at pin VS detected                                                                                                                                                                                  |

| Table 3-2.Output Data Protocol |

|--------------------------------|

|--------------------------------|

After power-on reset, the input register has the following status:

| Bit 1 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| SI    | ocs    | OLD    | PH3    | PL3    | PH2    | PL2   | PH1   | PL1   | HS3   | LS3   | HS2   | LS2   | HS1   | LS1   | SRR   |

| Н     | Н      | Н      | L      | L      | L      | L     | L     | L     | L     | L     | L     | L     | L     | L     | L     |

The following patterns are used to enable internal test modes of the IC. Do not use these patterns during normal operation.

| Bit 15 | Bit 14 | Bit 13<br>(OCS) | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6<br>(HS3) | Bit 5<br>(LS3) | Bit 4<br>(HS2) | Bit 3<br>(LS2) | Bit 2<br>(HS1) | Bit 1<br>(LS1) | Bit 0<br>(SRR) |

|--------|--------|-----------------|--------|--------|--------|-------|-------|-------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| Н      | Н      | Н               | Н      | Н      | L      | L     | L     | L     | L              | L              | L              | L              | L              | L              | L              |

| Н      | Н      | Н               | L      | L      | Н      | Н     | L     | L     | L              | L              | L              | L              | L              | L              | L              |

| Н      | Н      | Н               | L      | L      | L      | L     | Н     | Н     | L              | L              | L              | L              | L              | L              | L              |

### 3.2 Power-supply Fail

If undervoltage is detected at pin VS, the power-supply fail bit (PSF) in the output register is set and all outputs are disabled. To detect an undervoltage, its duration has to last longer than the undervoltage detection delay time  $t_{dUV}$ . The outputs are enabled immediately when the supply voltage returns to the normal operational value. The PSF bit stays high until it is reset by the SRR bit in the input register.

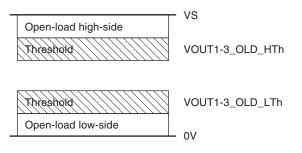

#### 3.3 Open-load Detection

If the open-load detection bit (OLD) is set to low, a pull-up current for each high-side switch and a pull-down current for each low-side switch is turned on (open-load detection current  $I_{Out1-3}$ ).

The open load condition of all the outputs is indicated in the SPI output register bit 1-6. High-side open load is detected in case of OUT1-3 voltage above maximum voltage VOUT1-3\_OLD\_HTh while Low-side open load is detected in case of OUT1-3 voltage below minimum voltage VOUT1-3\_OLD\_LTh, see Figure 3-2.

If the OUTx is not connected, a Low-side open load is indicated, because the low-side current sink is higher than the high-side current source, see open load detection current ratio  $I_{Out1-3L}/I_{Out1-3H}$ .

Switching on an output stage with the OLD bit set to low disables the open-load function for this output.

#### Figure 3-2. OLD Threshold Level

# ATA6831

### 3.4 Overtemperature Protection

If the junction temperature of one or more output stages exceeds the thermal prewarning threshold,  $T_{jPW set}$ , the temperature prewarning bit (TP) in the output register is set. When the temperature falls below the thermal prewarning threshold,  $T_{jPW reset}$ , the bit TP is reset. The TP bit can be read without transferring a complete 16-bit data word. The status of TP is available at pin DO with the falling edge of CS. After the microcontroller has read this information, CS is set high and the data transfer is interrupted without affecting the status of input and output registers.

If the junction temperature of an output stage exceeds the thermal shutdown threshold,  $T_{jswitch off}$ , the affected output is disabled and the corresponding bit in the output register is set to low. Additionally, the overload detection bit (OVL) in the output register is set. The output can be enabled again when the temperature falls below the thermal shutdown threshold,  $T_{jswitch on}$ , and the SRR bit in the input register is set to high. The hysteresis of thermal prewarning and shutdown threshold avoids oscillations.

### 3.5 Short-circuit Protection

The output currents are limited by a current regulator. Overcurrent detection is activated by writing a high to the overcurrent shutdown bit (OCS) bit in the input register. When the current in an output stage exceeds the overcurrent limitation and shut-down threshold, it is switched off, following a delay time ( $t_{dSd}$ ). The over-load detection bit (OVL) is set and the corresponding status bit in the output register is set to low. For OCS = low, the overcurrent shutdown is inactive and the OVL bit is not set by an overcurrent. By writing a high to the SRR bit in the input register the OVL bit is reset and the disabled outputs are enabled.

### 3.6 Inhibit

The SI bit in the input register has to be set to zero to inhibit the ATA6831.

In this state, all output stages are then turned off but the serial interface remains active. The current consumption is reduced to less than 5  $\mu$ A at pin VS and less than 100  $\mu$ A at pin VCC. The output stages can be reactivated by setting bit SI to "1".

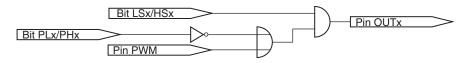

### 3.7 PWM Mode

The common input for all six outputs is pin PWM (Figure 3-3). The selection of the outputs, which are controlled by PWM, is done by input data register PLx or PHx. In addition to the PWM input register, the corresponding input registers HSx and LSs have to be set.

Switching the high side outputs is possible up to 25 kHz, low side switches up to 8 kHz.

### Figure 3-3. Output Control by PWM

## 4. Absolute Maximum Ratings

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Parameters                                             | Pin        | Symbol                                                                     | Value                                        | Unit |

|--------------------------------------------------------|------------|----------------------------------------------------------------------------|----------------------------------------------|------|

| Supply voltage                                         | 10, 11     | V <sub>VS</sub>                                                            | -0.3 to +40                                  | V    |

| Supply voltage t < 0.5s; $I_{VS}$ > -2A                | 10, 11     | V <sub>VS</sub>                                                            | -1                                           | V    |

| Logic supply voltage                                   | 9          | V <sub>VCC</sub>                                                           | -0.3 to +7                                   | V    |

| Logic input voltage                                    | 3, 4, 5, 6 | $V_{CS}, V_{DI}, V_{CLK}, V_{PWM}$                                         | –0.3 to V <sub>VCC</sub> + 0.3               | V    |

| Logic output voltage                                   | 7          | V <sub>DO</sub>                                                            | –0.3 to V <sub>VCC</sub> + 0.3               | V    |

| Input current                                          | 3, 4, 5, 6 | I <sub>CS</sub> , I <sub>DI</sub> , I <sub>CLK</sub> ,<br>I <sub>PWM</sub> | -10 to +10                                   | mA   |

| Output current                                         | 7          | I <sub>DO</sub>                                                            | -10 to +10                                   | mA   |

| Output current                                         | 2, 12, 15  | I <sub>Out1</sub> , I <sub>Out2</sub> , I <sub>Out3</sub>                  | Internally limited, see output specification |      |

| Output voltage                                         | 2, 12, 15  | I <sub>Out1</sub> , I <sub>Out2</sub> , I <sub>Out3</sub>                  | -0.3 to +40                                  | V    |

| Reverse conducting current $(t_{pulse} = 150 \ \mu s)$ | 2, 12, 15  | I <sub>Out1</sub> , I <sub>Out2</sub> , I <sub>Out3</sub>                  | 17                                           | А    |

| Junction temperature range                             |            | TJ                                                                         | -40 to +150                                  | °C   |

| Storage temperature range                              |            | T <sub>STG</sub>                                                           | -55 to +150                                  | °C   |

### 5. Thermal Resistance

| Parameters                                  | Test Conditions         | Symbol            | Value | Unit |

|---------------------------------------------|-------------------------|-------------------|-------|------|

| Thermal resistance from junction to case    |                         | R <sub>thJC</sub> | 5     | k/W  |

| Thermal resistance from junction to ambient | Depends on the PC board | R <sub>thJA</sub> | 40    | K/W  |

## 6. Operating Range

| Parameters                       | Symbol                             | Value                                | Unit |

|----------------------------------|------------------------------------|--------------------------------------|------|

| Supply voltage                   | V <sub>VS</sub>                    | V <sub>UV</sub> <sup>(1)</sup> to 40 | V    |

| Logic supply voltage             | V <sub>VCC</sub>                   | 4.75 to 5.25                         | V    |

| Logic input voltage              | $V_{CS}, V_{DI}, V_{CLK}, V_{PWM}$ | –0.3 to $V_{VCC}$                    | V    |

| Serial interface clock frequency | f <sub>CLK</sub>                   | 2                                    | MHz  |

| PWM input frequency              | f <sub>PWM</sub>                   | max. 25                              | kHz  |

| Junction temperature range       | Tj                                 | -40 to +150                          | °C   |

Note: 1. Threshold for undervoltage description

## 7. Noise and Surge Immunity

| Parameters                | Test Conditions | Value                  |

|---------------------------|-----------------|------------------------|

| Conducted interferences   | ISO 7637-1      | Level 4 <sup>(1)</sup> |

| Interference suppression  | VDE 0879 Part 2 | Level 5                |

| ESD (Human Body Model)    | ESD S 5.1       | 2 kV                   |

| CDM (Charge Device Model) | ESD STM5.3.1    | 500V                   |

Note: 1. Test pulse 5:  $V_{smax} = 40V$

### 8. Electrical Characteristics

$7.5V < V_{VS} < 40V$ ;  $4.75V < V_{VCC} < 5.25V$ ; INH = High;  $-40^{\circ}C < T_i < 150^{\circ}C$ ; unless otherwise specified, all values refer to GND pins.

| No. | Parameters                        | Test Conditions                                                                                      | Pin    | Symbol                    | Min. | Тур. | Max. | Unit | Type* |

|-----|-----------------------------------|------------------------------------------------------------------------------------------------------|--------|---------------------------|------|------|------|------|-------|

| 1   | Current Consumption               |                                                                                                      | L L    |                           |      |      |      |      |       |

| 1.1 | Quiescent current VS              | $V_{VS}$ < 20V, SI = low                                                                             | 10, 11 | I <sub>VS</sub>           |      | 1    | 5    | μA   | Α     |

| 1.2 | Quiescent current VCC             | 4.75V < V <sub>VCC</sub> < 5.25V,<br>SI = low                                                        | 9      | I <sub>VCC</sub>          |      | 60   | 100  | μA   | A     |

| 1.3 | Supply current VS                 | V <sub>VS</sub> < 20V normal<br>operating, all outputs off,<br>input register bit 13<br>(OLD) = high | 10, 11 | I <sub>VS</sub>           |      | 4    | 6    | mA   | A     |

| 1.4 | Supply current VCC                | 4.75V < V <sub>VCC</sub> < 5.25V,<br>normal operating                                                | 9      | I <sub>VCC</sub>          |      | 350  | 650  | μA   | A     |

| 1.5 | Discharge current VS              | $V_{VS} = 32.5V$ , INH = low                                                                         | 10, 11 | I <sub>VS</sub>           | 0.5  |      | 5.5  | mA   | Α     |

| 1.6 | Discharge current VS              | $V_{VS} = 40V$ , INH = low                                                                           | 10, 11 | I <sub>VS</sub>           | 2.5  |      | 14   | mA   | Α     |

| 2   | Undervoltage Detection            | n, Power-on Reset                                                                                    |        |                           |      |      |      |      | •     |

| 2.1 | Power-on reset<br>threshold       |                                                                                                      | 9      | V <sub>VCC</sub>          | 3.2  | 3.9  | 4.4  | V    | A     |

| 2.2 | Power-on reset delay time         | After switching on $V_{VCC}$                                                                         |        | t <sub>dPor</sub>         | 30   | 95   | 190  | μs   | A     |

| 2.3 | Undervoltage-detection threshold  | $V_{VCC} = 5V$                                                                                       | 10, 11 | V <sub>Uv</sub>           | 5.6  |      | 7.0  | V    | A     |

| 2.4 | Undervoltage-detection hysteresis | $V_{VCC} = 5V$                                                                                       | 10, 11 | $\Delta V_{Uv}$           |      | 0.6  |      | V    | A     |

| 2.5 | Undervoltage-detection delay time |                                                                                                      |        | t <sub>dUV</sub>          | 10   |      | 40   | μs   | A     |

| 3   | Thermal Prewarning an             | nd Shutdown                                                                                          |        |                           |      |      |      |      | •     |

| 3.1 | Thermal prewarning set            |                                                                                                      |        | T <sub>jPW set</sub>      | 120  | 145  | 170  | °C   | В     |

| 3.2 | Thermal prewarning reset          |                                                                                                      |        | T <sub>jPW reset</sub>    | 105  | 130  | 155  | °C   | В     |

| 3.3 | Thermal prewarning hysteresis     |                                                                                                      |        | $\Delta T_{jPW}$          |      | 15   |      | к    | В     |

| 3.4 | Thermal shutdown off              |                                                                                                      |        | T <sub>j switch off</sub> | 150  | 175  | 200  | °C   | В     |

| 3.5 | Thermal shutdown on               |                                                                                                      |        | T <sub>j switch on</sub>  | 135  | 160  | 185  | °C   | В     |

\*) Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

Notes: 1. Delay time between rising edge of input signal at pin CS after data transmission and switch on/off output stages to 90% of final level. Device not in standby for t > 1 ms.

- 2. Delay time between rising/falling edge of input signal at pin PWM and switch on/off output stages to 90% of final level.

- 3. Difference between switch-on and switch-off delay time of input signal at pin PWM to output stages in PWM mode.

### 8. Electrical Characteristics (Continued)

$7.5V < V_{VS} < 40V; 4.75V < V_{VCC} < 5.25V; INH = High; -40^{\circ}C < T_{j} < 150^{\circ}C; unless otherwise specified, all values refer to GND pins.$

| No.   | Parameters                                                    | Test Conditions                                                                          | Pin          | Symbol                                              | Min.                      | Тур.                      | Max.                | Unit | Type* |

|-------|---------------------------------------------------------------|------------------------------------------------------------------------------------------|--------------|-----------------------------------------------------|---------------------------|---------------------------|---------------------|------|-------|

| 3.6   | Thermal shutdown<br>hysteresis                                |                                                                                          |              | $\Delta T_{jswitchoff}$                             |                           | 15                        |                     | к    | В     |

| 3.7   | Ratio thermal shutdown off/thermal prewarning set             |                                                                                          |              | T <sub>j</sub> switch off∕<br>T <sub>jPW set</sub>  | 1.05                      | 1.2                       |                     |      | В     |

| 3.8   | Ratio thermal shutdown<br>on/thermal prewarning<br>reset      |                                                                                          |              | T <sub>j</sub> switch on∕<br>T <sub>jPW</sub> reset | 1.05                      | 1.2                       |                     |      | В     |

| 4     | Output Specification (                                        | OUT1 to OUT3)                                                                            |              |                                                     |                           |                           |                     |      |       |

| 4.1   | On resistance                                                 | I <sub>Out1-3</sub> = -0.9 A                                                             | 2, 12,<br>15 | R <sub>DSon1-3H</sub>                               |                           |                           | 1.5                 | Ω    | A     |

| 4.2   |                                                               | I <sub>Out1-3</sub> = -0.9 A                                                             | 2, 12,<br>15 | R <sub>DSon1-3L</sub>                               |                           |                           | 1.5                 | Ω    | A     |

| 4.3   | High-side output<br>leakage current                           | V <sub>Out 1-3 H</sub> = 0V,<br>output stages off                                        | 2, 12,<br>15 | I <sub>Out1-3H</sub>                                | -15                       |                           |                     | μA   | A     |

| 4.4   | Low-side output<br>leakage current                            | V <sub>Out 1-3 L</sub> = V <sub>VS,</sub><br>output stages off                           | 2, 12,<br>15 | I <sub>Out1-3L</sub>                                |                           |                           | 300                 | μA   | A     |

| 4.5   | High-side switch<br>reverse diode forward<br>voltage          | I <sub>Out</sub> = 1.5A                                                                  | 2, 12,<br>15 | V <sub>Out1-3</sub> – V <sub>VS</sub>               |                           |                           | 2                   | V    | A     |

| 4.6   | Low-side switch reverse diode forward voltage                 | I <sub>Out 1-3 L</sub> = -1.5A                                                           | 2, 12,<br>15 | V <sub>Out1-3L</sub>                                | 2                         |                           |                     | V    | А     |

| 4.7   | High-side overcurrent<br>limitation and shutdown<br>threshold | 7.5V < V <sub>VS</sub> < 20V                                                             | 2, 12,<br>15 | I <sub>Out1-3</sub>                                 | 1.0                       | 1.3                       | 1.7                 | А    | А     |

| 4.8   | Low-side overcurrent<br>limitation and shutdown<br>threshold  | 7.5V < V <sub>VS</sub> < 20V                                                             | 2, 12,<br>15 | I <sub>Out1-3</sub>                                 | -1.7                      | -1.3                      | -1.0                | A    | A     |

| 4.9   | High-side overcurrent<br>limitation and shutdown<br>threshold | 20V < V <sub>VS</sub> < 40V                                                              | 2, 12,<br>15 | I <sub>Out1-3</sub>                                 | 1.0                       | 1.3                       | 2.0                 | A    | A     |

| 4.10  | Low-side overcurrent<br>limitation and shutdown<br>threshold  | 20V < V <sub>VS</sub> < 40V                                                              | 2, 12,<br>15 | I <sub>Out1-3</sub>                                 | -2.0                      | -1.3                      | -1.0                | А    | A     |

| 4.11  | Overcurrent shutdown delay time                               |                                                                                          |              | t <sub>dSd</sub>                                    | 10                        |                           | 40                  | μs   | A     |

| 4.12  | High-side open load detection current                         | Input register bit 13<br>(OLD) = low, output off<br>$V_{VS} = 13V$ , $V_{Out 1-3} = 0V$  | 2, 12,<br>15 | I <sub>Out1-3H</sub>                                | 1                         | 2.5                       | 4                   | mA   | A     |

| 4.12a | High-side open load<br>detection threshold<br>level           | Input register bit 13<br>(OLD) = low, output off<br>$V_{VS} = 13V$ , $I_{Out1-3} = 0$ mA | 2, 12,<br>15 | $V_{Out1-3\_OLD\_HTh}$                              | V <sub>VS</sub> -<br>3.5V | V <sub>VS</sub> -<br>2.5V | V <sub>VS</sub> -1V | V    | А     |

\*) Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

Notes: 1. Delay time between rising edge of input signal at pin CS after data transmission and switch on/off output stages to 90% of final level. Device not in standby for t > 1 ms.

2. Delay time between rising/falling edge of input signal at pin PWM and switch on/off output stages to 90% of final level.

3. Difference between switch-on and switch-off delay time of input signal at pin PWM to output stages in PWM mode.

# ATA6831

### 8. Electrical Characteristics (Continued)

$7.5V < V_{VS} < 40V$ ;  $4.75V < V_{VCC} < 5.25V$ ; INH = High;  $-40^{\circ}C < T_j < 150^{\circ}C$ ; unless otherwise specified, all values refer to GND pins.

| No.   | Parameters                                                               | Test Conditions                                                                          | Pin           | Symbol                                     | Min.                | Тур. | Max.                   | Unit | Type* |

|-------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------|---------------|--------------------------------------------|---------------------|------|------------------------|------|-------|

| 4.13  | Low-side open load detection current                                     | Input register bit 13<br>(OLD) = low, output off<br>$V_{VS} = 13V$ , $V_{Out 1-3} = 13V$ | 2, 12,<br>15  | I <sub>Out1-3L</sub>                       | -6                  | -9   | -11                    | mA   | А     |

| 4.13a | Low-side open load<br>detection threshold<br>level                       | Input register bit 13<br>(OLD) = low, output off<br>$V_{VS} = 13V$ , $I_{Out1-3} = 0$ mA | 2, 12,<br>15  | V <sub>Out1-3_OLD_LTh</sub>                | 0.5                 | 1.5  | 2.5                    | V    | A     |

| 4.14  | Open load detection<br>current ratio                                     |                                                                                          |               | I <sub>Out1-3L</sub> /I <sub>Out1-3H</sub> | 2                   | 3    | 4                      |      |       |

| 4.15  | High-side output switch on delay <sup>(1),(2)</sup>                      | $V_{VS} = 13V$<br>$R_{Load} = 30\Omega$                                                  |               | t <sub>don</sub>                           |                     |      | 20                     | μs   | А     |

| 4.16  | Low-side output switch on delay <sup>(1),(2)</sup>                       | $V_{VS} = 13V$<br>$R_{Load} = 30\Omega$                                                  |               | t <sub>don</sub>                           |                     |      | 20                     | μs   | А     |

| 4.17  | High-side output switch off delay <sup>(1),(2)</sup>                     | $V_{VS} = 13V$<br>$R_{Load} = 30\Omega$                                                  |               | t <sub>doff</sub>                          |                     |      | 20                     | μs   | А     |

| 4.18  | Low-side output switch off delay <sup>(1),(2)</sup>                      | $V_{VS} = 13V$<br>$R_{Load} = 30\Omega$                                                  |               | t <sub>doff</sub>                          |                     |      | 3                      | μs   | А     |

| 4.19  | Dead time between<br>corresponding<br>high-side and low-side<br>switches | $V_{VS} = 13V$<br>$R_{Load} = 30\Omega$                                                  |               | t <sub>don</sub> — t <sub>doff</sub>       | 1                   |      |                        | μs   | A     |

| 4.20  | $\Delta t_{dPWM}$ low-side switch <sup>(3)</sup>                         | $V_{VS} = 13V$<br>$R_{Load} = 30\Omega$                                                  |               | $\Delta t_{dPWM} = t_{don} - t_{doff}$     |                     |      | 20                     | μs   | А     |

| 4.21  | ∆t <sub>dPWM</sub><br>high-side switch <sup>(3)</sup>                    | $V_{VS} = 13V$<br>$R_{Load} = 30\Omega$                                                  |               | $\Delta t_{dPWM} = t_{don} - t_{doff}$     | -5                  |      | 5                      | μs   | А     |

| 5     | Logic Inputs DI, CLK, 0                                                  | CS, PWM                                                                                  | 1             |                                            |                     |      | 1                      | 1    | 1     |

| 5.1   | Input voltage low-level threshold                                        |                                                                                          | 3, 4, 5,<br>6 | V <sub>IL</sub>                            | $0.3 	imes V_{VCC}$ |      |                        | V    | А     |

| 5.2   | Input voltage high-level threshold                                       |                                                                                          | 3, 4, 5,<br>6 | V <sub>IH</sub>                            |                     |      | $0.7 	imes V_{ m VCC}$ | V    | А     |

| 5.3   | Hysteresis of input voltage                                              |                                                                                          | 3, 4, 5,<br>6 | ΔVI                                        | 50                  |      | 700                    | mV   | A     |

| 5.4   | Pull-down current pins DI, CLK, PWM                                      | $V_{DI}, V_{CLK}, V_{PWM} = V_{VCC}$                                                     | 4, 5, 6       | I <sub>PD</sub>                            | 10                  |      | 65                     | μA   | A     |

| 5.5   | Pull-up current<br>pin CS                                                | $V_{CS} = 0V$                                                                            | 3             | I <sub>PU</sub>                            | -65                 |      | -10                    | μA   | А     |

\*) Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

Notes: 1. Delay time between rising edge of input signal at pin CS after data transmission and switch on/off output stages to 90% of final level. Device not in standby for t > 1 ms.

2. Delay time between rising/falling edge of input signal at pin PWM and switch on/off output stages to 90% of final level.

3. Difference between switch-on and switch-off delay time of input signal at pin PWM to output stages in PWM mode.

### 8. Electrical Characteristics (Continued)

$7.5V < V_{VS} < 40V$ ;  $4.75V < V_{VCC} < 5.25V$ ; INH = High;  $-40^{\circ}C < T_{j} < 150^{\circ}C$ ; unless otherwise specified, all values refer to GND pins.

| No. | Parameters                                        | Test Conditions                               | Pin | Symbol            | Min.                       | Тур. | Max. | Unit | Type* |

|-----|---------------------------------------------------|-----------------------------------------------|-----|-------------------|----------------------------|------|------|------|-------|

| 6   | Serial Interface – Logic                          | Output DO                                     |     |                   | 1 1                        |      | 1    | I    | 1     |

| 6.1 | Output-voltage low level                          | I <sub>DOL</sub> = 2 mA                       | 7   | V <sub>DOL</sub>  |                            |      | 0.4  | V    | A     |

| 6.2 | Output-voltage high level                         | I <sub>DOL</sub> = -2 mA                      | 7   | V <sub>DOH</sub>  | V <sub>VCC</sub> –<br>0.7V |      |      | V    | A     |

| 6.3 | Leakage current<br>(tri-state)                    | $V_{CS} = V_{VCC}$<br>$0V < V_{DO} < V_{VCC}$ | 7   | I <sub>DO</sub>   | -10                        |      | 10   | μA   | A     |

| 7   | Inhibit Input – Timing                            |                                               |     |                   |                            |      |      |      | •     |

| 7.1 | Delay time from<br>standby to normal<br>operation |                                               |     | t <sub>dINH</sub> |                            |      | 100  | μs   | A     |

\*) Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

Notes: 1. Delay time between rising edge of input signal at pin CS after data transmission and switch on/off output stages to 90% of final level. Device not in standby for t > 1 ms.

2. Delay time between rising/falling edge of input signal at pin PWM and switch on/off output stages to 90% of final level.

3. Difference between switch-on and switch-off delay time of input signal at pin PWM to output stages in PWM mode.

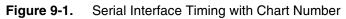

### 9. Serial Interface Timing

| No.  | Parameters                      | Test Conditions          | Pin | Timing Chart No. <sup>(1)</sup> | Symbol                | Min. | Тур. | Max. | Unit | Type* |

|------|---------------------------------|--------------------------|-----|---------------------------------|-----------------------|------|------|------|------|-------|

| 8    | Serial Interface Tim            | ing                      |     |                                 | •                     |      |      | •    |      |       |

| 8.1  | DO enable after CS falling edge | C <sub>DO</sub> = 100 pF | 7   | 1                               | t <sub>ENDO</sub>     |      |      | 200  | ns   | D     |

| 8.2  | DO disable after CS rising edge | C <sub>DO</sub> = 100 pF | 7   | 2                               | t <sub>DISDO</sub>    |      |      | 200  | ns   | D     |

| 8.3  | DO fall time                    | C <sub>DO</sub> = 100 pF | 7   | -                               | t <sub>DOf</sub>      |      |      | 100  | ns   | D     |

| 8.4  | DO rise time                    | C <sub>DO</sub> = 100 pF | 7   | -                               | t <sub>DOr</sub>      |      |      | 100  | ns   | D     |

| 8.5  | DO valid time                   | C <sub>DO</sub> = 100 pF | 7   | 10                              | t <sub>DOVal</sub>    |      |      | 200  | ns   | D     |

| 8.6  | CS setup time                   |                          | 3   | 4                               | t <sub>CSSethl</sub>  | 225  |      |      | ns   | D     |

| 8.7  | CS setup time                   |                          | 3   | 8                               | t <sub>CSSetlh</sub>  | 225  |      |      | ns   | D     |

| 8.8  | CS high time                    |                          | 3   | 9                               | t <sub>CSh</sub>      | 500  |      |      | ns   | D     |

| 8.9  | CLK high time                   |                          | 5   | 5                               | t <sub>CLKh</sub>     | 225  |      |      | ns   | D     |

| 8.10 | CLK low time                    |                          | 5   | 6                               | t <sub>CLKI</sub>     | 225  |      |      | ns   | D     |

| 8.11 | CLK period time                 |                          | 5   | -                               | t <sub>CLKp</sub>     | 500  |      |      | ns   | D     |

| 8.12 | CLK setup time                  |                          | 5   | 7                               | t <sub>CLKSethl</sub> | 225  |      |      | ns   | D     |

| 8.13 | CLK setup time                  |                          | 5   | 3                               | t <sub>CLKSetlh</sub> | 225  |      |      | ns   | D     |

| 8.14 | DI setup time                   |                          | 4   | 11                              | t <sub>Dlset</sub>    | 40   |      |      | ns   | D     |

| 8.15 | DI hold time                    |                          | 4   | 12                              | t <sub>DIHold</sub>   | 40   |      |      | ns   | D     |

\*) Type means: A =100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

Inputs DI, CLK, CS: High level = 0.7  $\times$  V<sub>CC</sub>, low level = 0.3  $\times$  V<sub>CC</sub> Output DO: High level = 0.8  $\times$  V<sub>CC</sub>, low level = 0.2  $\times$  V<sub>CC</sub>

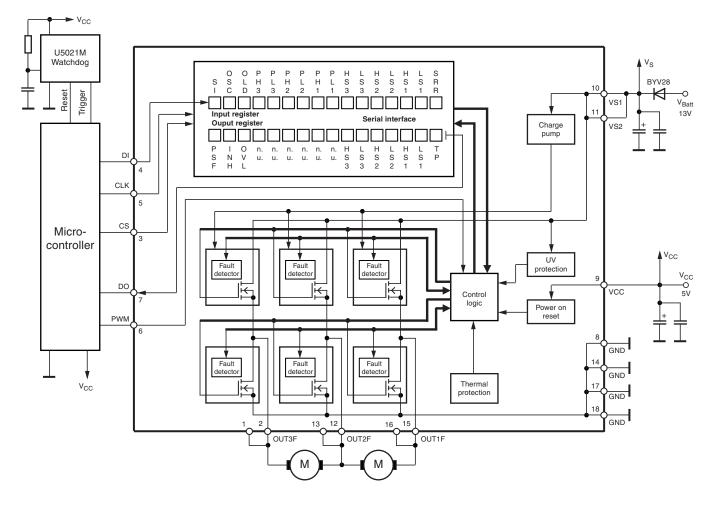

### **10. Application Circuit**

#### Figure 10-1. Application Circuit

### 10.1 Application Notes

- Connect the blocking capacitors at  $V_{\text{VCC}}$  and  $V_{\text{VS}}$  as close as possible to the power supply and GND pins.

- Recommended value for capacitors at V<sub>VS</sub>:

- Electrolytic capacitor C > 22  $\mu$ F in parallel with a ceramic capacitor C = 100 nF. The value for the electrolytic capacitor depends on external loads, conducted interferences, and the reverse conducting current I<sub>Out1.2.3</sub>.

- Recommended value for capacitors at  $V_{VCC}$ :

- Electrolytic capacitor C > 10  $\mu$ F in parallel with a ceramic capacitor C = 100 nF.

- To reduce thermal resistance, place cooling areas on the PCB as close as possible to the GND pins and to the die pad.

### **11. Ordering Information**

| Extended Type Number | Package                   | Remarks                   |

|----------------------|---------------------------|---------------------------|

| ATA6831-PIQW         | QFN18, 4 mm $\times$ 4 mm | Taped and reeled, Pb-free |

| ATA6831-PIPW         | QFN18, 4 mm $\times$ 4 mm | Taped and reeled, Pb-free |

| ATA6831-PISW         | QFN18, 4 mm $\times$ 4 mm | Tubes, Pb-free            |

### 12. Package Information

Drawing-No.: 6.543-5133.01-4 Issue: 1; 26.04.07

technical drawings according to DIN specifications

## 13. Revision History

Please note that the following page numbers referred to in this section refer to the specific revision mentioned, not to this document.

| Revision No.     | History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 4908G-AUTO-07/10 | <ul> <li>Section 3.3 Open-load Detection on page 6 changed</li> <li>Section 8 "Electrical Characteristics" numbers 4.12 and 4.13 on pages 10 to 11 changed.</li> <li>Section 8 "Electrical Characteristics" numbers 4.12a, 4.13a and 4.14 on pages 10 to 11 added.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| 4908F-AUTO-02/10 | Section 5 "Thermal Resistance" on page 8 changed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| 4908E-AUTO-06/07 | <ul> <li>Put datasheet into the newest template</li> <li>Package drawing changed</li> <li>Block diagram changed</li> <li>Pin description table changed</li> <li>El. Char. table: rows 1.6, 4.12, 4.13 and 4.21 changed</li> <li>El. Char. table row 4.14 deleted</li> <li>Application circuit drawing changed</li> </ul>                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| 4908D-AUTO-09/06 | <ul> <li>Features on page 1 changed</li> <li>Figure 1-1 "Block Diagram" on page 2 changed</li> <li>Section 2 "Pin Configuration" on pages 2 to 3 changed</li> <li>Section 4 "Absolute Maximum Ratings" on page 8 changed</li> <li>Section 8 "Electrical Characteristics" on pages 9 to 11 changed</li> <li>Section 9 "Serial Interface Timing" on page 12 changed</li> <li>Figure 10-1 "Application Circuit" on page 14 changed</li> <li>Section 11 "Ordering Information" on page 15 changed</li> <li>Section 12 "Package Information" on page 15 changed</li> </ul>                                                                                                                     |  |  |  |  |  |

| 4908C-AUTO-08/06 | <ul> <li>Title on page 1 changed</li> <li>Features on page 1 changed</li> <li>Figure 1-1 "Block Diagram" on page 1 changed</li> <li>Figure 2-1 "Pinning" on page 3 changed</li> <li>Table 2-1 "Pin Description" on page 3 changed</li> <li>Table 3-2 "Output Data Protocol" on page 5 changed</li> <li>Section 3.7 "PWM Mode" on page 7 added</li> <li>Section 4 "Absolute Maximum Ratings" on page 8 changed</li> <li>Section 8 "Electrical Characteristics" on page 9 to 12 changed</li> <li>Figure 10-1 "Application Circuit" on page 14 changed</li> <li>Section 11 "Ordering Information" on page 15 changed</li> <li>Section 12 "Package Information" on page 15 changed</li> </ul> |  |  |  |  |  |

#### Headquarters

Atmel Corporation 2325 Orchard Parkway San Jose, CA 95131 USA Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

#### International

Atmel Asia Unit 1-5 & 16, 19/F BEA Tower, Millennium City 5 418 Kwun Tong Road Kwun Tong, Kowloon Hong Kong Tel: (852) 2245-6100 Fax: (852) 2722-1369 Atmel Europe Le Krebs 8, Rue Jean-Pierre Timbaud BP 309 78054 Saint-Quentin-en-Yvelines Cedex France Tel: (33) 1-30-60-70-00 Fax: (33) 1-30-60-71-11

#### Atmel Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

#### **Product Contact**

Web Site www.atmel.com *Technical Support* auto\_drivers@atmel.com Sales Contact www.atmel.com/contacts

Literature Requests www.atmel.com/literature

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL'S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNTIVE, SPECIAL OR INCIDEN-TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel's products are not intended, or warranted for use as components in applications intended to support or sustain life.

© 2010 Atmel Corporation. All rights reserved. Atmel<sup>®</sup>, logo and combinations thereof, and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.