# 16-bit Proprietary Microcontroller

# F<sup>2</sup>MC-16LX MB90820 Series

# MB90822/F822/F823/V820

#### ■ DESCRIPTION

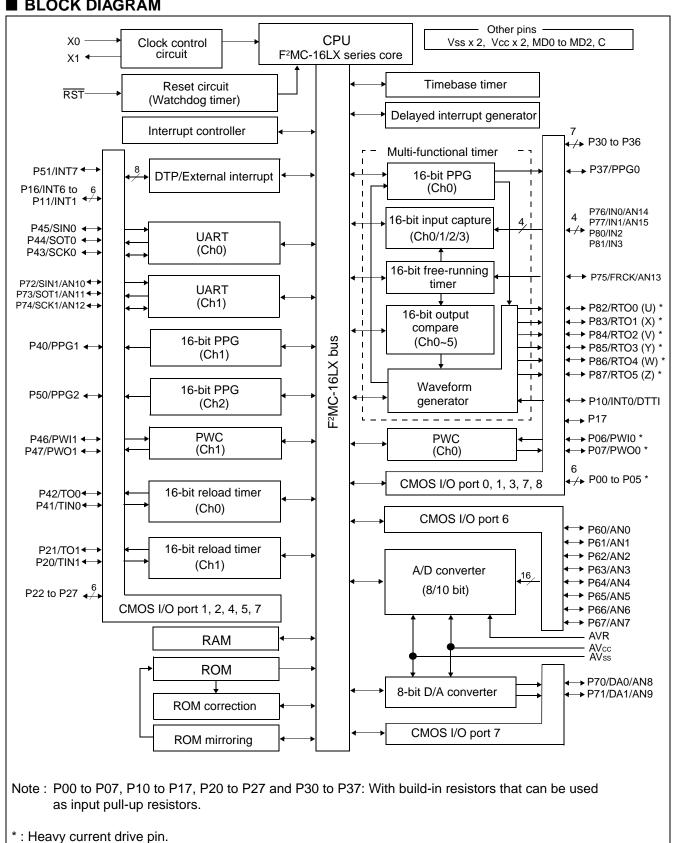

The MB90820 series is a line of general-purpose, Fujitsu 16-bit microcontrollers designed for process control applications which require high-speed real-time processing, such as consumer products.

While inheriting the AT architecture of the F²MC\* family, the instruction set for the F²MC-16LX CPU core of the MB90820 series incorporates additional instructions for high-level languages, supports extended addressing modes, and contains enhanced multiplication and division instructions as well as a substantial collection of improved bit manipulation instructions. In addition, the MB90820 series has an on-chip 32-bit accumulator which enables processing of long-word data.

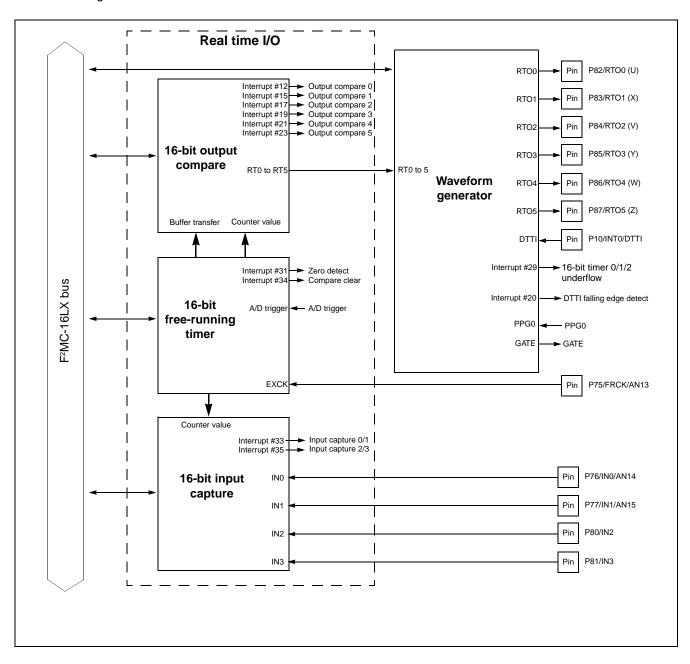

The peripheral resources integrated in the MB90820 series include: an 8/10-bit A/D converter, 8-bit D/A converters, UARTs (SCI) 0, 1, multi-functional timer (16-bit free-running timer, input capture units (ICUs) 0 to 3, output compare units (OCUs) 0 to 5, 16-bit PPG timer 0, waveform generator), 16-bit PPG timer 1, 2, PWC 0, 1, 16-bit reload timer 0, 1 and DTP/external interrupt.

\*: F2MC stands for FUJITSU Flexible Microcontroller, a registered trademark of FUJITSU LIMITED.

#### **■ FEATURES**

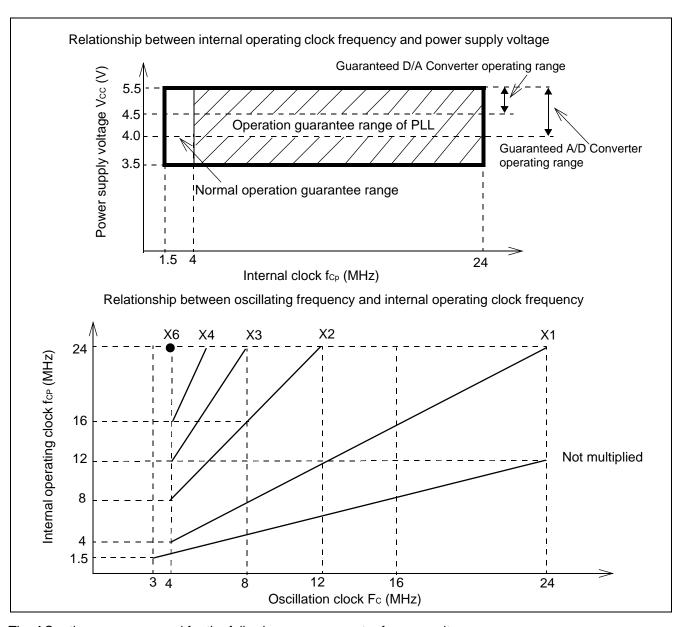

- Minimum execution time of instruction: 42 ns / 4 MHz oscillation (uses PLL clock multiplication) maximum multiplier = 6

- Maximum memory space 16M bytes Linear/bank access

(Continued)

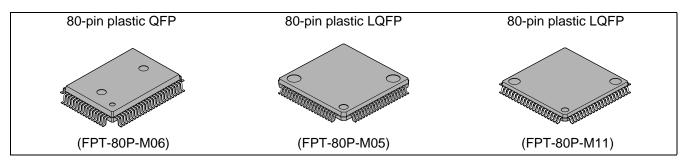

#### ■ PACKAGES

#### (Continued)

• Instruction set optimized for controller applications

Supported data types: bit, byte, word, and long-word types

Standard addressing modes: 23 types

32-bit accumulator enhancing high-precision operations

Enhanced multiplication/division and RETI instructions

• Enhanced high level language (C) and multi-tasking support instructions

Use of a system stack pointer

Symmetrical instruction set and barrel shift instructions

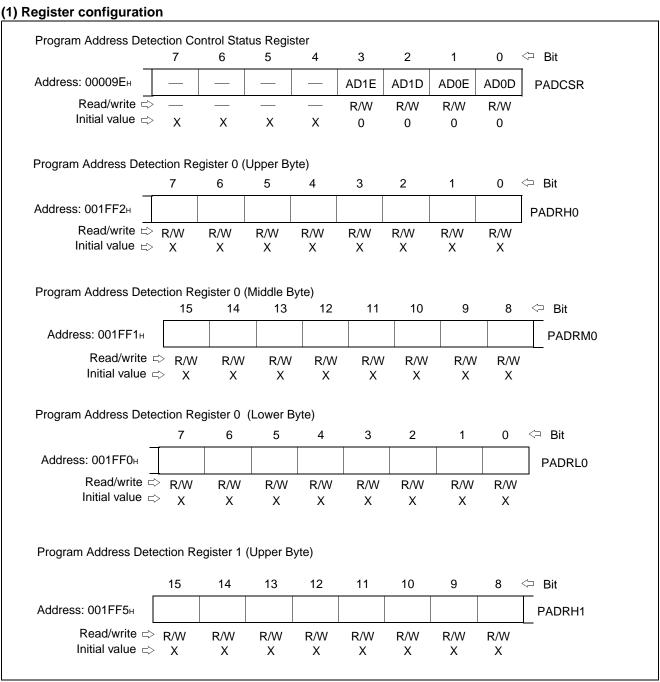

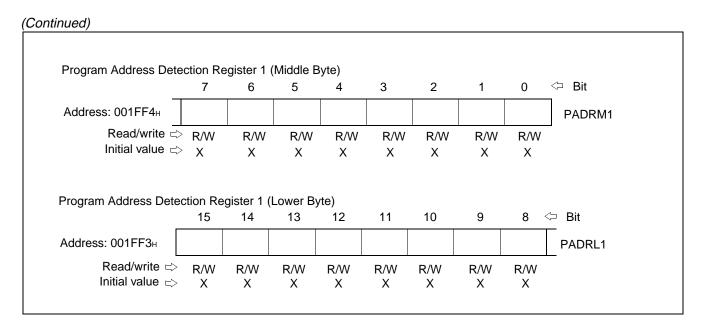

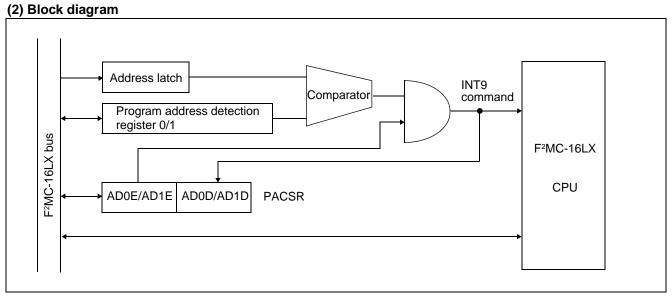

- Program patch function (for two address pointers)

- Increased execution speed: 4-byte instruction queue

- Powerful interrupt function

Up to eight priority levels programmable

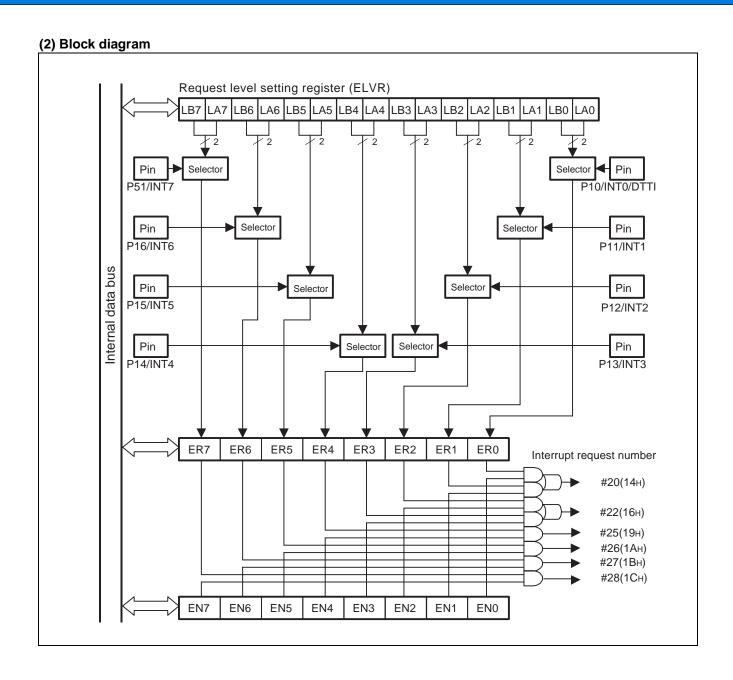

External interrupt inputs: 8 lines

· Automatic data transmission function independent of CPU operation

Up to 16 channels for the extended intelligent I/O service

DTP request inputs: 8 lines

Internal ROM

FLASH: 64/128K bytes with flash security

MASKROM: 64K bytes

Internal RAM EVA: 16K bytes FLASH: 4K bytes MASKROM: 4K bytes

General-purpose ports

Up to 66 channels (pull-up resistor settable input for : 32 channels)

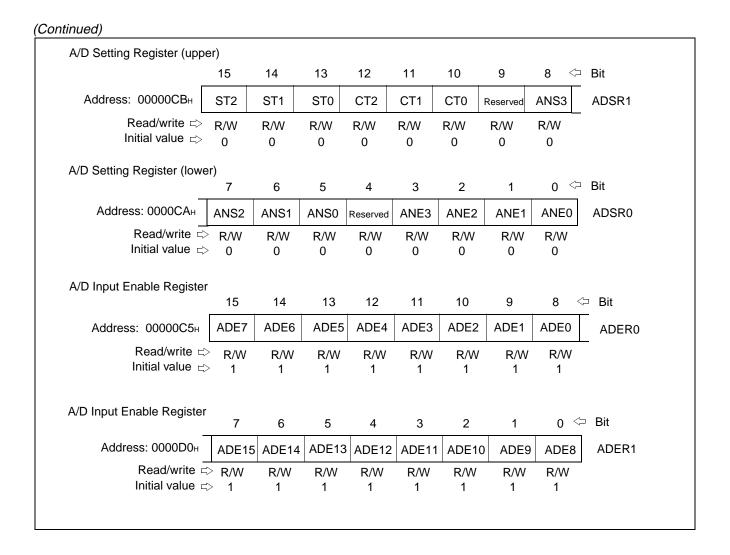

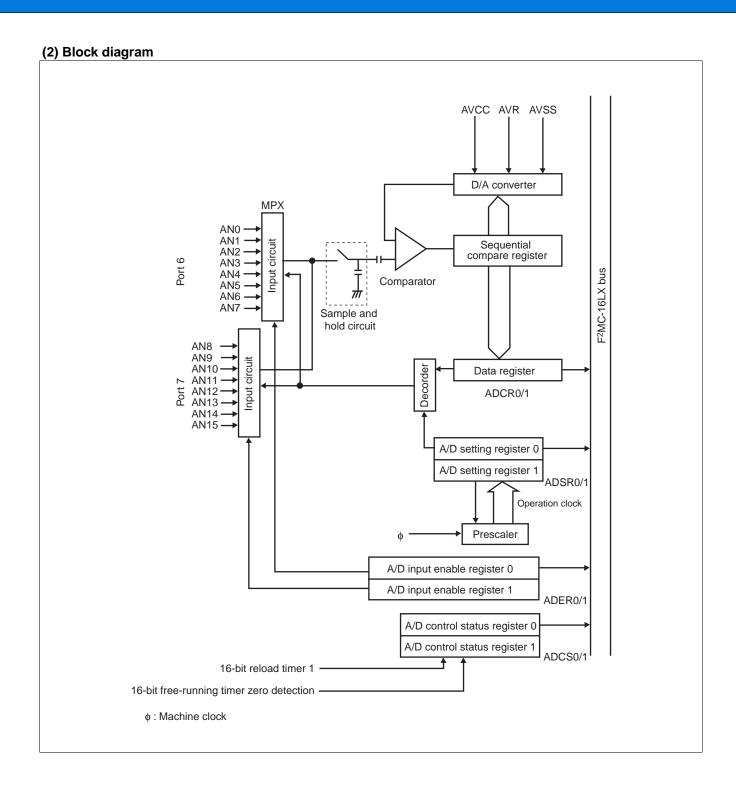

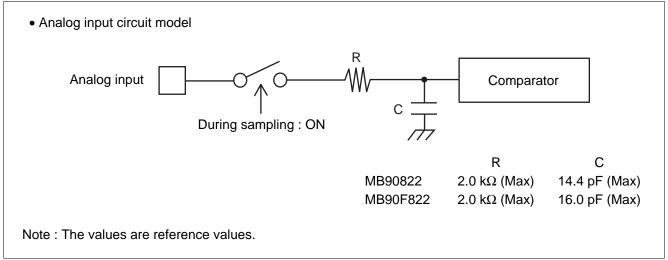

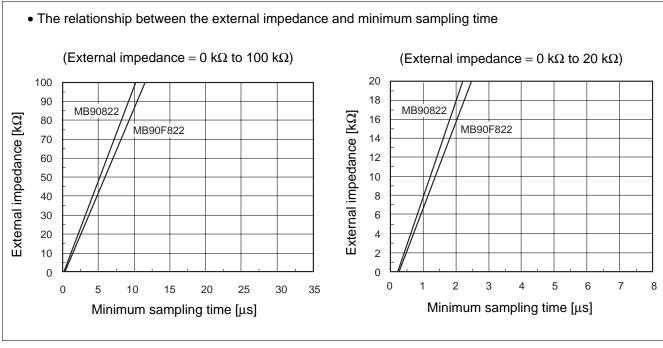

• A/D Converter (RC): 16 channels

8/10-bit resolution selectable

Conversion time: Min 3 µs at 24 MHz operating clock (including sampling time)

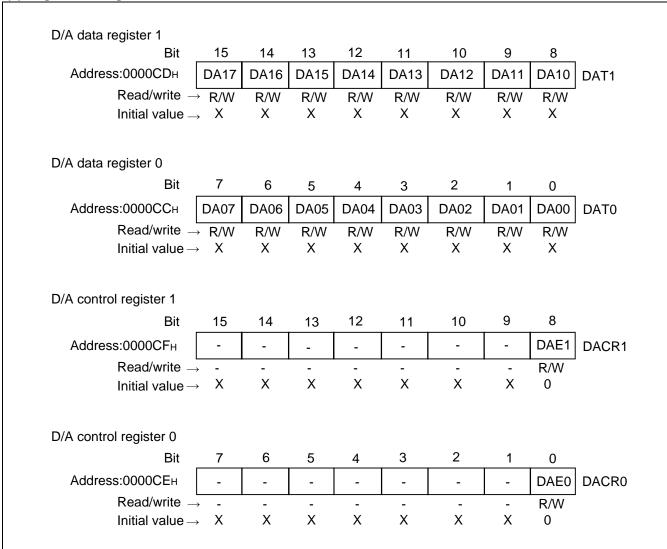

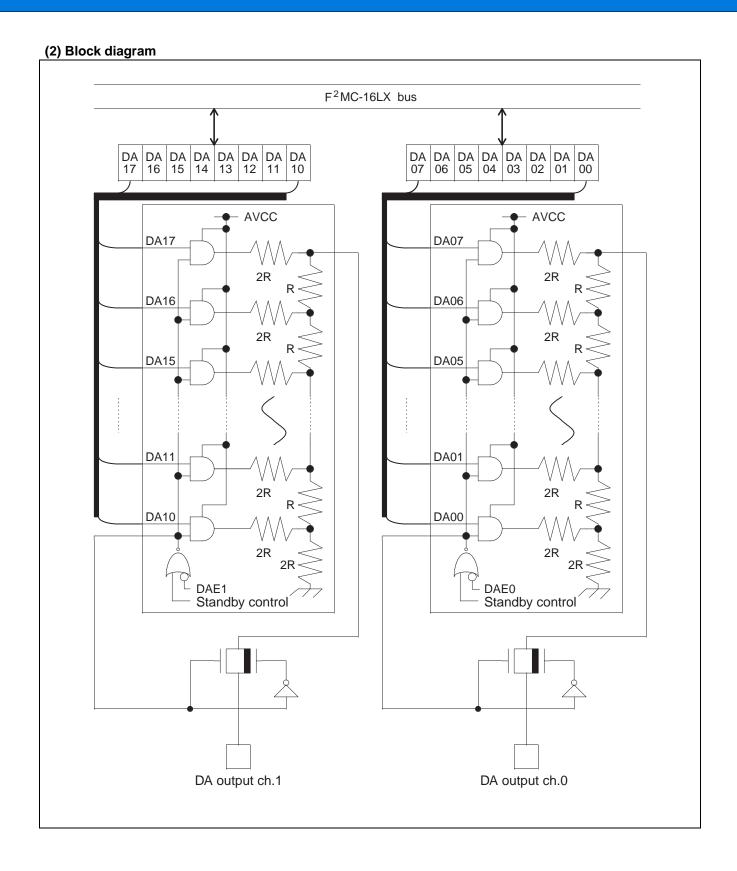

- 8-bit D/A Converter: 2 channels

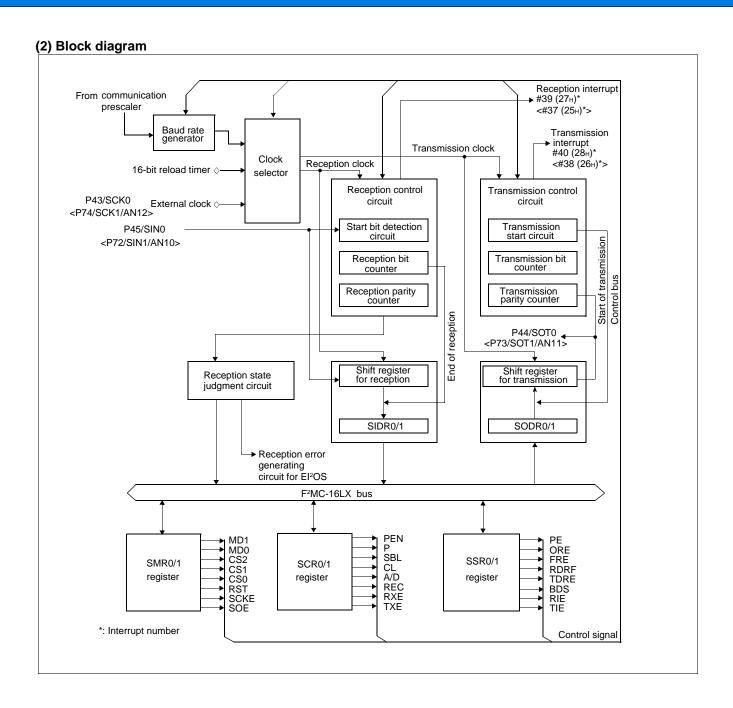

- UART: 2 channels

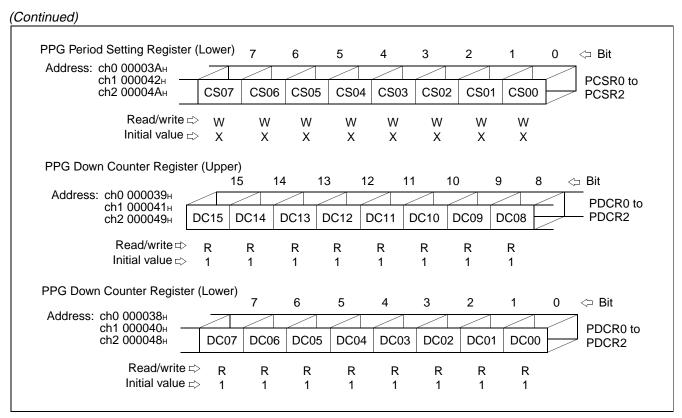

- 16-bit PPG: 3 channels

Mode switching function provided (PWM mode or one-shot mode)

Channel 0 can be worked with multi-functional timer or independently

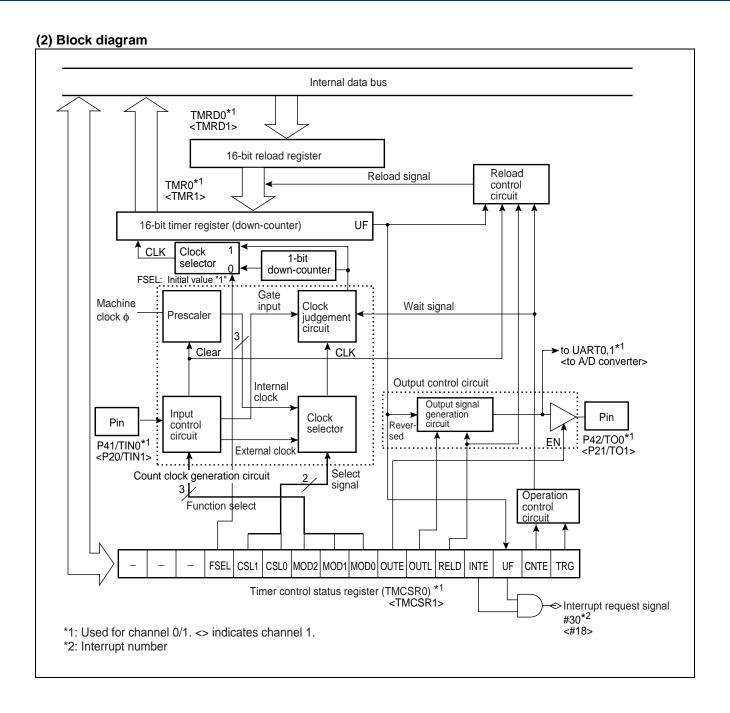

- 16-bit reload timer: 2 channels

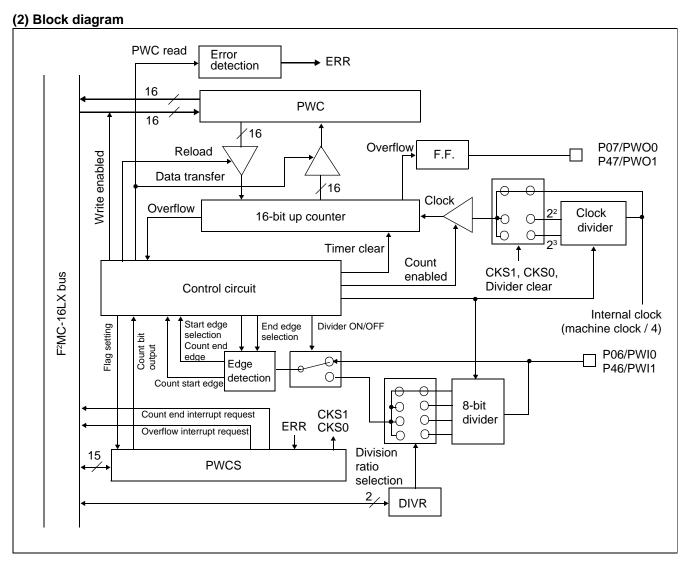

- 16-bit PWC timer: 2 channels

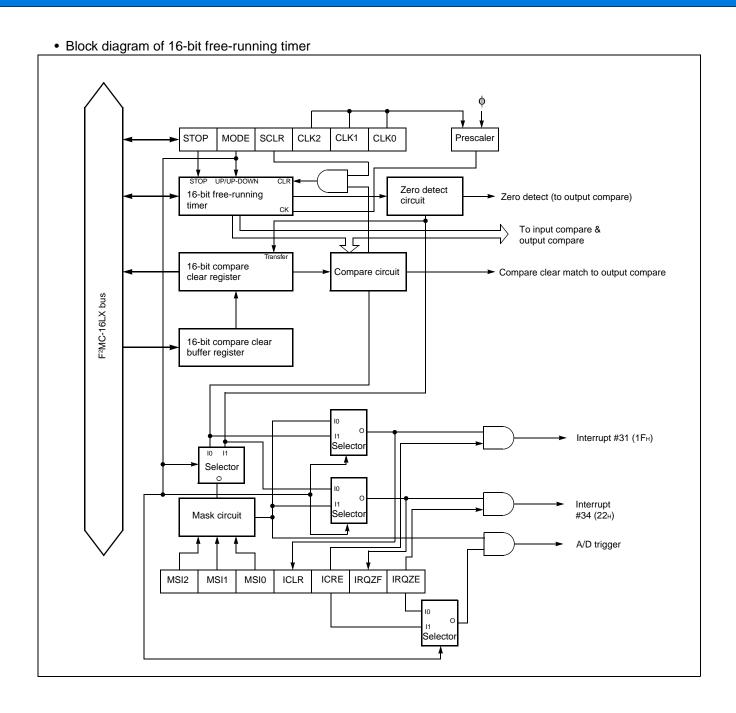

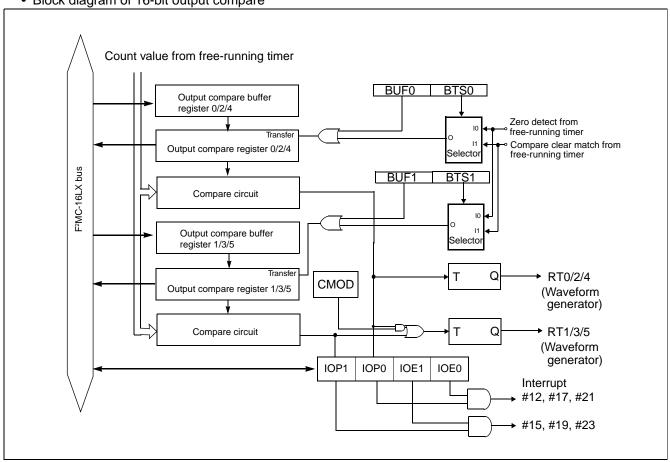

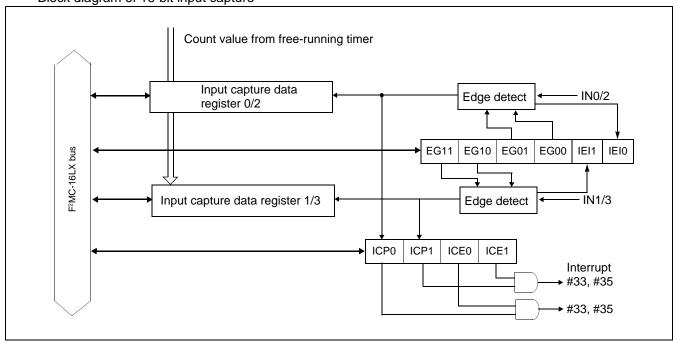

- Multi-functional timer

Input capture: 4 channels

Output compare with selectable buffer: 6 channels

Free-running timer with up or up-down mode selection and selectable buffer: 1 channel

16-bit PPG: 1 channel

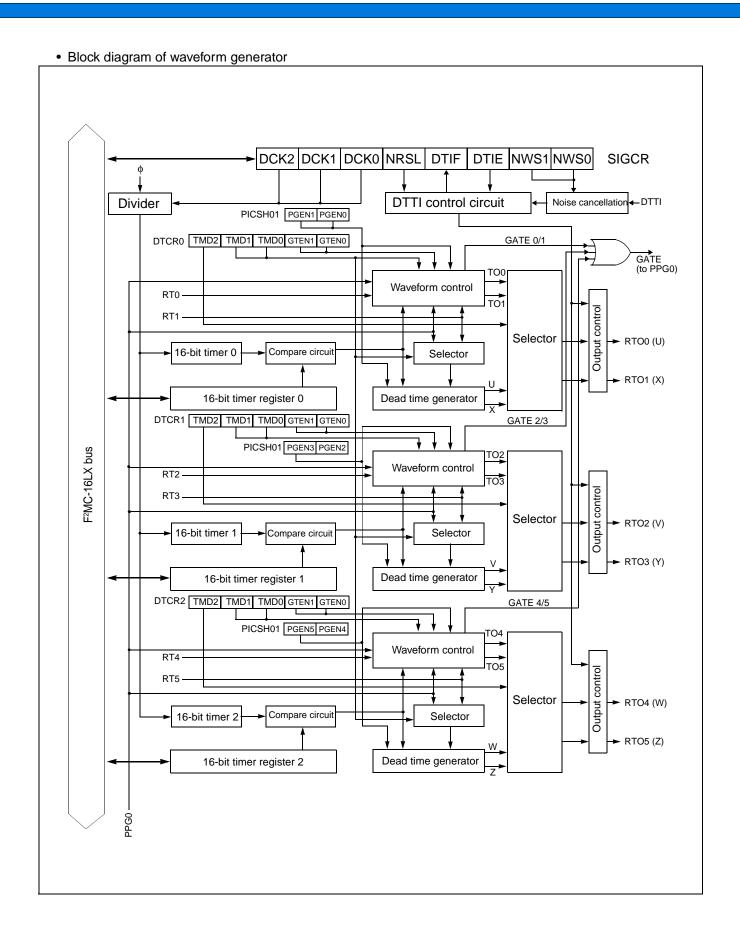

Waveform generator: (16-bit timer: 3 channels, 3-phase waveform or dead time)

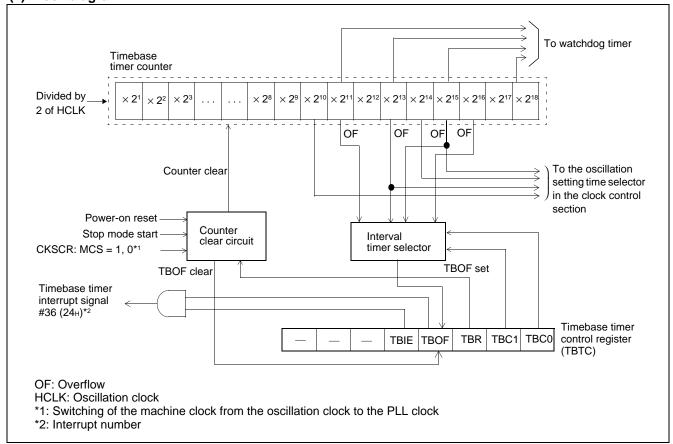

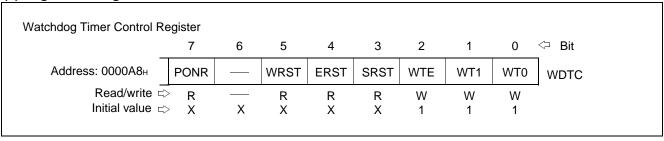

- Timebase counter/watchdog timer: 18-bit

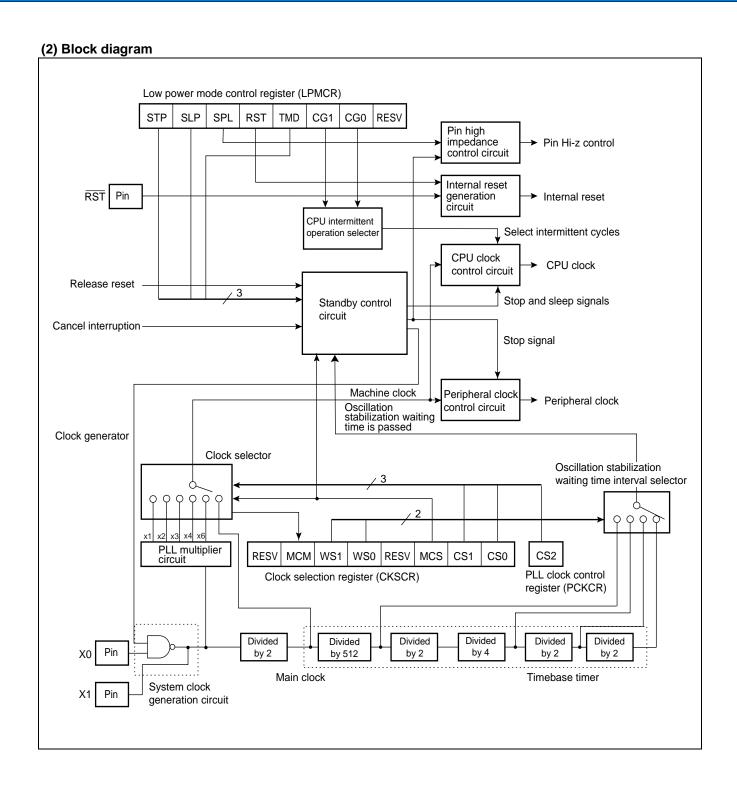

- Low-power consumption mode :

Sleep mode

Stop mode

CPU intermittent operation mode

### (Continued)

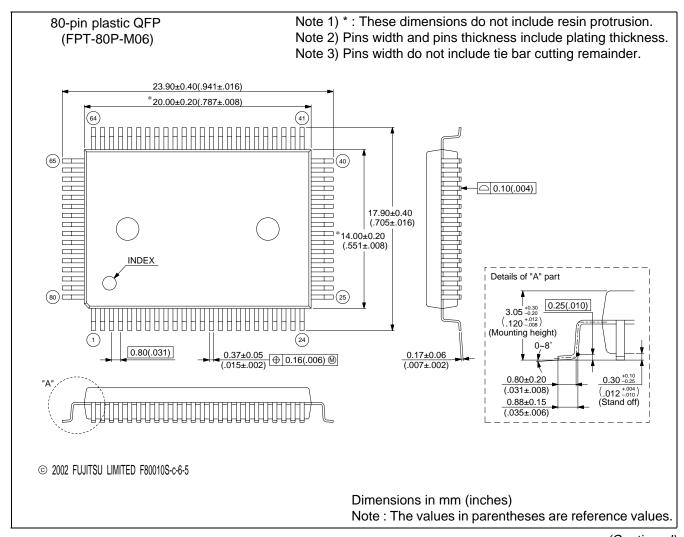

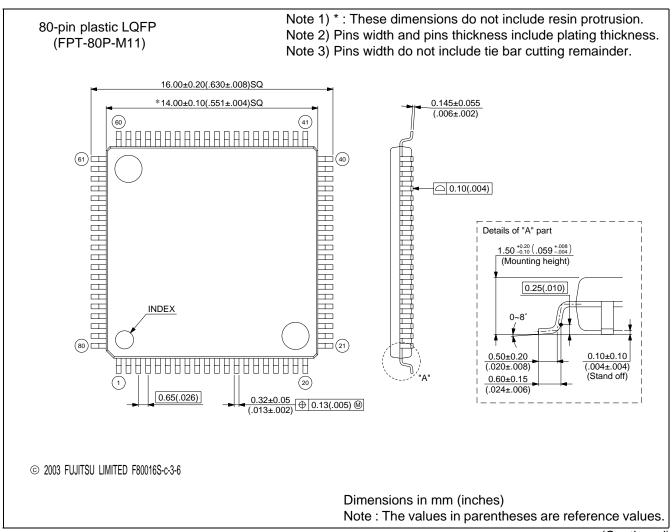

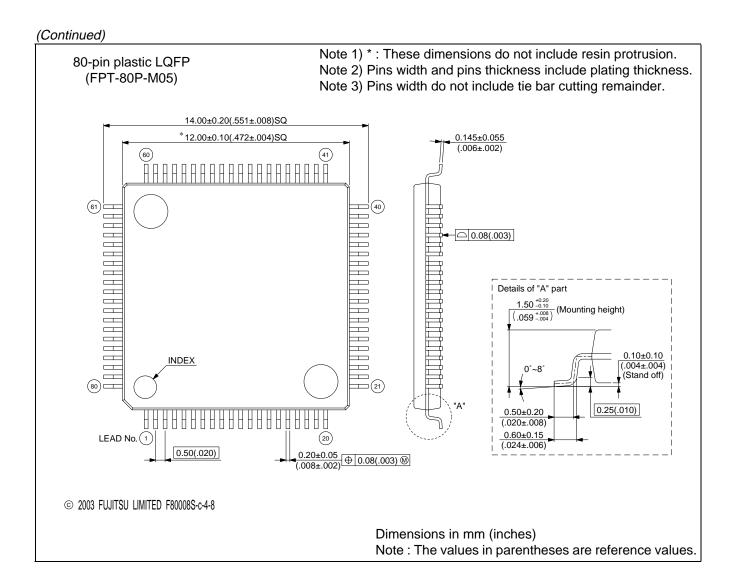

• Package :

LQFP-80 (FPT-80P-M05 : 0.50 mm pitch) LQFP-80 (FPT-80P-M11 : 0.65 mm pitch) QFP-80 (FPT-80P-M06 : 0.80 mm pitch)

• CMOS technology

### ■ PRODUCT LINEUP

| Part number                                               | MB90V820                                                                                                                                                                                                                                                           | MB90F822                                                                                  | MB90F823            | MB90822                                                                 |  |  |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|---------------------|-------------------------------------------------------------------------|--|--|

| Classification                                            | Development /evaluation product                                                                                                                                                                                                                                    | Mass-produced products (Flash ROM with flash security)  Mass-produced products (Mask ROM) |                     |                                                                         |  |  |

| ROM size                                                  | _                                                                                                                                                                                                                                                                  | 64K bytes                                                                                 | 128K bytes          | 64K bytes                                                               |  |  |

| RAM size                                                  | 16K bytes                                                                                                                                                                                                                                                          |                                                                                           | 4K b                | ytes                                                                    |  |  |

| CPU function                                              | Number of instruction: 351 Minimum execution time: 42 Addressing mode: 23 Data bit length: 1, 8, 16 bits Maximum memory space: 16                                                                                                                                  | ·                                                                                         | x 6)                |                                                                         |  |  |

| I/O port                                                  | I/O port (CMOS): 66                                                                                                                                                                                                                                                |                                                                                           |                     |                                                                         |  |  |

|                                                           | Pulse width counter timer: 2 of                                                                                                                                                                                                                                    | channels                                                                                  |                     |                                                                         |  |  |

| PWC                                                       |                                                                                                                                                                                                                                                                    | g function (H puls                                                                        | se width, L pulse v | cks) vidth, rising edge to falling edge edge period and falling edge to |  |  |

| UART                                                      | UART: 2 channels With full-duplex double buffer Clock asynchronized or clock selected and used. Transmission can be one-to-o munication).                                                                                                                          | synchronized tra                                                                          |                     | start and stop bits) can be or one-to-n (master-slave com-              |  |  |

| 16-bit reload<br>timer                                    | Reload timer : 2 channels<br>Reload mode, single-shot mo                                                                                                                                                                                                           | de or event cour                                                                          | nt mode selectabl   | e                                                                       |  |  |

| 16-bit PPG                                                | PPG timer : 3 channels                                                                                                                                                                                                                                             |                                                                                           |                     |                                                                         |  |  |

| timer                                                     | PWM mode or single-shot mo<br>Channel 0 can be worked with                                                                                                                                                                                                         |                                                                                           | I timer or indeper  | ndently.                                                                |  |  |

| Multi-functional<br>timer<br>(for AC/DC<br>motor control) | 16-bit free-running timer with up or up-down mode selection and buffer : 1 channel 16-bit output compare : 6 channels 16-bit input capture : 4 channels 16-bit PPG timer : 1 channel Waveform generator (16-bit timer : 3 channels, 3-phase waveform or dead time) |                                                                                           |                     |                                                                         |  |  |

| 8/10-bit A/D<br>converter                                 | 8/10-bit resolution (16 channe<br>Conversion time : Min 3 μs (2                                                                                                                                                                                                    | ,                                                                                         | lock, including sa  | ampling time)                                                           |  |  |

| 8-bit D/A<br>converter                                    | 8/10-bit resolution (2 channels)                                                                                                                                                                                                                                   |                                                                                           |                     |                                                                         |  |  |

| DTP/External interrupt                                    | 8 independent channels<br>Interrupt factors : Rising edge, falling edge, "L" level or "H" level                                                                                                                                                                    |                                                                                           |                     |                                                                         |  |  |

| Low-power consumption                                     | Stop mode / Sleep mode / CP                                                                                                                                                                                                                                        | U intermittent op                                                                         | peration mode       |                                                                         |  |  |

#### (Continued)

| Part number                          | MB90V820         | MB90F822                                                                                                                                                                               | MB90F823 | MB90822 |  |

|--------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------|--|

| Package                              | PGA-299          | LQFP-80 (FPT-80P-M05 : 0.50 mm pitch)<br>LQFP-80 (FPT-80P-M11 : 0.65 mm pitch)<br>QFP-80 (FPT-80P-M06 : 0.80 mm pitch)                                                                 |          |         |  |

| Power supply voltage for operation*1 | 4.5 V to 5.5 V*1 | 3.5 V to 5.5 V : Normal operation when A/D converter and D/A converter are not used 4.0 V to 5.5 V : Normal operation when D/A converter is not used 4.5 V to 5.5 V : Normal operation |          |         |  |

| Process                              |                  | CMOS                                                                                                                                                                                   |          |         |  |

| Emulator power supply*2              | Included         | _                                                                                                                                                                                      |          |         |  |

<sup>\*1 :</sup> Assurance for the MB90V820 is operating temperature 0 °C to +25 °C.

#### ■ PACKAGE AND CORRESPONDING PRODUCTS

| Package     | MB90V820 | MB90F822 | MB90F823 | MB90822 |

|-------------|----------|----------|----------|---------|

| PGA299      | 0        | X        | Х        | X       |

| FPT-80P-M05 | Х        | 0        | 0        | 0       |

| FPT-80P-M11 | Х        | 0        | 0        | 0       |

| FPT-80P-M06 | Х        | 0        | 0        | 0       |

: AvailableX : Not available

Note: For more information about each package, see "■ PACKAGE DIMENSIONS".

<sup>\*2:</sup> It is setting of Jumper switch (TOOL VCC) when emulator (MB2147-01) is used. Please refer to the MB2147-01 or MB2147-20 hardware manual (3.3 Emulator-dedicated Power Supply switching) about details.

#### **■ DIFFERENCES AMONG PRODUCTS**

#### **Memory Size**

In evaluation with an evaluation product, note the difference between the evaluation product and the product actually used. The following items must be taken into consideration.

- The MB90V820 does not have an internal ROM, however, operations equivalent to chips with an internal ROM

can be evaluated by using a dedicated development tool, enabling selection of ROM size by settings of the

development tool.

- In the MB90V820, images from FF8000<sub>H</sub> to FFFFFF<sub>H</sub> are mapped to bank 00, and FE0000<sub>H</sub> to FF7FFF<sub>H</sub> are mapped to bank FE and bank FF only. (This setting can be changed by configuring the development tool.)

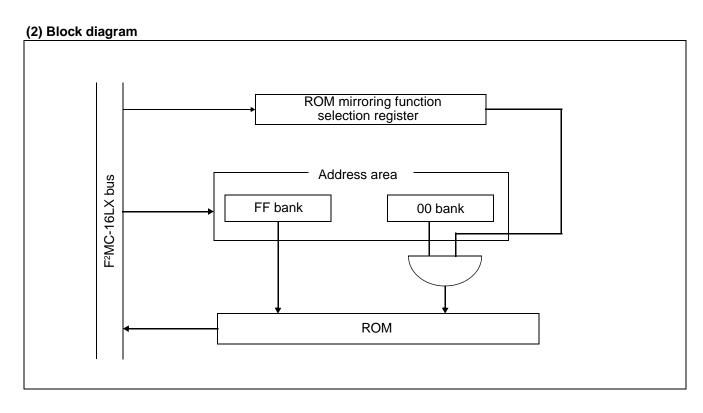

- In the MB90822/F822/F823, images from FF8000<sub>H</sub> to FFFFFF<sub>H</sub> are mapped to bank 00, and FF0000<sub>H</sub> to FF7FFF<sub>H</sub> are mapped to bank FF only. In the MB90F823, images from FF8000<sub>H</sub> to FFFFFF<sub>H</sub> are mapped to bank 00, and FE0000<sub>H</sub> to FF7FFF<sub>H</sub> are mapped to bank FE and bank FF only.

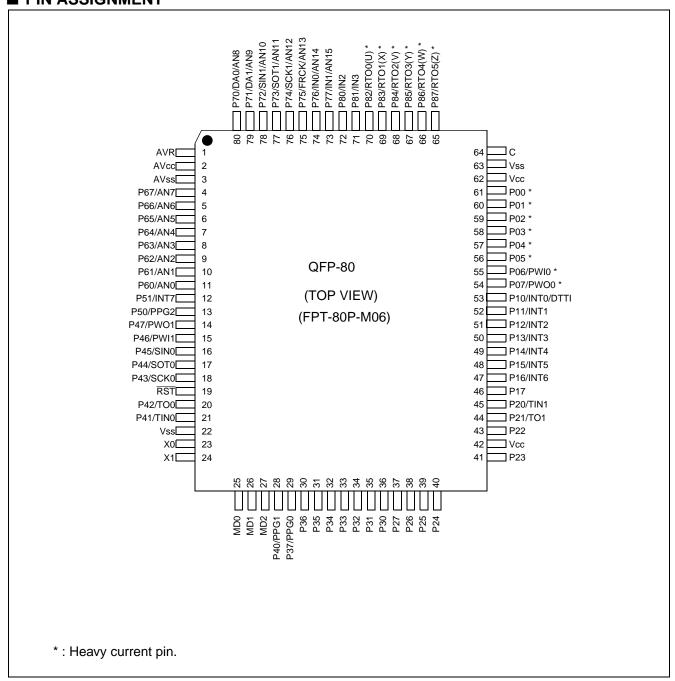

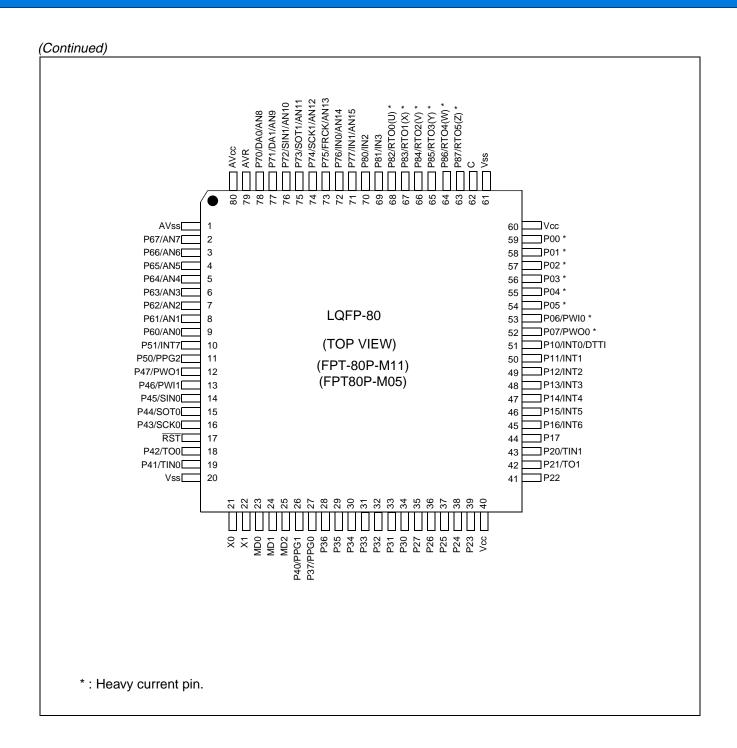

#### **■ PIN ASSIGNMENT**

### **■ PIN DESCRIPTION**

| Pin             | no.             |                 | I/O     | Pin status                 |                                                                                                                      |                            |

|-----------------|-----------------|-----------------|---------|----------------------------|----------------------------------------------------------------------------------------------------------------------|----------------------------|

| LQFP *1         | QFP *2          | Pin name        | circuit | during<br>reset            | Function                                                                                                             |                            |

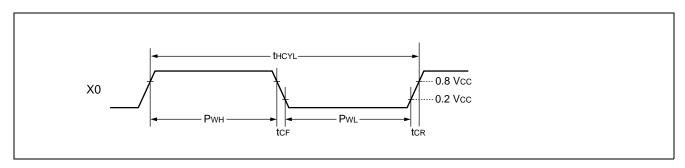

| 21, 22          | 23, 24          | X0,X1           | Α       | Oscillating                | Oscillation input pins.                                                                                              |                            |

| 17              | 19              | RST             | В       | Reset input                | External reset input pin.                                                                                            |                            |

| 59 to 54        | 61 to 56        | P00 to P05      | С       |                            | General-purpose I/O ports.                                                                                           |                            |

| 53              | 55              | P06             | С       |                            | General-purpose I/O ports.                                                                                           |                            |

| 33              | 3               | PWI0            | O       |                            | PWC0 signal input pin.                                                                                               |                            |

| 52              | 54              | P07             | С       |                            | General-purpose I/O ports.                                                                                           |                            |

| 32              | 5               | PWO0            | C       |                            | PWC0 signal output pin.                                                                                              |                            |

|                 |                 | P10             |         |                            | General-purpose I/O ports.                                                                                           |                            |

| 51              | 53              | INT0            | D       |                            | Can be used as interrupt request input channel 0. Input is enabled when 1 is set in EN0 in standby mode.             |                            |

|                 |                 | DTTI            |         |                            | RTO0 to 5 pins for fixed-level input. This function is enabled when the waveform generator specifies its input bits. |                            |

|                 |                 | P11 to P16      |         |                            | General-purpose I/O ports.                                                                                           |                            |

| 50 to 45        | 52 to 47        | INT1 to<br>INT6 | D       |                            | Can be used as interrupt request input channel 1 to 6. Input is enabled when 1 is set in EN1 to EN6 in standby mode. |                            |

| 44              | 46              | P17             | D       | -                          | General-purpose I/O ports.                                                                                           |                            |

| 43              | 45              | P20             | P20 P   |                            | D Port input                                                                                                         | General-purpose I/O ports. |

| 43              | 45              | TIN1            | U       |                            | External clock input pin for reload timer1.                                                                          |                            |

| 42              | 44              | P21 D           |         | General-purpose I/O ports. |                                                                                                                      |                            |

| 42              | 44              | TO1             | D       |                            | Event output pin for reload timer1.                                                                                  |                            |

| 41,<br>39 to 35 | 43,<br>41 to 37 | P22 to P27      | D       |                            | General-purpose I/O ports.                                                                                           |                            |

| 34 to 28        | 36 to 30        | P30 to P36      | Е       |                            | General-purpose I/O ports.                                                                                           |                            |

|                 |                 | P37             |         |                            | General-purpose I/O ports.                                                                                           |                            |

| 27              | 29              | PPG0            | E       |                            | Output pins for PPG channel 0. This function is enabled when output of PPG channel 0 is specified.                   |                            |

|                 |                 | P40             |         |                            | General-purpose I/O ports.                                                                                           |                            |

| 26              | 28              | PPG1            | F       |                            | Output pins for PPG channel 1. This function is enabled when output of PPG channel 1 is specified.                   |                            |

| 10              | 21              | P41             | F       |                            | General-purpose I/O ports.                                                                                           |                            |

| 19              | 21              | TIN0            | Г       |                            | External clock input pin for reload timer0.                                                                          |                            |

| 18              | 20              | P42             | F       |                            | General-purpose I/O ports.                                                                                           |                            |

| 10              | 20              | TO0             | Г       |                            | Event output pin for reload timer0.                                                                                  |                            |

| Pin     | no.     |            | I/O      | Pin status                 |                                                                                                                                                                                                                               |                         |  |                            |

|---------|---------|------------|----------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--|----------------------------|

| LQFP *1 | QFP *2  | Pin name   | circuit  | during<br>reset            | Function                                                                                                                                                                                                                      |                         |  |                            |

|         |         | P43        |          |                            | General-purpose I/O ports.                                                                                                                                                                                                    |                         |  |                            |

| 16      | 18      | SCK0       | F        |                            | Serial clock I/O pin for UART channel 0. This function is enabled when clock output of UART channel 0 is specified.                                                                                                           |                         |  |                            |

|         |         | P44        |          |                            | General-purpose I/O ports.                                                                                                                                                                                                    |                         |  |                            |

| 15      | 17      | SOT0       | F        |                            | Serial data output pin for UART channel 0. This function is enabled when data output of UART channel 0 is specified.                                                                                                          |                         |  |                            |

|         |         | P45        | <u> </u> |                            | General-purpose I/O ports.                                                                                                                                                                                                    |                         |  |                            |

| 14      | 16      | SIN0       | G        | Port Input                 | Serial data input pin for UART channel 0. While UART channel 0 is operating for input, the input of this pin is used as required. This pin must not be used for any other input.  CMOS input can be selected by user program. |                         |  |                            |

| 40      | 45      | P46        | F<br>F   | F                          | General-purpose I/O ports.                                                                                                                                                                                                    |                         |  |                            |

| 13      | 15      | PWI1       |          |                            | PWC1 signal input pin.                                                                                                                                                                                                        |                         |  |                            |

| 12      | 14      | P47        |          | F                          | E                                                                                                                                                                                                                             | E                       |  | General-purpose I/O ports. |

| 12      | 14      | PWO1       |          |                            |                                                                                                                                                                                                                               | PWC1 signal output pin. |  |                            |

|         |         | P50        |          | General-purpose I/O ports. |                                                                                                                                                                                                                               |                         |  |                            |

| 11      | 13      | PPG2       | F        |                            | Output pins for PPG channel 2. This function is enabled when output of PPG channel 2 is specified.                                                                                                                            |                         |  |                            |

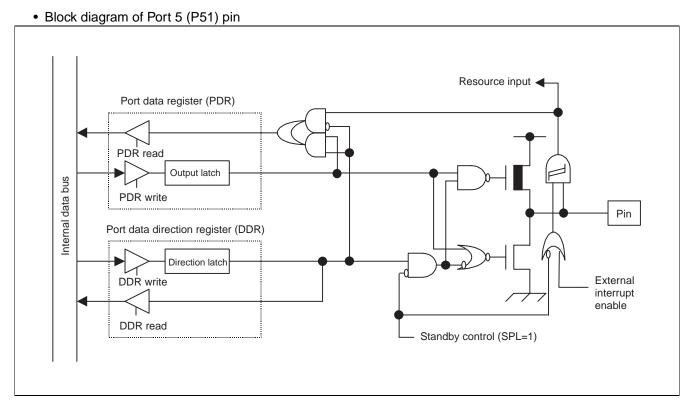

|         |         | P51        |          |                            | General-purpose I/O ports.                                                                                                                                                                                                    |                         |  |                            |

| 10      | 12      | INT7       | F        |                            | Usable as interrupt request input channel 7. Input is enabled when 1 is set in EN7 in standby mode.                                                                                                                           |                         |  |                            |

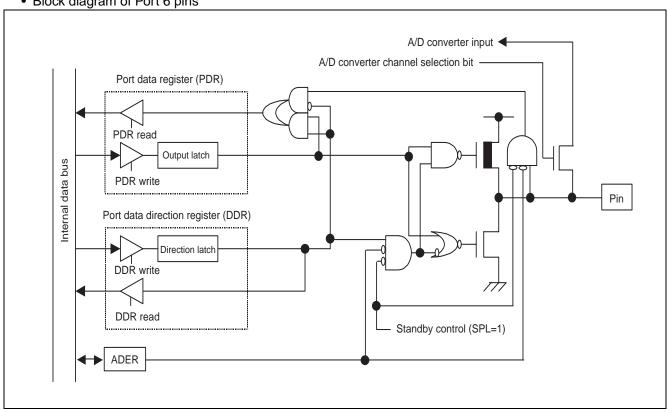

|         |         | P60 to P67 |          |                            | General-purpose I/O ports.                                                                                                                                                                                                    |                         |  |                            |

| 9 to 2  | 11 to 4 | AN0 to AN7 | Н        |                            | A/D converter analog input pins. This function is enabled when the analog input is specified (ADER0).                                                                                                                         |                         |  |                            |

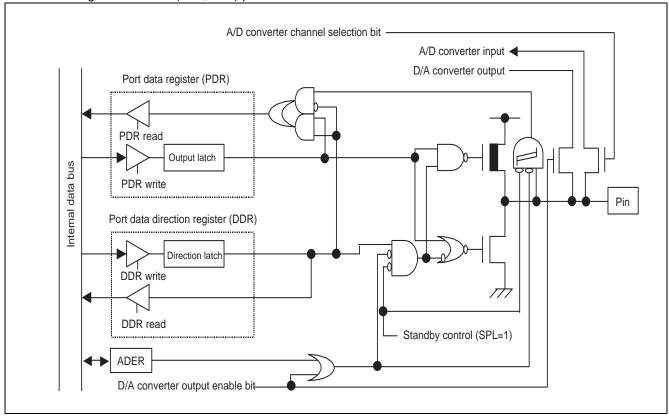

|         |         | P70, P71   |          | Analog                     | General-purpose I/O ports.                                                                                                                                                                                                    |                         |  |                            |

| 78, 77  | 80, 79  | DA0, DA1   | 1        | input                      | D/A converter analog output pins. This function is enabled when D/A converter is specified.                                                                                                                                   |                         |  |                            |

|         |         | AN8, AN9   |          |                            | A/D converter analog input pins. This function is enabled when the analog input is specified (ADER1).                                                                                                                         |                         |  |                            |

| Pin     | no.    |               | I/O                  | Pin status                |                                                                                                                                                                                                                               |  |                                                                                                                      |

|---------|--------|---------------|----------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|----------------------------------------------------------------------------------------------------------------------|

| LQFP *1 | QFP *2 | Pin name      | circuit              | during<br>reset           | Function                                                                                                                                                                                                                      |  |                                                                                                                      |

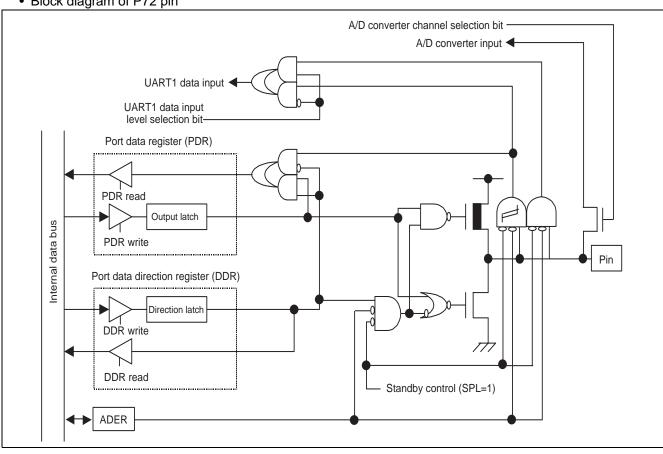

|         |        | P72           |                      |                           | General-purpose I/O ports.                                                                                                                                                                                                    |  |                                                                                                                      |

| 76      | 78     | SIN1          | J                    |                           | Serial data input pin for UART channel 1. While UART channel 1 is operating for input, the input of this pin is used as required. This pin must not be used for any other input.  CMOS input can be selected by user program. |  |                                                                                                                      |

|         |        | AN10          |                      |                           | A/D converter analog input pins. This function is enabled when the analog input is specified (ADER1).                                                                                                                         |  |                                                                                                                      |

|         |        | P73           |                      |                           | General-purpose I/O ports.                                                                                                                                                                                                    |  |                                                                                                                      |

| 75      | 77     | SOT1          | SOT1 K               | SOT1 K                    | К                                                                                                                                                                                                                             |  | Serial data output pin for UART channel 1. This function is enabled when data output of UART channel 1 is specified. |

|         |        | AN11          |                      |                           | A/D converter analog input pins. This function is enabled when the analog input is specified (ADER1).                                                                                                                         |  |                                                                                                                      |

|         |        | P74           | Analog<br>input<br>K | General-purpose I/O port. |                                                                                                                                                                                                                               |  |                                                                                                                      |

| 74      | 76     | SCK1          |                      |                           | Serial clock I/O pin for UART channel 1. This function is enabled when clock output of UART channel 1 is specified.                                                                                                           |  |                                                                                                                      |

|         |        | AN12          |                      |                           | A/D converter analog input pins. This function is enabled when the analog input is specified (ADER1).                                                                                                                         |  |                                                                                                                      |

|         |        | P75           |                      |                           | General-purpose I/O ports.                                                                                                                                                                                                    |  |                                                                                                                      |

| 73      | 75     | FRCK          | K                    |                           | External clock input pin for free-running timer.                                                                                                                                                                              |  |                                                                                                                      |

|         |        | AN13          |                      |                           | A/D converter analog input pins. This function is enabled when the analog input is specified (ADER1).                                                                                                                         |  |                                                                                                                      |

|         |        | P76, P77      |                      |                           | General-purpose I/O ports.                                                                                                                                                                                                    |  |                                                                                                                      |

| 72, 71  | 74, 73 | INO, IN1      | К                    |                           | Trigger input pins for input capture channels 0, 1. When input capture channels 0, 1 are used for input operation, these pins are enabled as required and must not be used for any other input.                               |  |                                                                                                                      |

|         |        | AN14,<br>AN15 |                      |                           | A/D converter analog input pins. This function is enabled when the analog input is specified (ADER1).                                                                                                                         |  |                                                                                                                      |

| Pin no.  |          | D: 1/O          |         | Pin status      |                                                                                                                                                                                                 |  |

|----------|----------|-----------------|---------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| LQFP *1  | QFP *2   | Pin name        | circuit | during<br>reset | Function                                                                                                                                                                                        |  |

|          |          | P80, P81        |         |                 | General-purpose I/O ports.                                                                                                                                                                      |  |

| 70, 69   | 72, 71   | IN2, IN3        | F       | - Port input    | Trigger input pins for input capture channels 2, 3. When input capture channels 2, 3 are used for input operation, these pins are enabled as required and must not be used for any other input. |  |

|          |          | P82 to P87      |         | 1 ort input     | General-purpose I/O ports.                                                                                                                                                                      |  |

| 68 to 63 | 70 to 65 | RTO0 to<br>RTO5 | L       |                 | Waveform generator output pins. These pins output the waveforms specified at the waveform generator. Output is generated when waveform generator output is enabled.                             |  |

| 25       | 27       | MD0             | М       | - Mode input    | Input pin for operation mode specification. Connect this pin directly to Vcc or Vss.                                                                                                            |  |

| 24, 23   | 26, 25   | MD1, MD0        | N       | Wode Input      | Input pin for operation mode specification. Connect this pin directly to Vcc or Vss.                                                                                                            |  |

| 80       | 2        | AVcc            | _       |                 | Vcc power input pin for analog circuits.                                                                                                                                                        |  |

| 79       | 1        | AVR             | _       | Power           | Vref + input pin for the A/D converter. This voltage must not exceed AVcc. Vref - is fixed to AVss.                                                                                             |  |

| 1        | 3        | AVss            | _       |                 | Vss power input pin for analog circuits.                                                                                                                                                        |  |

| 20, 61   | 22, 63   | Vss             |         | Power           | Power (0 V) input pin.                                                                                                                                                                          |  |

| 40, 60   | 42, 62   | Vcc             | _       | FOWEI           | Power (5 V) input pin.                                                                                                                                                                          |  |

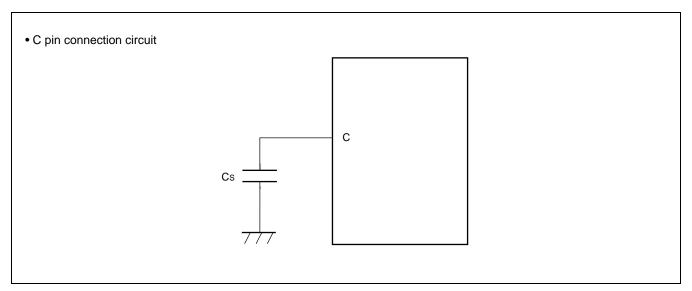

| 62       | 64       | С               | _       | _               | Capacity pin for power stabilization. Please connect to an approximately 0.1 $\mu F$ ceramic capacitor.                                                                                         |  |

<sup>\*1:</sup> FPT-80P-M05, FPT-80P-M11

<sup>\*2:</sup> FPT-80P-M06

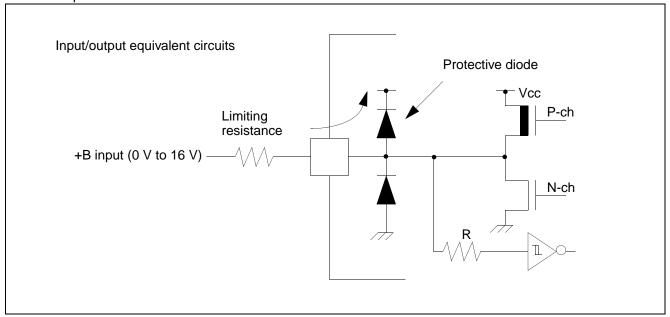

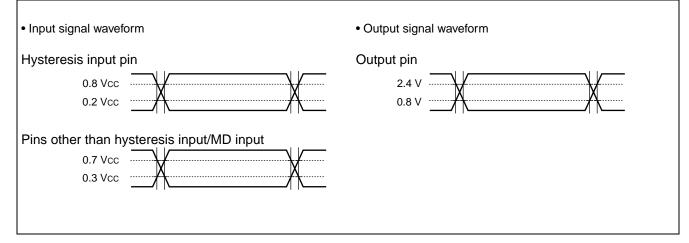

### ■ I/O CIRCUIT TYPE

| Classification | Туре                                                                           | Remarks                                                                                                                                |

|----------------|--------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| А              | X1 N-ch P-ch N-ch P-ch N-ch Standby mode control                               | Main clock (main clock crystal oscillator)  • Oscillation feedback resistor : approx. 1 MΩ                                             |

| В              | R                                                                              | <ul> <li>Hysteresis input</li> <li>Pull-up resistor : approx. 50 kΩ</li> </ul>                                                         |

| С              | P-ch Pull-up control P-ch Pout Nout N-ch Hysteresis input Standby mode control | <ul> <li>CMOS output</li> <li>Hysteresis input</li> <li>Selectable pull-up resistor : approx. 50 kΩ</li> <li>IoL = 12 mA</li> </ul>    |

| D              | P-ch Pull-up control P-ch Pout Nout N-ch Hysteresis input Standby mode control | <ul> <li>CMOS output</li> <li>Hysteresis input</li> <li>Selectable pull-up resistor :<br/>approx. 50 kΩ</li> <li>IoL = 4 mA</li> </ul> |

| E              | P-ch Pull-up control P-ch Pout N-ch Nout Standby mode control                  | <ul> <li>CMOS output</li> <li>CMOS input</li> <li>Selectable pull-up resistor :<br/>approx. 50 kΩ</li> <li>IoL = 4 mA</li> </ul>       |

| Classification | Туре                                                                               | Remarks                                                                                                                                     |

|----------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| F              | P-ch Pout N-ch Nout Hysteresis input Standby mode control                          | <ul> <li>CMOS output</li> <li>Hysteresis input</li> <li>IoL = 4 mA</li> </ul>                                                               |

| G              | P-ch Pout N-ch Nout Hysteresis input CMOS input Standby mode control               | <ul> <li>CMOS output</li> <li>Hysteresis input</li> <li>CMOS input (selectable for<br/>UART0 data input pin)</li> <li>IoL = 4 mA</li> </ul> |

| Н              | P-ch Pout N-ch Nout CMOS input Analog input control Analog input                   | <ul> <li>CMOS output</li> <li>CMOS input</li> <li>Analog input</li> <li>IoL = 4 mA</li> </ul>                                               |

| I              | P-ch Nout N-ch Nout Hysteresis input Analog I/O control Analog output Analog input | <ul> <li>CMOS output</li> <li>Hysteresis input</li> <li>Analog output</li> <li>Analog input</li> <li>IoL = 4 mA</li> </ul>                  |

| Classification | Туре                                                                              | Remarks                                                                                                                                      |

|----------------|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| J              | P-ch Pout N-ch Nout Hysteresis input CMOS input Analog input control Analog input | <ul> <li>CMOS output</li> <li>Hysteresis input</li> <li>CMOS input (selectable for<br/>UART1 data input pin)</li> <li>IoL = 4 mA</li> </ul>  |

| К              | P-ch Pout N-ch Nout Hysteresis input Analog input control Analog input            | <ul> <li>CMOS output</li> <li>Hysteresis input</li> <li>Analog input</li> <li>IoL = 4 mA</li> </ul>                                          |

| L              | P-ch Pout Nout N-ch Hysteresis input Standby mode control                         | <ul> <li>CMOS output</li> <li>Hysteresis input</li> <li>IoL = 12 mA</li> </ul>                                                               |

| М              | R<br>R<br>////                                                                    | Mask ROM / evaluation product  Hysteresis input  Selectable pull-up resistor: approx. 50 kΩ  FLASH product CMOS input  No pull-down resistor |

| N              |                                                                                   | Mask ROM / evaluation product  • Hysteresis input FLASH product  • CMOS input                                                                |

#### **■ HANDLING DEVICES**

#### 1. Preventing latch-up

CMOS ICs may cause latch-up in the following situations:

- When a voltage higher than Vcc or lower than Vss is applied to input or output pins.

- When a voltage exceeding the rating is applied between Vcc and Vss.

- When the AVcc power supply is applied before the Vcc voltage.

If latch-up occurs, the power supply current increases rapidly, sometimes resulting in thermal breakdown of the device. Use meticulous care not to exceed the rating.

For the same reason, also be careful not to let the analog power-supply voltage exceed the digital power-supply voltage.

#### 2. Handling unused pins

Unused input pins left open may cause abnormal operations, or latch-up leading to permanent damage. Unused input pins should be pulled up or pulled down through at least 2 k $\Omega$  resistance.

Unused input/output pins may be left open in output state, but if such pins are in input state they should be handled in the same way as input pins.

If any output pins are unused, set them to open.

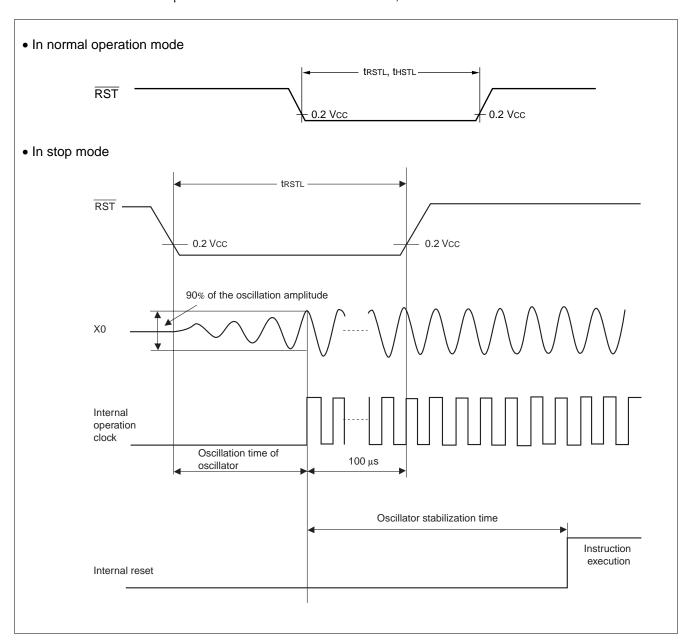

#### 3. Use of the external clock

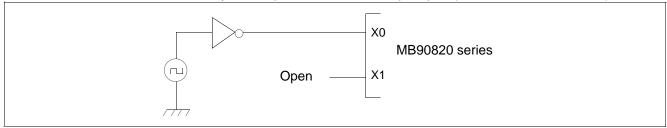

To use an external clock, drive only the X0 pin and leave the X1 pin open (See the illustration below).

#### 4. Power supply pins (Vcc/Vss)

In products with multiple Vcc or Vss pins, the pins of the same potential are internally connected in the device to avoid abnormal operations including latch-up. However, you must connect the pins to external power supply and a ground lines to lower the electro-magnetic emission level, to prevent abnormal operation of strobe signals caused by the rise in the ground level, and to conform to the total output current rating.

Moreover, connect the current supply source with the Vcc and Vss pins of this device at the low impedance.

It is also advisable to connect a ceramic bypass capacitor of approximately 0.1  $\mu$ F between Vcc and Vss near this device.

#### 5. Crystal oscillator circuit

Noise near the X0 and X1 pins may cause the device to malfunction. Design the printed circuit board so that X0, X1, the crystal oscillator (or ceramic oscillator) and the bypass capacitor to ground are located as close to the device as possible.

It is strongly recommended to design the PC board artwork with the X0 and X1 pins surrounded by ground plane because stable operation can be expected with such a layout.

#### 6. Turning-on sequence of power supply to A/D converter and D/A converter

Make sure to turn on the A/D converter and D/A converter power supply (AVcc, AVss, AVR) and analog inputs (AN0 to AN15) after turning-on the digital power supply (Vcc).

Turn-off the digital power after turning off the A/D converter and D/A converter supply and analog inputs. In this case, make sure that the voltage of AVR does not exceed AVcc (turning on/off the analog and digital power supplies simultaneously is acceptable).

#### 7. Connection of unused pins of A/D converter and D/A converter

When the A/D converter and D/A converter are not used, connect the pins as follows: AVcc = Vcc, AVss = AVR = Vss.

#### 8. N.C. pin

The N.C. (internally connected) pin must be opened for use.

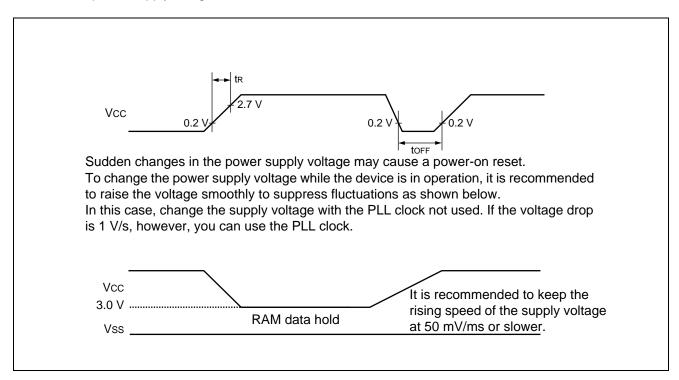

#### 9. Notes on energization

To prevent the internal regulator circuit from malfunctioning, set the voltage rise time during energization at 50 µs or more.

#### 10. Initialization

In the device, there are internal registers which are initialized only by a power-on reset. To initialize these registers turning on the power again.

#### 11. Return from standby state

If the power supply voltage goes below the standby RAM holding voltage in the standby state, the device may fail to return from the standby state. In this case, reset the device via the external reset pin to return to the normal state.

#### **■ BLOCK DIAGRAM**

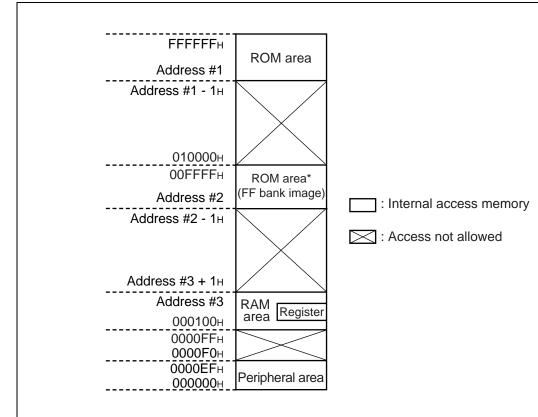

#### **■ MEMORY MAP**

\*: In Single chip mode, the mirror function is supported.

| Parts no. | Address#1           | Address#2 | Address#3 |

|-----------|---------------------|-----------|-----------|

| MB90822   | FF0000H             | 008000н   | 0010FFн   |

| MB90F822  | FF0000 <sub>H</sub> | 008000н   | 0010FFн   |

| MB90F823  | FE0000H             | 008000н   | 0010FFн   |

| MB90V820  | (FE0000н)           | 008000н   | 0040FFн   |

Note: The ROM data of bank FF is reflected to the upper address of bank 00, realizing effective use of the C compiler small model. The lower 16-bit is assigned to the same address, enabling reference of the table on the ROM without stating "far". For example, if an attempt has been made to access 00C000H, the contents of the ROM at FFC000H are accessed actually. Since the ROM area of the FF bank exceeds 32K bytes, the whole area cannot be reflected in the image for the 00 bank. The ROM data at FF8000H to FFFFFFH looks, therefore, as if it were the image for 008000H to 00FFFFH. Thus, it is recommended that the ROM data table be stored in the area of FF8000H to FFFFFFH.

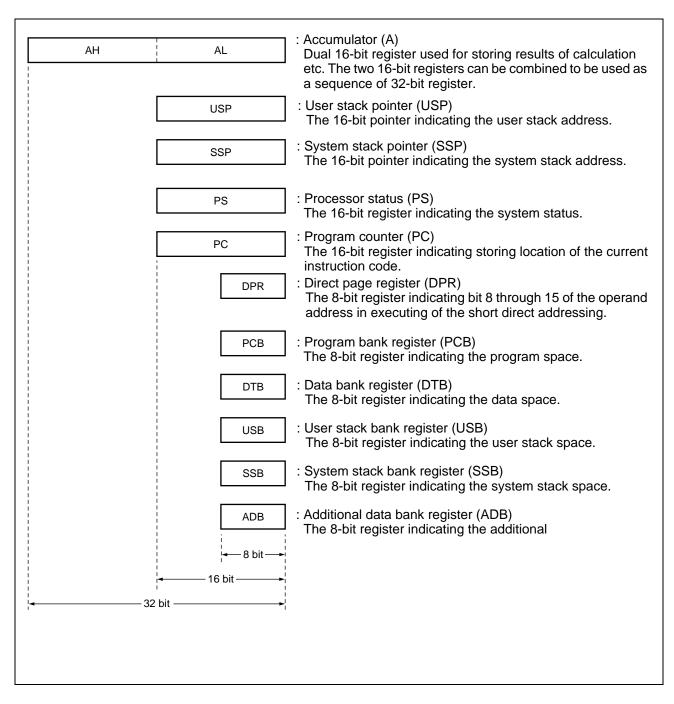

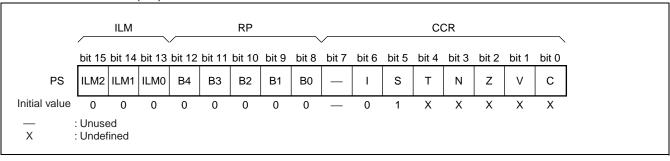

#### ■ F<sup>2</sup>MC-16LX CPU PROGRAMMING MODEL

Dedicated registers

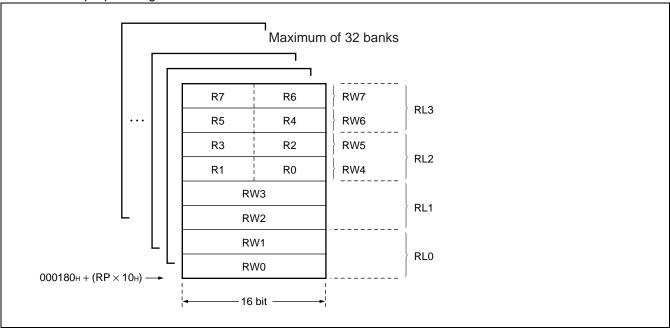

• General-purpose registers

• Processor status (PS)

### ■ I/O MAP

| Address              | Abbreviation     | Register                                                        | Byte access | Word access | Resource name   | Initial<br>value      |

|----------------------|------------------|-----------------------------------------------------------------|-------------|-------------|-----------------|-----------------------|

| 000000н              | PDR0             | Port 0 data register                                            | R/W         | R/W         | Port 0          | XXXXXXXXB             |

| 000001н              | PDR1             | Port 1 data register                                            | R/W         | R/W         | Port 1          | XXXXXXXX              |

| 000002н              | PDR2             | Port 2 data register                                            | R/W         | R/W         | Port 2          | XXXXXXXXB             |

| 000003н              | PDR3             | Port 3 data register                                            | R/W         | R/W         | Port 3          | XXXXXXXXB             |

| 000004н              | PDR4             | Port 4 data register                                            | R/W         | R/W         | Port 4          | XXXXXXXXB             |

| 000005н              | PDR5             | Port 5 data register                                            | R/W         | R/W         | Port 5          | XXXXXXXX              |

| 000006н              | PDR6             | Port 6 data register                                            | R/W         | R/W         | Port 6          | XXXXXXXXB             |

| 000007н              | PDR7             | Port 7 data register                                            | R/W         | R/W         | Port 7          | XXXXXXXX              |

| 000008н              | PDR8             | Port 8 data register                                            | R/W         | R/W         | Port 8          | XXXXXXXX              |

| 000009нtо<br>00000Fн |                  | Pro                                                             | hibited a   | rea         |                 |                       |

| 000010н              | DDR0             | Port 0 data direction register                                  | R/W         | R/W         | Port 0          | 0000000в              |

| 000011н              | DDR1             | Port 1 data direction register                                  | R/W         | R/W         | Port 1          | 0000000в              |

| 000012н              | DDR2             | Port 2 data direction register                                  | R/W         | R/W         | Port 2          | 0000000в              |

| 000013н              | DDR3             | Port 3 data direction register                                  | R/W         | R/W         | Port 3          | 0000000в              |

| 000014н              | DDR4             | Port 4 data direction register                                  | R/W         | R/W         | Port 4          | 0000000в              |

| 000015н              | DDR5             | Port 5 data direction register                                  | R/W         | R/W         | Port 5          | XXXXXX00 <sub>B</sub> |

| 000016н              | DDR6             | Port 6 data direction register                                  | R/W         | R/W         | Port 6          | 0000000в              |

| 000017н              | DDR7             | Port 7 data direction register                                  | R/W         | R/W         | Port 7          | 0000000в              |

| 000018н              | DDR8             | Port 8 data direction register                                  | R/W         | R/W         | Port 8          | 0000000в              |

| 000019нtо<br>00001Fн |                  | Pro                                                             | hibited a   | rea         |                 |                       |

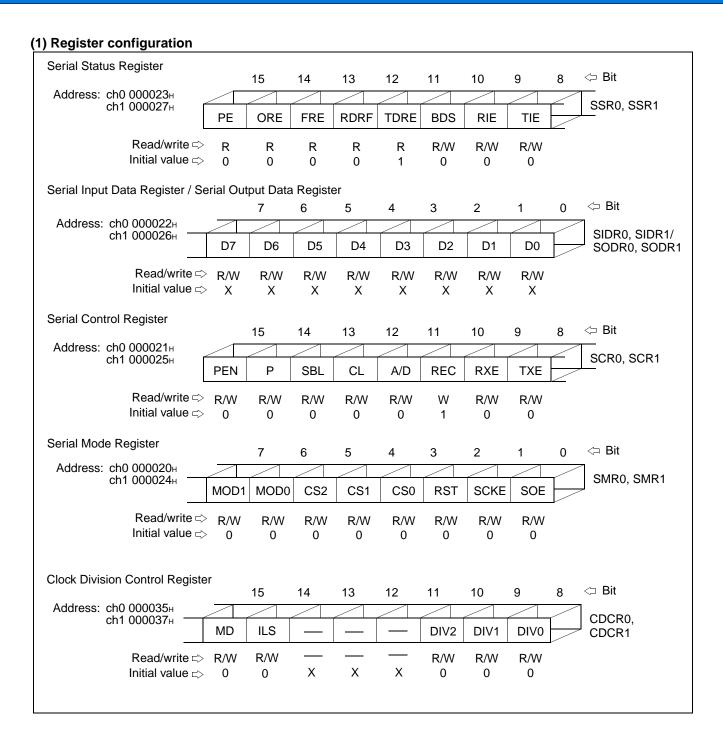

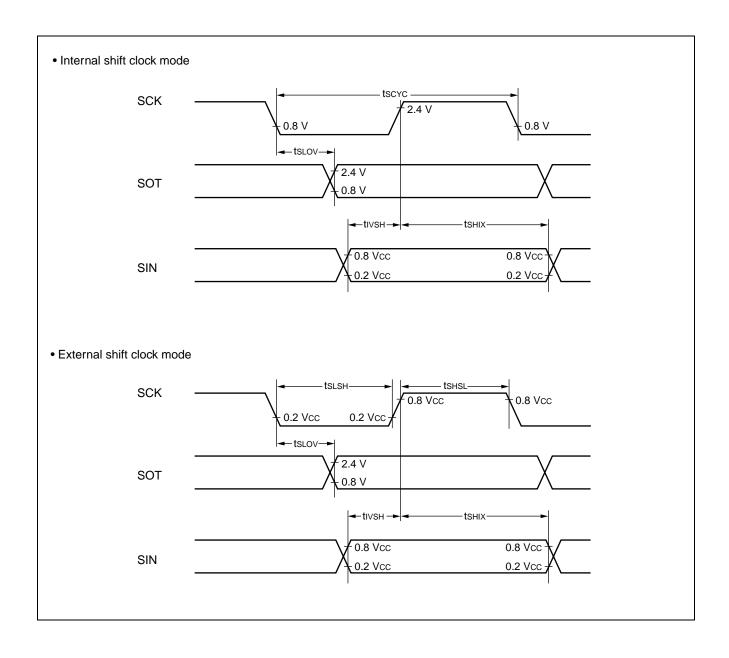

| 000020н              | SMR0             | Serial mode register 0                                          | R/W         | R/W         |                 | 0000000в              |

| 000021н              | SCR0             | Serial control register 0                                       | R/W         | R/W         |                 | 00000100в             |

| 000022н              | SIDR0 /<br>SODR0 | Serial input data register 0 /<br>Serial output data register 0 | R/W         | R/W         | UART0           | XXXXXXX               |

| 000023н              | SSR0             | Serial status register 0                                        | R/W         | R/W         |                 | 00001000в             |

| 000024н              | SMR1             | Serial mode register 1                                          | R/W         | R/W         |                 | 0000000в              |

| 000025н              | SCR1             | Serial control register 1                                       | R/W         | R/W         |                 | 00000100в             |

| 000026н              | SIDR1 /<br>SODR1 | Serial input data register 1 /<br>Serial output data register 1 | R/W         | R/W         | UART1           | XXXXXXXXB             |

| 000027н              | SSR1             | Serial status register 1                                        | R/W         | R/W         |                 | 00001000в             |

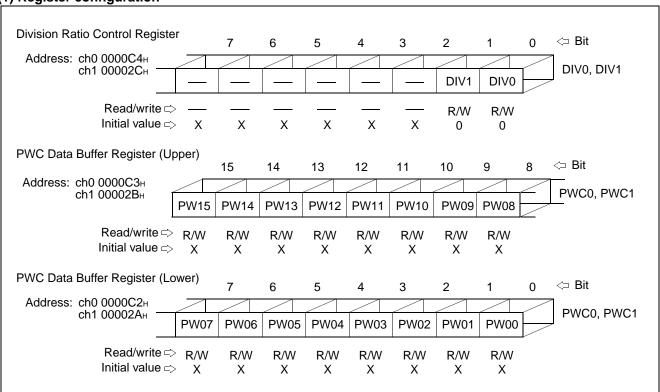

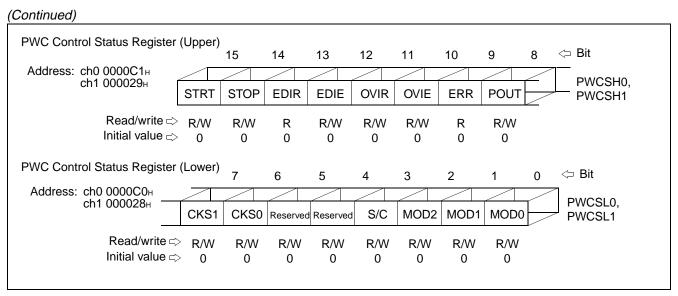

| 000028н              | PWCSL1           | PWC control status register                                     | R/W         | R/W         |                 | 0000000в              |

| 000029н              | PWCSH1           | CH1                                                             | R/W         | R/W         |                 | 0000000в              |

| 00002Ан              | DMC              | DWO lete by # 221                                               |             | D // /      | PWC timer (CH1) | XXXXXXXX              |

| 00002Вн              | PWC1             | PWC data buffer register CH1                                    | _           | R/W         |                 | XXXXXXXX              |

| 00002Сн              | DIV1             | Divide ratio control register<br>CH1                            | R/W         | R/W         |                 | XXXXXX00 <sub>B</sub> |

| Address             | Abbrevia-<br>tion | Register                                     | Byte access | Word access | Resource name              | Initial<br>value |  |  |  |

|---------------------|-------------------|----------------------------------------------|-------------|-------------|----------------------------|------------------|--|--|--|

| 00002Dн,<br>00002Eн |                   |                                              |             |             |                            |                  |  |  |  |

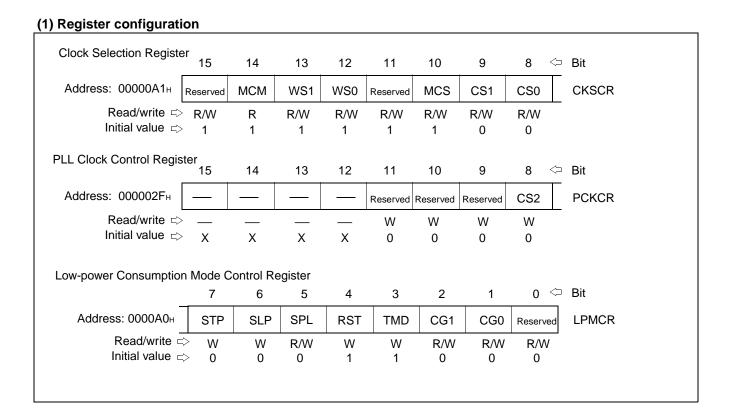

| 00002Fн             | PCKCR             | PLL clock control register                   | W           | W           | PLL                        | ХХХХ0000в        |  |  |  |

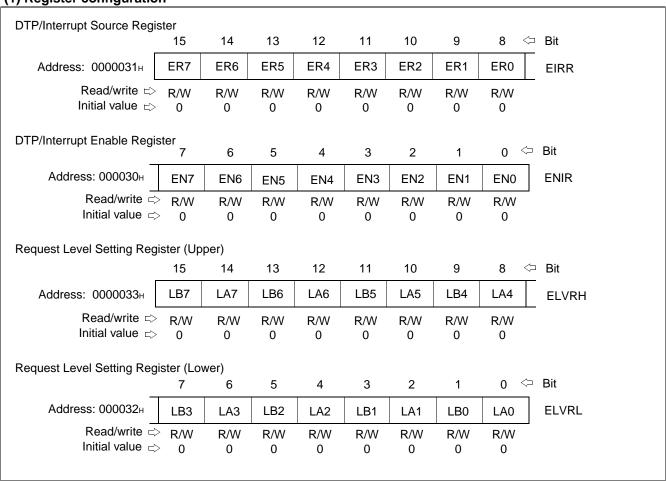

| 000030н             | ENIR              | DTP / Interrupt enable register              | R/W         | R/W         |                            | 0000000в         |  |  |  |

| 000031н             | EIRR              | DTP / Interrupt cause register               | R/W         | R/W         |                            | XXXXXXXXB        |  |  |  |

| 000032н             | ELVRL             | Request level setting register (lower byte)  | R/W         | R/W         | DTP/<br>external interrupt | 00000000в        |  |  |  |

| 000033н             | ELVRH             | Request level setting register (higher byte) | R/W         | R/W         |                            | 00000000в        |  |  |  |

| 000034н             |                   | Proh                                         | ibited are  | a           |                            |                  |  |  |  |

| 000035н             | CDCR0             | Clock division control register CH0          | R/W         | R/W         | Communication prescaler 0  | 00XXX000в        |  |  |  |

| 000036н             |                   | Proh                                         | ibited are  | a           |                            |                  |  |  |  |

| 000037н             | CDCR1             | Clock division control register CH1          | R/W         | R/W         | Communication prescaler 1  | 00XXX000в        |  |  |  |

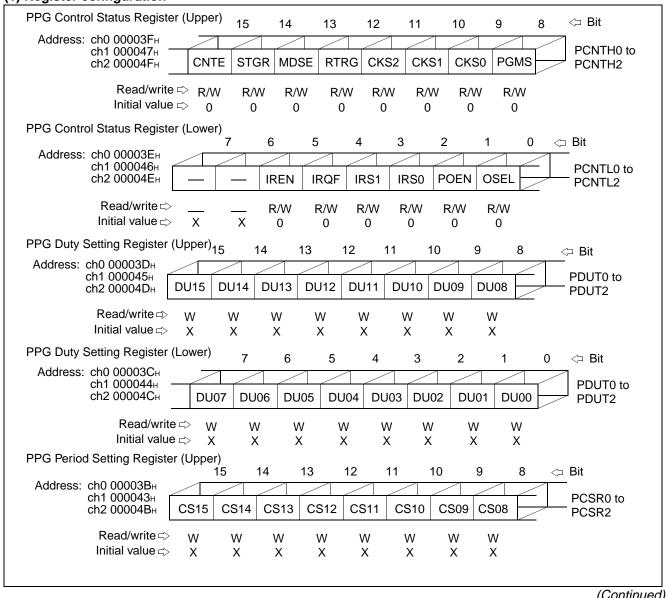

| 000038н             | DDCD0             | DDC0 down counter register                   |             | В           |                            | 11111111в        |  |  |  |

| 000039н             | PDCR0             | PPG0 down counter register                   |             | R           |                            | 11111111в        |  |  |  |

| 00003Ан             | PCSR0             | DDC0 period potting register                 |             | W           |                            | XXXXXXXXB        |  |  |  |

| 00003Вн             | PUSKU             | PPG0 period setting register                 |             | VV          | 16-bit PPG timer           | XXXXXXXXB        |  |  |  |

| 00003Сн             | PDUT0             | PPG0 duty setting register                   |             | W           | (CH0)                      | XXXXXXXXB        |  |  |  |

| 00003Dн             | PDOTO             | FFG0 duty setting register                   |             | VV          |                            | XXXXXXXXB        |  |  |  |

| 00003Ен             | PCNTL0            | PPG0 control status register                 | R/W         | R/W         |                            | ХХ000000в        |  |  |  |

| 00003Fн             | PCNTH0            | F F GO Control Status register               | R/W         | R/W         |                            | 0000000в         |  |  |  |

| 000040н             | PDCR1             | PG1 down counter register                    |             | R           |                            | 11111111в        |  |  |  |

| 000041н             |                   | 11 Of down counter register                  |             | IX          |                            | 11111111в        |  |  |  |

| 000042н             | PCSR1             | PPG1 period setting register                 |             | W           |                            | XXXXXXXXB        |  |  |  |

| 000043н             | 1 00101           | 11 O1 period setting register                |             | VV          | 16-bit PPG timer           | XXXXXXXXB        |  |  |  |

| 000044н             | PDUT1             | PPG1 duty setting register                   |             | W           | (CH1)                      | XXXXXXXX         |  |  |  |

| 000045н             | 1 0011            | 1 1 0 1 daty setting register                |             | VV          |                            | XXXXXXXXB        |  |  |  |

| 000046н             | PCNTL1            | PPG1 control status register                 | R/W         | R/W         |                            | ХХ000000в        |  |  |  |

| 000047н             | PCNTH1            | Or obtained status register                  | R/W         | R/W         |                            | 0000000в         |  |  |  |

| 000048н             | PDCR2             | PPG2 down counter register                   | _           | R           |                            | 11111111в        |  |  |  |

| 000049н             | 1 50112           |                                              |             | 1           |                            | 11111111в        |  |  |  |

| 00004Ан             | PCSR2             | PPG2 period setting register                 | _           | W           |                            | XXXXXXXXB        |  |  |  |

| 00004Вн             | 1 00112           | . 1 02 period setting register               |             | • • •       | 16-bit PPG timer           | XXXXXXXXB        |  |  |  |

| 00004Сн             | PDUT2             | PPG2 duty setting register                   |             | W           | (CH2)                      | XXXXXXXXB        |  |  |  |

| 00004Dн             | 1 0012            | 1 1 02 daty setting register                 |             | V V         |                            | XXXXXXXXB        |  |  |  |

| 00004Ен             | PCNTL2            | PPG2 control status register                 | R/W         | R/W         |                            | ХХ000000в        |  |  |  |

| 00004Fн             | PCNTH2            | 1 1 02 control status register               | R/W         | R/W         |                            | 0000000в         |  |  |  |

| Address                  | Abbreviation | Register                                                                   | Byte access | Word access | Resource name        | Initial<br>value      |

|--------------------------|--------------|----------------------------------------------------------------------------|-------------|-------------|----------------------|-----------------------|

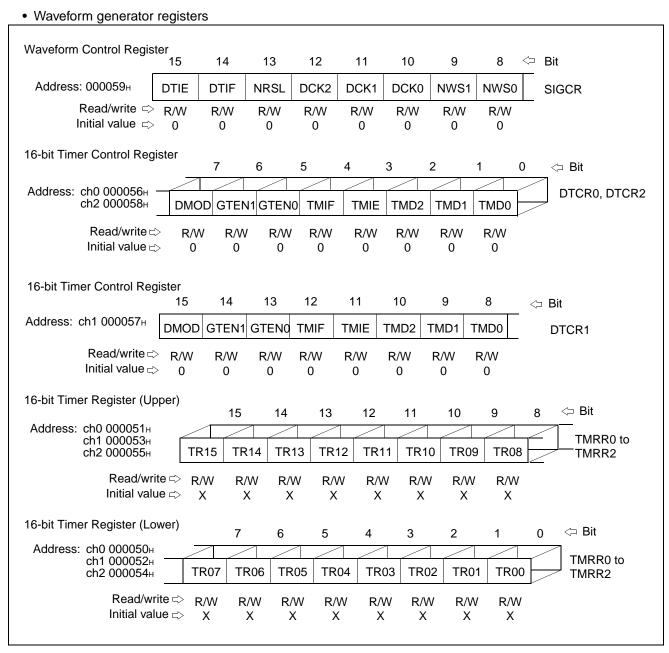

| 000050н                  | TMRR0        | 16 hit timer register 0                                                    |             | R/W         |                      | XXXXXXXXB             |

| 000051н                  | TWIKKU       | 16-bit timer register 0                                                    |             | I K/VV      |                      | XXXXXXXXB             |

| 000052н                  | TMRR1        | 16 bit timer register 1                                                    |             | R/W         |                      | XXXXXXXX              |

| 000053н                  | TIVIRKT      | 16-bit timer register 1                                                    |             | R/VV        |                      | XXXXXXXX              |

| 000054н                  | TMRR2        | 16 bit timer register 2                                                    |             | R/W         | Wayoform ganaratar   | XXXXXXXXB             |

| 000055н                  | TWIKKZ       | 16-bit timer register 2                                                    |             | I K/VV      | Waveform generator   | XXXXXXXX              |

| 000056н                  | DTCR0        | 16-bit timer control register 0                                            | R/W         | R/W         |                      | 0000000в              |

| 000057н                  | DTCR1        | 16-bit timer control register 1                                            | R/W         | R/W         |                      | 0000000в              |

| 000058н                  | DTCR2        | 16-bit timer control register 2                                            | R/W         | R/W         |                      | 0000000в              |

| 000059н                  | SIGCR        | Waveform control register                                                  | R/W         | R/W         |                      | 0000000в              |

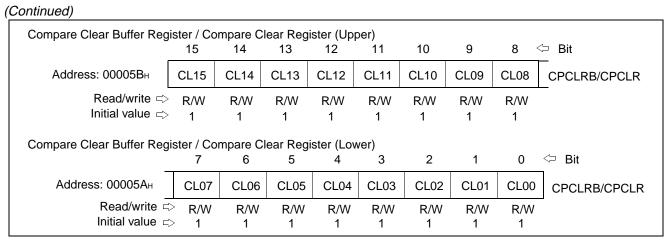

| 00005Ан                  | CPCLRB /     | Compare clear buffer register/                                             |             | R/W         |                      | 11111111в             |

| 00005Вн                  | CPCLR        | Compare clear register (lower)                                             |             | IN/VV       | 16-bit free-running  | 111111111             |

| 00005Сн                  | TCDT         | Timer register (lower)                                                     |             | R/W         | timer                | 0000000в              |

| 00005Dн                  | TCDT         | Timer register (lower)                                                     |             | I I V V V   |                      | 0000000в              |

| 00005Ен                  | TCCSL        | Timer control status register (lower)                                      | R/W         | R/W         | 16-bit free-running  | 0000000в              |

| 00005Fн                  | TCCSH        | Timer control status register (upper)                                      | R/W         | R/W         | timer                | Х0000000в             |

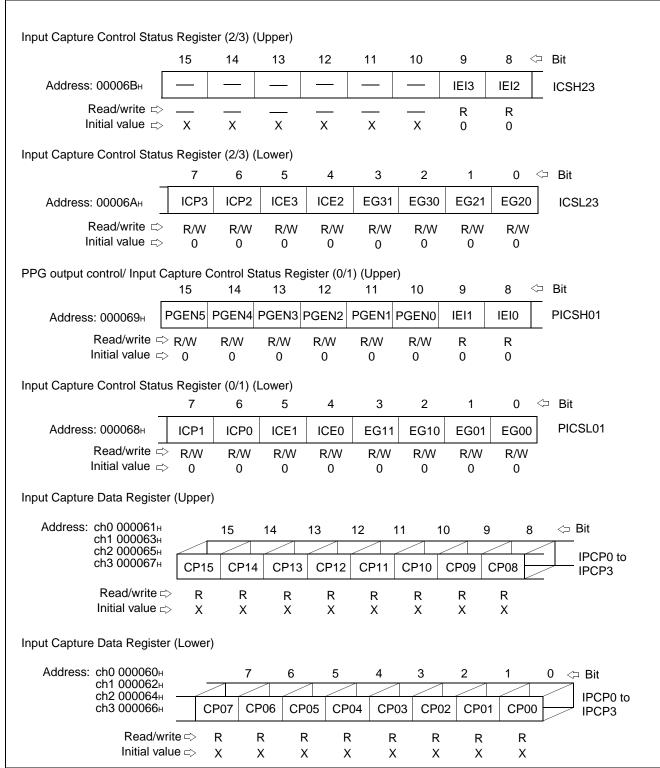

| 000060н                  | IPCP0        | Input conture data register CHO                                            |             | R           |                      | XXXXXXXX              |

| 000061н                  | IFCFU        | Input capture data register CH0                                            |             | I N         |                      | XXXXXXXX              |

| 000062н                  | IPCP1        | Input capture data register CH1                                            |             | R           |                      | XXXXXXXX              |

| 000063н                  | IFOFT        | Imput capture data register Ciff                                           |             |             |                      | XXXXXXXX              |

| 000064н                  | IPCP2        | Input capture data register CH2                                            |             | R           | 1                    | XXXXXXXX              |

| 000065н                  | IF GF Z      | Imput capture data register Criz                                           |             | IX.         |                      | XXXXXXXX              |

| 000066н                  | IPCP3        | Input capture data register CH3                                            |             | R           |                      | XXXXXXXX              |

| 000067н                  | 11 01 3      | imput capture data register Cris                                           |             | IX.         | 16-bit input capture | XXXXXXXX              |

| 000068н                  | PICSL01      | Input capture control status register (ch0,1) (lower)                      | R/W         | R/W         | (CH0 to CH3)         | 00000000в             |

| 000069н                  | PICSH01      | PPG output control / Input capture control status register (ch0,1) (upper) | R/W         | R/W         |                      | 00000000в             |

| 00006Ан                  | ICSL23       | Input capture control status register (ch2, 3) (lower)                     | R/W         | R/W         |                      | 00000000в             |

| 00006Вн                  | ICSH23       | Input capture control status register (ch2, 3) (upper)                     | R           | R           |                      | XXXXXX00 <sub>B</sub> |

| 00006Сн<br>to<br>00006Ен |              | Prol                                                                       | hibited a   | rea         |                      | (Continued)           |

| Address             | Abbreviation | Register                                  | Byte access | Word access | Resource name                | Initial<br>value      |

|---------------------|--------------|-------------------------------------------|-------------|-------------|------------------------------|-----------------------|

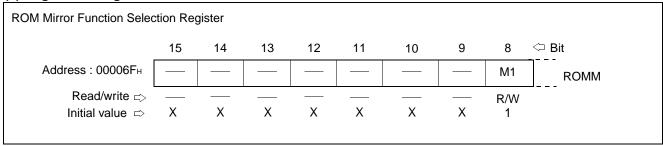

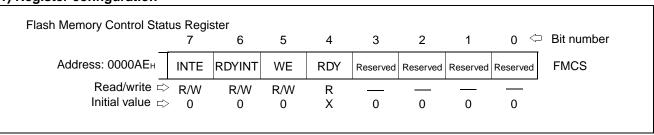

| 00006Fн             | ROMM         | ROM mirroring function selection register | W           | W           | ROM mirroring function       | XXXXXXX1 <sub>B</sub> |

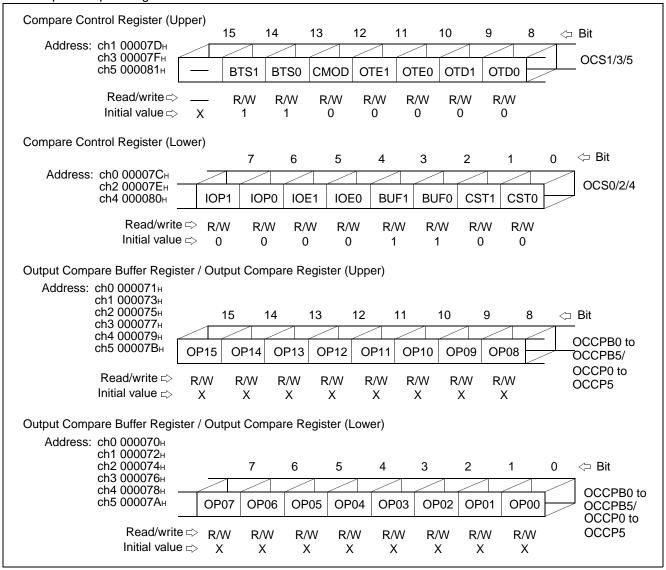

| 000070н             | OCCPB0 /     | Output compare buffer register /          |             | R/W         |                              | XXXXXXXXB             |

| 000071н             | OCCP0        | Output compare register 0                 |             | IX/VV       |                              | XXXXXXXXB             |

| 000072н             | OCCPB1 /     | Output compare buffer register /          |             | R/W         |                              | XXXXXXXXB             |

| 000073н             | OCCP1        | Output compare register 1                 |             | IX/VV       |                              | XXXXXXXXB             |

| 000074н             | OCCPB2 /     | Output compare buffer register /          |             | R/W         |                              | XXXXXXXXB             |

| 000075н             | OCCP2        | Output compare register 2                 |             | IX/VV       |                              | XXXXXXXXB             |

| 000076н             | OCCPB3 /     | Output compare buffer register /          |             | R/W         |                              | XXXXXXXXB             |

| 000077н             | OCCP3        | Output compare register 3                 |             | IX/VV       |                              | XXXXXXXXB             |

| 000078н             | OCCPB4 /     | Output compare buffer register /          |             | R/W         | Output compare               | XXXXXXXXB             |

| 000079н             | OCCP4        | Output compare register 4                 |             | K/VV        | (CH0 to CH5)                 | XXXXXXXXB             |

| 00007Ан             | OCCPB5 /     | Output compare buffer register /          |             | R/W         |                              | XXXXXXXXB             |

| 00007Вн             | OCCP5        | Output compare register 5                 |             | K/VV        |                              | XXXXXXXXB             |

| 00007Сн             | OCS0         | Compare control register CH0              | R/W         | R/W         |                              | 0000000в              |

| 00007Dн             | OCS1         | Compare control register CH1              | R/W         | R/W         |                              | Х000000в              |

| 00007Ен             | OCS2         | Compare control register CH2              | R/W         | R/W         |                              | 0000000в              |

| 00007Fн             | OCS3         | Compare control register CH3              | R/W         | R/W         |                              | Х000000в              |

| 000080н             | OCS4         | Compare control register CH4              | R/W         | R/W         |                              | 0000000в              |

| 000081н             | OCS5         | Compare control register CH5              | R/W         | R/W         |                              | Х000000в              |

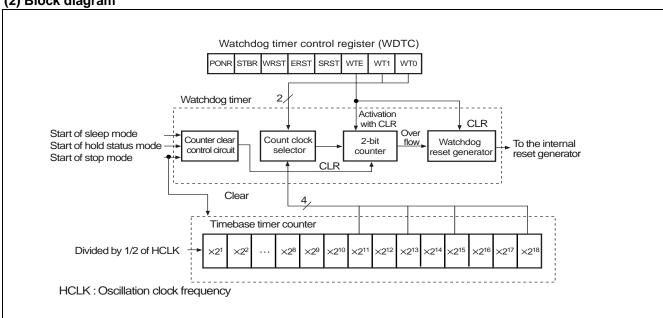

| 000082н             | TMCSRL0      | Timer control status register CH0 (lower) | R/W         | R/W         |                              | 0000000в              |

| 000083н             | TMCSRH0      | Timer control status register CH0 (upper) | R/W         | R/W         | 16-bit reload timer<br>(CH0) | ХХХХ0000в             |

| 000084н             | TMR0/        | 16 bit timer register CH0 /               |             | R/W         |                              | XXXXXXXXB             |

| 000085н             | TMRD0        | 16-bit reload register CH0                |             | IX/VV       |                              | XXXXXXXXB             |

| 000086н             | TMCSRL1      | Timer control status register CH1 (lower) | R/W         | R/W         |                              | 0000000в              |

| 000087н             | TMCSRH1      | Timer control status register CH1 (upper) | R/W         | R/W         | 16-bit reload timer<br>(CH1) | ХХХХ0000в             |

| 000088н             | TMR1/        | 16 bit timer register CH1 /               |             | DAM         |                              | XXXXXXXXB             |

| 000089н             | TMRD1        | 16-bit reload register CH1                |             | R/W         |                              | XXXXXXXXB             |

| 00008Ан,<br>00008Вн |              | Prol                                      | hibited a   |             |                              |                       |

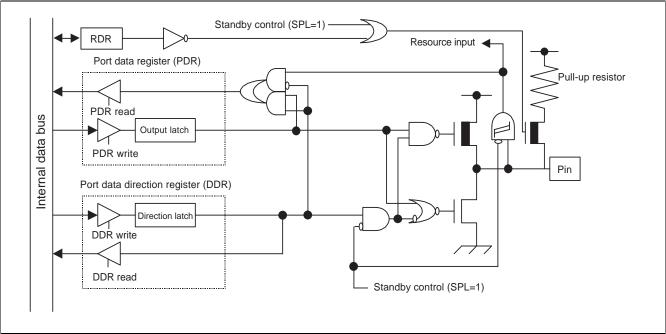

| 00008Сн             | RDR0         | Port 0 pull-up resistor setting register  | R/W         | R/W         | Port 0                       | 00000000в             |

| 00008Dн             | RDR1         | Port 1 pull-up resistor setting register  | R/W         | R/W         | Port 1                       | 00000000в             |