# USER'S MANUAL

# TCC720

32-bit RISC

Microprocessor

For

**Digital Media Player**

Preliminary Rev 0.51

### TABLE OF CONTENTS

32-bit RISC Microprocessor for Digital Media Player Dec. 16. 2002

Preliminary Spec 0.51

#### TABLE OF CONTENTS

- 1. INTRODUCTION

- 1.1 Features

- 1.2 Pin Description

- 1.3 Package Diagram

- 2. ADDRESS & REGISTER MAP

- 3. DAI (Digital Audio Interface) & CDIF (CD-DSP Interface)

- 4. INTERRUPT CONTROLLER

- 5. TIMER / COUNTER

- 6. GPIO

- 7. CLOCK GENERATOR

- 8. USB (Universal Serial Bus) CONTROLLER

- 9. UART / IrDA

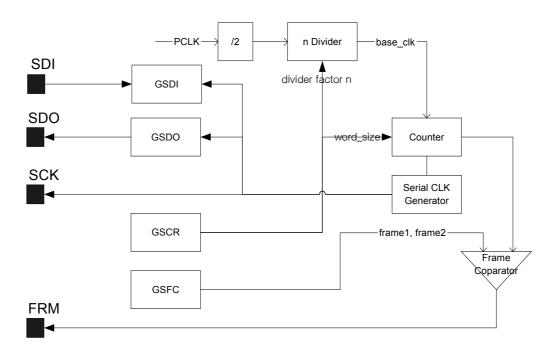

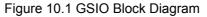

- 10. GSIO (General Purpose Serial Input/Output)

- 11. MISCELLANEOUS PERIPHERALS

- 11.1 ADC

- 11.2 CODEC

- 12. DMA CONTROLLER

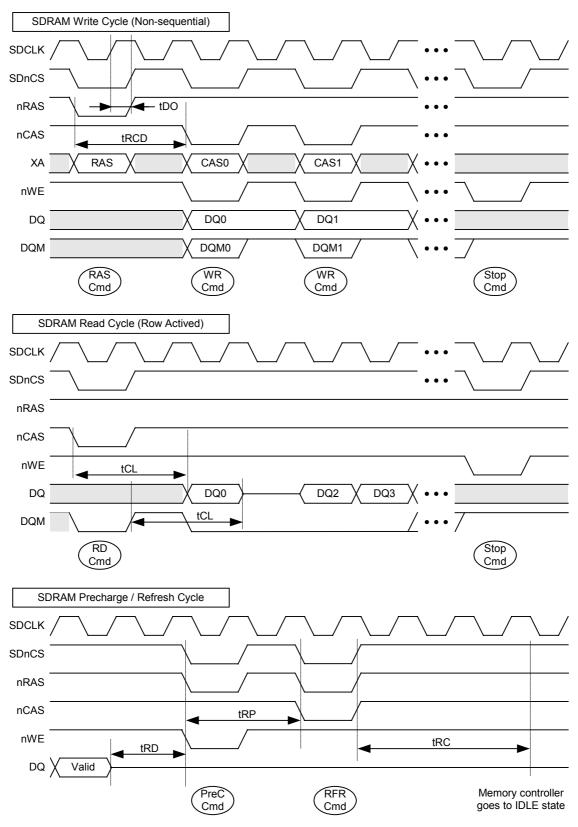

- 13. MEMORY CONTROLLER

- 13.1 Overview

- 13.2 SDRAM Controller

- 13.3 Miscellaneous Configuration

- 13.4 External Memory Controller

- 13.5 Internal Memories

- 14. BOOT ROM

- 14.1 External ROM Boot

- 14.2 UART Boot

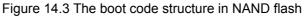

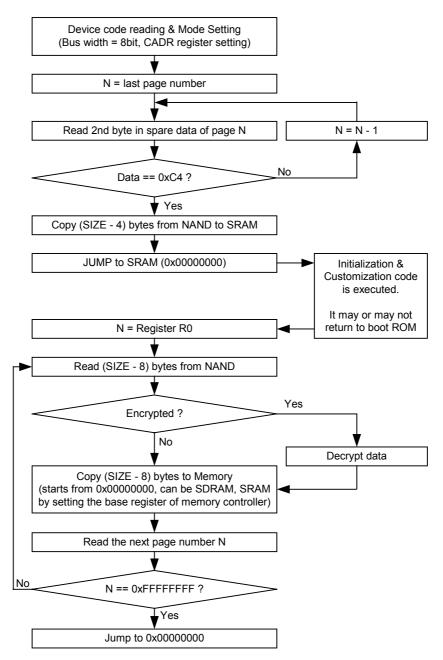

- 14.3 NAND Boot

- 14.4 NOR Boot with Security

- 14.5 HPI Boot

- 14.6 Development Mode

- 15. JTAG DEBUG INTERFACE

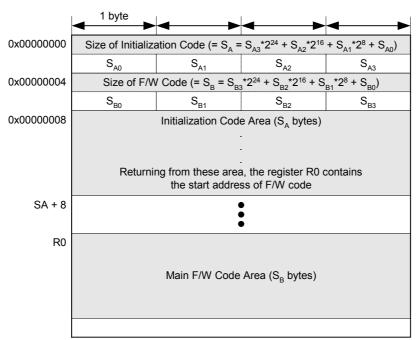

- 16. PACKAGE DIMENSION

### **CHAPTER 1**

### INTRODUCTION

Preliminary Spec 0.51

#### **1 INTRODUCTION**

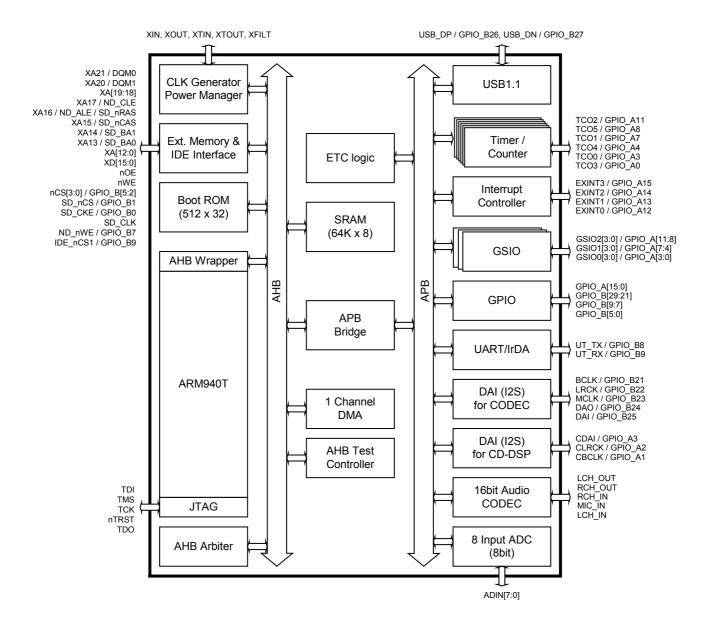

TCC720 is system LSI for digital media player which based on ARM940T, ARM's proprietary 32bit RISC CPU core. It can decode and encode MP3 or other types of audio/voice compression / decompression standards by software based architecture.

The on-chip USB controller enables the data transmission between a personal computer and storage of device such as NAND flash, HDD, CD etc, which can be controlled by TCC720.

TCC720 also includes on-chip stereo audio CODEC eliminates the need of expensive external audio CODEC. Using I2S port, TCC720 can also use the external audio CODEC by performance or other reason.

### INTRODUCTION

#### 32-bit RISC Microprocessor for Digital Media Player Dec. 16. 2002

Preliminary Spec 0.51

#### **1.1 FEATURES**

- 32bit ARM940TDMI RISC CPU core

- 8KB instruction/data cache

- Internal boot ROM of 4Kbytes for various boot procedure(NAND, UART) and security

- Internal SRAM of 64K bytes for general usage

- On-chip peripherals

- Memory controller for various memories such as PROM, FLASH, SRAM, SDRAM

- IDE Interface for HDD or USB device

- 4 external interrupts, 9 internal interrupts

- 4 timer/counters, 2 timers

- USB1.1 device (Full speed)

- UART(IrDA) for serial Host I/F

- GPIO, GSIO

- I2S interface for internal and external audio CODEC

- I2S interface for CD-DSP

- On chip audio CODEC with MIC input

- General purpose ADC (3 input)

- 1 Channel DMA for transferring a bulk of data

- JTAG interface for code debugging

- 0.25um low power CMOS process

- 2.5V for core, 3.3V for I/O port

- 128-pin TQFP

- Operating up to 120MHz

#### **1.2 APPLICATIONS**

- Portable Digital Audio Encoder/Decoder

- MP3 Juke Box

- Digital Audio Encoder/Decoder

- Digital Internet Radio Server

- Multimedia Storage Device

### INTRODUCTION

32-bit RISC Microprocessor for Digital Media Player Dec. 16. 2002

Figure 1.1 Functional Block Diagram

Preliminary Spec 0.51

#### **1.2 Pin Description**

#### **JTAG Interface**

| Signal Name | NUM | Туре | Description                                       |

|-------------|-----|------|---------------------------------------------------|

| TDI         | 99  | I    | JTAG serial data input for ARM940T                |

| TMS         | 100 | I    | JTAG Test mode select for ARM940T                 |

| ТСК         | 101 | I    | JTAG test clock for ARM940T                       |

| TDO         | 102 | 0    | JTAG serial data output for ARM940T               |

| nTRST       | 103 | I    | Reset signal for boundary scan logic. Active low. |

#### **External Memory Interface**

| Signal         | Shared Signal   | NUM     | Туре | Description                                           |

|----------------|-----------------|---------|------|-------------------------------------------------------|

| SD_CKE         | GPIO_B0         | 56      | 0    | Clock enable signal for SDRAM, Active high. / GPIO_B1 |

| SD_CLK         | GPO             | 44      | 0    | SDRAM clock                                           |

| SD_nCS         | GPIO_B1         | 46      | 0    | Chip select signal for SDRAM, Active low. / GPIO_B0   |

| XA[6:0]        | -               | 23:17   | 0    | Address bus for external memories.                    |

| XA[12:7]       | -               | 31:26   | 0    | Address bus for external memories.                    |

| XA[13]         | SD_BA0          | 34      | 0    | Bank Address 0 for SDRAM / XA[13]                     |

| XA[14]         | SD_BA1          | 35      | 0    | Bank Address 1 for SDRAM / XA[14]                     |

| XA[15]         | SD_nCAS         | 36      | 0    | CAS for SDRAM / XA[15]                                |

| XA[16]         | ND_ALE, SD_nRAS | 37      | 0    | ALE for NAND flash / RAS for SDRAM / XA[16]           |

| XA[17]         | ND_CLE          | 38      | 0    | CLE for NAND flash / XA[17]                           |

| XA[19:18]      | -               | 40:39   | 0    | XA[19:18] for static memory / Bus Width configuration |

| XA[21:20]      | DQM[0:1]        | 43:42   | 0    | XA[21:20] / Data I/O mask                             |

| XD[15:9],      | XD[15:9],       | 15:9,   |      |                                                       |

| XD[8:4],       | XD[8:4],        | 6:2,    | I/O  | Data bus for external memory                          |

| XD[3:0]        | XD[3:0]         | 128:125 |      |                                                       |

| nCS0 / ND_nOE0 | GPIO_B2         | 47      | 0    | External chip select 0 / NAND flash 0 OE / GPIO_B2    |

| nCS1 / ND_nOE1 | GPIO_B3         | 48      | 0    | External chip select 1 / NAND flash 1 OE / GPIO_B3    |

| nCS2 / ND_nOE2 | GPIO_B4         | 49      | 0    | External chip select 2 / NAND flash 2 OE / GPIO_B4    |

| nCS3 / ND_nOE3 | GPIO_B5         | 50      | 0    | External chip select 3 / NAND flash 3 OE / GPIO_B5    |

| IDE_nCS1       | GPIO_B9 / UT_RX | 61      | 0    | IDE chip select 1. Active low. / GPIO_B9 / UART RX    |

| ND_nWE         | GPIO_B7         | 57      | 0    | NAND flash WE. Active low. / GPIO_B7                  |

| nWE            | nWE             | 58      | 0    | Static memory write enable signal. Active low.        |

| nOE            | nOE             | 59      | 0    | Static memory output enable signal. Active low.       |

| READY          | -               | 73      | Ι    | Ready information from external device.               |

\*) XA[21:0] is used as system address bus for external memories such as SRAM, ROM.

XA[12:0] can be also used as RAS and CAS signals for SDRAM.

XD[15:0] is used as system data bus for all types of external memories contained.

SD\_CLK is also used as general purpose output port by setting clock control flag. Refer to the chapter of memory controller for detail.

Dec. 16. 2002

Preliminary Spec 0.51

#### **General Purpose I/O**

| Signal        | Shared Signal                                                              | NUM                        | Туре | Description                                                          |

|---------------|----------------------------------------------------------------------------|----------------------------|------|----------------------------------------------------------------------|

| GPIO_A[15:12] | EXINT[3:0]                                                                 | 124:121                    | I/O  | GPIO_A[15:12] / External Interrupt Source 3 ~ 0                      |

| GPIO_A[11:8]  | GSIO2[3:0]<br>(SDI_2, FRM_2,<br>SCK_2, SDO_2)                              | 118:115                    | I/O  | GPIO_A[11:8] / General Purpose Serial I/O 2                          |

| GPIO_A[7:4]   | GSIO1[3:0]<br>(SDI_1, FRM_1,<br>SCK_1, SDO_1)                              | 114:113<br>111<br>108      | I/O  | GPIO_A[7:4] / General Purpose Serial I/O 1                           |

| GPIO_A[3:1]   | GSIO0[3:1] (SDI_0,<br>FRM_0, SCK_0) /<br>CDIF[2:0] (CDAI,<br>CLRCK, CBCLK) | 107:105                    | I/O  | GPIO_A[3:1] / General purpose serial I/O 0 /<br>CD interface signals |

| GPIO_A[0]     | GSIO0[0] (SDO_0)                                                           | 104                        | I/O  | GPIO_A[0] / General purpose serial out 0                             |

| GPIO_B[29:28] | -                                                                          | 54:53                      | I/O  | GPIO_B[29:28]                                                        |

| GPIO_B[27:26] | USB_DP, USB_DN                                                             | 52:51                      | I/O  | GPIO_B[27:26] / USB_DP, USB_DN                                       |

| GPIO_B[25:21] | DAI<br>DAO<br>MCLK<br>LRCK<br>BCLK                                         | 68<br>67<br>66<br>63<br>62 | I/O  | GPIO_B[25:21] / I2S Interface Signals                                |

| GPIO_B[9:8]   | UT_RX / IDE_nCS1<br>UT_TX                                                  | 61<br>60                   | I/O  | GPIO_B[9:8] / UART Interface Signals<br>IDE chip select 1            |

| GPIO_B7       | ND_nWE                                                                     | 57                         | I/O  | GPIO_B7 / Write enable for NAND flash                                |

| GPIO_B[5:2]   | nCS[3:0]                                                                   | 50:47                      | I/O  | GPIO_B[5:2] / External Chip Select 3 ~ 0                             |

| GPIO_B1       | SD_nCS                                                                     | 46                         | I/O  | GPIO_B1 / Chip select for SDRAM                                      |

| GPIO_B0       | SD_CKE                                                                     | 56                         | I/O  | GPIO_B0 / SDRAM clock control                                        |

Dec. 16. 2002

Preliminary Spec 0.51

#### USB / UART / IrDA Interface

| Signal   | Shared Signal | NUM | Туре   | Description                        |

|----------|---------------|-----|--------|------------------------------------|

| USB D+   | GPIO_B26      | 51  | I/O    | USB Function D+ pin / GPIO_B26     |

| USB D-   | GPIO_B27      | 52  | I/O    | USB Function D- pin / GPIO_B27     |

| UART_TXD | GPIO_B8       | 60  | I/O    | UART or IrDA TX data pin / GPIO_B8 |

|          | GPIO_B9 /     | 61  | 61 I/O | UART or IrDA RX data pin / GPIO_B9 |

| UART_RXD | IDE_nCS1      | 01  |        | IDE chip select 1                  |

#### Audio Interface

| Signal   | Shared Signal | NUM | Туре | Description                                      |

|----------|---------------|-----|------|--------------------------------------------------|

| GPIO_B21 | BCLK          | 62  | I/O  | I2S Bit clock (64fs) / GPIO_B21                  |

| GPIO_B22 | LRCK          | 63  | I/O  | I2S Word clock / GPIO_B22                        |

| GPIO_B23 | MCLK          | 66  | I/O  | I2S system clock (256fs or 384fs) / GPIO_B23     |

| GPIO_B24 | DAO           | 67  | I/O  | I2S digital audio data output / GPIO_B24         |

| GPIO_B25 | DAI           | 68  | I/O  | I2S digital audio data input / GPIO_B25          |

| LCH_IN   | LCH_IN        | 90  | Ι    | ADC left channel input of internal audio CODEC   |

| RCH_IN   | RCH_IN        | 91  | Ι    | ADC right channel input of internal audio CODEC  |

| MIC_IN   | MIC_IN        | 92  | Ι    | Mic input of internal audio CODEC                |

| LCH_OUT  | LCH_OUT       | 93  | 0    | DAC left channel output of internal audio CODEC  |

| RCH_OUT  | RCH_OUT       | 94  | 0    | DAC right channel output of internal audio CODEC |

| VREF     | VREF          | 95  | 0    | Reference voltage of internal audio CODEC        |

#### **CD DSP Interface**

| Signal | Shared Signal | NUM | Туре | Description                        |

|--------|---------------|-----|------|------------------------------------|

| CBCLK  | GPIO_A1       | 105 | I/O  | CD Data Bit Clock Input / GPIO_A1  |

| CLRCK  | GPIO_A2       | 106 | I/O  | CD Data Word Clock Input / GPIO_A2 |

| CDAI   | GPIO_A3       | 107 | I/O  | CD Data input / GPIO_A3            |

#### **Clock Interface**

| Signal | Shared Signal | NUM | Туре | Description               |

|--------|---------------|-----|------|---------------------------|

| XIN    | -             | 74  | I    | Main clock input for PLL  |

| XOUT   | -             | 75  | 0    | Main clock output for PLL |

| XFILT  | -             | 78  | 0    | PLL filter output         |

| XTIN   | -             | 69  | I    | Sub clock input           |

| XTOUT  | -             | 70  | 0    | Sub clock output          |

#### **External Interrupt Interface**

| Signal     | Shared Signal                                | NUM                      | Туре | Description                                      |

|------------|----------------------------------------------|--------------------------|------|--------------------------------------------------|

| EXINT[3:0] | GPIO_A15<br>GPIO_A14<br>GPIO_A13<br>GPIO_A12 | 124<br>123<br>122<br>121 | I/O  | External interrupt request [3:0] / GPIO_A[15:12] |

#### Dec. 16. 2002

Preliminary Spec 0.51

#### **General Purpose ADC Interface**

| Signal    | Shared Signal | NUM   | Туре | Description                             |

|-----------|---------------|-------|------|-----------------------------------------|

| ADIN[2:0] | -             | 84:82 | I    | General purpose multi-channel ADC input |

#### Mode Control

| Signal | Shared Signal | NUM | Туре | Description          |

|--------|---------------|-----|------|----------------------|

| MODE1  | -             | 98  | I    | Mode Setting Input 1 |

| nRESET | -             | 72  | I    | System Reset         |

#### Power

| Signal | NUM            | Туре  | Description                       |

|--------|----------------|-------|-----------------------------------|

| 1/252  | 112<br>76      | DWD   |                                   |

| VDD3   | 64<br>33<br>16 | PWR   | Digital Power for I/O (3.3V)      |

|        | 119            |       |                                   |

|        | 109            |       |                                   |

| VDD2D  | 87<br>71       | PWR   | Digital Power for Internal (2.5V) |

| VDDZD  | 41             | I WIX | Digital Tower for Internal (2.5V) |

|        | 24             |       |                                   |

|        | 7              |       |                                   |

|        | 89             |       |                                   |

| VDD2A  | 81             | PWR   | Analog Power (2.5V)               |

|        | 77<br>97       |       |                                   |

|        | 65             |       |                                   |

| VSS3D  | 45             | PWR   | Digital Ground for I/O            |

|        | 32             |       |                                   |

|        | 1              |       |                                   |

|        | 120            |       |                                   |

|        | 110<br>88      |       |                                   |

| VSS2D  | 55             | PWR   | Digital Ground for Internal       |

|        | 25             |       |                                   |

|        | 8              |       |                                   |

|        | 96             |       |                                   |

| Veet   | 86             |       |                                   |

| VSSA   | 85<br>80       | PWR   | Analog Ground                     |

|        | 80<br>79       |       |                                   |

#### INTRODUCTION

32-bit RISC Microprocessor for Digital Media Player Dec. 16. 2002

Preliminary Spec 0.51

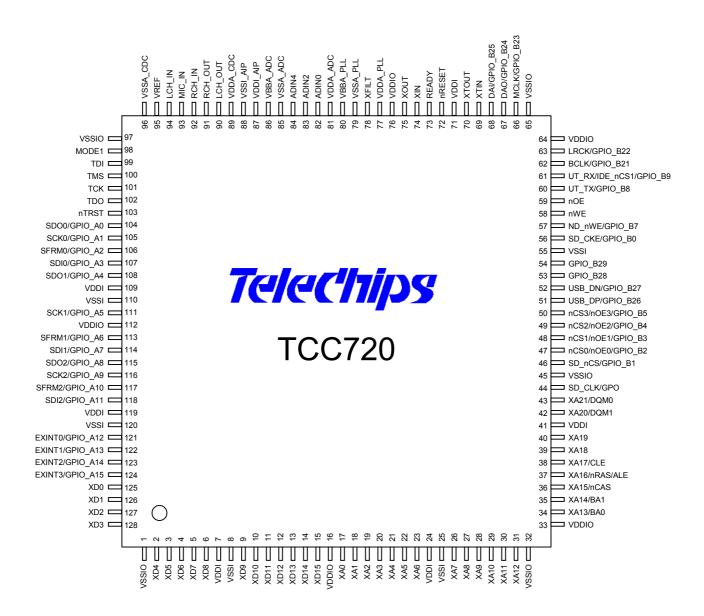

#### 1.3 Package Diagram

Figure 1.2 Package Diagram (128-TQFP-1414)

### **CHAPTER 2**

### **ADDRESS & REGISTER MAP**

Preliminary Spec 0.51

#### 2 ADDRESS & REGISTER MAP

#### 2.1 Address Map

The TCC720 has fixed address maps for digital audio en-decoder system. The address space is separated MSB 4bits of address bus, the following table represents overall address space of TCC720 system.

| Address Space           | Device Name                                             |  |  |  |

|-------------------------|---------------------------------------------------------|--|--|--|

|                         | internal or external ROM of chip select 3 (Remap == 0)  |  |  |  |

| 0x00000000 ~ 0x0FFFFFF  | Other type memory according to base value (Remap = 1)   |  |  |  |

|                         | Internal SRAM when any other memory is not assigned.    |  |  |  |

| 0x10000000 ~ 0x1FFFFFFF | Not Used                                                |  |  |  |

| 0x20000000 ~ 0x2FFFFFFF | Initial area for SDRAM                                  |  |  |  |

| 0x30000000 ~ 0x3FFFFFF  | Area of internal SRAM                                   |  |  |  |

| 0x40000000 ~ 0x4FFFFFFF | Initial area for chip select 0                          |  |  |  |

|                         | Initial configuration is for SRAM                       |  |  |  |

| 0x50000000 ~ 0x5FFFFFFF | Initial area for chip select 1                          |  |  |  |

|                         | Initial configuration is for IDE type device            |  |  |  |

| 0x60000000 ~ 0x6FFFFFF  | Initial area for chip select 2                          |  |  |  |

|                         | Initial configuration is for NAND flash                 |  |  |  |

| 0x70000000 ~ 0x7FFFFFF  | Initial area for chip select 3                          |  |  |  |

|                         | Initial configuration is for ROM                        |  |  |  |

| 0x80000000 ~ 0x8FFFFFF  | Various internal peripheral devices                     |  |  |  |

| 0x90000000 ~ 0x9FFFFFF  |                                                         |  |  |  |

| 0xA0000000 ~ 0xAFFFFFF  |                                                         |  |  |  |

| 0xB0000000 ~ 0xBFFFFFF  | Not Used                                                |  |  |  |

| 0xC0000000 ~ 0xCFFFFFF  |                                                         |  |  |  |

| 0xD0000000 ~ 0xDFFFFFF  |                                                         |  |  |  |

| 0xE0000000 ~ 0xEFFFFFFF | Area for internal boot ROM                              |  |  |  |

| 0xF0000000 ~ 0xFFFFFFFF | Area for memory controller configuration register space |  |  |  |

| Table 2.1 Address | Allocation I | Map of | f TCC720 |

|-------------------|--------------|--------|----------|

|                   | 7 1000010111 | map of | 100120   |

The address space ( $0x0000000 \sim 0x0FFFFFF$ ) is initially allocated to internal or external PROM for booting procedure, and a special flag is exist in memory controller unit for remapping lower half space to other type memories. Refer to the description of memory controller for

#### **ADDRESS & REGISTER MAP**

#### 32-bit RISC Microprocessor for Digital Media Player Dec. 16. 2002

Preliminary Spec 0.51

detailed operation.

TCC720 has only one chip select for SDRAM, so its address space is dependent on SDRAM size attached to TCC720.

TCC720 has various peripherals for controlling a digital audio en-decoder system. These peripherals can be configured appropriately by it's own registers that can be accessed through specially allocated address. These address maps are represented in the following table. In case of memory controller, its space is separated for preventing illegal accessing.

Refer to corresponding sections for detail information of each peripheral.

| Inal Tempherais (Base Address – 0x00000000) |

|---------------------------------------------|

| Peripheral                                  |

| DAI & CDIF                                  |

| Interrupt Controller                        |

| Timer Counter                               |

| GPIO                                        |

| Clock Generator & Power Management          |

| USB Function                                |

| UART/IrDA                                   |

| GSIO (General Purpose Serial Input/Output)  |

| -                                           |

| -                                           |

| Analog Control & Etc.                       |

| -                                           |

| -                                           |

| -                                           |

| DMA Controller                              |

| -                                           |

|                                             |

Table 2.2 Address Allocation for Internal Peripherals (Base Address = 0x8000000)

\*) Address decoding logic only monitors base address (i.e. 0x8xxxxxx), and bit11~bit8 of accessing address bus. So care must be taken not to modify these registers unintentionally.

#### ADDRESS & REGISTER MAP

32-bit RISC Microprocessor for Digital Media Player Dec. 16. 2002

Preliminary Spec 0.51

#### 2.2 Register Map

| Name    | Address | Туре | Reset  | Description                           |

|---------|---------|------|--------|---------------------------------------|

| DADI_L0 | 0x00    | R    | -      | Digital Audio Left Input Register 0   |

| DADI_R0 | 0x04    | R    | -      | Digital Audio Right Input Register 0  |

| DADI_L1 | 0x08    | R    | -      | Digital Audio Left Input Register 1   |

| DADI_R1 | 0x0C    | R    | -      | Digital Audio Right Input Register 1  |

| DADO_L0 | 0x10    | R/W  | -      | Digital Audio Left Output Register 0  |

| DADO_R0 | 0x14    | R/W  | -      | Digital Audio Right Output Register 0 |

| DADO_L1 | 0x18    | R/W  | -      | Digital Audio Left Output Register 1  |

| DADO_R1 | 0x1C    | R/W  | -      | Digital Audio Right Output Register 1 |

| DAMR    | 0x20    | R/W  | 0x0000 | Digital Audio Mode Register           |

| DAVC    | 0x24    | R/W  | 0x0000 | Digital Audio Volume Control Register |

| CDDI_0  | 0x80    | R    | -      | CD Digital Audio Input Register 0     |

| CDDI_1  | 0x84    | R    | -      | CD Digital Audio Input Register 1     |

| CICR    | 0x88    | R/W  | 0x0000 | CD Interface Control Register         |

#### DAI & CDIF Register Map (Base Address = 0x8000000)

#### Interrupt Controller Register Map (Base Address = 0x80000100)

| Name   | Address | Туре | Reset  | Description                               |

|--------|---------|------|--------|-------------------------------------------|

| IEN    | 0x00    | R/W  | 0x0000 | Interrupt Enable Register                 |

| CREQ   | 0x04    | W    | -      | Clear Interrupt Request Register          |

| IREQ   | 0x08    | R    | 0x0000 | Interrupt Request Flag Register           |

| IRQSEL | 0x0C    | R/W  | 0x0000 | IRQ/FIQ Select Register                   |

| ICFG   | 0x10    | R/W  | 0x0000 | External Interrupt Configuration Register |

| MREQ   | 0x14    | R    | 0x0000 | Masked Interrupt Request Flag Register    |

| IRQREQ | 0x18    | R    | 0x0000 | IRQ Interrupt Request Flag Register       |

| FIQREQ | 0x1C    | R    | 0x0000 | FIQ Interrupt Request Flag Register       |

Dec. 16. 2002

Preliminary Spec 0.51

#### Timer/Counter Register Map (Base Address = 0x80000200)

| Name   | Address | Туре | Reset   | Description                                |

|--------|---------|------|---------|--------------------------------------------|

| TCFG0  | 0x0000  | R/W  | 0x00    | Timer/Counter 0 Configuration Register     |

| TCNT0  | 0x0004  | R/W  | 0x0000  | Timer/Counter 0 Counter Register           |

| TREF0  | 0x0008  | R/W  | 0xFFFF  | Timer/Counter 0 Reference Register         |

| TMREF0 | 0x000C  | R/W  | 0x0000  | Timer/Counter 0 Middle Reference Register  |

| TCFG1  | 0x0010  | R/W  | 0x00    | Timer/Counter 1 Configuration Register     |

| TCNT1  | 0x0014  | R/W  | 0x0000  | Timer/Counter 1 Counter Register           |

| TREF1  | 0x0018  | R/W  | 0xFFFF  | Timer/Counter 1 Reference Register         |

| TMREF1 | 0x001C  | R/W  | 0x0000  | Timer/Counter 1 Middle Reference Register  |

| TCFG2  | 0x0020  | R/W  | 0x00    | Timer/Counter 2 Configuration Register     |

| TCNT2  | 0x0024  | R/W  | 0x0000  | Timer/Counter 2 Counter Register           |

| TREF2  | 0x0028  | R/W  | 0xFFFF  | Timer/Counter 2 Reference Register         |

| TMREF2 | 0x002C  | R/W  | 0x0000  | Timer/Counter 2 Middle Reference Register  |

| TCFG3  | 0x0030  | R/W  | 0x00    | Timer/Counter 3 Configuration Register     |

| TCNT3  | 0x0034  | R/W  | 0x0000  | Timer/Counter 3 Counter Register           |

| TREF3  | 0x0038  | R/W  | 0xFFFF  | Timer/Counter 3 Reference Register         |

| TMREF3 | 0x003C  | R/W  | 0x0000  | Timer/Counter 3 Middle Reference Register  |

| TCFG4  | 0x0040  | R/W  | 0x00    | Timer/Counter 4 Configuration Register     |

| TCNT4  | 0x0044  | R/W  | 0x00000 | Timer/Counter 4 Counter Register           |

| TREF4  | 0x0048  | R/W  | 0xFFFFF | Timer/Counter 4 Reference Register         |

| TCFG5  | 0x0050  | R/W  | 0x00    | Timer/Counter 5 Configuration Register     |

| TCNT5  | 0x0054  | R/W  | 0x00000 | Timer/Counter 5 Counter Register           |

| TREF5  | 0x0058  | R/W  | 0xFFFFF | Timer/Counter 5 Reference Register         |

| TIREQ  | 0x0060  | R/W  | 0x0000  | Timer/Counter n Interrupt Request Register |

| TWDCFG | 0x0070  | R/W  | 0x0000  | Watchdog Timer Configuration Register      |

| TWDCLR | 0x0074  | W    | -       | Watchdog Timer Clear Register              |

Dec. 16. 2002

Preliminary Spec 0.51

#### GPIO Register Map (Base Address = 0x80000300)

| Name     | Addr | Туре | Reset      | Description                       |

|----------|------|------|------------|-----------------------------------|

| GDATA_A  | 0x00 | R/W  | 0xFFFFFFFF | GPIO_A Data Register              |

| GIOCON_A | 0x04 | R/W  | 0xFFFF0000 | GPIO_A Direction Control Register |

| GSEL_A   | 0x08 | R/W  | 0x00000000 | GPIO_A Function Select Register   |

| GTSEL_A  | 0x0C | R/W  | 0x00000000 | GPIO_A Function Select Register 2 |

| GDATA_B  | 0x10 | R/W  | 0x3FFFFFFF | GPIO_B Data Register              |

| GIOCON_B | 0x14 | R/W  | 0x001FFCFF | GPIO_B Direction Control Register |

| GSEL_B   | 0x18 | R/W  | 0x3C0000BF | GPIO_B Function Select Register   |

| GTSEL_B  | 0x1C | R/W  | 0x0000000  | GPIO_B Function Select Register 2 |

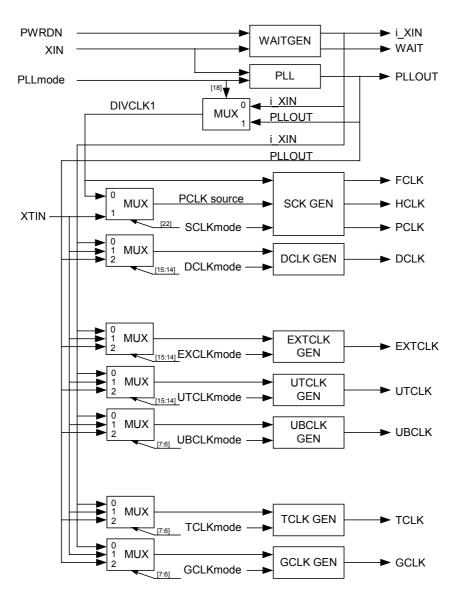

#### Clock Generator Register Map (Base Address = 0x80000400)

| Name       | Address | Туре | Reset     | Description                        |

|------------|---------|------|-----------|------------------------------------|

| CKCTRL     | 0x00    | R/W  | 0x0003FFE | Clock Control Register             |

| PLLMODE    | 0x04    | R/W  | 0x03806   | PLL Control Register               |

| SCLKmode   | 0x08    | R/W  | 0x082000  | System Clock Control Register      |

| DCLKmode   | 0x0C    | R/W  | 0x0800    | DCLK (DAI/CODEC) Control Register  |

| EXTCLKmode | 0x14    | R/W  | 0x0000    | EXTCLK (CD/Other) Control Register |

| UTCLKmode  | 0x18    | R/W  | 0x01BE    | UTCLK (UART) Control Register      |

| UBCLKmode  | 0x1C    | R/W  | 0x000     | UBCLK (USB) Control Register       |

| TCLKmode   | 0x24    | R/W  | 0x000     | TCLK (Timer) Control Register      |

| GCLKmode   | 0x28    | R/W  | 0x000     | GCLK (GSIO) Control Register       |

| SW_nRST    | 0x3C    | R/W  | 0x000     | Software Reset Control Register    |

Preliminary Spec 0.51

#### USB Register Map (Base Address = 0x80000500)

| Name    | Address | Туре | Reset | Description                     |

|---------|---------|------|-------|---------------------------------|

| UBFADR  | 0x00    |      |       | Function Address Register       |

| UBPWR   | 0x04    |      |       | Power Management Register       |

| UBIIR   | 0x08    |      |       | In-Interrupt Register           |

| UBOIR   | 0x10    |      |       | Out-Interrupt Register          |

| UBIR    | 0x18    |      |       | Interrupt Register              |

| UBIIEN  | 0x1C    |      |       | In-Interrupt Enable Register    |

| UBOIEN  | 0x24    |      |       | Out-Interrupt Enable Register   |

| UBIEN   | 0x2C    |      |       | Interrupt Enable Register       |

| UBFRM1  | 0x30    |      |       | Frame Number 1 Register         |

| UBFRM2  | 0x34    |      |       | Frame Number 2 Register         |

| UBIDX   | 0x38    |      |       | Index Register                  |

| INMXPn  | 0x40    |      |       | IN Max Packet Register          |

| INCSR1n | 0x44    |      |       | IN CSR1 Register                |

| INCSR2n | 0x48    |      |       | IN CSR2 Register                |

| OMXPn   | 0x4C    |      |       | OUT Max Packet Register         |

| OCSR1n  | 0x50    |      |       | OUT CSR1 Register               |

| OCSR2n  | 0x54    |      |       | OUT CSR2 Register               |

| OFIFO1n | 0x58    |      |       | OUT FIFO Write Count 1 Register |

| OFIFO2n | 0x5C    |      |       | OUT FIFO Write Count 2 Register |

| EP0FIFO | 0x80    |      |       | EP0 FIFO Register               |

| EP1FIFO | 0x84    |      |       | EP1 FIFO Register               |

| EP2FIFO | 0x88    |      |       | EP2 FIFO Register               |

Dec. 16. 2002

Preliminary Spec 0.51

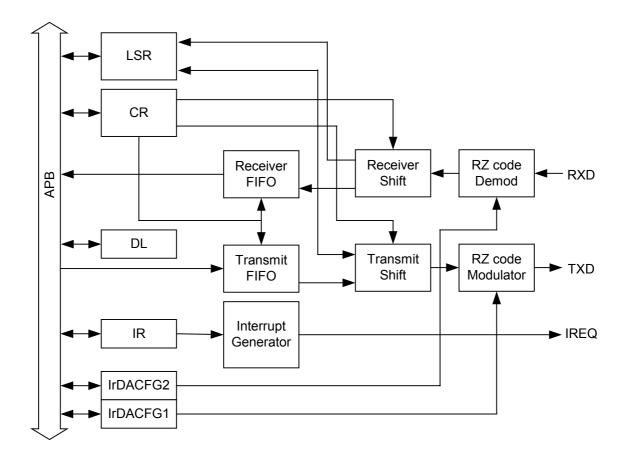

#### UART/IrDA Register Map (Base Address = 0x80000600)

| Name     | Address | Туре | Reset  | Description                   |

|----------|---------|------|--------|-------------------------------|

| RB       | 0x00    | R    | -      | Receiver Buffer Register      |

| THR      | 0x00    | W    | -      | Transmitter Holding Register  |

| DL       | 0x04    | W    | 0x0000 | Divisor Latch Register        |

| IR       | 0x08    | R/W  | 0x000  | Interrupt Register            |

| CR       | 0x0C    | R/W  | 0x000  | UART Control Register         |

| LSR      | 0x10    | R    | 0x0101 | Status Register               |

| IrDACFG1 | 0x14    | R/W  | 0x0003 | IrDA Configuration Register 1 |

| IrDACFG2 | 0x18    | R/W  | 0x4da1 | IrDA Configuration Register 2 |

#### GSIO Register Map (Base Address = 0x80000700)

| Name  | Address | Туре | Reset | Description                     |

|-------|---------|------|-------|---------------------------------|

| GSDO0 | 0x00    | R/W  |       | GSIO0 Output Data Register      |

| GSDI0 | 0x04    | R/W  |       | GSIO0 Input Data Register       |

| GSCR0 | 0x08    | R/W  |       | GSIO0 Control Register          |

| GSICR | 0x0C    | R/W  |       | GSIO Interrupt Control Register |

| GSDO1 | 0x10    | R/W  |       | GSIO1 Output Data Register      |

| GSDI1 | 0x14    | R/W  |       | GSIO1 Input Data Register       |

| GSCR1 | 0x18    | R/W  |       | GSIO1 Control Register          |

| GSDO2 | 0x20    | R/W  |       | GSIO2 Output Data Register      |

| GSDI2 | 0x24    | R/W  |       | GSIO2 Input Data Register       |

| GSCR2 | 0x28    | R/W  |       | GSIO2 Control Register          |

| GSDO3 | 0x30    | R/W  |       | GSIO3 Output Data Register      |

| GSDI3 | 0x34    | R/W  |       | GSIO3 Input Data Register       |

| GSCR3 | 0x38    | R/W  |       | GSIO3 Control Register          |

Dec. 16. 2002

Preliminary Spec 0.51

#### Analog Interface & ETC Register Map (Base Address = 0x80000A00)

| Name    | Address | Туре | Reset | Description                                |

|---------|---------|------|-------|--------------------------------------------|

| ADCTR   | 0x00    | R/W  | 0     | ADC Control Register                       |

| ADDATA  | 0x04    | R    | -     | ADC Data Register                          |

| CDCTR   | 0x08    | R/W  | 0     | Codec Control Register                     |

| CDCGAIN | 0x0C    | R/W  | 0     | Codec Gain Register                        |

| LZC     | 0x10    | R/W  | -     | Leading Zero Counter Register              |

| USBCTR  | 0x14    | R/W  | 0     | USB Port Control Register                  |

| TSTSEL  | 0x18    | R/W  | 0     | Test Mode Register (must be remained zero) |

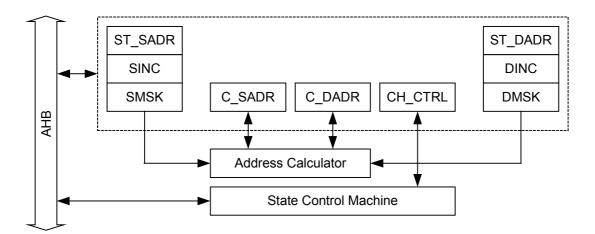

#### DMA Controller Register Map (Base Address = 0x80000E00)

| Name    | Address   | Туре | Reset      | Description                          |

|---------|-----------|------|------------|--------------------------------------|

| ST_SADR | 0x00      | R/W  | -          | Start Address of Source Block        |

| SPARAM  | 0x04/0x08 | R/W  | -          | Parameter of Source Block            |

| C_SADR  | 0x0C      | R    | -          | Current Address of Source Block      |

| ST_DADR | 0x10      | R/W  | -          | Start Address of Destination Block   |

| DPARAM  | 0x14/0x18 | R/W  | -          | Parameter of Destination Block       |

| C_DADR  | 0x1C      | R    | -          | Current Address of Destination Block |

| HCOUNT  | 0x20      | R/W  | 0x00000000 | Initial and Current Hop count        |

| CHCTRL  | 0x24      | R/W  | 0x00000000 | Channel Configuration                |

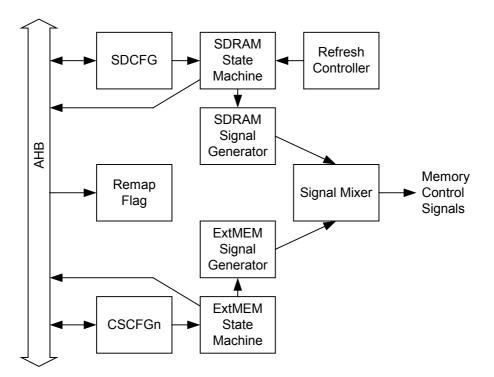

#### Memory Controller Register Map (Base Address = 0xF0000000)

| Name   | Address | Туре | Reset       | Description                                |

|--------|---------|------|-------------|--------------------------------------------|

| SDCFG  | 0x00    | R/W  | 0x4268A020  | SDRAM Configuration Register               |

| SDFSM  | 0x04    | R    | -           | SDRAM FSM Status Register                  |

| MCFG   | 0x08    | R/W  | 0xZZZZ_02   | Miscellaneous Configuration Register       |

| TST    | 0x0C    | W    | 0x0000      | Test mode register (must be remained zero) |

| CSCFG0 | 0x10    | R/W  | 0x0B405601  | External Chip Select 0 Configuration       |

|        |         |      | 0X00403001  | Register (Initially set to SRAM)           |

| CSCFG1 | 0x14    | R/W  | 0x0150569A  | External Chip Select 1 Configuration       |

|        |         |      | 0X0150509A  | Register (Initially set to IDE)            |

| CSCFG2 | 0x18    | R/W  | 0x0060569A  | External Chip Select 2 Configuration       |

|        |         |      | 0X0000309A  | Register (Initially set to NAND)           |

| CSCFG3 | 0x1C    | R/W  | 0x0A70569A  | External Chip Select 3 Configuration       |

|        |         |      | UXUA7 U309A | Register (Initially set to NOR)            |

#### ADDRESS & REGISTER MAP

32-bit RISC Microprocessor for Digital Media Player Dec. 16. 2002

Preliminary Spec 0.51

#### NAND flash Register Map (Base Address = N \* 0x1000000)

| Name  | Address | Туре | Reset | Description                   |

|-------|---------|------|-------|-------------------------------|

| CMD   | 0x00    | R/W  | -     | Command Cycle Register        |

| LADDR | 0x04    | W    | -     | Linear Address Cycle Register |

| BADDR | 0x08    | W    | -     | Block Address Cycle Register  |

| IADDR | 0x0C    | W    | -     | Single Address Cycle Register |

| DATA  | 0x10    | R/W  | -     | Data Access Cycle Register    |

\*) N represents BASE field of CSCFGn registers.

### **CHAPTER 3**

**DAI & CDIF**

#### 3 DAI (Digital Audio Interface) & CDIF (CD-DSP Interface)

#### 3.1 DAI

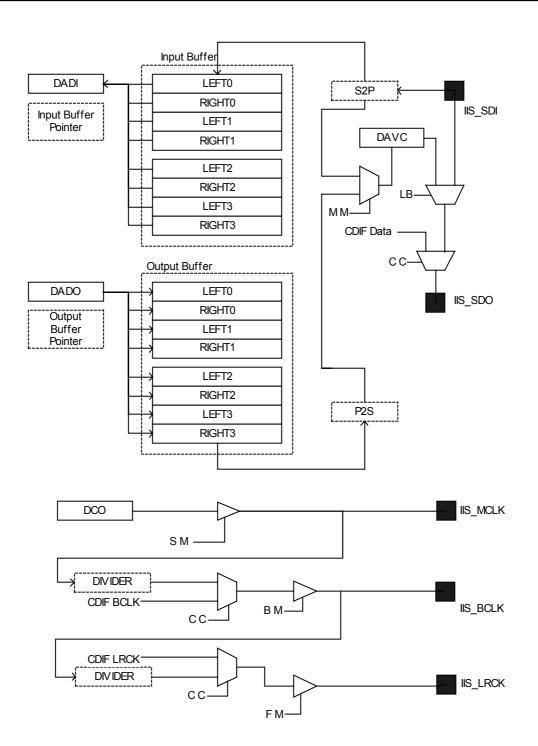

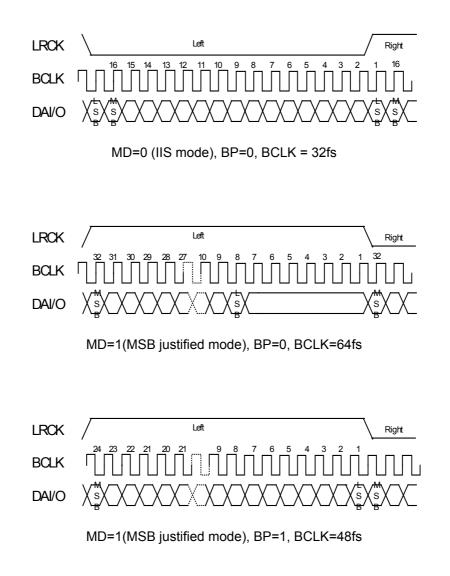

The TCC720 provides digital audio interface that complies with IIS (Inter-IC Sound). The DAI has five input/output pins for IIS interface; MCLK, BCLK, LRCK, DAI, DAO. All DAI input/output pins are multiplexed with GPIO pins; GPIO\_B<21:25>. The MCLK is the system clock pin that is used for CODEC system clock. The DAI provides 256fs, 384fs and 512fs as a system clock. 256fs means that 256 times of sampling frequency fs. The BCLK is the serial bit clock for IIS data exchange. The DAI can generate 64fs, 48fs and 32fs by dividing a system clock. The polarity of BCLK can be programmed. The LRCK is the frame clock for the audio channel Left and Right. The frequency of LRCK is the "fs" – sampling frequency. Generally, for audio application – such as MP3 Player , CD player, the fs can be set to 8kHz, 16kHz, 11.05kHz, 24kHz, 32kHz, 44.1kHz and 48kHz. For supporting the wide range of sampling frequency in audio application, the DCO function is very useful to generate a system clock. Refer Chap. 7 for detail information. All three clocks are selectable as master or slave. The DAI, DAO are the serial data input output pins respectively.

The DAI has two 8-word input/output buffers. The buffers can be read/written through the DADI/DADO. The hidden buffer pointers automatically increment when user read/write from/to the DADI/DADO. The maximum data word size is 24 bit. Data is justified to MSB of 32bits and zeros are padded to LSB.

There are 2 types of interrupt from IIS; transmit done interrupt, receive done interrupt. The transmit-done interrupt is generated when the 4 words are transferred successfully in the output buffer. At this interrupt, user should fill another 4 more words into the other part of the output buffer in the interrupt service routine (ISR). In this ISR routine, 4 consecutive stores of word data to the DADO is needed – sequence is that the left channel is the first and right channel. The receive-done interrupt is generated when the 4 words are received successfully in the input buffer. At this interrupt, user should read 4 received words from the input buffer using 4 consecutive load instructions from the DADI – sequence is that the left channel is the first.

Dec. 16. 2002

Preliminary Spec 0.51

#### DAI Register Map (Base Address = 0x8000000)

| Name    | Address | Туре | Reset  | Description                           |

|---------|---------|------|--------|---------------------------------------|

| DADI_L0 | 0x00    | R    | -      | Digital Audio Left Input Register 0   |

| DADI_R0 | 0x04    | R    | -      | Digital Audio Right Input Register 0  |

| DADI_L1 | 0x08    | R    | -      | Digital Audio Left Input Register 1   |

| DADI_R1 | 0x0C    | R    | -      | Digital Audio Right Input Register 1  |

| DADO_L0 | 0x10    | R/W  | -      | Digital Audio Left Output Register 0  |

| DADO_R0 | 0x14    | R/W  | -      | Digital Audio Right Output Register 0 |

| DADO_L1 | 0x18    | R/W  | -      | Digital Audio Left Output Register 1  |

| DADO_R1 | 0x1C    | R/W  | -      | Digital Audio Right Output Register 1 |

| DAMR    | 0x20    | R    | 0x0000 | Digital Audio Mode Register           |

| DAVC    | 0x24    | R/W  | 0x0000 | Digital Audio Volume Control Register |

Dec. 16. 2002

| Digita | l Aud | io Mo | de Re | gister | · (DAN | /IR) |      |       |      |     |      |    | 0  | x8000 | 0020 |

|--------|-------|-------|-------|--------|--------|------|------|-------|------|-----|------|----|----|-------|------|

| 31     | 30    | 29    | 28    | 27     | 26     | 25   | 24   | 23    | 22   | 21  | 20   | 19 | 18 | 17    | 16   |

|        |       |       |       |        |        |      | Rese | erved |      |     |      |    |    |       |      |

| 15     | 14    | 13    | 12    | 11     | 10     | 9    | 8    | 7     | 6    | 5   | 4    | 3  | 2  | 1     | 0    |

| EN     | TE    | RE    | MD    | SM     | BM     | FM   | CC   | BD<   | 1:0> | FD< | 1:0> | BP | СМ | MM    | LB   |

| EN [15] | DAI Master Enable |

|---------|-------------------|

| 0       | DAI disabled      |

| 1       | DAI enabled       |

| TE [14] | DAI Transmitter Enable   |

|---------|--------------------------|

| 0       | DAI transmitter disabled |

| 1       | DAI transmitter enabled  |

| RE [13] | DAI Receiver Enable   |

|---------|-----------------------|

| 0       | DAI receiver disabled |

| 1       | DAI receiver enabled  |

| MD [12] | DAI Bus Mode               |

|---------|----------------------------|

| 0       | DAI has IIS bus mode       |

| 1       | DAI has MSB justified mode |

| SM [11] | DAI System Clock Master Select                             |

|---------|------------------------------------------------------------|

| 0       | DAI system clock is come from external pin                 |

| 1       | DAI system clock is generated by the clock generator block |

| BM [10] | DAI Bit Clock Master Select                             |

|---------|---------------------------------------------------------|

| 0       | DAI bit clock is come from external pin                 |

| 1       | DAI bit clock is generated by dividing DAI system clock |

| FM [9] | DAI Frame Clock Master Select                          |

|--------|--------------------------------------------------------|

| 0      | DAI frame clock is come from external pin              |

| 1      | DAI frame clock is generated by dividing DAI bit clock |

#### **DAI & CDIF**

#### 32-bit RISC Microprocessor for Digital Media Player

Dec. 16. 2002

| CC [8] | CDIF Clock Select               |

|--------|---------------------------------|

| 0      | CDIF Clock master mode disabled |

| 1      | CDIF Clock master mode enabled. |

| BD [7:6] | DAI Bit Clock Divider select                |

|----------|---------------------------------------------|

| 00       | Div 4(256fs->64fs)                          |

| 01       | Div 6(384fs->64fs)                          |

| 10       | Div 8(512fs->64fs, 384fs->48fs,256fs->32fs) |

| 11       | Div16 ( 512fs->32fs )                       |

| FD [5:4] | DAI Frame Clock Divider select |

|----------|--------------------------------|

| 00       | Div 32 ( 32fs->fs )            |

| 01       | Div 48 ( 48fs->fs )            |

| 10       | Div 64 ( 64fs->fs )            |

| BP [3] | DAI Bit Clock Polarity                         |

|--------|------------------------------------------------|

| 0      | Data is captured at positive edge of bit clock |

| 1      | Data is captured at negative edge of bit clock |

| CM [2] | CDIF Monitor Mode                                   |

|--------|-----------------------------------------------------|

| 0      | CDIF monitor mode is disabled                       |

| 1      | CDIF monitor mode is enabled. Data bypass from CDIF |

| MM [1] | DAI Monitor Mode                                  |

|--------|---------------------------------------------------|

| 0      | DAI monitor mode is disabled                      |

| 1      | DAI monitor mode is enabled. TE should be enabled |

| LB [0] | DAI Loop-back Mode             |

|--------|--------------------------------|

| 0      | DAI Loop back mode is disabled |

| 1      | DAI Loop back mode is enabled  |

Dec. 16. 2002

| Digita | Digital Audio Volume Control Register (DAVC) |    |    |    |    |    |    |    |    |    |    |    |     | 0x80000024 |    |  |

|--------|----------------------------------------------|----|----|----|----|----|----|----|----|----|----|----|-----|------------|----|--|

| 31     | 30                                           | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18  | 17         | 16 |  |

|        | Reserved                                     |    |    |    |    |    |    |    |    |    |    |    |     |            |    |  |

| 15     | 14                                           | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2   | 1          | 0  |  |

|        | Reserved                                     |    |    |    |    |    |    |    |    |    |    |    | VC< | 3:0>       |    |  |

| VC [3:0] | DAI Volume control |

|----------|--------------------|

| 0000     | 0dB                |

| 0001     | -6dB               |

| 0010     | -12dB              |

| 0011     | -18dB              |

| 0100     | -24dB              |

| 0101     | -30dB              |

| 0110     | -36dB              |

| 0111     | -42dB              |

| 1000     | -48dB              |

| 1001     | -54dB              |

| 1010     | -60dB              |

| 1011     | -66dB              |

| 1100     | -72dB              |

| 1101     | -78dB              |

| 1110     | -84dB              |

| 1111     | -90dB              |

32-bit RISC Microprocessor for Digital Media Player

Dec. 16. 2002

Preliminary Spec 0.51

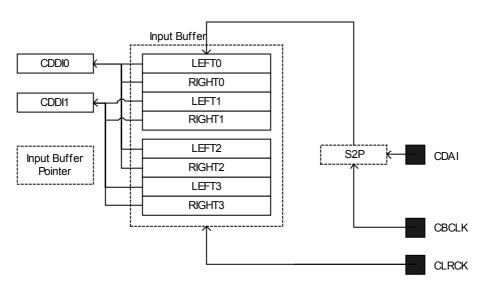

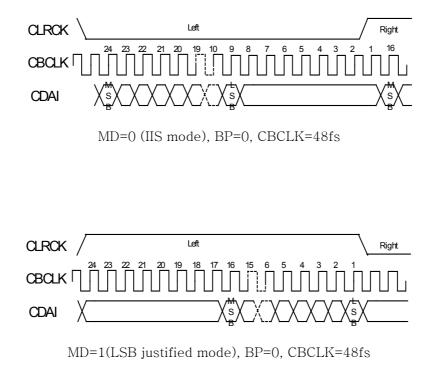

Figure 3.1 DAI Block Diagram

Figure 3.2 DAI Bus Timing Diagram

#### Preliminary Spec 0.51

#### 3.2 CDIF

The TCC720 provides CD-ROM interface for feasible implementation of CD-ROM application such as CD-MP3 player. The CDIF supports the industry standard IIS format and the LSB justified format that is used as the most popular format for CD-ROM interface by Sony and Samsung. The CDIF has three pins for interface; CBCLK, CLRCK, CDAI that are multiplexed with GPIO B14, GPIO\_B15 and GPIO\_B16, respectively. The CBCLK is the bit clock input pins of which frequency can be programmed by CICR for selection of 48fs and 32fs. The CLRCK is the frame clock input pin that indicates the channel of CD digital audio data. The CDAI is the input data pin.

The CDIF has three registers; CDDI\_0, CDDI\_1 and CICR. The CDDI\_0 and the CDDI\_1 are the banked read only registers for access of data input buffer. The data input buffer is composed of four 32 bit wide registers of which upper 16 bit is left channel data and lower is right channel data. The CDIF receive the serial data from CDAI pin and store the data into the buffer through the serial to parallel register. Whenever the half of buffer is filled, the receive interrupt is generated. Only the half of input buffer can be accessible through the CDDI\_0 and the CDDI 1.

| Name   | Address | Туре | Reset  | Description                       |  |  |  |  |  |

|--------|---------|------|--------|-----------------------------------|--|--|--|--|--|

| CDDI_0 | 0x80    | R    |        | CD Digital Audio Input Register 0 |  |  |  |  |  |

| CDDI_1 | 0x84    | R    |        | CD Digital Audio Input Register 1 |  |  |  |  |  |

| CICR   | 0x88    | R/W  | 0x0000 | CD Interface Control Register     |  |  |  |  |  |

#### CDIF Register Map (Base Address = 0x8000000)

#### CD Data Input (CDDI0)

| CD Da | CD Data Input (CDDI0) 0x8000080 |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|-------|---------------------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| 31    | 30                              | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|       | Left Channel Data               |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| 15    | 14                              | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|       | Right Channel Data              |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

#### CD Data Input (CDDI1)

| CD Da | CD Data Input (CDDI1) 0x80000084 |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|-------|----------------------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| 31    | 30                               | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|       | Left Channel Data                |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| 15    | 14                               | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|       | Right Channel Data               |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

Dec. 16. 2002

| CD Ir    | CD Interface Control Register (CICR) 0x800008 |    |    |    |    |    |    |    |             |    |    |    |    | 88000 |    |

|----------|-----------------------------------------------|----|----|----|----|----|----|----|-------------|----|----|----|----|-------|----|

| 31       | 30                                            | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22          | 21 | 20 | 19 | 18 | 17    | 16 |

|          | Reserved                                      |    |    |    |    |    |    |    |             |    |    |    |    |       |    |

| 15       | 14                                            | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6           | 5  | 4  | 3  | 2  | 1     | 0  |

| Reserved |                                               |    |    |    |    |    |    | EN | Reserved BS |    |    | S  | MD | BP    |    |

| EN [7] | CDIF Enable   |

|--------|---------------|

| 0      | CDIF disabled |

| 1      | CDIF enabled  |

| BS [3:2] | CDIF Bit Clock select |

|----------|-----------------------|

| 00       | 64fs                  |

| 01       | 32fs                  |

| 10       | 48fs                  |

| MD [1] | Interface Mode select |

|--------|-----------------------|

| 0      | IIS format            |

| 1      | LSB justified format  |

| BP [3] | CDIF Bit Clock Polarity                        |

|--------|------------------------------------------------|

| 0      | Data is captured at positive edge of bit clock |

| 1      | Data is captured at negative edge of bit clock |

32-bit RISC Microprocessor for Digital Media Player Dec. 16. 2002

Figure 3.3. CDIF Block Diagram

Figure 3.3 CDIF Bus Timing Diagram

**CHAPTER 4**

### **INTERRUPT CONTROLLER**

Preliminary Spec 0.51

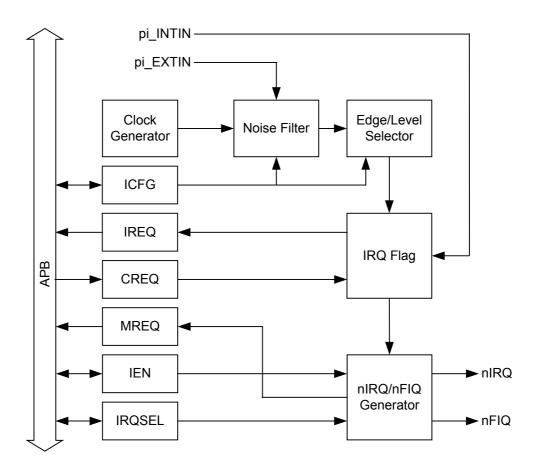

#### 4 INTERRUPT CONTROLLER

#### 4.1 Overview

Interrupt controller can manage up to 16 interrupt sources. In TCC720, there are 4 external interrupt sources that can be detected various kind of method, that is a rising edge/ falling edge / level high / level low detection can be set for external interrupt sources. External interrupt sources can be reliably managed with noise filtering up to 100 ~ 400 us.

There are two types of interrupt in ARM940T, IRQ type, FIQ type. Interrupt controller can manage these two types for each interrupt sources separately.

The following figure represents the block diagram of interrupt controller.

#### 32-bit RISC Microprocessor for Digital Media Player

Dec. 16. 2002

Preliminary Spec 0.51

#### 4.2 Register Description

#### Interrupt Controller Register Map (Base Address = 0x80000100)

| Name   | Address | Туре | Reset  | Description                                |

|--------|---------|------|--------|--------------------------------------------|

| IEN    | 0x00    | R/W  | 0x0000 | Interrupt Enable Register                  |

| CREQ   | 0x04    | W    | -      | Clear Interrupt Request Register           |

| IREQ   | 0x08    | R    | 0x0000 | Interrupt Request Flag Register            |

| IRQSEL | 0x0C    | R/W  | 0x0000 | IRQ/FIQ Select Register                    |

| ICFG   | 0x10    | R/W  | 0x0000 | External Interrupt Configuration Register  |

| MREQ   | 0x14    | R    | 0x0000 | Masked Interrupt Request Flag Register     |

| TSTREQ | 0x18    | R/W  | 0x0000 | Test Mode Register (must be remained zero) |

#### Interrupt Enable Register (IEN)

#### 0x80000100

| 15  | 14 | 13  | 12  | 11   | 10 | 9  | 8  | 7  | 6  | 5   | 4   | 3  | 2  | 1  | 0  |

|-----|----|-----|-----|------|----|----|----|----|----|-----|-----|----|----|----|----|

| MEN | -  | DMA | LCD | CDIF | -  | GS | UB | UT | тс | I2T | I2R | E3 | E2 | E1 | E0 |

| MEN [15] | Master Enable                                                         |

|----------|-----------------------------------------------------------------------|

| 0        | All interrupts are disabled                                           |

| 1        | All interrupt enabled by corresponding bit[14:0] can be passed to CPU |

| Bit Field         | Each Interrupt Request Control                |

|-------------------|-----------------------------------------------|

|                   | 1 = Interrupt enabled, 0 = Interrupt disabled |

| DMA [13]          | DMA interrupt control                         |

| LCD [12]          | LCD interrupt control                         |

| CDIF [11]         | CDIF interrupt control                        |

| [10]              | Not used                                      |

| GS <sub>[9]</sub> | GSIO interrupt control                        |

| UB <sub>[8]</sub> | USB interrupt control                         |

| UT [7]            | UART/IrDA interrupt control                   |

| TC [6]            | Timer/Counter interrupt control               |

| I2T [5]           | I2S TX interrupt control                      |

| I2R [4]           | I2S RX interrupt control                      |

| E3 <sub>[3]</sub> | External interrupt request 3 control          |

| E2 [2]            | External interrupt request 2 control          |

| E1 [1] | External interrupt request 1 control |

|--------|--------------------------------------|

| E0 [0] | External interrupt request 0 control |

#### **Clear Interrupt Request Register (CREQ)**

32-bit RISC Microprocessor for Digital Media Player

| 15 | 14 | 13  | 12  | 11   | 10 | 9  | 8  | 7  | 6  | 5   | 4   | 3  | 2  | 1  | 0  |

|----|----|-----|-----|------|----|----|----|----|----|-----|-----|----|----|----|----|

| -  | -  | DMA | LCD | CDIF | -  | GS | UB | UT | тс | I2T | I2R | E3 | E2 | E1 | E0 |

\*) When writing "1" to each field, the interrupt request flag of corresponding interrupt is cleared.

#### Interrupt Request Register (IREQ)

| I | Interrupt Request Register (IREQ) 0x8000010 |    |     |     |      |    |    |    |    |    |     |     |    |    | 0108 |    |

|---|---------------------------------------------|----|-----|-----|------|----|----|----|----|----|-----|-----|----|----|------|----|

|   | 15                                          | 14 | 13  | 12  | 11   | 10 | 9  | 8  | 7  | 6  | 5   | 4   | 3  | 2  | 1    | 0  |

|   | -                                           | -  | DMA | LCD | CDIF | -  | GS | UB | UT | тс | I2T | I2R | E3 | E2 | E1   | E0 |

\*) When each field is "1", the corresponding interrupt has been requested and not cleared.

#### **IRQ Interrupt Select Register (IRQSEL)**

| 15 | 14 | 13  | 12  | 11   | 10 | 9  | 8  | 7  | 6  | 5   | 4   | 3  | 2  | 1  | 0  |

|----|----|-----|-----|------|----|----|----|----|----|-----|-----|----|----|----|----|

| -  | -  | DMA | LCD | CDIF | -  | GS | UB | UT | тс | I2T | I2R | E3 | E2 | E1 | E0 |

\*) When each field is "1", the corresponding interrupt is considered as IRQ interrupt, otherwise as FIQ interrupt.

#### **External Interrupt Configuration Register (ICFG)**

| 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| FE3 | DTY | PE3 | FT3 | FE2 | DTY | PE2 | FT2 | FE1 | DTY | PE1 | FT1 | FE0 | DTY | PE0 | FT0 |

| FE3~FE0 | Filter Enable                                     |

|---------|---------------------------------------------------|

| 0       | Noise filter is enabled (in case of DTYPEn != 3)  |

| 1       | Noise filter is disabled (in case of DTYPEn != 3) |

\*) If DTYPEn == 3, noise filter is always enabled, and this field sets which level generates the interrupt. If it is set to 1, level high triggers interrupt, and if it is set to 0, level low triggers interrupt.

| DTYPE3~0 | Detection Type                                                                                                                                                                                              |  |  |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 0        | Falling edge triggered external interrupt                                                                                                                                                                   |  |  |  |

| 1        | Rising edge triggered external interrupt                                                                                                                                                                    |  |  |  |

| 2        | Both edge triggered external interrupt                                                                                                                                                                      |  |  |  |

| 3        | Level high / low triggered external interrupt<br>FEn field determines which level triggers the interrupt. If FEn == 1, level high<br>triggers the interrupt and FEn == 0, level low triggers the interrupt. |  |  |  |

### TeleChips

### INTERRUPT CONTROLLER

### Preliminary Spec 0.51

#### 0x8000010C

0x80000110

### **TCC720**

Dec. 16. 2002

0x80000104

# **TCC720**

# INTERRUPT CONTROLLER

## 32-bit RISC Microprocessor for Digital Media Player

Dec. 16. 2002

#### Preliminary Spec 0.51

| FT3~FT0 | Filter Type                                                                    |  |  |  |  |  |  |  |  |  |  |

|---------|--------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|

| 0       | Clock based filter is used. The filter delay is proportional to PCLK period as |  |  |  |  |  |  |  |  |  |  |

|         | the following equations.                                                       |  |  |  |  |  |  |  |  |  |  |

|         | Filter Delay = T <sub>PCLK</sub> * 64                                          |  |  |  |  |  |  |  |  |  |  |

|         | If PCLK has 25MHz, then the filter delay has about 16us.                       |  |  |  |  |  |  |  |  |  |  |

| 1       | Delay cell based filter is used. The filter delay varies on the operating      |  |  |  |  |  |  |  |  |  |  |

|         | conditions, like voltage, temperature, etc.                                    |  |  |  |  |  |  |  |  |  |  |

|         | The nominal delay is about 120ns.                                              |  |  |  |  |  |  |  |  |  |  |

|         | This type of filter must be selected when the PCLK has to be stopped, as like  |  |  |  |  |  |  |  |  |  |  |

|         | as stop mode etc.                                                              |  |  |  |  |  |  |  |  |  |  |

#### Masked Interrupt Request Register (MREQ)

### 0x80000114

| 15 | 14 | 13  | 12  | 11   | 10 | 9  | 8  | 7  | 6  | 5   | 4   | 3  | 2  | 1  | 0  |

|----|----|-----|-----|------|----|----|----|----|----|-----|-----|----|----|----|----|

| -  | -  | DMA | LCD | CDIF | -  | GS | UB | UT | тс | I2T | I2R | E3 | E2 | E1 | E0 |

\*) Same meaning as IREQ except that it represents only the enabled interrupt's request.

**CHAPTER 5**

**TIMER / COUNTER**

### 5 TIMER / COUNTER

#### 5.1 Overview

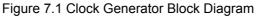

The TCC720 has four 16bit and two 20bit timer counter. Each timer counter has 3 registers for various operation modes. Refer to register description table for details. When operating in counter modes, External interrupt pin is used as counting clock for that counter.

The main clock frequency of timer counter can be configured by setting TCLK frequency. (Refer to Clock generator block) With the 12bit internal basic counter, the timer counter can generate various intervals from micro-seconds to seconds unit.

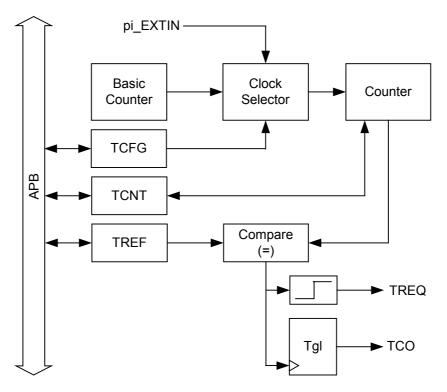

The following figure represents the block diagram of timer counter.

Figure 5.1 Timer Counter Block Diagram

The following table explains the three registers of each timer counter. The address of each timer counter is 16bytes aligned. The base address of timer counter is 0x80000200.

The number n represents for each timer/counter. In case of timer/counter 4, 5 (that is n = 4 or 5)

#### 32-bit RISC Microprocessor for Digital Media Player Dec. 16. 2002

Preliminary Spec 0.51

the TREF, TCNT register has 20bit resolution. It can be used for generation of a long time period.

### 5.2 Register Description

#### Timer/Counter Register Map (Base Address = 0x80000200)

| Name   | Address | Туре | Reset   | Description                                |

|--------|---------|------|---------|--------------------------------------------|

| TCFG0  | 0x0000  | R/W  | 0x00    | Timer/Counter 0 Configuration Register     |

| TCNT0  | 0x0004  | R/W  | 0x0000  | Timer/Counter 0 Counter Register           |

| TREF0  | 0x0008  | R/W  | 0xFFFF  | Timer/Counter 0 Reference Register         |

| TMREF0 | 0x000C  | R/W  | 0x0000  | Timer/Counter 0 Middle Reference Register  |

| TCFG1  | 0x0010  | R/W  | 0x00    | Timer/Counter 1 Configuration Register     |

| TCNT1  | 0x0014  | R/W  | 0x0000  | Timer/Counter 1 Counter Register           |

| TREF1  | 0x0018  | R/W  | 0xFFFF  | Timer/Counter 1 Reference Register         |

| TMREF1 | 0x001C  | R/W  | 0x0000  | Timer/Counter 1 Middle Reference Register  |

| TCFG2  | 0x0020  | R/W  | 0x00    | Timer/Counter 2 Configuration Register     |

| TCNT2  | 0x0024  | R/W  | 0x0000  | Timer/Counter 2 Counter Register           |

| TREF2  | 0x0028  | R/W  | 0xFFFF  | Timer/Counter 2 Reference Register         |

| TMREF2 | 0x002C  | R/W  | 0x0000  | Timer/Counter 2 Middle Reference Register  |

| TCFG3  | 0x0030  | R/W  | 0x00    | Timer/Counter 3 Configuration Register     |

| TCNT3  | 0x0034  | R/W  | 0x0000  | Timer/Counter 3 Counter Register           |

| TREF3  | 0x0038  | R/W  | 0xFFFF  | Timer/Counter 3 Reference Register         |

| TMREF3 | 0x003C  | R/W  | 0x0000  | Timer/Counter 3 Middle Reference Register  |

| TCFG4  | 0x0040  | R/W  | 0x00    | Timer/Counter 4 Configuration Register     |

| TCNT4  | 0x0044  | R/W  | 0x00000 | Timer/Counter 4 Counter Register           |

| TREF4  | 0x0048  | R/W  | 0xFFFFF | Timer/Counter 4 Reference Register         |

| TCFG5  | 0x0050  | R/W  | 0x00    | Timer/Counter 5 Configuration Register     |

| TCNT5  | 0x0054  | R/W  | 0x00000 | Timer/Counter 5 Counter Register           |

| TREF5  | 0x0058  | R/W  | 0xFFFFF | Timer/Counter 5 Reference Register         |

| TIREQ  | 0x0060  | R/W  | 0x0000  | Timer/Counter n Interrupt Request Register |

| TWDCFG | 0x0070  | R/W  | 0x0000  | Watchdog Timer Configuration Register      |

| TWDCLR | 0x0074  | W    | -       | Watchdog Timer Clear Register              |

TeleChips

# **TIMER / COUNTER**

## 32-bit RISC Microprocessor for Digital Media Player

Dec. 16. 2002

#### Preliminary Spec 0.51

| Time | Timer/Counter n Configuration Register (TCFGn) |    |                            |  |  |  |    |     |   |      |   | 0   | x8000 | 002n0 |    |

|------|------------------------------------------------|----|----------------------------|--|--|--|----|-----|---|------|---|-----|-------|-------|----|

| 15   | 14                                             | 13 | 12 11 10 9 8 7 6 5 4 3 2 1 |  |  |  |    |     |   | 0    |   |     |       |       |    |

|      | 0                                              |    |                            |  |  |  | СС | POL | Т | CKSE | L | IEN | PWM   | CON   | EN |

| CC [8] | Clear Count               |

|--------|---------------------------|

| 0      | TCNTn hold its value.     |

| 1      | TCNTn is cleared to zero. |

| POL [7] | TCK Polarity                                                        |

|---------|---------------------------------------------------------------------|

| 0       | TCNTn is incremented at rising edge of the selected counting clock  |

| 1       | TCNTn is incremented at falling edge of the selected counting clock |

| TCKSEL [6:4] | TCK Select                                                                             |

|--------------|----------------------------------------------------------------------------------------|

| k = 0 ~ 4    | TCK is internally generated from divider circuit. It is driven by PCLK, and this       |

|              | value determines the division factor of this circuit. Division factor is $2^{(k+1)}$ . |

| k = 5, 6     | TCK is internally generated from divider circuit. It is driven by PCLK, and this       |

|              | value determines the division factor of this circuit. Division factor is $2^{2k}$      |

| k = 7        | TCK is the external pin shared by external interrupt signal. In TCC721, there          |

|              | are 4 external pins for this purpose, so this configuration is valid only for          |

|              | timer/counter $3 \sim 0$ . (not for timer/counter 5, 4)                                |

| IEN [3] | Interrupt Enable                   |

|---------|------------------------------------|

| 1       | Timer/Counter interrupt is enabled |

| PWM [2] | PWM Mode Enable                                                     |  |  |  |  |  |  |  |  |  |  |  |

|---------|---------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|

| 1       | Timer/Counter Output is changed at every time the TCNTn is equal to |  |  |  |  |  |  |  |  |  |  |  |

|         | TREFn and TMREFn value. It can be used to generate PWM waveform, by |  |  |  |  |  |  |  |  |  |  |  |

|         | changing TMREFn while fixing TREFn. (where, TREFn > TMREFn)         |  |  |  |  |  |  |  |  |  |  |  |

| CON [1] | Continue Counting                                                      |

|---------|------------------------------------------------------------------------|

| 0       | TCNTn is stop counting at the time TCNTn is equal to TREFn             |

| 1       | When the TCNTn is reached to TREFn, TCNTn continues counting from 0 at |

|         | the next pulse of selected clock source                                |

| EN [0] | Timer/Counter Enable                                               |

|--------|--------------------------------------------------------------------|

| 1      | Timer counter is enabled. TCNTn value is cleared at the same time. |

# **TIMER / COUNTER**

# 32-bit RISC Microprocessor for Digital Media Player

Dec. 16. 2002

#### Preliminary Spec 0.51

| Timer | imer/Counter n Counting Register (TCNTn) |    |    |    |    |    |    |    |    |    |    |              | 0x800002n4 |    |    |

|-------|------------------------------------------|----|----|----|----|----|----|----|----|----|----|--------------|------------|----|----|

| 31    | 30                                       | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19           | 18         | 17 | 16 |

|       | 0                                        |    |    |    |    |    |    |    |    |    |    | TCNTn[19:16] |            |    |    |

| 15    | 14                                       | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3            | 2          | 1  | 0  |

|       | TCNTn[15:0]                              |    |    |    |    |    |    |    |    |    |    |              |            |    |    |

\*) TCNTn is increased by 1 at every pulse of selected clock source. TCNTn can be set to any value by writing the value to this register. In case of timer 4 and timer 5, it has 20bit.

### Timer/Counter n Counting Reference Register (TREFn)

| 31 | 30          | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19           | 18 | 17 | 16 |

|----|-------------|----|----|----|----|----|----|----|----|----|----|--------------|----|----|----|

|    | 0           |    |    |    |    |    |    |    |    |    |    | TREFn[19:16] |    |    |    |

| 15 | 14          | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3            | 2  | 1  | 0  |

|    | TREFn[15:0] |    |    |    |    |    |    |    |    |    |    |              |    |    |    |

\*) When TCNTn is reached at TREFn, the TCNTn is cleared to 0. According to the TCFGn settings, various

kinds of operations may be done. In case of timer 4 and timer 5, it has 20bit.

0x800002n8

## 32-bit RISC Microprocessor for Digital Media Player

### Dec. 16. 2002

#### Preliminary Spec 0.51

| • | Timer | Timer/Counter Interrupt Request Register (TIREQ) |     |     |     |     |     |     |   |    |     |     | C   | )x800 | 00260 |     |

|---|-------|--------------------------------------------------|-----|-----|-----|-----|-----|-----|---|----|-----|-----|-----|-------|-------|-----|

|   | 15    | 14                                               | 13  | 12  | 11  | 10  | 9   | 8   | 7 | 6  | 5   | 4   | 3   | 2     | 1     | 0   |

|   | 0     | TWF                                              | TF5 | TF4 | TF3 | TF2 | TF1 | TF0 | 0 | TW | TI5 | TI4 | TI3 | TI2   | TI1   | TIO |

| TWF | Watchdog Timer Flag                                |

|-----|----------------------------------------------------|

| 1   | Watchdog timer has reached to its reference value. |

| TFn | Timer/Counter n Flag                 |  |  |  |  |

|-----|--------------------------------------|--|--|--|--|

| 1   | Timer/counter n has been overflowed. |  |  |  |  |

| TWI | Watchdog Timer Interrupt Request Flag       |

|-----|---------------------------------------------|

| 1   | Watchdog timer has generated its interrupt. |

| TIn | Timer/Counter n Interrupt Request Flag       |

|-----|----------------------------------------------|

| 1   | Timer/counter n has generated its interrupt. |

\*) if a timer n has reached its reference value, the TFn is set. (bit n represents for Timer n). If its interrupt request is enabled by set bit 3 of TCFGn register, the TIn is set. And if the TC bit of IEN register is set, the timer interrupt is really generated, and this TIREQ register is used to determine which timer has requested the interrupt. After checking these flags, user can clear these TFn, TIn field by writing "1" to corresponding TIn bit field.

# **TIMER / COUNTER**

# 32-bit RISC Microprocessor for Digital Media Player

Dec. 16. 2002

#### Preliminary Spec 0.51

0x80000270

## Watchdog Timer Configuration Register (TWDCFG)

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5    | 4 | 3   | 2 | 1   | 0  |

|----|----|----|----|----|----|---|---|---|---|------|---|-----|---|-----|----|

|    | 0  |    |    |    |    |   |   |   | Т | CKSE | L | IEN | 0 | RST | EN |

Watchdog timer is used for the system not to be stuck by generating a reset pulse automatically when the watchdog timer counter overflows to zero.

The programmer must clear the watchdog counter before it overflows by writing any value to TWDCLR register.

| TCKSEL [6:4] | TCK Select                                                                             |

|--------------|----------------------------------------------------------------------------------------|

| k = 0 ~ 4    | TCK is internally generated from divider circuit. It is driven by PCLK, and this       |

|              | value determines the division factor of this circuit. Division factor is $2^{(k+1)}$ . |

| k = 5, 6     | TCK is internally generated from divider circuit. It is driven by PCLK, and this       |

|              | value determines the division factor of this circuit. Division factor is $2^{2k}$      |

| k = 7        | Undefined. Should not be used.                                                         |

| IEN [3] | Interrupt Enable                                   |  |  |  |  |  |

|---------|----------------------------------------------------|--|--|--|--|--|

| 1       | Watchdog Timer Interrupt is initiated.             |  |  |  |  |  |

|         | This field is valid only if RST field is set to 0. |  |  |  |  |  |

| RST [1] | Reset Enable                                                               |  |  |  |  |

|---------|----------------------------------------------------------------------------|--|--|--|--|

| 0       | Watchdog timer does not generate reset signal although it reaches to the   |  |  |  |  |

|         | reference value, and it continue counting from 0.                          |  |  |  |  |

| 1       | Watchdog timer generates the reset signal when it reaches to the reference |  |  |  |  |

|         | value, the reset signal is applied to every component in the chip.         |  |  |  |  |

| EN [0] | Watchdog Timer Enable                                                       |

|--------|-----------------------------------------------------------------------------|

| 1      | Watchdog timer is enabled. If the watchdog timer is disabled, its counter   |

|        | goes to 0xffe0, so when it is first enabled, user must clear the counter by |

|        | writing to TWDCLR register.                                                 |

#### Watchdog Timer Clear Register (TWDCLR) 0x80000274 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 any value

\*) The watchdog timer counter can be cleared to 0 by writing any value to this register. If it is not cleared before it overflows, the watchdog timer generate reset signal to the entire component of chip.

0

**CHAPTER 6**

**GPIO PORT**

## 6 GPIO (General Purpose I/O) PORT

#### 6.1 Functional Description

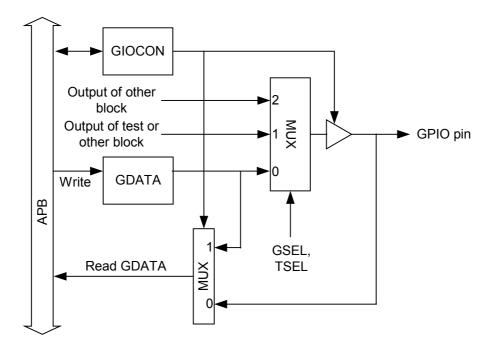

The TCC720 has a lot of general purpose I/Os that can be programmed by setting internal registers. All I/Os are set to input mode at reset. The block diagram of GPIO is in the following figure.

Figure 6.1 GPIO Block Diagram

The I/O mode can be set by the state of GIOCONn register.

If a bit of GIOCONn register is 1, the corresponding GPIO pin has come to output mode, and if 0, which is the default state of GIOCON register, the corresponding GPIO pin is set to input mode.

If GPIO pin is set to input mode, GPIO pin's state can be fed to CPU by reading GDATAn register and when output mode, GPIO pin's state can be controlled by the state of the corresponding bit of GDATAn register.

If GDATAn register is read when the mode is output mode, the value that CPU gets is the one

Preliminary Spec 0.51

that CPU has written before.

In TCC720, there are various kinds of peripherals that generate its own control signals. These peripherals can occupy the dedicated GPIO pins. This option is controlled by the state of the GSELx register. If a bit of these GSELx is 1, the corresponding GPIO pin is entered to other function mode, so used by other peripherals not by GPIO block. The direction control method of GPIO pins in the other function mode is determined case by case. One of them follows the normal direction control method using GDDR register, the other method uses a dedicated direction control signals.

# **TCC720**

# **GPIO PORT**

#### 32-bit RISC Microprocessor for Digital Media Player Dec. 16. 2002

Preliminary Spec 0.51

#### 6.2 Register Description

#### GPIO Register Map (Base Address = 0x80000300)

| Name     | Addr | Туре | Reset      | Description                       |

|----------|------|------|------------|-----------------------------------|

| GDATA_A  | 0x00 | R/W  | 0xFFFFFFFF | GPIO_A Data Register              |

| GIOCON_A | 0x04 | R/W  | 0x0000000  | GPIO_A Direction Control Register |

| GSEL_A   | 0x08 | R/W  | 0x0000000  | GPIO_A Function Select Register 1 |

| GTSEL_A  | 0x0C | R/W  | 0x00000000 | GPIO_A Function Select Register 2 |

| GDATA_B  | 0x10 | R/W  | 0x3FFFFFFF | GPIO_B Data Register              |

| GIOCON_B | 0x14 | R/W  | 0x001FFCFF | GPIO_B Direction Control Register |

| GSEL_B   | 0x18 | R/W  | 0x3C0000BF | GPIO_B Function Select Register 1 |

| GTSEL_B  | 0x1C | R/W  | 0x00000000 | GPIO_B Function Select Register 2 |

### 32-bit RISC Microprocessor for Digital Media Player

Dec. 16. 2002

#### Preliminary Spec 0.51

| GPIO | GPIO_A Data Register (GDATA_A)0x80000300 |    |    |    |    |    |    |    |    |    |    |    |    |    |    |