#### Rev C1, Page 1/26

#### FEATURES

- ✤ IO-Link compliant slave transceiver

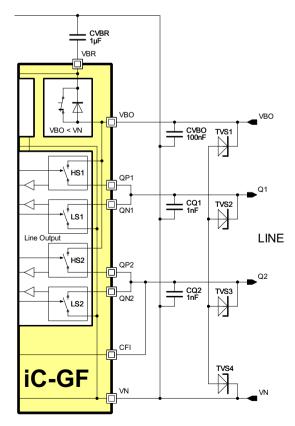

- Dual channel switches, configurable for high-side, low-side and push-pull operation with tristate function

- Configuration via pins or SPI interface

- Switches are current limited

- Switches, iC supply and feedback channel are protected against reverse polarity

- Output current of up to 150 mA per channel

- Parallel connection of both channels possible

- The channels can be inverted for antivalent output

- Sensor communication request function (IO-Link wake-up)

- ♦ Wide supply voltage range of 9 to 30 V

- Sensor parametrisation via a feedback channel (up to 30 V)

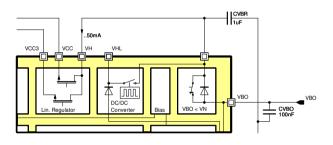

- Switching converters and linear regulators for 3.3/5 V voltage generation

- Error detection with hysteresis with excess temperature, overload and undervoltage

- Driver shut-down on all errors

- Error signalling at two open-collector outputs

- IO-Link slaves

- ♦ I/O sensor interface

- Digital sensors

- Light barriers

- Proximity switches

# PACKAGES

QFN24 4 mm x 4 mm

#### DESCRIPTION

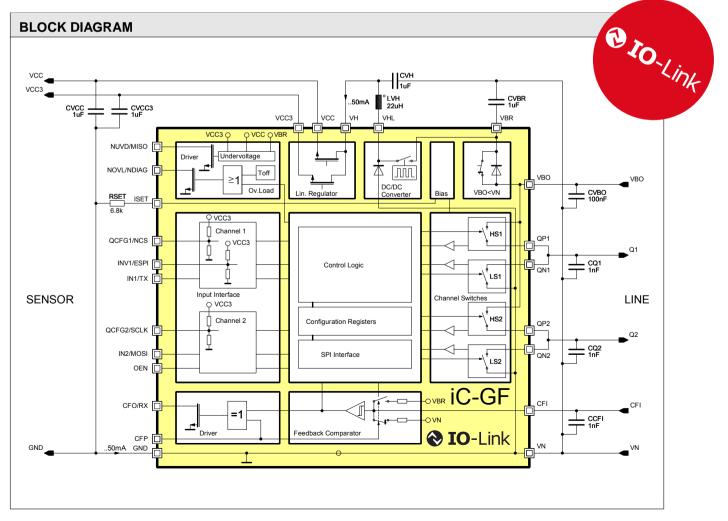

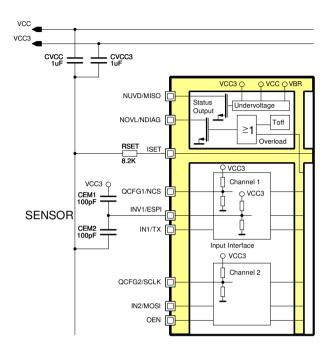

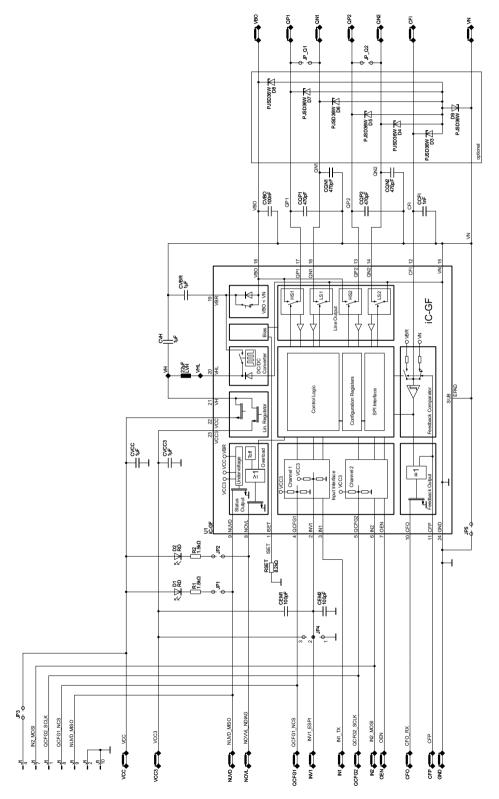

iC-GF is a fully IO-Link compliant transceiver iC with two independent switching channels which enables digital sensors to drive peripheral elements, such as programmable logic controllers (PLC) and relays, for example. All functions are controlled either by pins or via SPI interface, with extended functionality and configurability in SPI mode.

The output switches can be configured for push-pull, high-side or low-side operation and share a common tri-state function (separate tri-state switching in SPI mode). The switches are designed to cope with high driver currents of at least 100 mA (RSET =  $6.8 \text{ k}\Omega$ ), are current limited and also short-circuit-proof in that they shut down with excessive temperature or overload. The output current limit can be easily set with a resistor at pin ISET.

The protective overload feature is accomplished in a way so that capacitive loads can be switched with low repeat rates without the protective circuitry cutting in. In the event of excess temperature an error message is generated immediately.

Errors are signalled by two open-collector outputs: NOVL (for excess temperature and overloads) and NUVD (for low voltage at VBR or VCC resp. VCC3). The output switches are shut down with all types of errors.

To avoid error signalling during power-up, the output switches remain at high impedance for ca. 50 ms.

In SPI mode, the chip acts as an SPI slave and allows function configuration via register access. It also features a diagnostic register and supports *communication requests* (= IO-Link *wake-up*) at pin CFI, which generate interrupt signals at pin NDIAG.

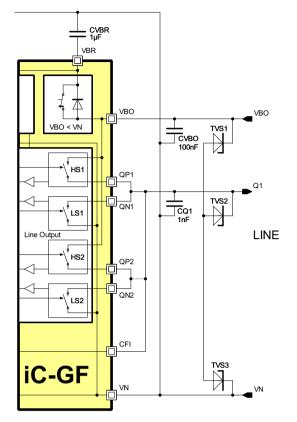

The pins on the 24 V line side of the sensor interface (VBO, QP1, QN1, QP2, QN2, VN and CFI) are protected against reverse polarity. This makes any external reverse polarity protection diodes superfluous.

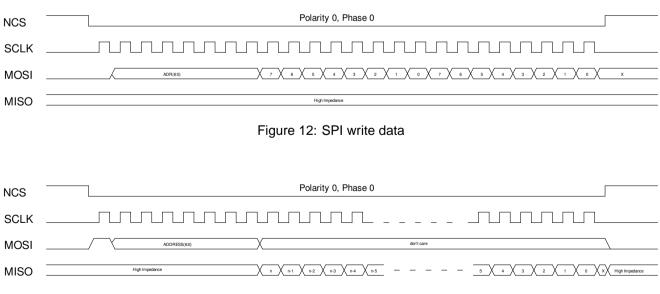

iC-GF features an integrated switching converter which generates voltages VCC (5V) and VCC3 (3.3V) with the aid of two downstream linear regulators. For *medium* currents the inductor may as well be replaced by a resistor (e.g.  $170 \Omega$ ), resulting though in a considerably less efficiency. If only a low current is required inductor LVH may be omitted completely; the linear regulators are then powered directly by VBR.

The switching regulator comes equipped with a spread spectrum oscillator to reduce interferences.

Input INV1 permits the input signal at channel 1 (IN1) to be inverted and if left unconnected, switches the chip into SPI mode.

The connected sensor can be parametrised using the feedback channel with a high voltage input (CFI  $\rightarrow$  CFO).

## CONTENTS

| PACKAGES                                  | 4  |

|-------------------------------------------|----|

| ABSOLUTE MAXIMUM RATINGS                  | 5  |

| THERMAL DATA                              | 5  |

| ELECTRICAL CHARACTERISTICS                | 7  |

| OPERATING REQUIREMENTS: SPI Interface     | 12 |

| DESCRIPTION OF FUNCTIONS                  | 13 |

| Reverse polarity protection               | 13 |

| Output characteristics of Q1, Q2          | 13 |

| Free-wheeling circuit for inductive loads | 13 |

| Dead time                                 | 13 |

| Overload detection                        | 13 |

| Undervoltage detection                    | 14 |

| Digital filtering at inputs               | 14 |

| Feedback channel CFI–CFO                  | 14 |

| Spread spectrum oscillator                | 14 |

| Configuration mode                        | 14 |

| DEFAULT MODE                              | 15 |

| Enabling the switches                     | 15 |

| Configuring the switches                  | 15 |

| Feedback channel CFI–CFO configuration    | 15 |

| Undervoltage signalling                | 15 |

|----------------------------------------|----|

| SPI MODE                               | 16 |

| Switch enable                          | 16 |

| Switch control                         | 16 |

| Switch configuration                   | 16 |

| Digital filtering at inputs            | 17 |

| Excitation current                     | 17 |

| Feedback channel CFI–RX configuration  | 18 |

| Overload detection                     | 18 |

| Spread spectrum oscillator             | 19 |

| Pull-down currents                     | 19 |

| Undervoltage signalling                | 19 |

| Communication requests                 | 19 |

| SPI INTERFACE                          | 20 |

| REGISTERS                              | 21 |

| Configuration overview                 | 21 |

| APPLICATION NOTES                      | 22 |

| Setup for medium and small currents at |    |

| VCC/VCC3                               | 22 |

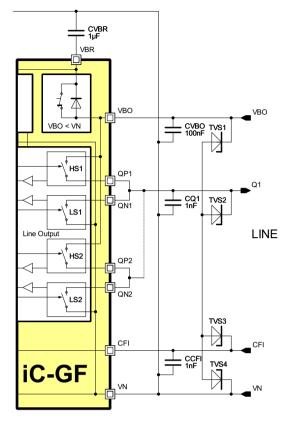

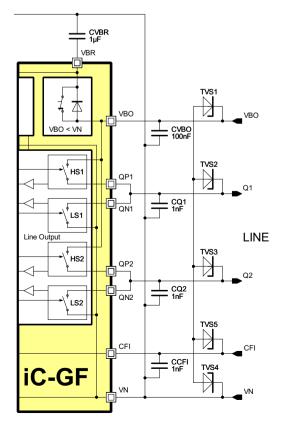

| Output protection                      | 22 |

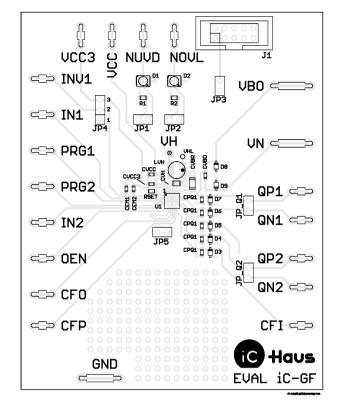

| DEMO BOARD                             | 24 |

Rev C1, Page 4/26

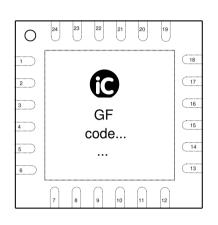

#### PACKAGES QFN24 4 mm x 4 mm to JEDEC Standard

#### PIN CONFIGURATION QFN24 4 mm x 4 mm

#### **PIN FUNCTIONS**

#### No. Name Function

| 1 ISET | Reference Current for current limitation |

|--------|------------------------------------------|

|        | of driver outputs                        |

- 2 INV1 Inverting Input Channel 1

- ESPI Enable SPI (pin open)

- 3 IN1 Input Channel 1

- TX Transmission Input (SPI mode)

- 4 QCFG1 Configuration Input Channel 1 NCS Chip Select (SPI mode)

## PIN FUNCTIONS

| PIN | PIN FUNCTIONS |                                      |  |  |  |  |  |  |  |  |

|-----|---------------|--------------------------------------|--|--|--|--|--|--|--|--|

| No. | Name          | Function                             |  |  |  |  |  |  |  |  |

| 5   | QCFG2         | Configuration Input Channel 2        |  |  |  |  |  |  |  |  |

|     | SCLK          | Serial Clock (SPI mode)              |  |  |  |  |  |  |  |  |

| 6   | IN2           | Input Channel 2                      |  |  |  |  |  |  |  |  |

|     | MOSI          | Master Output Slave Input (SPI mode) |  |  |  |  |  |  |  |  |

| 7   | OEN           | Output Enable Input                  |  |  |  |  |  |  |  |  |

| 8   | NOVL          | Overload Error Output                |  |  |  |  |  |  |  |  |

|     | NDIAG         | Diagnosis Output (SPI mode)          |  |  |  |  |  |  |  |  |

| 9   | NUVD          | Undervoltage Error Output            |  |  |  |  |  |  |  |  |

|     | MISO          | Master Input Slave Output (SPI mode) |  |  |  |  |  |  |  |  |

| 10  | CFO           | Feedback Channel Output              |  |  |  |  |  |  |  |  |

|     | RX            | Transmission Output (SPI mode)       |  |  |  |  |  |  |  |  |

| 11  | CFP           | Configuration Input Feedback Channel |  |  |  |  |  |  |  |  |

| 12  | CFI           | Feedback Channel Input               |  |  |  |  |  |  |  |  |

| 13  | QP2           | High Side Switch Output Channel 2    |  |  |  |  |  |  |  |  |

|     | QN2           | Low Side Switch Output Channel 2     |  |  |  |  |  |  |  |  |

| 15  | VN            | Ground                               |  |  |  |  |  |  |  |  |

| 16  | QN1           | Low Side Switch Output Channel 1     |  |  |  |  |  |  |  |  |

| 17  | QP1           | High Side Switch Output Channel 1    |  |  |  |  |  |  |  |  |

| 18  | VBO           | Power Supply                         |  |  |  |  |  |  |  |  |

| 19  | VBR           | Power Supply for switching converter |  |  |  |  |  |  |  |  |

| 20  | VHL           | Inductor Switching Converter         |  |  |  |  |  |  |  |  |

| 21  | VH            | Input Linear Regulators              |  |  |  |  |  |  |  |  |

|     | VCC           | 5 V Sensor Supply                    |  |  |  |  |  |  |  |  |

| 23  | VCC3          | 3.3 V Sensor Supply                  |  |  |  |  |  |  |  |  |

| 24  | GND           | Sensor Ground                        |  |  |  |  |  |  |  |  |

|     |               |                                      |  |  |  |  |  |  |  |  |

The *Thermal Pad* is to be connected to a Ground Plane (VN) on the PCB.

Only pin 1 marking on top or bottom defines the package orientation (iC-GF label and coding is subject to change).

#### **ABSOLUTE MAXIMUM RATINGS**

Beyond these values damage may occur; device operation is not guaranteed. Absolute Maximum Ratings are no operating conditions! Integrated circuits with system interfaces, e.g. via cable accessible pins (I/O pins, line drivers) are per principle endangered by injected interferences, which may compromise the function or durability. The robustness of the devices has to be verified by the user during system development with regards to applying standards and ensured where necessary by additional protective circuitry. By the manufacturer suggested protective circuitry is for information only and given without responsibility and has to be verified within the actual system with respect to actual interferences.

| ltem<br>No. | Symbol  | Parameter                                         | Conditions                                                                                                                                                              | Min.        | Max.      | Unit     |

|-------------|---------|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------|----------|

| G001        | VBO     | Power Supply at VBO                               | Referenced to lowest voltage of VN, VBR,<br>QP1, QN1, QP2, QN2, CFI, VH, VHL                                                                                            | -           | 36        | V        |

|             |         |                                                   | Referenced to highest voltage of VN, VBR,<br>QP1, QN1, QP2, QN2, CFI, VH, VHL                                                                                           | -36         |           | V        |

| G002        | I(VBO)  | Current in VBO                                    |                                                                                                                                                                         | -10         | 600       | mA       |

| G003        | VBR     | Voltage at VBR                                    | Referenced to lowest voltage of VN, VBO,<br>QP1, QN1, QP2, QN2, CFI, VH, VHL<br>Referenced to highest voltage of VN, VBO,<br>QP1, QN1, QP2, QN2, CFI, VH, VHL           | -36         | 36        | V<br>V   |

| G004        | I(VBR)  | Current in VBR                                    |                                                                                                                                                                         | -10         | 600       | mA       |

| G005        | CI(VBR) | Capacitive load at VBR                            |                                                                                                                                                                         |             | 3.3       | μF       |

| G006        | V(VH)   | Voltage at VH                                     | Referenced to lowest voltage of VN, VBR,<br>VBO, QP1, QN1, QP2, QN2, CFI, VHL<br>Referenced to highest voltage of VN, VBR,<br>VBO, QP1, QN1, QP2, QN2, CFI, VHL         | -36         | 36        | V<br>V   |

| G007        | I(VH)   | Current in VH                                     |                                                                                                                                                                         | -5          | 70        | mA       |

| G008        | V(VHL)  | Voltage at VHL                                    | Referenced to lowest voltage of VN, VBR,<br>VBO, QP1, QN1, QP2, QN2, CFI, VH<br>Referenced to highest voltage of VN, VBR,<br>VBO, QP1, QN1, QP2, QN2, CFI, VH           | -36         | 36        | V<br>V   |

| G009        | I(VHL)  | Current in VHL                                    |                                                                                                                                                                         | -150        | 5         | mA       |

| G010        | V(VN)   | Voltage at GND vs. VN                             |                                                                                                                                                                         | -2          | 2         | V        |

| G011        | I(VN)   | Current in VN                                     | VN < VBO<br>VN > VBO                                                                                                                                                    | -500<br>-10 | 500<br>10 | mA<br>mA |

| G012        | V()     | Voltage at VCC, VCC3                              |                                                                                                                                                                         | -0.3        | 7         | V        |

| G013        |         | Current in VCC, VCC3                              |                                                                                                                                                                         | -50         | 10        | mA       |

| G014        | V()     | Voltage at QP1, QN1, QP2, QN2                     | Referenced to lowest voltage of VN, VBO,<br>VBR, QP1, QN1, QP2, QN2, CFI, VH, VHL<br>Referenced to highest voltage of VN, VBO,<br>VBR, QP1, QN1, QP2, QN2, CFI, VH, VHL | -36         | 36        | V<br>V   |

| G015        | I()     | Current in QP1, QP2                               |                                                                                                                                                                         | -400        |           | mA       |

| G016        | I()     | Current in QN1, QN2                               |                                                                                                                                                                         |             | 400       | mA       |

| G017        | V(CFI)  | Voltage at CFI                                    | Referenced to lowest voltage of VN, VBO,<br>VBR, QP1, QN1, QP2, QN2, VH, VHL<br>Referenced to highest voltage of VN, VBO,<br>VBR, QP1, QN1, QP2, QN2, VH, VHL           | -36         | 36        | V<br>V   |

| G018        | I(CFI)  | Current in CFI                                    |                                                                                                                                                                         | -4          | 4         | mA       |

| G019        | V()     | Voltage at INV1, QCFG1, QCFG2, IN1, IN2, OEN, CFP |                                                                                                                                                                         | -0.3        | 7         | V        |

| G020        | I()     | Current in INV1, QCFG1, QCFG2, IN1, IN2, OEN, CFP |                                                                                                                                                                         | -4          | 4         | mA       |

|             | V()     | Voltage at NOVL, NUVD, CFO                        |                                                                                                                                                                         | -0.3        | 7         | V        |

| G022        |         | Current in NOVL, NUVD, CFO                        |                                                                                                                                                                         | -5          | 20        | mA       |

| G023        | V(ISET) | Voltage at ISET                                   |                                                                                                                                                                         | -0.3        | 7         | V        |

| G024        | I(ISET) | Current in ISET                                   |                                                                                                                                                                         | -4          | 4         | mA       |

| G025        |         | ESD Susceptibility at all pins                    | HBM, 100 pF discharged through $1.5  k\Omega$                                                                                                                           |             | 2         | kV       |

| G026        | -       | Junction Temperature                              |                                                                                                                                                                         | -40         | 150       | °C       |

| G027        | Ts      | Storage Temperature Range                         |                                                                                                                                                                         | -40         | 150       | °C       |

All currents into the device pins are positive; all currents out of the device pins are negative.

Rev C1, Page 6/26

#### THERMAL DATA

Operating Conditions: VBO = 9...30 V (referenced to VN), Tj = -40...125 °C, RSET = 6.8 kΩ ±1%, unless otherwise stated

| Item | Symbol | Parameter                                                       | Conditions                                                               |      |      |      | Unit |

|------|--------|-----------------------------------------------------------------|--------------------------------------------------------------------------|------|------|------|------|

| No.  | -      |                                                                 |                                                                          | Min. | Тур. | Max. |      |

| T01  |        | Operating Ambient Temperature Range (extended range on request) |                                                                          | -40  |      | 85   | °C   |

| T02  | Rthja  |                                                                 | Surface mounted, thermal pad soldered to ca. 2 cm <sup>2</sup> heat sink |      | 30   | 40   | K/W  |

Rev C1, Page 7/26

| ltem<br>No. | Symbol     | Parameter                                                                                                                                           | Conditions                                                                                                  | Min.                  | Тур.       | Max.               | Unit                 |

|-------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------|------------|--------------------|----------------------|

|             | Device     |                                                                                                                                                     |                                                                                                             |                       |            |                    |                      |

| 001         | VBO        | Permissible Supply Voltage                                                                                                                          | Referenced to VN                                                                                            | 9                     | 24         | 30                 | V                    |

| 002         | I(VBO)     | Supply Current in VBO                                                                                                                               | No load, VH conected to VBR,<br>I(QP1) = I(QP2) = 0, QPx switched on                                        |                       |            | 4.5                | mA                   |

| 003         | Vs(VBR)    | Saturation Voltage at VBR referenced to VBO                                                                                                         | I(VBR) = 20mA<br>I(VBR) = 50mA                                                                              |                       |            | 0.8<br>1           | V<br>V               |

| 004         | VH         | Permissible Voltage at VH                                                                                                                           | VH > VHnr                                                                                                   | 8.4                   |            | 30                 | V                    |

| 005         | I(VH)      | Supply Current in VH                                                                                                                                | VH = 8 V, no load, I(VCC) = I(VCC3) = 0,<br>V(OEN) = hi                                                     | 1.5                   |            | 3                  | mA                   |

| 006         | Vc()hi     | Clamp Voltage hi at VBO, VBR vs. VN                                                                                                                 | I() = 10 mA                                                                                                 | 36                    |            |                    | V                    |

| 007         | Vc()lo     | Clamp Voltage lo at VBO, VBR<br>vs. VN                                                                                                              | I() = -10 mA                                                                                                |                       |            | -36                | V                    |

| 008         | Vc()hi     | Clamp Voltage hi at QN1, QN2<br>vs. VN                                                                                                              | I() = 1 mA, VBO > VN                                                                                        | 36                    |            |                    | V                    |

| 009         | Vc()lo     | Clamp Voltage lo at QP1, QP2<br>vs. VBO                                                                                                             | I() = -1 mA, VBO > VN                                                                                       |                       |            | -36                | V                    |

| 010         | Vc()hi     | Clamp Voltage hi at VN, VBO,<br>VBR, QP1, QN1, QP2, QN1, CFI,<br>VH, VHL vs. lowest voltage of<br>VN, VBO, VBR, QP1, QN1, QP2,<br>QN1, CFI, VH, VHL | I() = 1 mA                                                                                                  | 36                    |            |                    | V                    |

| 011         | Vc()hi     | Clamp Voltage hi at VCC, VCC3,<br>ISET, INV1, IN1, IN2, QCFG1,<br>QCFG2, OEN, CFO, CFP, NOVL,<br>NUVD                                               | I() = 1 mA                                                                                                  | 7                     |            |                    | V                    |

| 012         | Vc()lo     | Clamp Voltage lo at VCC, VCC3,<br>ISET, INV1, IN1, IN2, QCFG1,<br>QCFG2, OEN, CFO, CFP, NOVL,<br>NUVD                                               | I() = -1 mA                                                                                                 |                       |            | -0.5               | V                    |

| 013         | RGND       | Resistance GND to VN                                                                                                                                |                                                                                                             |                       | 3          | 7                  | Ω                    |

| Low-S       | ide Switch | QN1, QN2                                                                                                                                            |                                                                                                             |                       |            |                    |                      |

| 101         | Vs()lo     | Saturation Voltage lo at QN1,<br>QN2 vs. VN                                                                                                         | RSET = 5.1 kΩ;<br>I() = 100 mA<br>I() = 50 mA<br>I() = 10 mA                                                |                       |            | 1.2<br>0.65<br>0.3 | V<br>V<br>V          |

| 102         | lsc()lo    | Short-Circuit Current lo in QN1, QN2                                                                                                                | RSET = 6.8 kΩ, V() = 3 VVBO<br>RSET = 5.1 kΩ, V() = 4 VVBO                                                  | 100<br>160            | 140<br>200 | 180<br>260         | mA<br>mA             |

| 103         | Vol()on    | Overload Detection Threshold on                                                                                                                     | QN1, QN2 lo $\rightarrow$ hi; referenced to GND                                                             | 1.5                   |            | 2.1                | V                    |

| 104         | Vol()off   | Overload Detection Threshold off                                                                                                                    | QN1, QN2 hi $\rightarrow$ lo; referenced to GND                                                             | 1.5                   |            | 1.8                | V                    |

| 105         | Vol()hys   | Overload Detection Threshold<br>Hysteresis                                                                                                          | Vol()hys = Vol()on - Vol()off                                                                               | 0.1                   |            |                    | V                    |

| 106         | lik()      | Leakage Current at QN1, QN2                                                                                                                         | OEN = Io;<br>V(QN1, QN2) = VBOVBO + 6 V<br>V(QN1, QN2) = 0VBO<br>V(QN1, QN2) = -60 V<br>V(QN1, QN2) = -60 V | 0<br>0<br>-70<br>-200 |            | 50<br>50<br>0<br>0 | μΑ<br>μΑ<br>μΑ<br>μΑ |

| 107         | SR()       | Slew Rate (switch off $\rightarrow$ on)                                                                                                             | VBO = 30 V, Cl = 2.2 nF                                                                                     |                       |            | 45                 | V/µs                 |

| 108         | lmax()     | Maximum Current in QN1, QN2                                                                                                                         | V(ISET) = 0 V, QNx > 3 V                                                                                    | 170                   | 300        | 440                | mA                   |

| 109         | lr()       | Reverse Current in QN1, QN2                                                                                                                         | QNx activated; $V(QNx) = -6 V$                                                                              | -300                  |            |                    | μA                   |

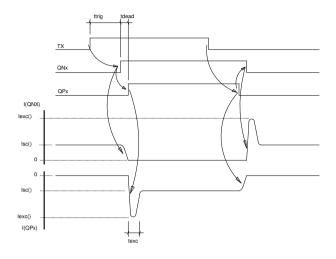

| 110         | lexc()     | Excitation Current                                                                                                                                  | NEXC = 0 (see Fig. 9)                                                                                       | 300                   |            | 540                | mA                   |

| 111         | texc       | Excitation Time                                                                                                                                     | NEXC = 0 (see Fig. 9)                                                                                       | 1.5                   |            | 3.5                | μs                   |

| 112         | tdead      | Dead Time                                                                                                                                           | Push-pull configuration, QNx activation delay after QPx deactivation (see Fig. 9)                           | 1.2                   |            | 2.8                | μs                   |

Rev C1, Page 8/26

| ltem   | Symbol                | Parameter                                                                                                                         | Conditions                                                                        |          |      |      | Unit     |

|--------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|----------|------|------|----------|

| No.    |                       |                                                                                                                                   |                                                                                   | Min.     | Тур. | Max. |          |

| -      | Side Switch           |                                                                                                                                   |                                                                                   | _        |      |      |          |

| 201    | Vs()hi                | Saturation Voltage hi vs. VBO                                                                                                     | RSET = 5.1 kΩ;<br>I() = -100 mA                                                   | -1.4     |      |      | v        |

|        |                       |                                                                                                                                   | I() = -50  mA                                                                     | -0.85    |      |      | v        |

|        |                       |                                                                                                                                   | I() = -10  mA                                                                     | -0.35    |      |      | V        |

| 202    | lsc()hi               | Short-Circuit Current hi                                                                                                          | RSET = 6.8 kΩ, V() = 0VBO - 3 V                                                   | -230     | -150 | -100 | mA       |

|        |                       |                                                                                                                                   | RSET = 5.1 kΩ, V() = 0VBO – 4 V                                                   | -325     | -220 | -140 | mA       |

| 203    | Vol()on               | Overload Detection Threshold on                                                                                                   | QP1, QP2 hi $\rightarrow$ lo; referenced to VBO                                   | -2.1     |      | -1.5 | V        |

| 204    | Vol()off              | Overload Detection Threshold off                                                                                                  | QP1, QP2 Io $\rightarrow$ hi; referenced to VBO                                   | -1.9     |      | -1.4 | V        |

| 205    | Vol()hys              | Overload Detection Threshold<br>Hysteresis                                                                                        | Vol()hys = Vol()off - Vol()on                                                     | 0.1      |      |      | V        |

| 206    | llk()                 | Leakage Current at QP1, QP2                                                                                                       | OEN = lo;                                                                         |          |      |      |          |

|        |                       |                                                                                                                                   | V(QP1, QP2) = -60V                                                                | -100     |      | 0    | μA       |

|        |                       |                                                                                                                                   | V(QP1, QP2) = 0 VVBO<br>V(QP1, QP2) > VBOVN + 30 V                                | -40<br>0 |      | 0    | μΑ<br>μΑ |

| 207    | SR()                  | Slew Rate (switch off $\rightarrow$ on)                                                                                           | VBO = 30 V. CI = 2.2 nF                                                           |          |      | 40   | ν/με     |

| 207    | Imax()                | Maximum Current in QP1, QP2                                                                                                       | VBO = 30 V, CI = 2.2 HP<br>V(ISET) = 0 V, VBO - QPx > 4 V                         | -520     |      | -170 | mA       |

| 208    | lr()                  | Reverse Current in QP1, QP2                                                                                                       | V(ISET) = 0.7, VBO - QFX > 4.7<br>QPx activated; $V(QPx) = VBOVBO + 6.7$          | -520     |      | -170 | mA       |

| 209    | lexc()                | Excitation Current                                                                                                                | NEXC = 0 (see Fig. 9)                                                             | -540     |      | -300 | mA       |

| 210    |                       | Excitation Current<br>Excitation Time                                                                                             | NEXC = 0 (see Fig. 9) $NEXC = 0 (see Fig. 9)$                                     | -540     |      |      |          |

|        | texc                  |                                                                                                                                   |                                                                                   | _        |      | 3.5  | μs       |

| 212    | tdead                 | Dead Time                                                                                                                         | Push-pull configuration, QPx activation delay after QNx deactivation (see Fig. 9) | 1.2      |      | 2.8  | μs       |

| Short  | 1                     | erload Monitor                                                                                                                    | 1                                                                                 | _        |      |      |          |

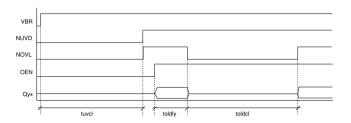

| 301    | toldly                | Time to Overload Message (NOVL 1 $\rightarrow$ 0, outputs tri-state)                                                              | Permanent overload (see Fig. 6)                                                   | 126      | 160  | 213  | μs       |

| 302    | tolcl                 | Time to Overload Message Reset (NOVL $0 \rightarrow 1$ , outputs active)                                                          | No overload (see Fig. 6)                                                          | 35       | 50   | 80   | ms       |

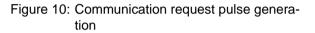

| 303    | tdscr                 | Time to Communication Request acknowledge                                                                                         | SPI mode, ENSCR = 1,<br>QCFGx(1:0) = 01/10/11                                     | 70       |      | 90   | μs       |

| 304    | tdnscr <sub>max</sub> | Maximum Time for no Communi-<br>cation Request acknowledge                                                                        |                                                                                   |          |      | 40   | μs       |

| 305    | tdnscr <sub>min</sub> | Minimum Time for no Communi-<br>cation Request acknowledge                                                                        |                                                                                   | 151      |      |      | μs       |

| VBO V  | Voltage Mor           | nitor                                                                                                                             | <u>`</u>                                                                          |          |      |      |          |

| 401    | VBOon                 | Turn-On Threshold VBO                                                                                                             | Referenced to GND                                                                 | 8        |      | 9    | V        |

| 402    | VBOoff                | Turn-Off Threshold VBO                                                                                                            | Decreasing voltage VBO                                                            | 7.3      |      | 8.5  | V        |

| 403    | VBOhys                | Hysteresis                                                                                                                        | VBOhys = VBOon - VBOoff                                                           | 200      | 500  |      | mV       |

| 404    | tuvdly                | Time to Undervoltage Message (NUVD $1 \rightarrow 0$ , switch tri-state)                                                          | Permanent undervoltage at VBR, VCC or VCC3                                        | 25       |      | 120  | μs       |

| 405    | tuvcl                 | Time to Undervoltage Message Reset                                                                                                | No undervoltage at VBR, VCC and VCC3 (see Fig. 6)                                 | 35       | 50   | 80   | ms       |

| _      |                       | (NUVD 0 $\rightarrow$ 1, switch active)                                                                                           |                                                                                   |          |      |      | <u> </u> |

|        | erature Mor           |                                                                                                                                   | l                                                                                 |          |      |      |          |

| 501    | Toff                  | Overtemperature Shutdown (NOVL 1 $\rightarrow$ 0, switch tri-state)                                                               | Increasing temperature Tj                                                         | 130      |      | 165  | °C       |

| 502    | ton                   | $\begin{array}{l} \text{Overtemperature Shutdown Reset Delay} \\ \text{(NOVL 0} \rightarrow \text{1, switch active)} \end{array}$ | Temperature Tj < Toff                                                             | 35       | 50   | 80   | ms       |

| Inputs | s IN1/TX, IN          | 2/MOSI, INV1/ENSPI, QCFG1/NCS                                                                                                     | , QCFG2/SCLK, OEN                                                                 |          |      |      |          |

| 601    | Vt()hi                | Input Threshold Voltage hi at<br>IN1/TX, IN2/MOSI, OEN, SCLK,<br>NCS                                                              |                                                                                   |          |      | 2    | V        |

| 602    | Vt()lo                | Input Threshold Voltage Io at<br>IN1/TX, IN2/MOSI, OEN, SCLK,<br>NCS                                                              |                                                                                   | 0.8      |      |      | V        |

Rev C1, Page 9/26

| ltem<br>No. | Symbol     | Parameter                                                                                                                                   | Conditions                                                                     | Min.     | Тур.     | Max.       | Unit     |

|-------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|----------|----------|------------|----------|

| 603         | Vt()hys    | Hysteresis at IN1/TX, IN2/MOSI,<br>OEN, SCLK, NCS                                                                                           | Vt()hys = Vt()hi - Vt()lo                                                      | 200      | 280      |            | mV       |

| 604         | lpd()      | Pull-Down Current at IN1/TX,<br>IN2/MOSI                                                                                                    | V() > 0.4 V                                                                    | 10       |          | 168        | μA       |

| 605         | lpd()      | Pull-Down Current at NCS, SCLK                                                                                                              | SPI mode, V() > 0.4 V                                                          | 10       |          | 40         | μA       |

| 606         | Ipd(OEN)   | Pull-Down Current at OEN                                                                                                                    | V(OEN) > 0.4 V                                                                 | 1        |          | 6          | μA       |

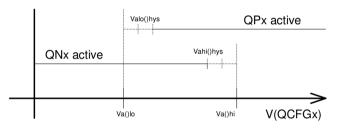

| 607         | Vahi()     | Input Threshold hi at QCFG1, QCFG2, INV1                                                                                                    |                                                                                | 52       | 64       | 69         | %VCC3    |

| 608         | Vahi()hys  | Hysteresis hi at QCFG1, QCFG2, INV1                                                                                                         |                                                                                | 3        |          | 7          | %VCC     |

| 609         | Valo()     | Input Threshold lo at QCFG1, QCFG2, INV1                                                                                                    |                                                                                | 24       | 29       | 34         | %VCC3    |

| 610         | Valo()hys  | Hysteresis lo at QCFG1, QCFG2, INV1                                                                                                         |                                                                                | 3        |          | 7          | %VCC3    |

| 611         | Voc()      | Open Circuit Voltage at QCFG1, QCFG2, INV1                                                                                                  |                                                                                | 42       | 46.5     | 51         | %VCC3    |

| 612         | Ri()       | Internal Resistance at QCFG1, QCFG2, INV1                                                                                                   | Referenced to VCC3<br>Referenced to GND                                        | 40<br>40 | 85<br>85 | 190<br>190 | kΩ<br>kΩ |

| 613         | tsup()     | Permissible Spurious Pulse<br>Width at IN1/TX, IN2, INV1/ESPI                                                                               | No activity triggered, DEFAULT mode or SPI<br>mode with FCFG(1:0) = 10         |          |          | 2.5        | μs       |

| 614         | ttrig()    | Required Pulse Width at IN1/TX, IN2, INV1/ESPI                                                                                              | Activity triggered, DEFAULT mode or SPI mode with FCFG(1:0) = 10               | 6        |          |            | μs       |

| 615         | tsup()     | Permissible Spurious Pulse<br>Width at QCFG1, QCFG2, OEN                                                                                    | No activity triggered, DEFAULT mode or SPI<br>mode with FCFG(1:0) = 10         |          |          | 5          | μs       |

| 616         | ttrig()    | Required Pulse Width at QCFG1, QCFG2, OEN                                                                                                   | Activity triggered, DEFAULT mode or SPI mode with FCFG(1:0) = 10               | 12       |          |            | μs       |

| 617         | tpio       | $\begin{array}{l} \mbox{Propagation Delay} \\ \mbox{IN1} \rightarrow \mbox{QP1, QN1} \\ \mbox{IN2} \rightarrow \mbox{QP2, QN2} \end{array}$ | INV1 = low or high, DEFAULT mode or SPI<br>mode with FCFG(1:0) = 10            | 2.4      |          | 10         | μs       |

| Error       | Output NOV | L/NDIAG, NUVD/MISO                                                                                                                          |                                                                                |          |          |            |          |

| 701         | Vs()lo     | Saturation Voltage Io at NOVL, NUVD                                                                                                         | DEFAULT mode, I() = 1.0 mA                                                     |          |          | 0.4        | V        |

| 702         | Vs()lo     | Saturation Voltage lo at NDIAG                                                                                                              | SPI mode, I() = 1.0 mA                                                         |          |          | 0.4        | V        |

| 703         | lsc()lo    | Short Circuit Current Io in NOVL, NUVD                                                                                                      | DEFAULT mode, V() = 0.4 VVCC                                                   | 1.2      |          | 25         | mA       |

| 704         | lsc()lo    | Short Circuit Current lo in NDIAG                                                                                                           | SPI mode, V() = 0.4 VVCC                                                       | 1.2      |          | 25         | mA       |

| 705         | llk()      | Leakage Current in NOVL, NUVD                                                                                                               | DEFAULT mode, V() = 0 VVCC, no error                                           | -10      |          | 10         | μA       |

| 706         | llk()      | Leakage Current in NDIAG                                                                                                                    | SPI mode, V() = 0 VVCC, no error                                               | -10      |          | 10         | μA       |

| 707         | Vs()hi     | Saturation Voltage high at MISO                                                                                                             | SPI mode, I(MISO) = -2 mA,<br>Vs(MISO)hi = VCC3 - V(MISO)                      |          |          | 0.4        | V        |

| 708         | Vs()lo     | Saturation Voltage low at MISO                                                                                                              | SPI mode, I(MISO) = 2 mA                                                       |          |          | 0.4        | V        |

| 709         | lsc()hi    | Short Circuit current hi in MISO                                                                                                            | SPI mode, V(MISO) = 0VCC3 - 0.4 V                                              | -40      |          |            | mA       |

| 710         | lsc()lo    | Short Circuit current lo in MISO                                                                                                            | SPI mode, V(MISO) = 0.4 VVCC3                                                  |          |          | 90         | mA       |

| 711         | tr(MISO)   | Rise Time                                                                                                                                   | SPI mode, CI(MISO) = 30 pF,<br>$0 \rightarrow 90\%$ VCC3                       |          |          | 22         | ns       |

|             | tf(MISO)   | Fall Time                                                                                                                                   | SPI mode, $100 \rightarrow 10\%$ VCC3                                          |          |          | 16         | ns       |

| Feedb       | ack Channe | el CFI to CFO/RX                                                                                                                            |                                                                                |          |          |            |          |

| 801         | . ,        | Input Threshold 1 hi at CFI                                                                                                                 | VBR < 18 V                                                                     | 59       | 66       | 74         | %VBR     |

| 802         | Vt1(CFI)lo | Input Threshold 1 lo at CFI                                                                                                                 | VBR < 18 V                                                                     | 44       | 50       | 56         | %VBR     |

| 803         | Vt2(CFI)hi | Input Threshold 2 hi at CFI                                                                                                                 | VBR > 18 V                                                                     | 10.5     | 11.3     | 12         | V        |

| 804         | Vt2(CFI)lo | Input Threshold 2 lo at CFI                                                                                                                 | VBR > 18 V                                                                     | 8.3      | 9        | 10.5       | V        |

| 805         | Vt()hys    | Hysteresis at CFI                                                                                                                           | Vt(CFI)hys = Vt(CFI)hi - Vt(CFI)lo                                             | 1        |          |            | V        |

| 806         | lpu(CFI)   | Pull-Up Current at CFI                                                                                                                      | DEFAULT mode: CFP = hi,<br>V(CFI) = 0VBR - 3 V<br>SPI mode: POL = 1, ENPUD = 1 | -300     |          | -40        | μA       |

Rev C1, Page 10/26

| ltem<br>No. | Symbol                | Parameter                                               | Conditions                                                                           | Min.     | Тур.       | Max.       | Unit     |

|-------------|-----------------------|---------------------------------------------------------|--------------------------------------------------------------------------------------|----------|------------|------------|----------|

| 807         | Ipd(CFI)              | Pull-Down Current at CFI                                | DEFAULT mode: CFP = Io, V(CFI) = 3 VVBR<br>SPI mode: POL = 0, ENPUD = 1              | 40       |            | 300        | μΑ       |

| 808         | tpcf                  | Propagation Delay CFI $\rightarrow$ CFO/RX              | $V(CFO/RX) = 10 \leftrightarrow 90\%$                                                | 2.4      |            | 10         | μs       |

| 809         | Vs()lo                | Saturation Voltage lo at CFO/RX                         | Open collector mode, I(CFO/RX) = 1.0 mA                                              |          |            | 0.4        | V        |

| 810         | lsc()lo               | Short Circuit Current lo in<br>CFO/RX                   | Open collector mode,<br>V(CFO/RX) = 0.4 VVCC                                         | 1.2      |            | 25         | mA       |

| 811         | llk()                 | Leakage Current at CFO/RX                               | Open collector mode, V(CFO/RX) = 0 VVCC,<br>CFO/RX = off                             | -10      |            | 10         | μA       |

| 812         | Vt(CFP)hi             | Input Threshold Voltage hi at<br>CFP                    |                                                                                      |          |            | 2          | V        |

| 813         | Vt(CFP)lo             | Input Threshold Voltage lo at<br>CFP                    |                                                                                      | 0.8      |            |            | V        |

| 814         | Vt(CFP)hys            | Hysteresis at CFP                                       | Vt(CFP)hys = Vt(CFP)hi - Vt(CFP)lo                                                   | 200      | 280        |            | mV       |

| 815         | Ipd(CFP)              | Pull-Down Current at CFP                                | V(CFP) = 0.4 VVt(CFP)lo<br>V(CFP) > Vt(CFP)hi                                        | 30<br>10 |            | 168<br>40  | μΑ<br>μΑ |

| 816         | tsup(CFI)             | Permissible Spurious Pulse<br>Width at CFI              | No activity triggered, DEFAULT mode or SPI<br>mode with FCFI(1:0) = 01               |          |            | 2.5        | μs       |

| 817         | ttrig(CFI)            | Required Pulse Width at CFI                             | Activity triggered, DEFAULT mode or SPI mode with FCFI(1:0) = 01                     | 6        |            |            | μs       |

| 818         | tsup(CFP)             | Permissible Spurious Pulse<br>Width at CFP              | No activity triggered                                                                |          |            | 5          | μs       |

| 819         | ttrig(CFP)            | Required Pulse Width at CFP                             | Activity triggered                                                                   | 12       |            |            | μs       |

| 820         | lpd(CFI)+<br>llk(QPx) | Pull-Down Current at CFI plus<br>leakage current at QPx | V(CFI) = 3 VVBR, OEN = Io;<br>DEFAULT mode: CFP = Io<br>SPI mode: POL = 0, ENPUD = 1 | 20       |            |            | μA       |

| 821         | Vs(RX)hi              | Saturation Voltage high at RX                           | SPI mode, ENOD = 0, I(RX) = -2 mA,<br>Vs(RX)hi = VCC3 - V(RX)                        |          |            | 0.4        | V        |

| 822         | Vs(RX)lo              | Saturation Voltage low at RX                            | SPI mode, ENOD = 0, I(RX) = 2 mA                                                     |          |            | 0.4        | V        |

| 823         | lsc(RX)hi             | Short Circuit current hi in RX                          | SPI mode, ENOD = 0,<br>V(RX) = 0VCC3 - 0.4 V                                         | -40      |            |            | mA       |

| 824         | lsc(RX)lo             | Short Circuit current lo in RX                          | SPI mode, ENOD = 0, V(RX) = 0.4 VVCC3                                                |          |            | 90         | mA       |

| 825         | tr(RX)                | Rise Time at RX                                         | SPI mode, ENOD = 0, CL(RX) = 30 pF, $0 \rightarrow 90\%$ VCC3                        |          |            | 22         | ns       |

| 826         | tf(RX)                | Fall Time at RX                                         | SPI mode, ENOD = 0, CL(RX) = 30 pF, 100 $\rightarrow$ 10%VCC3                        |          |            | 22         | ns       |

| Step [      | Down Conve            | rter VHL, VH                                            |                                                                                      |          |            |            |          |

| 901         | VHn                   | Nominal Voltage at VH                                   | LVH = 22 $\mu$ H, Ri(LVH) < 1.1 $\Omega$ , CVH = 1 $\mu$ F,<br>I(VH) = 050 mA        | 6.3      | 6.7        | 7.4        | V        |

| 902         | VHnr                  | Nominal Voltage at VH, LVH re-<br>placed by a resistor  | R = 170 Ω, I(VH) = 010 mA                                                            | 6.3      |            | 8.4        | V        |

| 903         | la(VHL)               | max. DC Cut-Off Current in VHL                          |                                                                                      | -200     |            |            | mA       |

| 904         | Va(VH)                | Cut-Off Voltage at VH                                   | Va(VH) > VHn                                                                         | 6.5      | 7.3        | 8.4        | V        |

| 906         | Vs(VHL)               | Saturation Voltage at VHL vs.<br>VBR                    | I(VHL) = -50 mA<br>I(VHL) = -150 mA                                                  |          | 0.5<br>1.5 | 1.1<br>3.0 | V<br>V   |

| 907         | Vf(VHL)               | Saturation Voltage at VHL vs.<br>GND                    | Vf(VHL) = V(GND) - V(VHL);<br>I(VHL) = -50 mA<br>I(VHL) = -150 mA                    |          | 0.6<br>1.7 | 1.5<br>2.9 | V<br>V   |

| 908         | llk(VHL)              | Leakage Current at VHL                                  | VHL = IO, V(VHL) = V(VH)                                                             | -20      |            | 20         | μA       |

| 909         | η ν Η                 | Efficiency of VH switching regula-<br>tor               | I(VH) = 50 mA, Ri(LVH) < 1.1 Ω,<br>V(VBR) = 1230 V                                   | 70       |            |            | %        |

Rev C1, Page 11/26

| ltem<br>No. | Symbol            | Parameter                                                        | Conditions                                                                                                                                                                                                             | Min.        | Тур. | Max.        | Unit       |

|-------------|-------------------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------|-------------|------------|

| Series      | Regulator         | vcc                                                              |                                                                                                                                                                                                                        |             |      |             |            |

| A01         | VCCn              | Nominal Voltage at VCC                                           | I(VCC) = -500 mA, VH = VHn                                                                                                                                                                                             | 4.75        | 5    | 5.25        | V          |

| A02         | CVCC              | Required Capacitor at VCC vs.<br>GND                             |                                                                                                                                                                                                                        | 150         |      |             | nF         |

| A03         | RiCVCC            | Maximum Permissible Internal<br>Resisitance of capacitor at VCC  |                                                                                                                                                                                                                        |             |      | 1           | Ω          |

| A04         | VCCon             | VCC Monitor Threshold hi                                         |                                                                                                                                                                                                                        | 89          |      | 98          | %VCCn      |

| A05         | VCCoff            | VCC Monitor Threshold lo                                         | Decreasing Voltage at VCC                                                                                                                                                                                              | 80          |      | 90          | %VCCn      |

| A06         | VCChys            | Hysteresis                                                       | VCChys = VCCon - VCCoff                                                                                                                                                                                                | 50          | 500  |             | mV         |

| Series      | Regulator         | VCC3                                                             |                                                                                                                                                                                                                        |             |      |             |            |

| B01         | VCC3n             | Nominal Voltage at VCC3                                          | I(VCC3) = -500 mA, VH = VHn                                                                                                                                                                                            | 3.1         | 3.3  | 3.5         | V          |

| B02         | CVCC3             | Required Capacitor at VCC3 vs.<br>GND                            |                                                                                                                                                                                                                        | 150         |      |             | nF         |

| B03         | RiCVCC3           | Maximum Permissible Internal<br>Resisitance of capacitor at VCC3 |                                                                                                                                                                                                                        |             |      | 1           | Ω          |

| B04         | VCC3on            | VCC3 Monitor Threshold hi                                        |                                                                                                                                                                                                                        | 89          |      | 98          | %<br>VCC3n |

| B05         | VCC3off           | VCC3 Monitor Threshold lo                                        | Decreasing Voltage at VCC3                                                                                                                                                                                             | 80          |      | 90          | %<br>VCC3n |

| B06         | VCC3hys           | Hysteresis                                                       | VCC3hys = VCC3on - VCC3off                                                                                                                                                                                             | 50          | 200  |             | mV         |

| Oscill      | ator              | -                                                                |                                                                                                                                                                                                                        |             |      |             |            |

| C01         | fos <sub>ss</sub> | Spread Spectrum Oscillator Fre-<br>quency                        | Average value from 64 clock cycles                                                                                                                                                                                     | 0.88        |      | 1.5         | MHz        |

| C02         | Tos <sub>ss</sub> | Single Clock Cycle Periode<br>(spread spectrum oscillator)       |                                                                                                                                                                                                                        | 0.571       |      | 1.35        | μs         |

| C03         | fos               | Fixed Oscillator Frequency                                       | Tj = 27 °C                                                                                                                                                                                                             | 1.5<br>1.53 |      | 2.5<br>2.43 | MHz<br>MHz |

| Refer       | ence and Bi       | as                                                               |                                                                                                                                                                                                                        |             |      |             |            |

| D01         | V(ISET)           | Voltage at ISET                                                  | Tj = 27 °C                                                                                                                                                                                                             | 1.12        | 1.24 | 1.29        | V          |

| D02         | Isc(ISET)         | Short Circuit Current in ISET                                    | V(ISET) = 0 V, Tj = 27 °C                                                                                                                                                                                              | -0.55       | -0.4 | -0.28       | mA         |

| D03         | rlbeg             | Transmission Ratio for driver<br>output current limitation       | $\begin{array}{l} \text{Imax}(\text{QP1}) = \text{Imax}(\text{QP2}) = \text{Imax}(\text{QN1}) = \\ \text{Imax}(\text{QN2}) = \text{I}(\text{ISET}) * \text{rlbeg}, \\ \text{RSET} = 5.120 \text{ k}\Omega \end{array}$ |             | 800  |             |            |

Rev C1, Page 12/26

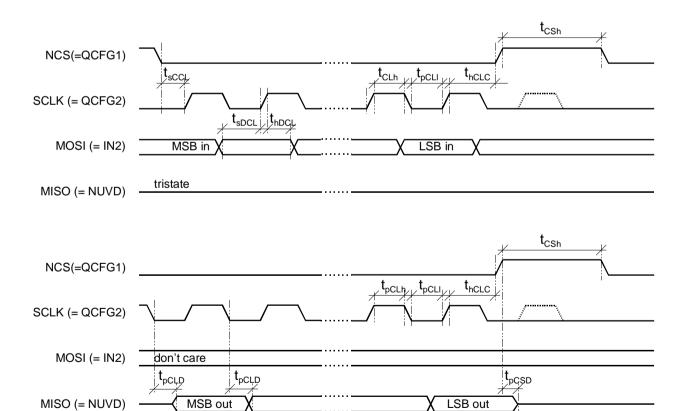

#### **OPERATING REQUIREMENTS: SPI Interface**

#### Operating Conditions: VBO = 9...30 V (referenced to VN), Tj = -40...125 °C

| ltem | Symbol | Parameter                                                            | Conditions |      |      | Unit |

|------|--------|----------------------------------------------------------------------|------------|------|------|------|

| No.  |        |                                                                      |            | Min. | Max. |      |

| 1001 | tsCCL  | Setup Time: NCS hi $\rightarrow$ lo before SCLK lo $\rightarrow$ hi  |            | 15   |      | ns   |

| 1002 | tsDCL  | Setup Time: MOSI stable before SCLK lo $\rightarrow$ hi              |            | 20   |      | ns   |

| 1003 | thDCL  | Hold Time: MOSI stable after SCLK lo $\rightarrow$ hi                |            | 0    |      | ns   |

| 1004 | tCLh   | Signal Duration SCLK hi                                              |            | 30   |      | ns   |

| 1005 | tCLI   | Signal Duration SCLK lo                                              |            | 30   |      | ns   |

| 1006 | thCLC  | Hold Time: NCS lo after SCLK lo $\rightarrow$ hi                     |            | 0    |      | ns   |

| 1007 | tCSh   | Signal Duration NCS hi                                               |            | 0    |      | ns   |

| 1008 | tpCLD  | Propagation Delay: MISO stable after SCLK hi $\rightarrow$ lo        |            | 0    | 90   | ns   |

| 1009 | tpCSD  | Propagation Delay: MISO high impedance after NCS lo $\rightarrow$ hi |            | 0    | 25   | ns   |

| 1010 | f(SPI) | SPI Frequency                                                        |            |      | 5    | MHz  |

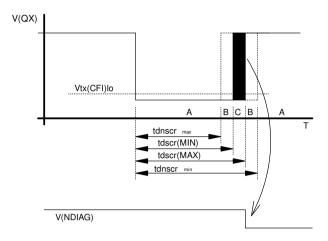

Figure 1: SPI write cycle (top) and read cycle (bottom)

#### **DESCRIPTION OF FUNCTIONS**

iC-GF has two independent switching channels which enables digital sensors to drive peripheral elements. They are designed to cope with high driver currents. The switches are reverse-polarity protected, feature a free-wheeling circuit for inductive loads and a saturation voltage minimising system.

#### **Reverse polarity protection**

The pins VBO, QPx, QNx, VN and CFI on the *line side* of the chip are reverse polarity protected. As far as the maximum voltage ratings are not exceeded, no possible supply combination at the *line side* pins can damage the chip.

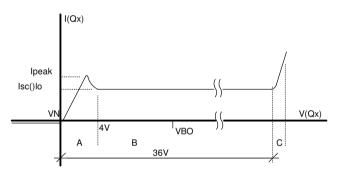

Figure 2: QNx characteristic when active

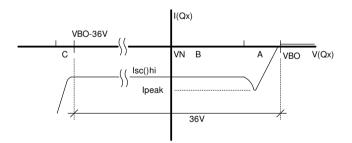

Figure 3: QPx characteristic when active

#### Output characteristics of Q1, Q2

The switching channels are current limited to a value set by the external resistor RSET (cf. Electrical Characteristics No. D03). If pin ISET is short circuited to GND, the current limitation will be set to a maximum value (cf. Electrical Characteristics Nos. 108, 208). The current limitation works only for voltages higher than 4 V at QNx resp. lower than VBO - 4 V at QPx. For smaller output voltages the current limitation is reduced in order to minimise the saturation voltages without increasing the power dissipation. Figures 2 and 3 show the characteristic of the switching channels when activated. Region "A" is the saturation range, where the current limitation is not fully active yet and region "B" is the current limited range. Region "C" cor-

responds to the free-wheeling circuit activated. The switching channels are designed so that QNx can only sink current and QPx can only source current (no reverse current).

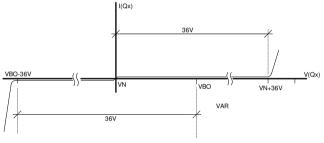

#### Free-wheeling circuit for inductive loads

The free-wheeling circuit is always present and does not depend on the current output status. It is activated by voltages higher than 36 V at QNx referenced to VN or lower than -36 V at QPx referenced to VBO. In that case the correspondent channel will switch on without current limitation (see Figure 4).

Figure 4: Free-wheeling characteristic

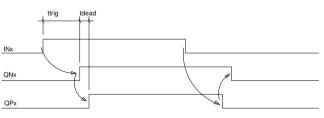

#### **Dead time**

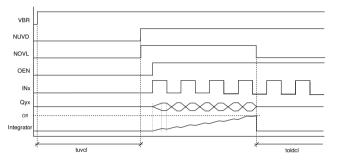

In order to avoid current flow between high- and lowside switch in push-pull configuration, a dead time  $t_{dead}$ is implemented as shown in Figure 5 (cf. Electrical Characteristics Nos. 112 and 212).

Figure 5: Propagation delay

#### **Overload detection**

To protect the device against excessive power dissipation due to high currents the switches are clocked if an overload occurs. If a short circuit is detected, i.e. if the voltage at the switch output overshoots or undershoots *Overload Detection Threshold off* (cf. Electrical Characteristics Nos. 104 and 204), the switches are shut down for a typical 50 ms (cf. Electrical Characteristics No. 302) and the current flow thus interrupted.

The level of power dissipation depends on the current and the time during which this current flows. A current which fails to trigger the overload detection

# **iC-GF ⊘ IO**-Link TRANSCEIVER

Rev C1, Page 14/26

is not critical; high current can also be tolerated for a short period and with low repeat rates. This is particularly important when switching capacitive loads (charge/discharge currents).

Figure 6: Permanent short circuit

Figure 7: Overload

So that this is possible a shared back-end integrator follows the switches for the purpose of overload detection. This integrator is an 8-bit counter which is updated together with the oscillator clock. If an overload is detected on one channel the counter is incremented by 1; an overload on both channels increments the counter by 2. If no overload is apparent the counter is decremented by 1 every 10 clock pulses. A maximum duty cycle – without deactivation of the switches – of 1:10 results if one channel is overloaded. Only when this ratio is exceeded the counter can reach its maximum value, generating an error message at NOVL and deactivating the switches.

#### Undervoltage detection

iC-GF features two separate undervoltage detectors: voltage monitoring at VBO and voltage monitoring at

VCC and VCC3. Both undervoltage detectors are filtered against spurious events smaller than  $25 \,\mu s$  (cf. Electrical Characteristics No. 404). In case of a valid undervoltage event (longer than  $25 \,\mu s$ ) both QPx and QNx are unconditionally brought to high impedance for at least 35 ms (cf. Electrical Characteristics No. 405) resp. as long as the duration of the undervoltage situation.

#### Digital filtering at inputs

To obtain high noise immunity the pins QCFGx, INV1/ESPI, IN1/TX, IN2, OEN, CFI and CFP have a digital input filter. Figure 5 shows this filter time  $t_{trig}$  for INx (cf. Electrical Characteristics Nos. 613 to 616 and 816 to 819).

#### Feedback channel CFI–CFO

iC-GF implements a feedback channel which permits a communication from the *line side* to the *sensor side*. *High voltage* digital signals at CFI are converted into low voltage (open-collector) levels at CFO.

#### Spread spectrum oscillator

To reduce the electromagnetic interference generated by the switching converter (pin VHL) a *spread spectrum oscillator* has been introduced. Here the switch is not triggered by a fixed frequency but by a varying 32 step frequency mix. Generated interference is then distributed across the frequency spectrum with its amplitude reduced at the same time.

#### **Configuration mode**

Leaving pin INV1 unconnected (cf. Table 1) selects SPI mode for configuration. All functions implemented in DEFAULT mode are also available in SPI mode plus some additional functions, available in SPI mode only.

| Mode Select |         |  |  |

|-------------|---------|--|--|

| INV1        | MODE    |  |  |

| L           | DEFAULT |  |  |

| Н           | DEFAULT |  |  |

| Z           | SPI     |  |  |

Table 1: Operating mode configuration

# **C**Haus

Rev C1, Page 15/26

#### **DEFAULT MODE**

#### **Enabling the switches**

Setting pin OEN to low unconditionally disables all four output switches. Other functions of the chip (like the DC/DC converter or the feedback channel) remain enabled.

#### Configuring the switches

The functionality of the switches is determined by the pins QCFG1 and QCFG2. A voltage at QCFGx which is lower than Va()lo (cf. Figure 8) deactivates the relevant high-side switches; with a voltage higher than Va()hi the relevant low-side switches are deactivated. Both high-side and low-side switches are activated, when the pin is left open.

Figure 8: Levels at QCFG1/QCFG2 for switch configuration

| CHA | CHANNEL 1 |      |     |     |     |  |

|-----|-----------|------|-----|-----|-----|--|

| IN1 | QCFG1     | INV1 | OEN | QN1 | QP1 |  |

| Х   | Х         | Х    | L   | off | off |  |

| L   | Z         | L    | Н   | on  | off |  |