Rev D4, Page 1/39

#### **FEATURES**

Latency-free sine-to-digital conversion to 400 angle steps 500 kHz input frequency for interpolation factors of x1 and x2 (10 kHz for x100)

Flexible pin assignment due to signal path multiplexers PGA inputs for differential and single-ended signals Variable input resistance for current/voltage conversion Signal conditioning for offset, amplitude and phase Controlled 50 mA current source for LED or MR sensor supply Fault-tolerant RS422 outputs with 50 mA sink/source drive current

Preselectable minimum phase distance for spike-proof counter stimulus

Zero signal conditioning and electronic index pulse generation Signal and operation monitoring with configurable alarm output, output shutdown and error storage

I<sup>2</sup>C multimaster interface for in-circuit calibration and parameters (EEPROM)

Adjustable overtemperature alarm and shutdown Supply from 4.3 to 5.5 V, operation from -25(-40) to +100 °C Reverse polarity proof including the sub-system

#### **APPLICATIONS**

Optical and magnetic position sensors Angle encoders Linear scales

#### **PACKAGES**

TSSOP20

Rev D4, Page 2/39

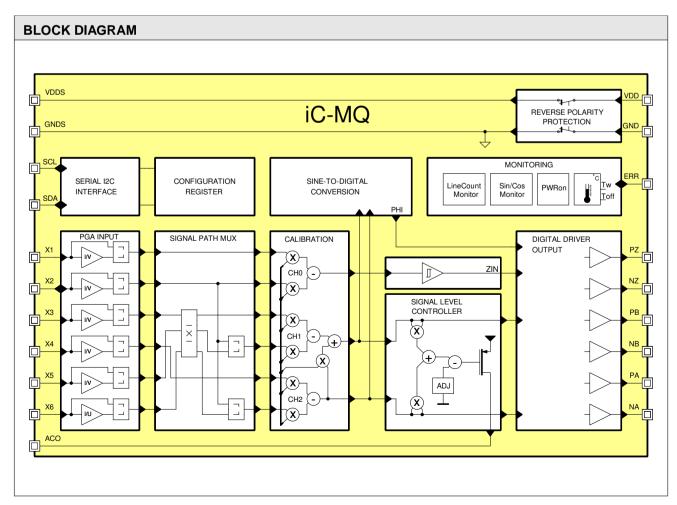

#### DESCRIPTION

Interpolator iC-MQ is a non-linear A/D converter which digitizes sine/cosine sensor signals using a count-safe tracking conversion principle with selectable resolution and hysteresis. The angle resolution per sine period can be set using SELRES; up to 400 angle steps are possible (see page 26).

The angle position is output incrementally by differential RS422 drivers as an encoder quadrature signal with a zero pulse or, if selected, as a counter signal for devices compatible with 74HC191 or 74HC193.

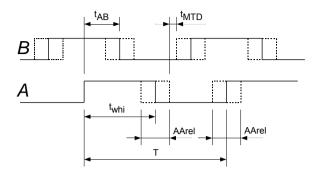

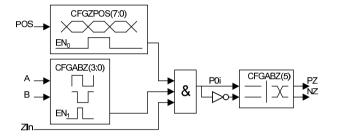

The zero pulse is generated electronically when an enable has been set by the X1/X2 inputs. This pulse can be configured extensively: both in its relative position to the input signal with regard to the logic gating with A and/or B and in its width from 90° to 360° (1/4 to 1 T).

A preselectable minimum transition distance permits glitch-free output signals and prevents counting errors which in turn boosts the noise immunity of the position encoder.

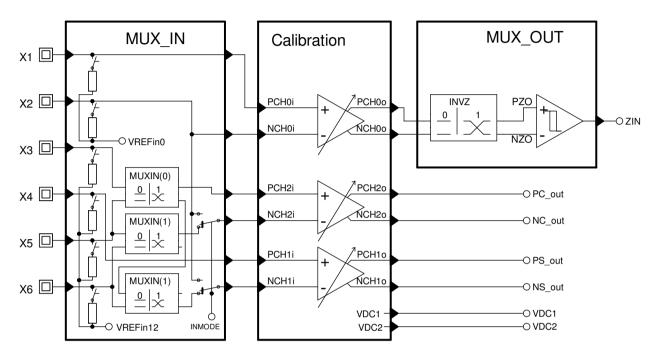

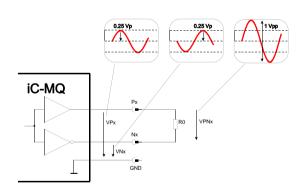

Programmable instrumentation amplifiers with selectable gain levels allow differential or single-ended, referenced input signals; via input X2 the external reference can be used as reference voltage for the offset correction.

The modes of operation differentiate between high impedance (V modes) and low impedance (I modes). This adaptation of the iC to voltage or current signals enables MR sensor bridges or photosensors to be directly connected up to the device. The optical scanning of low resolution code discs is also supported by the reference function of input X2; these discs do not evaluate tracks differentially but in comparison with a reference photodiode.

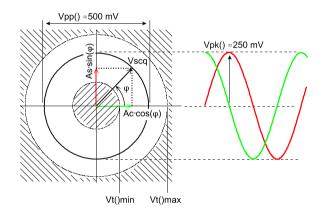

The integrated signal conditioning unit allows signal amplitudes and offset voltages to be calibrated accurately and also any phase error between the sine and cosine signals to be corrected. The channel for the zero signal can be configured separately.

A control signal is generated from the conditioned signals which can track the transmitting LED of optical encoders via the integrated 50 mA driver stage (output ACO). If MR sensors are connected this driver stage can also track the power supply of the measuring bridges. By tracking the sensor energy supply any temperature and aging effects are compensated for, the input signals stabilized and the exact calibration of the input signals is maintained. This enables a constant accuracy of the interpolation circuit across the entire operating temperature range.

When control limits are reached, these can be indicated at the maskable error pin ERR. Faults such as overdrive, wire breakage, short circuiting, dirt or aging, for example, are logged.

iC-MQ includes extensive self-test and system diagnosis functions which check whether the sensor is working properly or not. For all error events the user can select whether the fault be displayed at error pin ERR or the outputs shutdown. At the same time errors can be stored in the EEPROM to enable failures to be diagnosed at a later stage. For encoder applications the line count of the code disc, the sensor signal regarding signal level and frequency and the operating temperature can be monitored, for example, the latter using an adjustable on-chip sensor.

Display error pin ERR is bidirectional; a system fault recognized externally can be recorded and also registered in the error memory.

iC-MQ is protected against reverse polarity and offers its monitored supply voltage to the external circuit, thus extending the protection to the system (for load currents to 20 mA). Reverse polarity protection also covers the short-circuit-proof line drivers so that an unintentional faulty wiring during initial operation is tolerated.

On being activated the device configuration is loaded via the serial configuration interface from an external EEPROM and verified by a CRC. A microcontroller can also configure iC-MQ; the implemented interface is multimaster-competent and enables direct RAM access.

Rev D4, Page 3/39

#### **CONTENTS**

| PACKAGES                                               | 4  | Photodiode array connected to current inputs, LED supply with constant |    |

|--------------------------------------------------------|----|------------------------------------------------------------------------|----|

| ABSOLUTE MAXIMUM RATINGS                               | 5  | current source                                                         | 23 |

|                                                        |    | 2. Encoder supplying 100 mVpp to voltage                               |    |

| THERMAL DATA                                           | 5  | inputs                                                                 | 23 |

| ELECTRICAL CHARACTERISTICS                             | 6  | SIGNAL CONDITIONING CH0                                                | 24 |

|                                                        |    | Gain Settings CH0                                                      | 24 |

| PROGRAMMING                                            | 11 | Offset Calibration CH0                                                 | 24 |

| REGISTER MAP                                           | 12 | SIGNAL LEVEL CONTROL and SIGNAL MONITORING                             | 25 |

| SERIAL CONFIGURATION INTERFACE                         | 14 | SINE-TO-DIGITAL CONVERSION                                             | 26 |

| Example of CRC Calculation Routine                     | 14 | SINE-10-DIGITAL CONVERSION                                             | 20 |

| EEPROM Selection                                       | 14 | OUTPUT SETTINGS AND ZERO SIGNAL                                        | 27 |

| I <sup>2</sup> C Slave Mode (ENSL=1)                   | 15 | Zero Signal Generation                                                 | 27 |

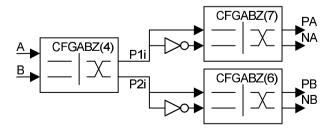

|                                                        |    | Description Of CFGABZ Setup                                            | 28 |

| BIAS CURRENT SOURCE AND TEMPERATURE SENSOR CALIBRATION | 16 | Setup Example 1                                                        | 28 |

|                                                        | 16 | Setup Example 2                                                        | 28 |

| Bias Current                                           | 16 | Output Driver Configuration                                            | 29 |

| Temperature Sensor                                     | 10 | Minimum Phase Distance                                                 | 29 |

| OPERATING MODES                                        | 17 | ERROR MONITORING AND ALARM OUTPUT                                      | 30 |

| Mode ABZ                                               | 17 | Error Protocol                                                         | 31 |

| Mode 191/193                                           | 17 | Line Count Error                                                       | 31 |

| Calibration 1, 2, 3                                    | 17 | Temperature Monitoring                                                 | 31 |

| TEST 6                                                 | 18 |                                                                        |    |

| System Test                                            | 18 | REVERSE POLARITY PROTECTION                                            | 32 |

| INPUT CONFIGURATION                                    | 19 | TEST MODE                                                              | 33 |

| Current Signals                                        | 19 | Quick programming in the                                               |    |

| Voltage Signals                                        |    | single master system                                                   | 34 |

|                                                        |    | Quick programming in the multimaster system                            | 34 |

| SIGNAL PATH MULTIPLEXING                               | 20 | mullimaster system                                                     | 34 |

| SIGNAL CONDITIONING CH1, CH2                           | 21 | EXAMPLE APPLICATIONS                                                   | 35 |

| Gain Settings                                          | 21 | APPLICATION HINTS                                                      | 37 |

| Offset Calibration CH1, CH2                            | 22 | In-circuit programming of the EEPROM                                   | 37 |

| Phase Correction CH1 vs. CH2                           | 22 | Absolute angle accuracy and edge jitter                                | 37 |

| Signal Conditioning Examples                           |    | Information on the demo board                                          |    |

Rev D4, Page 4/39

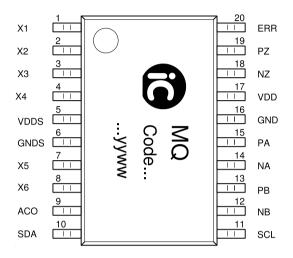

#### **PACKAGES**

#### **PIN CONFIGURATION TSSOP20**

#### PIN FUNCTIONS

| No. | Name        | Function                                        |

|-----|-------------|-------------------------------------------------|

| 1   | X1          | Signal Input 1 (Index +)                        |

| 2   | X2          | Signal Input 2 (Index -)                        |

| 3   | X3          | Signal Input 3                                  |

| 4   | X4          | Signal Input 4                                  |

| 5   | VDDS        | Switched Supply Output                          |

|     |             | (reverse polarity proof, load to 20 mA max.)    |

| 6   | <b>GNDS</b> | Switched Ground                                 |

|     |             | (reverse polarity proof)                        |

| 7   | X5          | Signal Input 5                                  |

| _   | X6          | Signal Input 6                                  |

| 9   | ACO         | Signal Level Controller,                        |

|     |             | high-side current source output                 |

| 10  | SDA         | Serial Configuration Interface,                 |

|     |             | data line                                       |

| 11  | SCL         | Serial Configuration Interface,                 |

|     |             | clock line                                      |

|     | NB          | Incremental Output B-                           |

|     | PB          | Incremental Output B+                           |

|     | NA          | Incremental Output A-                           |

|     | PA          | Incremental Output A+                           |

|     | GND         |                                                 |

|     | VDD         | +4.35.5 V Supply Voltage                        |

| _   | NZ          | Incremental Output Z-                           |

|     | PZ          | Incremental Output Z+                           |

| 20  | ERR         | Error Signal (In/Out) / Test Mode Trigger Input |

Rev D4, Page 5/39

#### **ABSOLUTE MAXIMUM RATINGS**

These ratings do not imply operating conditions; functional operation is not guaranteed. Beyond these ratings device damage may occur.

| Item | Symbol | Parameter                                             | Conditions                           |      |            | Unit |

|------|--------|-------------------------------------------------------|--------------------------------------|------|------------|------|

| No.  |        |                                                       |                                      | Min. | Max.       |      |

| G001 | V()    | Voltage at VDD, PA, NA, PB, NB, PZ, NZ, SCL, SDA, ACO |                                      | -6   | 6          | V    |

| G002 | V()    | Voltage at ERR                                        |                                      | -6   | 8          | V    |

| G003 | V()    | Pin-Pin Voltage                                       |                                      |      | 6          | V    |

| G004 | V()    | Voltage at X1X6, SCL, SDA                             |                                      | -0.3 | VDDS + 0.3 | V    |

| G005 | I(VDD) | Current in VDD                                        |                                      | -20  | 400        | mA   |

| G006 | I()    | Current in VDDS, GNDS                                 |                                      | -50  | 50         | mA   |

| G007 | I()    | Current in X1X6, SCL, SDA, ERR                        |                                      | -20  | 20         | mA   |

| G008 | I()    | Current in PA, NA, PB, NB, PZ, NZ                     |                                      | -100 | 100        | mA   |

| G009 | I(ACO) | Current in ACO                                        |                                      | -100 | 20         | mA   |

| G010 | Vd()   | ESD Susceptibility at all pins                        | HBM 100 pF discharged through 1.5 kΩ |      | 2          | kV   |

| G011 | Ptot   | Permissible Power Dissipation                         |                                      |      | 300        | mW   |

| G012 | Tj     | Junction Temperature                                  |                                      | -40  | 150        | °C   |

| G013 | Ts     | Storage Temperature                                   |                                      | -40  | 150        | °C   |

#### THERMAL DATA

| Item | Symbol | Parameter                                                                 | Conditions |      |      |      | Unit |

|------|--------|---------------------------------------------------------------------------|------------|------|------|------|------|

| No.  |        |                                                                           |            | Min. | Тур. | Max. |      |

| T01  | Та     | Operating Ambient Temperature Range (extended range to -40 °C on request) |            | -25  |      | 100  | °C   |

| T02  | Rthja  | Thermal Resistance Chip to Ambient                                        |            |      | 80   |      | K/W  |

Rev D4, Page 6/39

#### **ELECTRICAL CHARACTERISTICS**

Operating Conditions: VDD = 4.3...5.5 V, Tj = -40 °C...125 °C, IBN calibrated to 200 µA, unless otherwise stated

| Item<br>No. | Symbol      | Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Conditions                                                                                                            | Min.                           | Тур.                           | Max.                           | Unit                         |

|-------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------|--------------------------------|--------------------------------|------------------------------|

| Total I     | Device      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                       |                                |                                |                                | II.                          |

| 001         | V(VDD)      | Permissible Supply Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Load current I(VDDS) to 10 mA                                                                                         | 4.3                            |                                | 5.5                            | V                            |

|             | ` ′         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Load current I(VDDS) to 20 mA                                                                                         | 4.5                            |                                | 5.5                            | V                            |

| 002         | I(VDD)      | Supply Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Tj = -40125 °C, no load<br>Tj = 27 °C, no load                                                                        |                                | 12                             | 25                             | mA<br>mA                     |

| 003         | I(VDDS)     | Permissible Load Current VDDS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ,, _, ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,                                                                               | -20                            |                                | 0                              | mA                           |

| 004         | Vcz()hi     | Clamp-Voltage hi at all pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                       |                                |                                | 11                             | V                            |

| 005         | Vc()hi      | Clamp-Voltage hi at Inputs SCL,<br>SDA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Vc()hi = V() - V(VDD), I() = 1 mA                                                                                     | 0.4                            |                                | 1.5                            | V                            |

| 006         | Vc()hi      | Clamp-Voltage hi at Inputs<br>X1X6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Vc()hi = V() - V(VDD), I() = 4 mA                                                                                     | 0.3                            |                                | 1.2                            | V                            |

| 007         | Vc()lo      | Clamp-Voltage lo at all pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I() = -4 mA                                                                                                           | -1.2                           |                                | -0.3                           | V                            |

|             |             | ing, Inputs X1X6 (CH1, CH2: i =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0                                                                                                                     | 1.2                            |                                | 0.5                            |                              |

| 101         | Vin()sig    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | RINi() = 0x01                                                                                                         | 0.75                           |                                | VDDS                           | V                            |

| 101         | VIII()Sig   | remissible input voltage Kange                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                       |                                |                                | <b>– 1.5</b>                   |                              |

| 400         | 11 - () - 1 | Daniel de la control de la con | RINi() = 0x09                                                                                                         | 0                              |                                | VDDS                           | V                            |

| 102         | lin()sig    | Permissible Input Current Range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | RINi(0) = 0; BIASi = 0<br>RINi(0) = 0; BIASi = 1                                                                      | -300<br>10                     |                                | -10<br>300                     | μA<br>μA                     |

| 103         | lin()       | Input Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | RINi() = 0x01                                                                                                         | -10                            |                                | 10                             | μΑ                           |

| 104         | Rin()       | Input Resistance vs. VREFin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Tj = 27 °C;<br>RINi(3:0) = 0x09<br>RINi(3:0) = 0x00<br>RINi(3:0) = 0x02<br>RINi(3:0) = 0x04<br>RINi(3:0) = 0x06       | 16<br>1.1<br>1.6<br>2.2<br>3.2 | 20<br>1.6<br>2.3<br>3.2<br>4.6 | 24<br>2.1<br>3.0<br>4.2<br>6.0 | kΩ<br>kΩ<br>kΩ<br>kΩ<br>kΩ   |

| 105         | TC(Rin)     | Temperature Coefficient of Rin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                       |                                | 0.15                           |                                | %/K                          |

| 106         | VREFin()    | Reference Voltages<br>VREFin0, VREFin12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | RINi(0) = 0, BIASi = 1<br>RINi(0) = 0, BIASi = 0                                                                      | 1.35<br>2.25                   | 1.5<br>2.5                     | 1.65<br>2.75                   | V                            |

| 107         | G0, G12     | Selectable Gain Factors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | RINi(3) = 0, GRi and GFi = 0x0<br>RINi(3) = 0, GRi and GFi = max.<br>RINi(3) = 1, GRi and GFi = 0x0                   |                                | 2<br>100<br>0.5                |                                | -                            |

|             |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | RINi(3) = 1, GRi and GFi = max.                                                                                       |                                | 25                             |                                |                              |

| 108         | Gdiff       | Relative Gain Ratio CH1 vs. CH2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | GF2 = 0x10, GF1 = 0x0<br>GF2 = 0x10, GF1 = 0x7F                                                                       |                                | 39<br>255                      |                                | %<br>%                       |

| 109         | ΔG          | Step Width Of Fine Gain<br>Adjustment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | for CH0<br>for CH1<br>for CH2                                                                                         |                                | 1.06<br>1.015<br>1.06          |                                |                              |

| 110         | INL(Gi)     | Integral Linearity Error of Gain Adjustment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                       | -1.06                          |                                | 1.06                           |                              |

| 111         | Vin()diff   | Recommended Differential Input<br>Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Vin()diff = V(PCHx) - V(NCHx);<br>RINi(3) = 0<br>RINi(3) = 1                                                          | 10<br>40                       |                                | 500<br>2000                    | mVpp<br>mVpp                 |

| 112         | Vin()os     | Input Offset Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | referred to side of input                                                                                             |                                | 25                             |                                | μV                           |

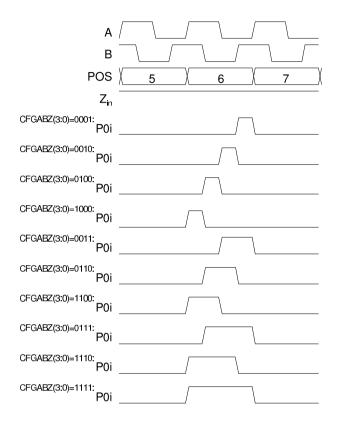

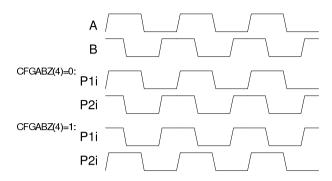

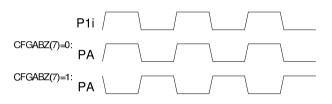

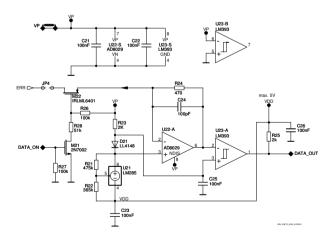

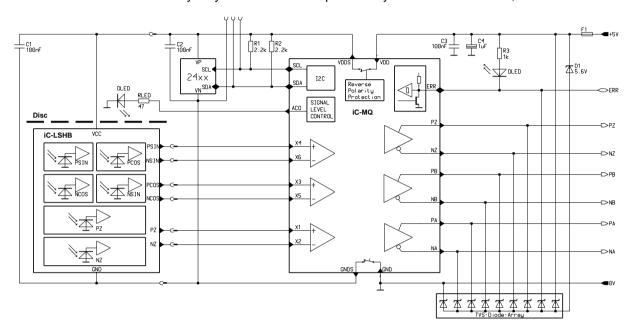

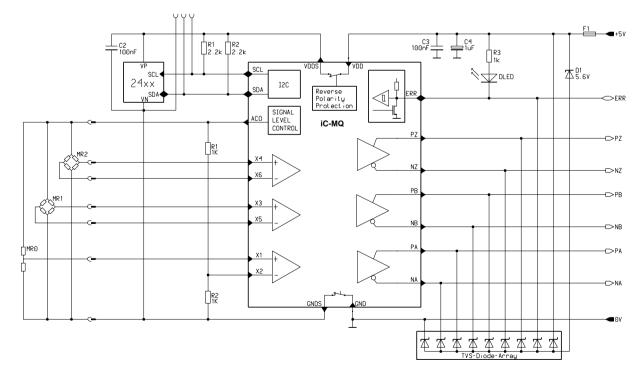

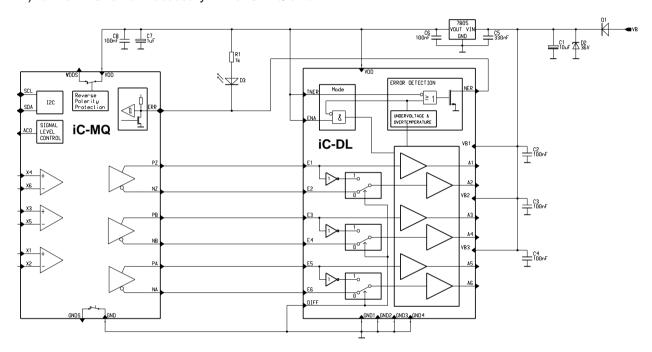

| 113         | VOScal      | Offset Calibration Range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | referenced to the selected source (VOS0 resp. VOS12), mode <i>Calibration 2</i> ; ORi = 00 ORi = 01 ORi = 10 ORi = 11 |                                | ±100<br>±200<br>±600<br>±1200  |                                | %V()<br>%V()<br>%V()<br>%V() |