# RCD

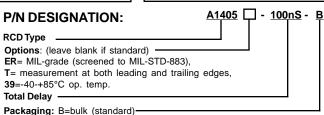

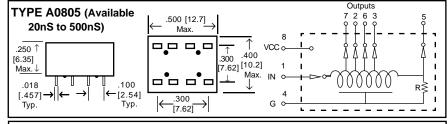

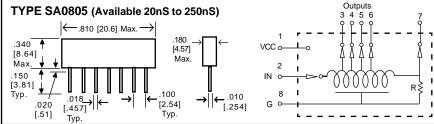

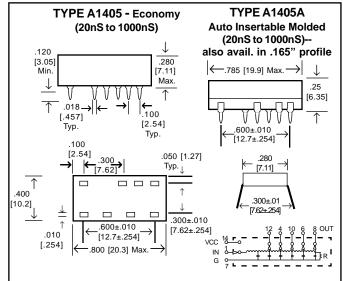

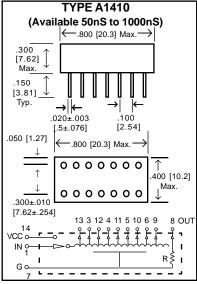

# ACTIVE (DIGITAL) DELAY LINES A0805 SERIES 5-TAP 8-PIN DIP SA0805 SERIES 5-TAP 8-PIN DIP A1405 SERIES 5-TAP 8-PIN DIP A1410 SERIES 10-TAP 14-PIN DIP

### Wide selection of sizes!

RCD's digital delay lines have been designed to provide precise tap delays with all the necessary drive and pick-off circuitry. All inputs and outputs are schottky-type and require no additional components to achieve specified delays. Encapsulated/molded construction ensures full compliance to all applicable requirements of MIL-D-23859. Units are 100% inspected for solder joint integrity and electrical conformance.

# **FEATURES**

- ☐ Economical cost, prompt delivery!

- ☐ Wide varieties of values

- ☐ Choice of 5 or 10 equally spaced taps

- ☐ TTL and DTL compatible

- ☐ Operating temperature: 0°C to 70°C

- Excellent for applications requiring high delay stability, fast rise times and no jitter, such as memory boards, disk drives, and signal processing

### **OPTIONS**

- Non-standard delay times or tolerances

- Non-symmetrical tap delays

- □ Dynamic RAM timing delay

- □ Faster rise times

- ☐ ECL, H-CMOS, and low power designs available

- Measurement at both leading and trailing edges (Opt. T).

- ☐ Ceramic IC's screened to MIL-STD-883, -55 to +125°C per MIL-D-83532 (Opt. ER)

- ☐ Fast logic TTL available

## **TEST CONDITIONS @25°C**

- 1) Delay measured at 1.5V on leading edge only with no loads on output.

- 2) Rise time measured from 0.75V to 2.4V.

- 3) Delay will inversely vary approximately 4% for every 5% change in supply voltage.

- 4) Supply voltage (VCC) = 5.0±.25VDC

- 5) Input test pulse: 3.2V, 2nS rise time, width>40% of total delay, pulse period to be a minimum of 3x the pulse width.

### Delay Per Tap (nSec) Total A0805 Delay **SA080** A1410 A1405 20 25 5 30 6 40 8 50 10 60 12 7.5 75 15 100 20 10 125 25 125 150 30 15 175 35 17.5 40 200 20 250 50 25 300 60 30 350 70 35 400 80 40 450 45 90 500 100 50 750 150 75 1000 200

\* Consult factory for availability

### **ELECTRICAL CHARACTERISTICS**

| ELECTRICAL CHARACTERISTICS |                                   |

|----------------------------|-----------------------------------|

| Total Delay Tolerance      | ±5% or 2nS (whichever is greater) |

| Tap Delay Tolerance        | ±5% or 2nS (whichever is greater) |

| Insulation Resistance      | 1000M $\Omega$ min.               |

| Dielectric Strength        | 100VDC                            |

| Rise Time                  | 4nS max.                          |

|                            |                                   |