# **Plastic Power Transistors**

# **SO-8 for Surface Mount Applications**

- Collector –Emitter Sustaining Voltage  $V_{CEO(sus)} = 30 \text{ Vdc (Min)} @ I_C = 10 \text{ mAdc}$

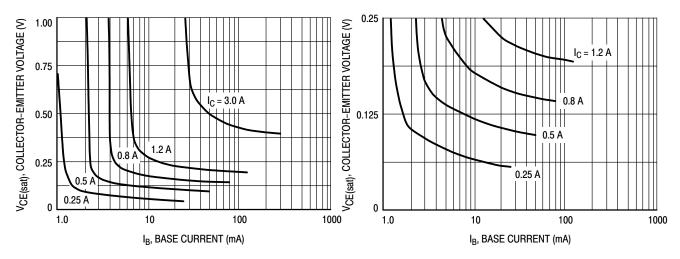

- High DC Current Gain  $h_{FE} = 125$  (Min) @  $I_C = 0.8$  Adc = 90 (Min) @  $I_C = 3.0$  Adc

• Miniature SO-8 Surface Mount Package - Saves Board Space

# MMDJ3P03BJT

**ON Semiconductor Preferred Device**

DUAL BIPOLAR

POWER TRANSISTOR

PNP SILICON

30 VOLTS

3 AMPERES

CASE 751-07, Style 16 (SO-8)

## **MAXIMUM RATINGS** ( $T_C = 25^{\circ}C$ unless otherwise noted)

| Rating                                           | Symbol                            | Value       | Unit |

|--------------------------------------------------|-----------------------------------|-------------|------|

| Collector-Base Voltage                           | V <sub>CB</sub>                   | 45          | Vdc  |

| Collector–Emitter Voltage                        | V <sub>CEO</sub>                  | 30          | Vdc  |

| Emitter–Base Voltage                             | V <sub>EB</sub>                   | ±6.0        | Vdc  |

| Collector Current — Continuous<br>— Peak         | I <sub>C</sub>                    | 3.0<br>5.0  | Adc  |

| Base Current — Continuous                        | I <sub>B</sub>                    | 1.0         | Adc  |

| Operating and Storage Junction Temperature Range | T <sub>J</sub> , T <sub>stg</sub> | -55 to +150 | °C   |

## THERMAL CHARACTERISTICS

| Characteristic                                                                                                                                                                                                                                                | Symbol         | Max        | Unit           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------|----------------|

| Thermal Resistance – Junction to Ambient on 1" sq. (645 sq. mm) Collector pad on FR–4 board material with one die operating. Thermal Resistance – Junction to Ambient on 0.012" sq. (7.6 sq. mm) Collector pad on FR–4 board material with one die operating. | $R_{\thetaJA}$ | 100<br>185 | °C/W           |

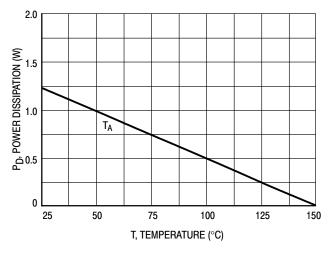

| Total Power Dissipation @ T <sub>A</sub> = 25°C mounted on 1" sq. (645 sq. mm) Collector pad on FR–4 board material with one die operating. Derate above 25°C                                                                                                 | $P_{D}$        | 1.25<br>10 | Watts<br>mW/°C |

| Maximum Temperature for Soldering                                                                                                                                                                                                                             | T <sub>L</sub> | 260        | °C             |

Preferred devices are ON Semiconductor recommended choices for future use and best overall value.

## **ELECTRICAL CHARACTERISTICS** (T<sub>C</sub> = 25°C unless otherwise noted)

| Characteristic                                                                                                                                                                    | Symbol                | Min              | Тур            | Max                  | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------|----------------|----------------------|------|

| OFF CHARACTERISTICS                                                                                                                                                               | ,                     |                  |                | l                    |      |

| Collector–Emitter Sustaining Voltage (I <sub>C</sub> = 10 mAdc, I <sub>B</sub> = 0 Adc)                                                                                           | V <sub>CEO(sus)</sub> | 30               | _              | _                    | Vdc  |

| Emitter–Base Voltage ( $I_E = 50 \mu Adc$ , $I_C = 0 Adc$ )                                                                                                                       | V <sub>EBO</sub>      | 6.0              | _              | _                    | Vdc  |

| Collector Cutoff Current (V <sub>CE</sub> = 25 Vdc, R <sub>BE</sub> = 200 $\Omega$ ) (V <sub>CE</sub> = 25 Vdc, R <sub>BE</sub> = 200 $\Omega$ , T <sub>J</sub> = 125°C)          | I <sub>CER</sub>      | _                |                | 20<br>200            | μAdc |

| Emitter Cutoff Current<br>(V <sub>BE</sub> = 5.0 Vdc)                                                                                                                             | I <sub>EBO</sub>      | _                | _              | 10                   | μAdc |

| ON CHARACTERISTICS <sup>(1)</sup>                                                                                                                                                 |                       |                  |                |                      |      |

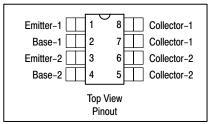

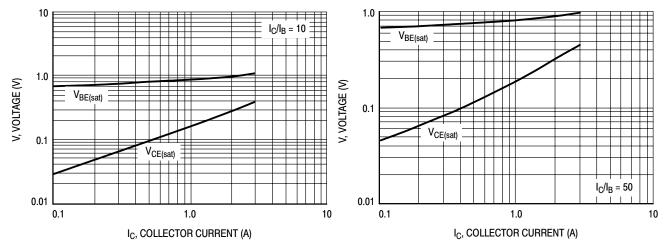

| Collector–Emitter Saturation Voltage ( $I_C = 0.8$ Adc, $I_B = 20$ mAdc) ( $I_C = 1.2$ Adc, $I_B = 20$ mAdc) ( $I_C = 3.0$ Adc, $I_B = 0.3$ Adc)                                  | V <sub>CE(sat)</sub>  | _<br>_<br>_      | 0.15<br>—<br>— | 0.21<br>0.24<br>0.55 | Vdc  |

| Base–Emitter Saturation Voltage ( $I_C = 3.0$ Adc, $I_B = 0.3$ Adc)                                                                                                               | V <sub>BE(sat)</sub>  | _                | _              | 1.25                 | Vdc  |

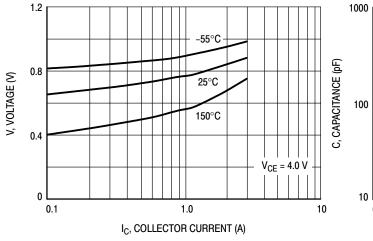

| Base–Emitter On Voltage<br>(I <sub>C</sub> = 1.2 Adc, V <sub>CE</sub> = 4.0 Vdc)                                                                                                  | V <sub>BE(on)</sub>   | _                | _              | 1.10                 | Vdc  |

| DC Current Gain ( $I_C = 0.8 \text{ Adc}, V_{CE} = 1.0 \text{ Vdc}$ ) ( $I_C = 1.2 \text{ Adc}, V_{CE} = 1.0 \text{ Vdc}$ ) ( $I_C = 3.0 \text{ Adc}, V_{CE} = 1.0 \text{ Vdc}$ ) | h <sub>FE</sub>       | 125<br>110<br>90 | 260<br>—<br>—  |                      | _    |

| DYNAMIC CHARACTERISTICS                                                                                                                                                           |                       |                  |                |                      |      |

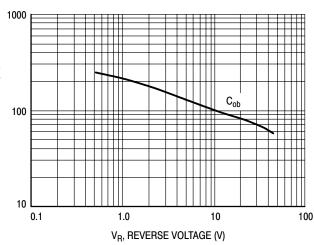

| Output Capacitance<br>(V <sub>CB</sub> = 10 Vdc, I <sub>E</sub> = 0 Adc, f = 1.0 MHz)                                                                                             | C <sub>ob</sub>       | _                | 100            | 150                  | pF   |

| Input Capacitance<br>(V <sub>EB</sub> = 8.0 Vdc)                                                                                                                                  | C <sub>ib</sub>       | _                | 135            | _                    | pF   |

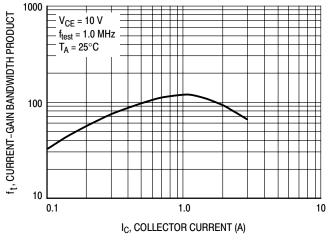

| Current–Gain — Bandwidth Product <sup>(2)</sup><br>(I <sub>C</sub> = 500 mA, V <sub>CE</sub> = 10 V, F <sub>test</sub> = 1.0 MHz)                                                 | f⊤                    | _                | 110            | _                    | MHz  |

<sup>(1)</sup> Pulse Test: Pulse Width  $\leq$  300  $\mu$ s, Duty Cycle  $\leq$  2%. (2)  $f_T = |h_{FE}| \bullet f_{test}$

Figure 1. Collector Saturation Region

Figure 2. Collector Saturation Region

Figure 3. DC Current Gain

Figure 4. DC Current Gain

Figure 5. "On" Voltages

Figure 6. "On" Voltages

Figure 7. V<sub>BE(on)</sub> Voltage

Figure 8. Output Capacitance

Figure 9. Current-Gain Bandwidth Product

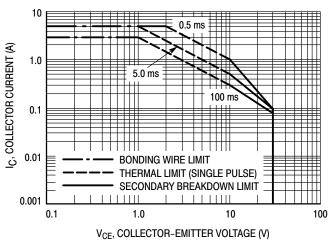

Figure 10. Active Region Safe Operating Area

Figure 11. Power Derating

There are two limitations on the power handling ability of a transistor: average junction temperature and secondary breakdown. Safe operating area curves indicate  $I_C - V_{CE}$  limits of the transistor that must be observed for reliable operation; i.e., the transistor must not be subjected to greater dissipation than the curves indicate.

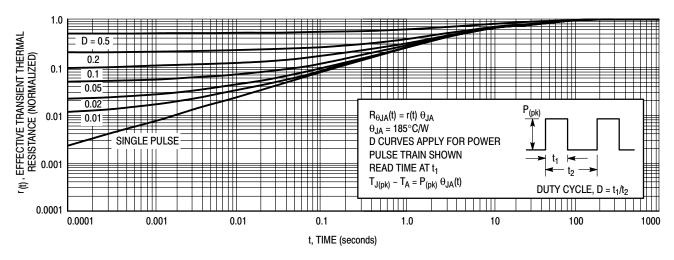

The data of Figure 10 is based on  $T_{J(pk)} = 150^{\circ}C$ ;  $T_C$  is variable depending on conditions. Secondary breakdown pulse limits are valid for duty cycles to 10% provided  $T_{J(pk)} \le 150^{\circ}C$ .  $T_{J(pk)}$  may be calculated from the data in Figure 12. At high case temperatures, thermal limitations will reduce the power that can be handled to values less than the limitations imposed by secondary breakdown.

Figure 12. Thermal Response

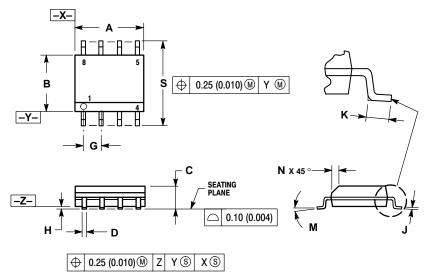

#### **PACKAGE DIMENSIONS**

# SOIC-8 NB CASE 751-07 **ISSUE W**

#### NOTES:

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSION A AND B DO NOT INCLUDE MOLD PROTRUSION.

4. MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE.

5. DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

|     | MILLIMETERS |       | INCHES |       |

|-----|-------------|-------|--------|-------|

| DIM | MIN         | MAX   | MIN    | MAX   |

| Α   | 4.80        | 5.00  | 0.189  | 0.197 |

| В   | 3.80        | 4.00  | 0.150  | 0.157 |

| С   | 1.35        | 1.75  | 0.053  | 0.069 |

| D   | 0.33        | 0.51  | 0.013  | 0.020 |

| G   | 1.27        | 7 BSC | 0.05   | 0 BSC |

| Н   | 0.10        | 0.25  | 0.004  | 0.010 |

| J   | 0.19        | 0.25  | 0.007  | 0.010 |

| K   | 0.40        | 1.27  | 0.016  | 0.050 |

| M   | 0 °         | 8 °   | 0 °    | 8 °   |

| N   | 0.25        | 0.50  | 0.010  | 0.020 |

| S   | 5.80        | 6.20  | 0.228  | 0.244 |

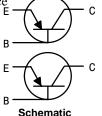

- STYLE 16:

PIN 1. EMITTER, DIE #1

2. BASE, DIE #1

- EMITTER, DIE #2

- BASE, DIE #2 COLLECTOR, DIE #2

- COLLECTOR, DIE #2 COLLECTOR, DIE #1 COLLECTOR, DIE #1

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer.

#### **PUBLICATION ORDERING INFORMATION**

#### NORTH AMERICA Literature Fulfillment:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA

**Phone**: 303–675–2175 or 800–344–3860 Toll Free USA/Canada **Fax**: 303–675–2176 or 800–344–3867 Toll Free USA/Canada

Email: ONlit@hibbertco.com

Fax Response Line: 303-675-2167 or 800-344-3810 Toll Free USA/Canada

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

**EUROPE:** LDC for ON Semiconductor – European Support

German Phone: (+1) 303–308–7140 (Mon–Fri 2:30pm to 7:00pm CET)

Email: ONlit-german@hibbertco.com

French Phone: (+1) 303–308–7141 (Mon–Fri 2:00pm to 7:00pm CET)

Email: ONlit-french@hibbertco.com

English Phone: (+1) 303–308–7142 (Mon–Fri 12:00pm to 5:00pm GMT)

Email: ONlit@hibbertco.com

EUROPEAN TOLL-FREE ACCESS\*: 00-800-4422-3781

\*Available from Germany, France, Italy, UK, Ireland

#### CENTRAL/SOUTH AMERICA:

Spanish Phone: 303-308-7143 (Mon-Fri 8:00am to 5:00pm MST)

Email: ONlit-spanish@hibbertco.com

Toll-Free from Mexico: Dial 01-800-288-2872 for Access -

then Dial 866-297-9322

ASIA/PACIFIC: LDC for ON Semiconductor – Asia Support

Phone: 1-303-675-2121 (Tue-Fri 9:00am to 1:00pm, Hong Kong Time)

Toll Free from Hong Kong & Singapore:

001-800-4422-3781 Email: ONlit-asia@hibbertco.com

JAPAN: ON Semiconductor, Japan Customer Focus Center 4–32–1 Nishi–Gotanda, Shinagawa–ku, Tokyo, Japan 141–0031

**Phone**: 81–3–5740–2700 **Email**: r14525@onsemi.com

ON Semiconductor Website: http://onsemi.com

For additional information, please contact your local

Sales Representative.