# **DRAM Accelerator Module**

### **Features**

- 4-megabyte to 1-gigabyte control capability

- 32- or 64-bit bus interface (M7232 only)

- 32- or 64-bit EDC versions

- 1-bit correct; 2-bit detect

- Multiplexed or non-multiplexed bus

- i486, Pentium<sup>®</sup>, i860, 68040, 88110, Power PC, SPARC, and MIPS compatible

- Synchronous bus interface

- 25-, 33-, and 40-MHz versions

- Error-logging facilities

- Cache line fill burst support; posted writes

- Cache line write-back support; write FIFO

- High performance

- 25-ns writes

- --- 175-, 25-, 50-, 25-ns burst read/80-ns DRAMs

- Automatic refresh with scrubbing

- Multiprocessor compatible

- Inhibited reads and writes

- Reflective reads

- Reads for ownership

- · Bus parity generation and checking

- Very small size

# **Functional Description**

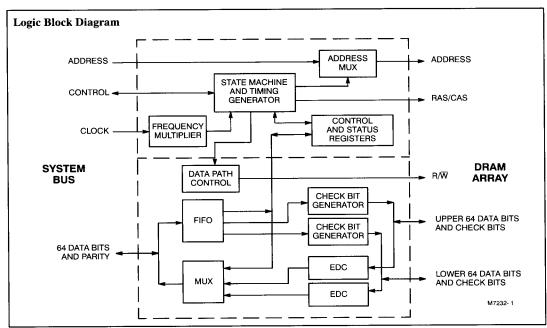

The CYM7232 and the CYM7264 consist of a full-function DRAM controller and a pipelined/FIFO data multiplexer/demultiplexer with error correction for cachebased, uniprocessor, and multiprocessor systems memory control. The CYM7232 performs 32-bit Error Detection and Correction (EDC) while CYM7264 performs 64-bit EDC. They both connect to the system bus through a 64-bit-wide data bus, and a 36-bit wide address bus. The CYM7232 also supports 32-bit system buses. The bus transfer control signals support i486, Pentium, i860, 68040, 88110, SPARC MBus, MIPS R4000, or other interfaces. The controller module interfaces to the DRAM array through a

16-byte-wide data bus plus check bits, a 12-bit row/column address bus, four RAS outputs, four CAS outputs, and four read/write control lines.

During write operations, data passes from the system bus through a FIFO array that acts as an incoming queue. Writes occur at the system bus speed until the FIFO is full (sixteen 64-bit words). The FIFO supports cache-line copy-back and fill operations, reducing system bus traffic to a minimum. The module supports posted writes, by suspending the actual write to DRAM until the cache-line read is completed during cache-line write-back. This speeds cache-line fill operations. The module pipelines a 16-byte-wide DRAM access into the data path for EDC, and multiplexes the data to the system bus during reads. This supports high-speed burst line fills with error corrected data. Reads and writes may be inhibited for multiprocessor support. Inhibited reads may be turned into reflective reads, and inhibited writes may be turned into readsfor-ownership.

Pentium is a trademark of Intel Corporation.

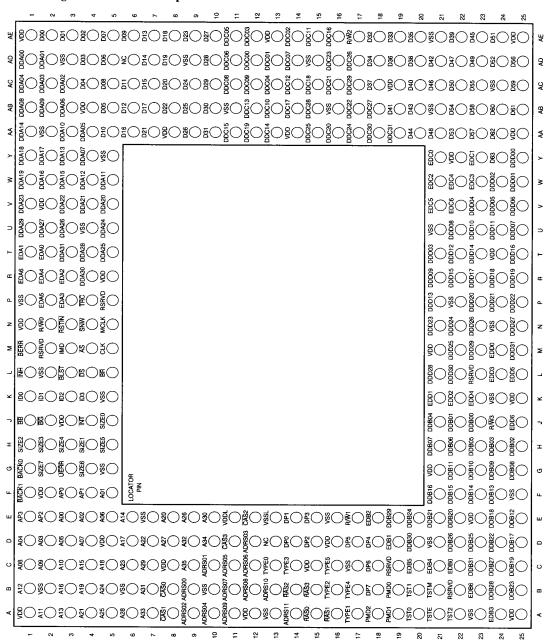

# Pin Configuration: CYM7232 Top View

# Pin Configuration: CYM7264 Top View

|          | 1                                                     | ı          |

|----------|-------------------------------------------------------|------------|

|          |                                                       | AE         |

| Ą        |                                                       | ΑD         |

| Ϋ́       |                                                       | AC         |

| ΑB       |                                                       | AB         |

| A        |                                                       | \$         |

| >        |                                                       | >          |

| W        |                                                       | 3          |

| >        |                                                       | >          |

| >        |                                                       | 5          |

| <b>-</b> |                                                       | -          |

| Œ        |                                                       | Œ          |

|          |                                                       | a.         |

| z        |                                                       | z          |

|          |                                                       | Σ          |

|          |                                                       |            |

| ¥        |                                                       | <b>x</b> . |

| ~        |                                                       | 2          |

| I        |                                                       | I          |

| g        |                                                       | 9          |

| L.       |                                                       | ш          |

| ш        |                                                       | ш          |

|          |                                                       |            |

| O        |                                                       | O          |

| 8        |                                                       | <u>_</u>   |

|          |                                                       | 1          |

|          | - 9 8 4 9 9 7 8 9 5 1 5 5 5 5 5 5 8 5 8 2 8 2 8 2 8 2 | -          |

# Overview

Cypress Semiconductor offers two DRAM control subsystem module types: the CYM7232, which supports 32-bit EDC, and the CYM7264, which supports 64-bit EDC. The modules are very similar in functionality and architecture, with minor differences to support the EDC variation. Both modules support four blocks of DRAMs for a total capacity of 1 gigabyte of data storage. The CYM7232 divides the memory blocks into four 32-bit-wide data banks, each with 7 check bits, which provide a 156-bit-wide data path to the DRAM array. The CYM7264 divides the memory blocks into two banks of 64-bit-wide data, each with 8 check bits, for a total DRAM interface of 144 bits.

The CYM7232 can be programmed and wired for use with 32-bit system buses, and the operation is very similar to use in 64-bit systems.

The modules support multiplexed address/data buses as well as separate address and data buses for applications such as the SPARC MBus architecture. This datasheet includes a detailed MBus Operation section.

The modules are offered in high-speed and standard speed versions. The high-speed version may be programmed for 100 MHz DRAM timing resolution, while the standard speed version may be programmed for 80-MHz DRAM timing resolution.

### System Bus Modes

The modules include selectable bus modes that support a variety of processors and cache controllers. Programmability includes the byte-ordering protocol (big endian/little endian); burst length is configurable for SPARC MBus, 88K or 68040 SIZE, or i86 and i860 byte enables. A data strobe initiates the bus handshake for systems where the bus master must indicate when it can supply or accept data; bus acknowledge signals are programmable to be early (active in the bus cycle preceding the data) or normal (active in the cycle in which the data transfer takes place). The early modes support the Motorola 88K family of microprocessors. Other programmable options allow optimization of the acknowledge timing to the system requirements.

### General Description of Bus Transactions

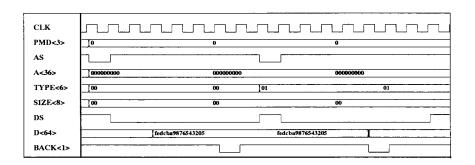

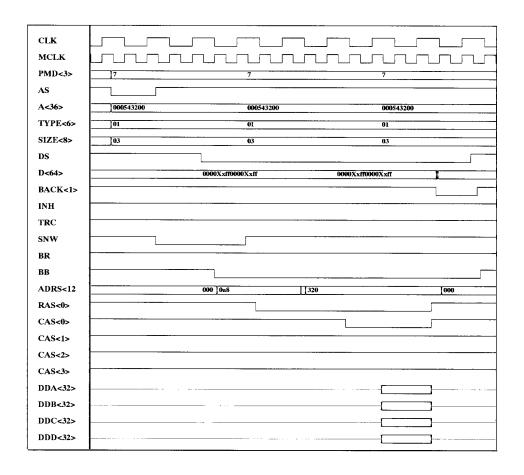

The fully synchronous bus interface uses the rising edge of the system bus clock. Every system transaction has an address/control phase and one or more data phases.

### Address Phase

During the address/control phase, which is specified by the assertion of the Address Strobe for one bus clock cycle, the address and nature (size and type) of the transaction is supplied over the system bus to the module.

# Data Phase

During the data phase, which is specified by the assertion of the data strobe for one or more bus clock cycles, one or more data words is transferred over the system bus.

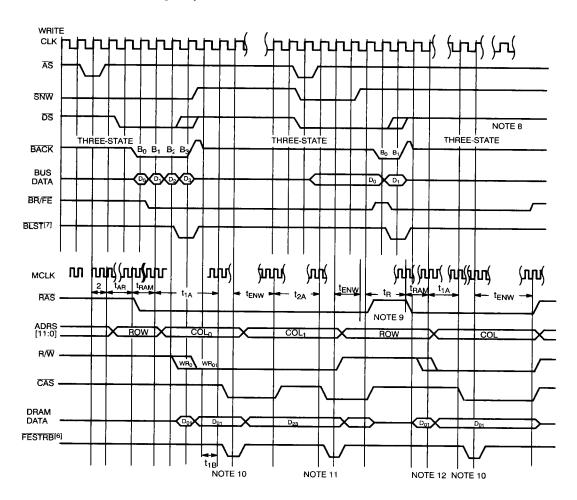

### Data Write

The module supports four different write modes. Data strobe will be interpreted differently depending on the mode. Data strobe may be permanently asserted, asserted one clock early, or in real-time. Systems using Real-Time Data Strobe mode must monitor the Bus Request/FIFO Empty output and postpone data strobe assertion until the write FIFOs are empty. These systems do not require bus acknowledges since the FIFOs are empty when the data phase begins. The module will not respond with bus acknowledge (real-time data strobe case) or will assert bus ac-

knowledge one cycle before, or during the same cycle, as the data transfer.

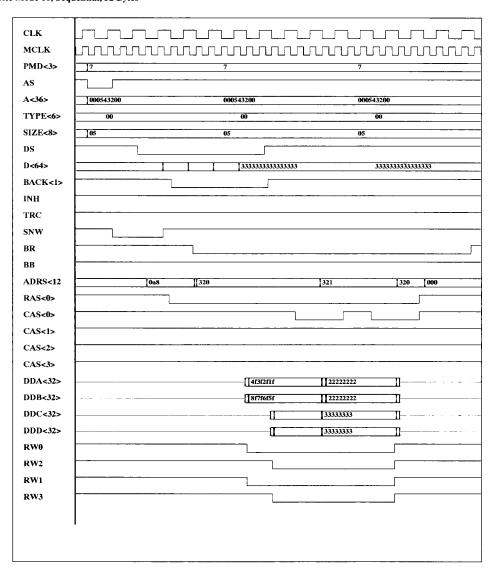

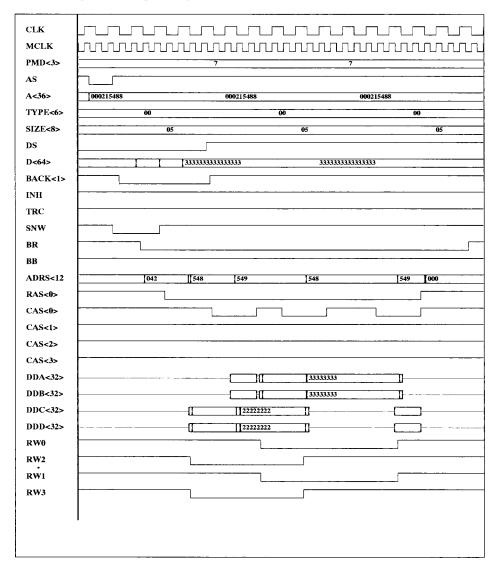

### Write Data Flow

During system bus writes and reflective read operations, two identical sets of FIFOs buffer the incoming data. One set is used during normal write transactions, and the second set is used exclusively during reflective read transactions. In the CYM7232, each set contains four FIFOs that are 32 bits wide by 8 words deep. In the CYM7264, each set contains two FIFOs that are 64 bits wide by 8 words deep. During writes, the module demultiplexes the incoming data into the appropriate FIFO according to the address and burst order. As soon as the required data falls through the FIFOs, a write to DRAM commences. This process continues until completion of the burst. When the inhibit signal and transform cycle inputs are asserted during a read, the module demultiplexes the write data into the appropriate reflective FIFO. These FIFOs operate in an identical fashion to the normal write FIFOs.

During writes to DRAM, the module appends the demultiplexed data with associated error detection and correction check bits. For the 32-bit EDC version, the demultiplexed data word consists of four sets of 32 data bits plus their 7 associated error check bits for a total of 156 bits. For the 64-bit EDC version, the data word consists of two sets of 64 data bits plus their 8 associated error check bits for a total of 144 bits.

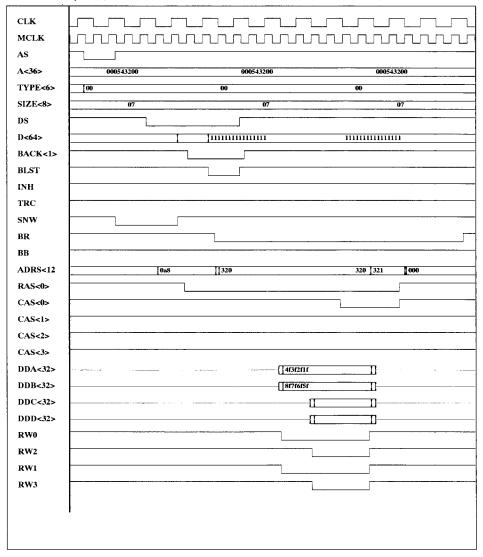

### Data Phase Read

During read operations the module suspends data transfer until two clocks after the assertion of data strobe and the closing of the snoop window, whichever occurs last. The data transfer continues at the system bus speed. In systems where the master does not regulate the data flow, data strobe may be permanently asserted.

The module offers options for both early and real-time bus acknowledge for reads. At fast system bus clocks, wait states may be inserted to delay the bus acknowledge, allowing the data to propagate through the error-detection and correction logic.

### Read Data Flow

The module reads 128 bits of data and the corresponding EDC check bits in parallel from the DRAM. The data then passes simultaneously through parallel error correction circuitry to a multiplexer that selects the corrected or uncorrected data. The module appends parity to the data and routes it to the system bus. The CYM7232 transfers the data in 32-bit packets, and the CYM7264 transfers 64-bit packets, which makes the CYM7264 incompatible with 32-bit system buses.

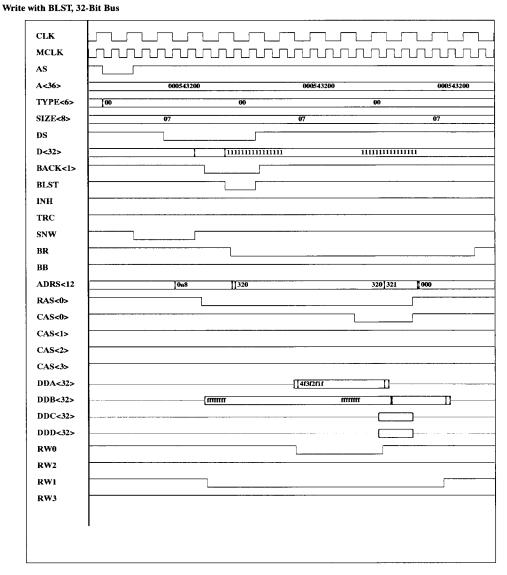

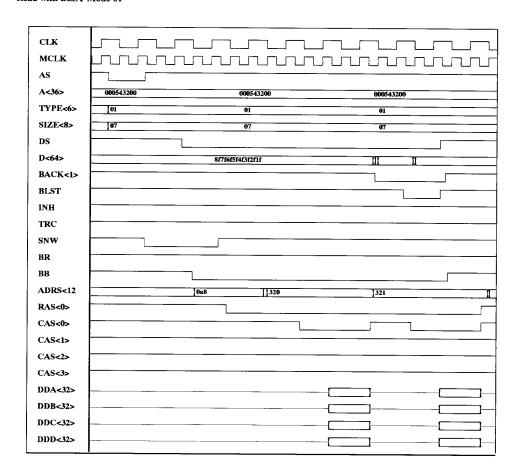

### Burst Last

The module allows any read or write burst transaction to terminate prematurely with the assertion of Burst last.

# Data Alignment

The data path portion of the module contains data buffers and demultiplexers on writes and multiplexers and error correctors on reads. The bus interface is 64 data bits wide and the DRAM interface is 128 data bits wide.

### Bus Alignment

All data flowing between the DRAM controller and the system data bus is assumed to be aligned to the bus width. When a system bus transaction crosses aligned boundaries, the processor or cache controller must split the transaction into multiple operations and issue an address phase for each portion. The misaligned transactions cannot, therefore, be bursts.

# DRAM Alignment

The DRAM controller stores data into memory on 128-bit aligned boundaries. Transactions over the system bus of 16 bytes or less are assumed to be aligned within a 128-bit DRAM page. This implies that a single DRAM transaction will be associated with bus transactions of 16 bytes or less. Burst transactions exceeding 16 bytes may be misaligned to the DRAM storage boundary. Such transactions will involve transfers of 4, 8, or 12 bytes between controller and DRAM during the first cycle of the burst (i.e., not all DRAM banks will be involved in the first data transfer). The DRAM address will wrap around within the burst boundary as more data is transferred. The final data transfer will include the bank(s) omitted during the first cycle of the DRAM transfer. The nature of the misalignment will depend on the defined burst order (i.e., sequential or Intel).

### I/O Operations

The internal command and status registers are accessed through I/O transactions. The ID inputs select between Memory, I/O transactions, or the Indirect Address register. The Indirect Address register points to the desired command and status I/O registers. I/O read and write transactions follow the same bus acknowledge and data strobe protocols as memory operations.

I/O operations may be inhibited prior to the closure of the snoop window.

### Multiprocessor Support

The modules provide complete multiprocessing support. Any operation may be inhibited or aborted, including I/O operations.

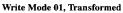

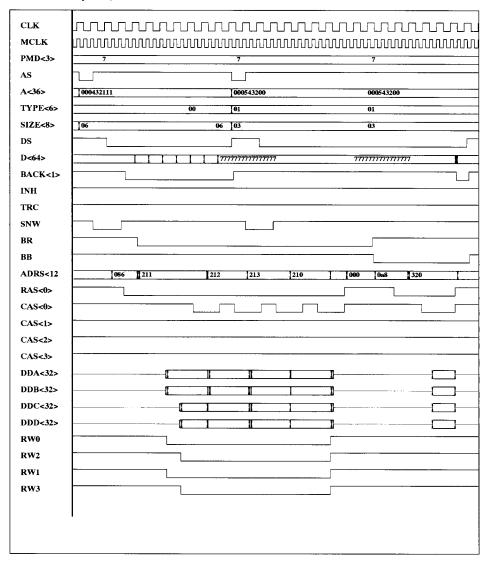

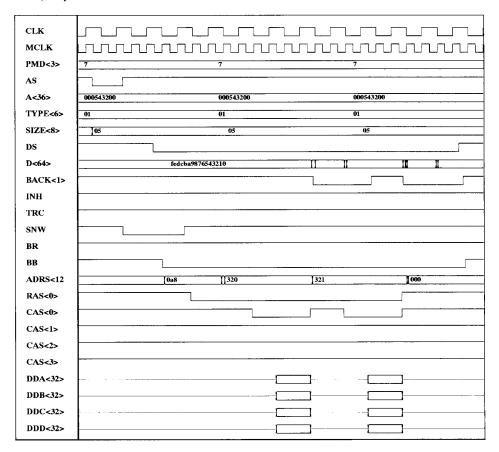

# Reflective Read Operations

A reflective read transaction occurs when a main memory read operation is inhibited and transformed into a write. Such transactions can occur in a multiprocessor environment when a processor's cache controller requests a line from main memory. The particular main memory line may be stale with the only valid copy contained in another processor's snooping cache. The cache line owner will inhibit the main memory, and then fetch and supply the data to the requesting processor's cache. Simultaneously, the data is copied into FIFO buffers inside the controller module for later transfer to DRAM. The memory read operation is thereby transformed into a memory write operation.

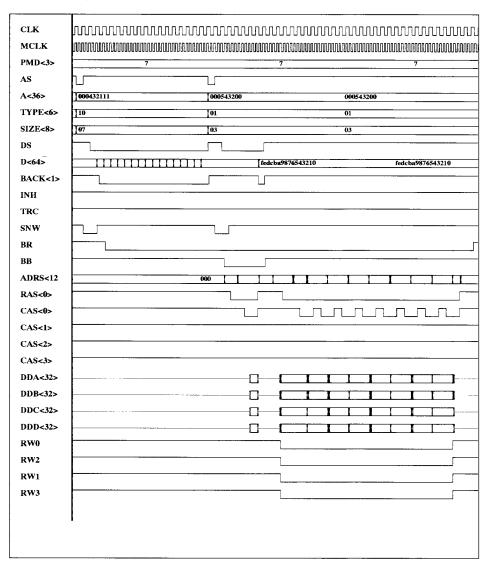

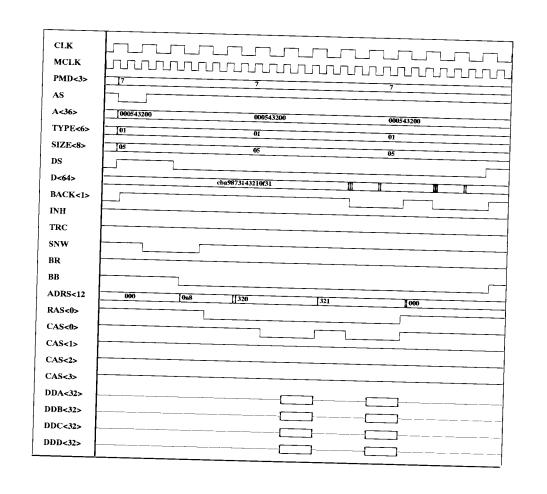

# Reads For Ownership

The address space of a copy-back cache-based system will typically be partitioned into distinct regions. Some of these regions will be cachable and others (typically peripheral I/O registers and some small portion of memory) will not be cachable. Whenever a processor begins a write operation to a particular address location, the cachability status of that location must be determined. Should the write operation result in a miss within a cachable region of main memory, a line would be fetched. The DRAM controller module permits a write to begin into DRAM before the cachability status is completely determined. When the status of the address in question is resolved the operation can be inhibited and transformed into a read of a cache line.

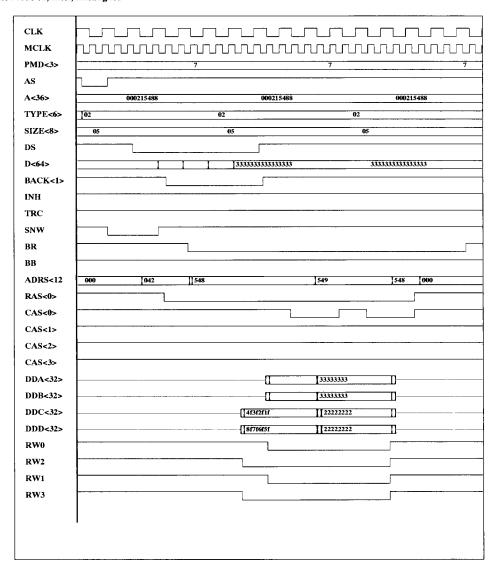

# **Write Operations**

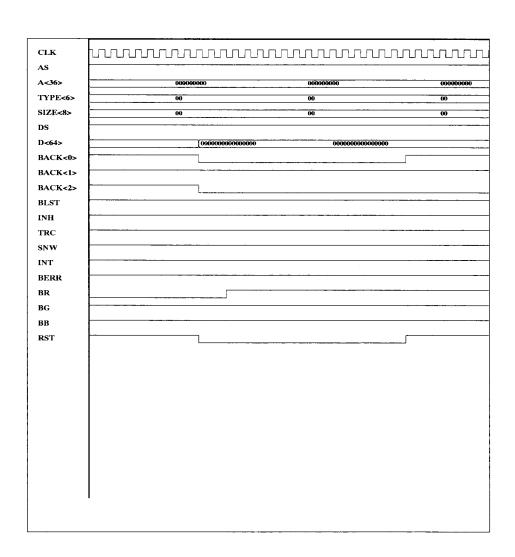

# **Address Phase**

A write operation is initiated when Address Strobe  $(\overline{AS})$  is asserted and an address and all appropriate control signals meet the set-up conditions to the rising edge of CLK. This is the address phase of the transaction. The control signals that accompany the address during the address phase include SIZE and TYPE inputs. The address and certain control information is strobed

into the Address-Control register in the cycle in which  $\overline{AS}$  is asserted. If address parity check is enabled, the lowest 32 bits of the system bus address is checked for byte parity. The control signals are not parity checked. If parity is error-free, the address and other control information is used to initiate the requested transaction. If address parity is enabled and an address bus parity error is detected, the Address Bus Parity Error (ABE) bit is set in the status register, the Bus Error (BERR) output is asserted, and the write operation is aborted. This action takes place whether or not the address is decoded to address the DRAM controller.

### Data Phase

Data placed on the bus is clocked into the Write Data FIFO on a rising CLK edge. The system will use  $\overline{DS}$  (Data Strobe) to signal the onset of a write transaction. Once  $\overline{DS}$  is asserted, it must remain asserted throughout the bus operation. The system must continue to assert the write data until it is acknowledged (except in the no acknowledge mode). If the SIZE[7:0] control indicated a non-burst transfer, the write transaction is terminated upon the acceptance of the data. When SIZE[7:0] control inputs indicate a burst transaction, the module will continue the write transaction by accepting data until the transaction is terminated. The transaction is terminated by one or more of the following events: the bus responds by asserting Burst Last ( $\overline{BLST}$ ) or the burst length indicated by SIZE or the programmed default burst length is reached.

During the data phase, data is checked for valid parity (if data parity checking is enabled). Parity is checked over individual bytes. Should a data bus parity error occur, data is clocked into the Write Data FIFO (but is later discarded) and the Bus Error output (BERR) is asserted. After parity check, data flows into the Write Data FIFO and is subsequently written into the DRAM memory. When a parity error occurs, the entire word that would have been written to DRAM with the byte(s) incurring the parity error is discarded. The discarded word consists of bits over which the EDC algorithm is applied. It is therefore 32 (CYM7232) or 64 (CYM7264) bits in length. Recovery schemes must consequently rewrite more than the byte(s) incurring the parity error. Subsequent data transferred to the FIFO is written to DRAM even though a previous data word may have incurred a parity error.

Burst operations are supported up to the full FIFO depth. The FIFO permits these operations to take place at the full bus speed. If the Write Data FIFO contains data from a previous write (FIFO not Empty), the address and control information is accepted into the controller's internal Write Address register, but the data phase cannot begin until the previous write is completed to DRAM. BACK remains three-state until the FIFO is available for the new write. The system must use the Bus Request/FIFO Empty (BR/FE) output to determine if the controller is capable of accepting data when using the No Bus Acknowledge Mode.

# Posted Writes

Posted writes support fast cache line fills. A posted write is accomplished by issuing the Posted Write encoding in the TYPE input during the address phase. The module accepts the write data as usual and holds the data in the Write Data FIFO. After the next read transaction is completed, the actual write of the data to DRAM is accomplished. The posted write operation allows a cache controller to purge a cache line and fetch the new cache line as rapidly as possible by postponing the DRAM access for the write. Posted writes must be followed by a read operation.

When the address of the posted write is in the same burst address region as that of the following read, a memory incoherency can result. To resolve the incoherency, the module compares the

# Posted Writes (continued)

address of the posted write with that of the read for address bits A7 and higher. (A[6:0] span the longest possible burst). If the compare shows equal, the posted write is performed before the read. Posted writes may not be inhibited.

# **Byte Writes**

Single byte and partial word transfers are supported by a readmodify-write DRAM memory cycle. The old word is accessed and combined with the new data under control of the address and SIZE inputs. A new set of EDC check bits is generated and the modified data and new check bits are written back to the memory to complete the read-modify-write cycle. In the 32-bit EDC version, a read-modify-write cycle occurs for all writes less than 32 bits. In the 64-bit EDC version, a read-modify-write cycle occurs for all writes less than 64 bits.

# **Inhibited Write Operations**

A write operation may be inhibited at any time prior to the end of the snoop window by asserting Inhibit, INFH. When Inhibit is recognized, the module write operation is aborted and the module plays no further role in the bus transaction. Note that the system may perform data writes to the controller prior to the close of the snoop window and prior to the assertion of Inhibit. In these cases, the data will not be written to the DRAM and the write FIFO will be cleared upon recognition of the Inhibit. When data transfers occur prior to a write inhibit there must be at least two bus clock cycles between the close of the snoop window and the address strobe of the following transaction.

An inhibited write may also be converted into a read for ownership. This option is enabled by asserting the TRC input (Transform Cycle) along with the Inhibit. When Inhibit is recognized, the module write operation is transformed into a read operation. After Inhibit is recognized and before the read is completed, any data written to the Write FIFO is purged.

# Write Snoop Window

The snoop window is determined by an internal counter that is programmable by the system or by an external input, SNW. The snoop window source is selectable by driving UERR as an input when RSTIN is asserted. Refer to the signal descriptions for programming details. The write into the DRAM is postponed until the snoop window closes. This prevents data from an inhibited write operation from corrupting main memory data. Long snoop window intervals may cause performance degradation.

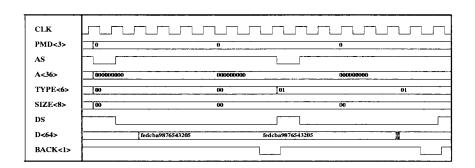

# **Read Operations**

# **Address Phase**

A read operation begins with the address phase similar to write operations.

# Data Phase

The DRAM interface accesses 128 data bits from the memory simultaneously with their related check bits. The addressed 64-bit word (or the first word of the burst) is pipelined to the system bus and simultaneously to the error check logic. The data is accessed from DRAM but the transfer over the system bus is suspended until two clock cycles after the snoop window closes or two clock cycles after Data Strobe is asserted, whichever occurs last. The appropriate Bus Acknowledge is asserted as dictated by the selected modes. Byte-wide parity is appended to the data as it exits the module onto the system bus.

During bursts, data is pipelined consecutively over the bus until the transaction is terminated. Transactions may be terminated by Burst Last (BLST) or when the burst length indicated by SIZE or the default burst length is reached.

The error detection logic generates check bits that are compared with the check bits from the memory. The exclusive NOR of the generated check bits and the check bits from the memory form the syndrome bits. When the two sets of check bits are identical, no errors have occurred in the data. Should the comparison show a difference, the Error Detector decodes the syndrome bits, identifying the type of error (single-bit correctable, double-bit detectable, or uncorrectable multi-bit error). The Error Position Decoder creates a 32-bit word that is used to correct the defective bit for single-bit errors.

Should the data contain an error, the appropriate status bits are set in the Interrupt Status register. An interrupt is generated when enabled. Whenever an error occurs, the syndrome bits are saved in the Syndrome FIFO allowing the syndrome to be read by the system. This output can be used to determine which bit was defective. The corrected data is not written back into the memory array but is corrected later as part of the refresh/scrubbing operations.

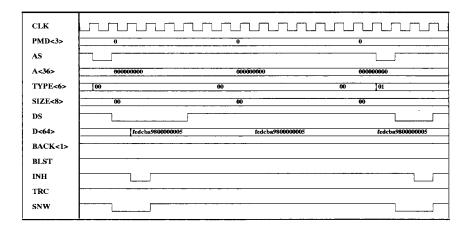

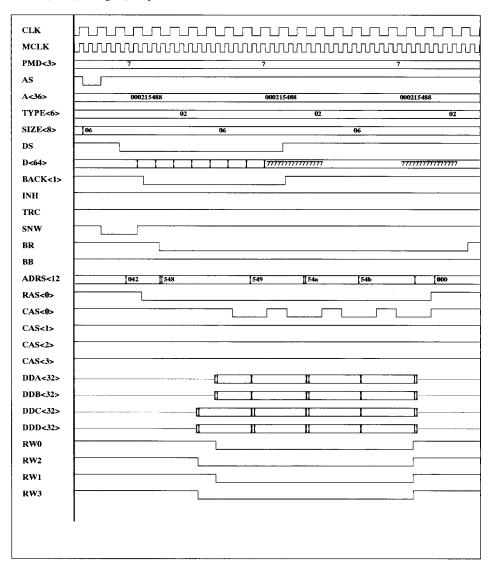

# **Inhibited Read Operations**

Read operations may be inhibited. This action is required in multiprocessor systems when a main memory read must be terminated to allow a snooping cache to supply data to the requesting cache. A read operation may be inhibited prior to the close of the snoop window by asserting INH. When an Inhibit is recognized, the module read operation is aborted and the module plays no further role in the bus transaction.

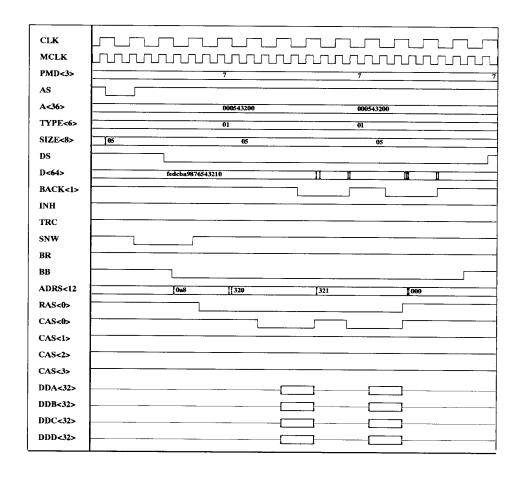

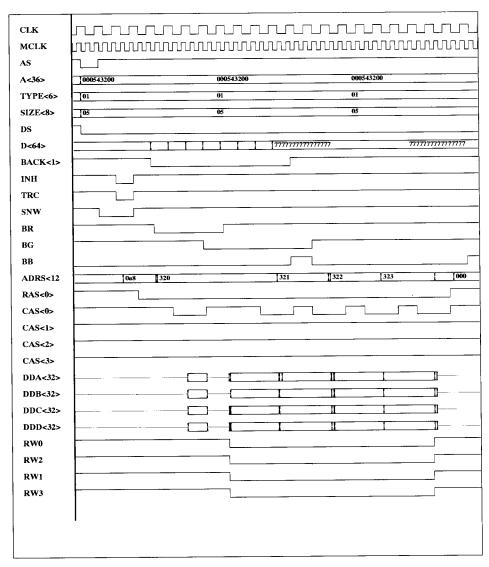

### Reflective Reads

Inhibited reads may also be reflective. This option is enabled by asserting Transform Cycle (TRC) simultaneously with INH. When a transformed Inhibit is recognized, the module read operation is changed into a write operation. INH and TRC must be asserted within the snoop window. After Inhibit is recognized, BACK and the Data Bus become inputs. BACK are now used as a synchronous write enable to strobe the bus data into the Reflective Read FIFO. As the slave in the transaction, the snooping cache must supply BACK. The timing of the BACK input to strobe data into the reflective FIFO is either early or real-time following the Bus Acknowledge mode selection for reads.

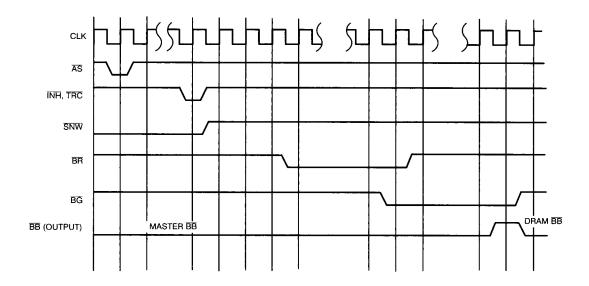

The Reflective FIFO is an image of the normal Write Data FIFO and is devoted exclusively to reflective read operations. Upon inhibit, the data bus is kept three-stated, allowing the snooping cache to drive the bus with the requested data. The module accepts the data into the Reflective Read FIFO at the full bus speed. A mechanism is required to prevent overrun of the reflective FIFO during consecutive transformed reads. As soon as the Inhibit is recognized, the module asserts Bus Request (BR) in order to become the bus master in the next address phase. The system responds with Bus Grant (BG). When the bus is acquired, the module asserts Bus Busy (BB) until the reflective FIFO data is written to the DRAM and the module is capable of accepting another read. Since BR provides status of the availability of the reflective FIFO, the output may be used to delay the address phase of the next operation.

# Read Snoop Window

As with writes, the snoop window may originate from either of two sources, one internal and the other external. On reads, the assertion of the bus acknowledge to transfer the data to the system is postponed until at least two clocks after the snoop window closes.

# I/O Operations

Access to the internal Command and Status registers is controlled by the ID input. The details of the ID control are given in the Pin Description section. When the ID code for memory is input, all transactions access DRAM. The ID input can also point to the Indirect Address register. When the ID input specifies an I/O register, the Command and Status register accessed is the one pointed to by the Indirect Address register. The register address, position on the system bus, and the bit definition for each of the Command and Status registers is given in the Internal Registers section.

I/O register access follows the same Data Strobe and Bus Acknowledge modes as invoked for memory transactions with a few exceptions. In the Real-Time Data Strobe mode for writes, the BR/FE output plays no role and the transaction is acknowledged with the controller asserting BACK. In all writes, system bus data must be valid at least one clock cycle before it is accepted. The controller delays BACK to meet this criterion. In all reads, data is always transferred in the second clock cycle after the snoop window closes or Data Strobe is asserted, whichever occurs last.

I/O operations may be inhibited. The duration of the I/O snoop window may be set externally or internally as in reads.

# Write Bus Acknowledge and Data Strobe Modes

There are four modes of bus handshake: Early Data Strobe/Early Bus Acknowledge, Real-Time Data Strobe, Early Data Strobe/Real-Time Bus Acknowledge, and MBus. These modes are invoked by driving the BACK and UERR pins during Reset with a specific pattern. *Table 1* is a summary of the modes and their operation.

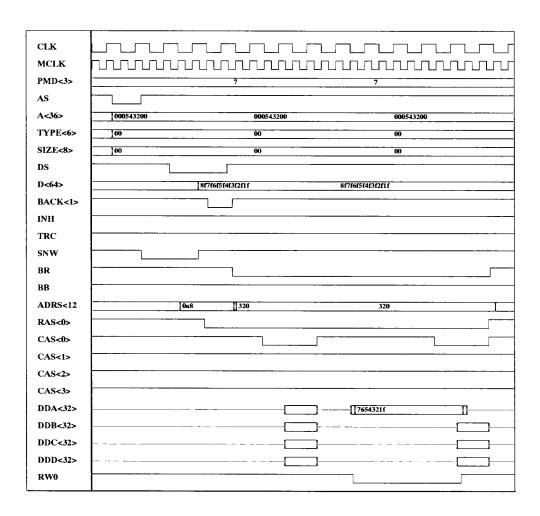

### Early Data Strobe / Early Bus Acknowledge Mode

Data Strobe may be asserted at any time during or after the address phase. In  $Table\ 1$ , the cycle in which Data Strobe is asserted is designated cycle N. Data Strobe, once asserted, must remain asserted throughout the transaction. The FIFO may not be empty when the system asserts Data Strobe. If the FIFO goes empty in cycle N + k, the controller will assert Bus Acknowledge (BACK) in the cycle following the one in which the FIFO goes empty (N + k + 1). The controller accepts the write data in the cycle following the one in which it asserted Bus Acknowledge (cycle N + k + 2). If the FIFO is empty when the Data Strobe is asserted then k = 0. The controller would then assert Bus Acknowledge in the cycle following the one in which Data Strobe was asserted (cycle N + 1). Data is accepted in the following cycle (N + 2). If the transfer is a burst, Bus Acknowledge continues to be asserted until one cycle before the last data transfer.

# Real-Time Data Strobe Mode

Writes are performed by programming the  $\overline{BR/FE}$  output to include the status of the write data FIFO. The system may begin the write transaction with the address phase, but may not assert Data Strobe until the FIFO is known to be empty. In  $Table\ 1$ , the controller asserts  $\overline{BR/FE}$  in cycle N. The system responds with Data Strobe in cycle N + k (k greater than or equal to 1) and the controller accepts the data in the same cycle. If the transaction is a burst, data is accepted each clock cycle thereafter until the burst is terminated. Data Strobe, once asserted, must remain asserted throughout the transaction.

### Early Data Strobe/Real-Time Bus Acknowledge Mode

Data is accepted one clock cycle after Data Strobe is asserted in this mode. Bus Acknowledge is asserted in the same cycle in which the data is accepted (real-time Bus Acknowledge). Refer-

ring to Table 1, the system asserts Data Strobe in cycle N. The FIFO goes empty in cycle N + k. If the FIFO is already empty, k is 0. The controller asserts Bus Acknowledge and accepts the data in the next cycle (N + k + 1).

Table 1. Write Bus Acknowledge and Data Strobe Modes

| Mode                        | Write Action                                | Write Cycle         |

|-----------------------------|---------------------------------------------|---------------------|

| Early DS<br>Early BACK      | System asserts DS                           | N                   |

|                             | Cntrlr FIFO goes empty                      | $N+k$ , $(k \ge 0)$ |

|                             | Cntrlr asserts BACK                         | N+k+1               |

|                             | Cntrlr accepts DATA                         | N+k+2               |

| Real-Time DS,<br>No BACK    | Cntrlr asserts BR/FE                        | N                   |

|                             | Systems asserts DS,<br>Cntrlr accepts DATA  | $N+k (k \ge 1)$     |

| Early DS,<br>Real-Time BACK | System asserts DS                           | N                   |

|                             | Cntrlr FIFO goes empty                      | $N+k (k \ge 0)$     |

|                             | Cntrlr asserts BACK,<br>Cntrlr accepts DATA | N+k+1               |

| MBus,<br>DS Gnded           | System asserts AS                           | N                   |

|                             | Cntrlr FIFO goes empty                      | $N+k (k \ge 0)$     |

|                             | Cntrlr asserts BACK<br>Cntrlr accepts DATA  | N+k+1               |

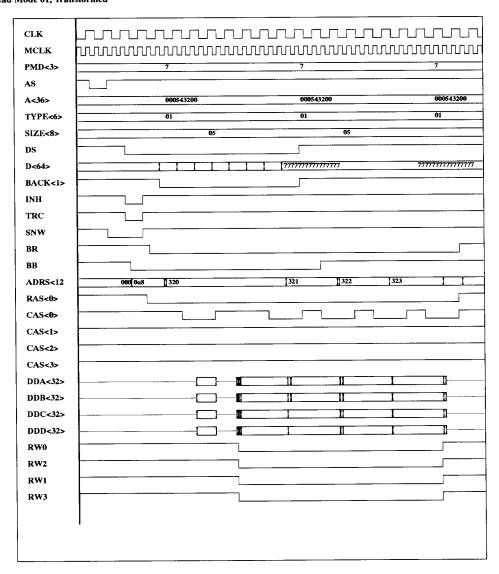

### MBus Mode

Data Strobe is permanently asserted in MBus mode. The controller operates as if it were in Early Data Strobe mode. The system asserts Address Strobe in cycle 0. The FIFO goes empty in cycle k. If the FIFO is already empty, k is 0. The controller asserts Bus Acknowledge and accepts the data in the next cycle (k + 1).

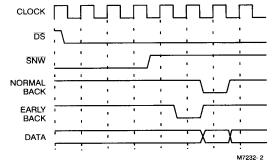

### **Read Operating Modes**

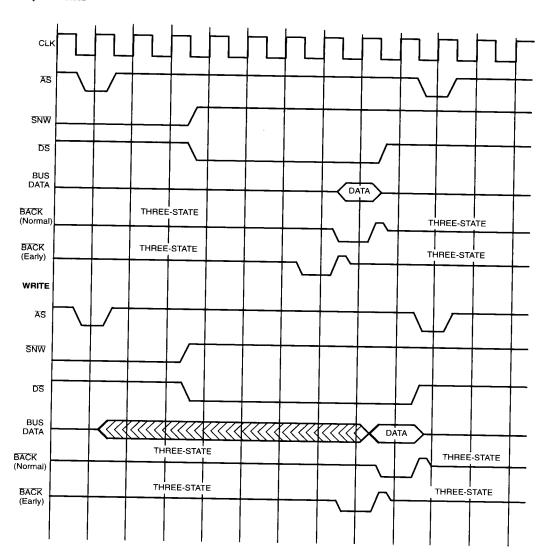

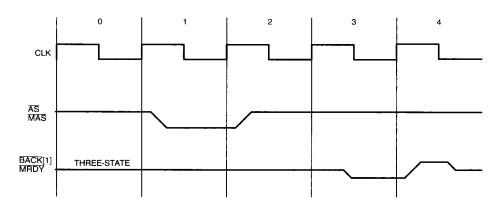

The module offers several programmable options to control the data transfer during memory-read operations. Wait states may be inserted to allow additional propagation delay through the EDC path. Error correction can be disabled for diagnostic purposes. As in write operations, Data Strobe may be used to regulate transfers over the system interface. Finally, Bus Acknowledges may be programmed to occur one clock early or in real time with respect to the corresponding data transfer. The timing of the Bus Acknowledges is shown in Figure 1.

Figure 1. Early and Normal Bus Acknowledge Modes for Reads

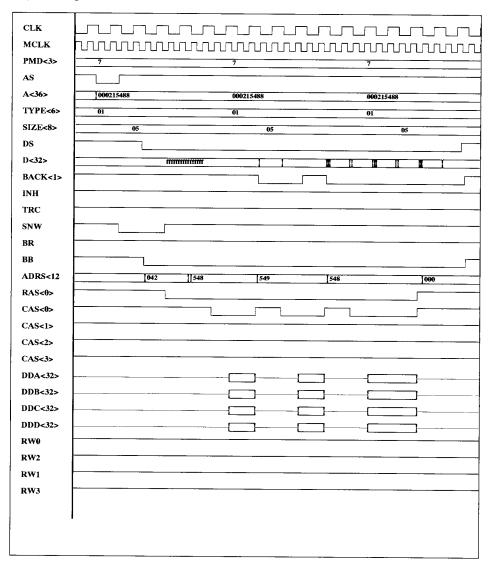

# Read Early BACK Mode

The Read Early BACK data transfer is triggered by the assertion of Data Strobe and closure of the snoop window (whichever occurs last) in cycle N. Data Strobe, once asserted, must remain asserted throughout the transaction. When read data is about to become available,  $\overline{BACK}[1]$  is asserted (cycle N + k). Read data is supplied to the bus in cycle N + k + 1.

### Read Real-Time BACK Mode

The Read Real-Time BACK Mode begins when both Data Strobe is asserted and the snoop window is closed (cycle N). The controller responds with data and the corresponding Bus Acknowledge in cycle N+k+2.

### Wait States

The controller module may be programmed to insert wait states in the data path. This guarantees extra data set-up time when using error correction in system environments with fast bus clocks. The controller delays the Bus Acknowledges accordingly. Wait states may be inserted in either early or real-time Bus Acknowledge systems.

# Acknowledge on Burst Reads

Read burst acknowledges will not generally be contiguous. The assertion of the acknowledge on long bursts (above 16 bytes) will be interrupted as more data is fetched from adjacent 128-bit DRAM pages. During a burst pause, the acknowledge is deasserted and then three-stated one-half clock later.

### **Bus Acknowledges in Transformed Transactions**

When a read is transformed, the operation internal to the controller becomes a write. Bus Acknowledge becomes an input and is used as a strobe to clock the data into the reflective FIFO on each data transfer. The controller will treat the strobe derived from the incoming bus acknowledge as an early strobe when programmed in the early bus acknowledge mode. Otherwise the controller assumes that the data is aligned with the corresponding strobe derived from the incoming bus acknowledge.

When a write is transformed, the operation converts to a read. In this case, the controller behaves according to the invoked read mode. Transformed operations use a preprogrammed default burst length to specify their burst duration.

### **Bus Acknowledge Timing Characteristics**

The Bus Acknowledge control signals are bidirectional and may be driven by the controller or another device on the system bus. Therefore there are times when no device will be driving this signal line. At high bus speeds, pull-ups may not be sufficient to guarantee that the Bus Acknowledge line will revert in a sufficiently short time to the deasserted state after the controller has ceased driving the line. To guarantee the state of the BACK signal lines at the end of a transaction, the controller first drives the outputs HIGH (deasserted) in the first half of the clock cycle in which Bus Acknowledge is to be deasserted and then three-states these outputs in the second half of this clock cycle. To insure that the Bus Acknowledge signal lines remain in the deasserted state when no device is driving them for long periods, pull-ups should be employed. At the beginning of a transaction cycle, Bus Acknowledge remains three-stated until it is to be asserted. Thus in the first acknowledge cycle of a transaction, BACK becomes driven and asserted at the same time. BACK continues to be driven until the end of the transaction cycle and terminates as described above.

### **Burst Last**

Any read or write burst transaction may be terminated prematurely with the assertion of BLST. BLST must be asserted during the clock cycle in which the last piece of data is transferred. Systems that require the data bus to go three-state in the next cycle must also deassert Data Strobe (DS) when asserting BLST. Burst last may not be used in Early Back mode or to prematurely terminate a transformed operation.

# Inhibits and Snoop Window

Certain constraints apply to the system's assertion of inhibits and the closing of the snoop window.

The inhibit signal must not be asserted until at least two clocks after the address phase (i.e., if  $\overline{AS}$  is asserted in bus clock N, inhibit may not be asserted until N + 2 or later).

Table 2. Read Bus Acknowledge Modes

| Mode                            | Read Action                                 | Read Cycle          |  |

|---------------------------------|---------------------------------------------|---------------------|--|

| Early BACK no wait states       | System asserts DS and closes SNW by cycle N | N                   |  |

|                                 | Cntrlr asserts BACK                         | $N + k \ (k \ge 2)$ |  |

|                                 | Cntrlr supplies data                        | N + k + 1           |  |

| Early BACK with wait states     | System asserts DS and closes SNW by cycle N | N                   |  |

|                                 | Cntrlr asserts BACK                         | $N+k+1 \ (k \ge 2)$ |  |

|                                 | Cntrlr supplies data                        | N + k + 2           |  |

| Real Time BACK no wait states   | System asserts DS and closes SNW by cycle N | N                   |  |

|                                 | Cntrlr asserts BACK and supplies data       | $N+k \ (k \ge 2)$   |  |

| Real Time BACK with wait states | System asserts DS and closes SNW by cycle N | N                   |  |

|                                 | Cntrlr asserts BACK and supplies data       | $N+k+1 (k \ge 2)$   |  |

### Inhibits and Snoop Window (continued)

There must be a minimum of one bus clock cycle between the close of a transaction's snoop window and the address strobe of the next transaction (i.e., if the snoop window is deasserted on the system bus during bus clock N, the next transaction's address strobe must not be asserted until N  $\pm$  2). This scenario would most likely occur when the first transaction is inhibited but not transformed.

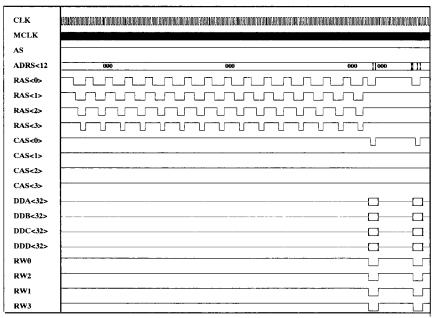

### **DRAM Interface**

The DRAM array is 128 data bits wide. This data is subdivided into banks: 4 banks of 32 bits each for the 32-bit EDC version and two banks of 64 bits each for the 64-bit EDC version. Each bank includes the associated error check bits: 7 bits for the 32-bit EDC version and 8 bits for the 64-bit EDC version. The DRAM array is divided in depth into blocks. Each block may be populated with different DRAM chip sizes, however, all DRAM chips in a given block must have the same depth. From one to four blocks may be populated with DRAM, however there are certain restrictions as given in other sections.

The DRAM interface consists of a bidirectional data bus for each DRAM bank, plus a bidirectional bus for the associated error detection and correction check bits. There is also a set of bank-associated write/read control outputs. The DRAM blocks are controlled by separate RAS and CAS control outputs. There is one RAS and one CAS for each block. The entire DRAM array is addressed through one set of 12 row/column multiplexed address lines. The row/column partition is dictated by the DRAM that populates a particular block.

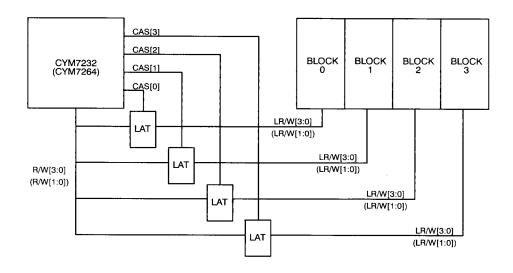

# Latch Requirements

Transparent latches are required between the R/W signals issued by the controller module and the DRAM. These latches guarantee that the R/W signals to the DRAM are stable while CAS asserted. The latch is transparent when CAS is HIGH and closed when CAS is LOW. The latches can also be used to buffer R/W lines to the DRAM. A 74ABT373 or equivalent is recommended.

There are two alternatives for the latches:

- One quad latch is devoted to each DRAM block. Each quad latch is enabled by the CAS for that block. R/W[3:0] is connected to the four inputs of the quad latch and the outputs of the quad latch are connected to the R/W inputs of the appropriate DRAM bank in that block. Refer to part (a) in Figure 2.

- One quad latch is devoted to all of the DRAM blocks, the quad latch is enabled by the logical OR of CAS[3:0]. R/W[3:0] is connected to the four inputs of the quad latch and the outputs of the quad latch are connected to the R/W inputs of the appropriate DRAM bank for all of the blocks. Refer to part (b) in Figure 2.

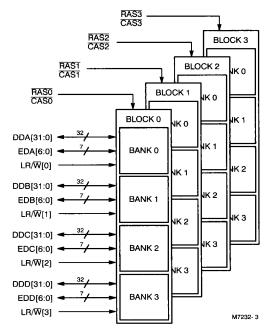

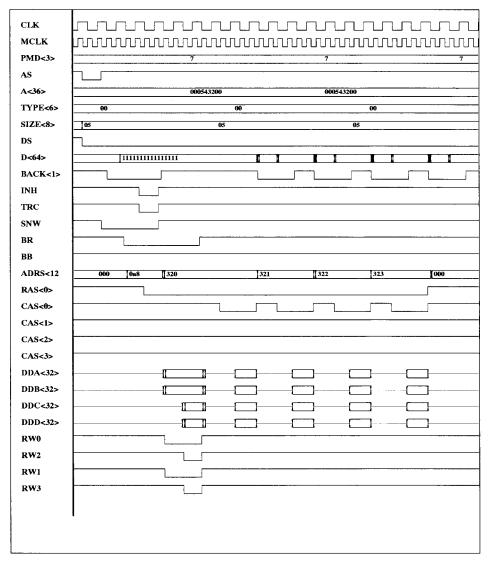

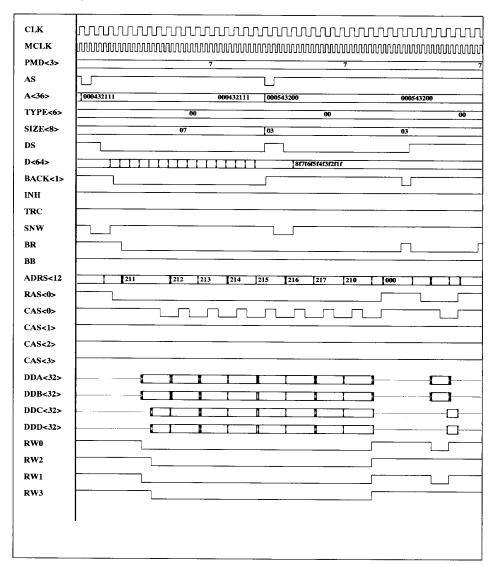

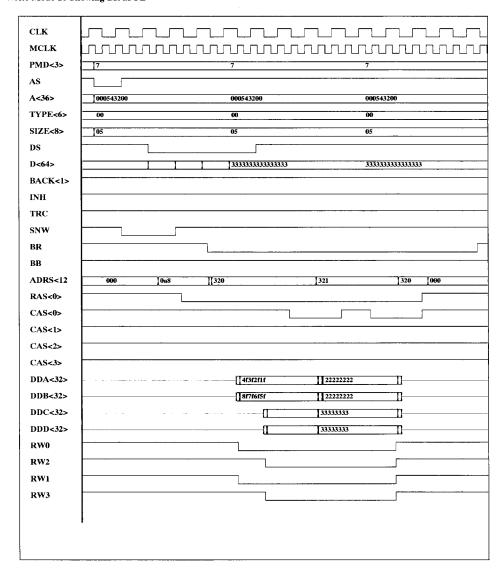

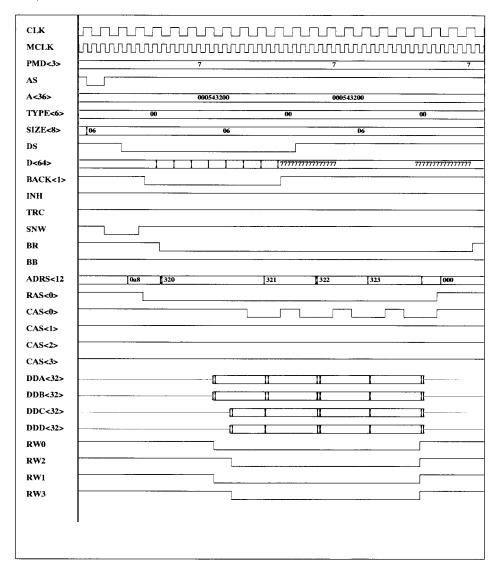

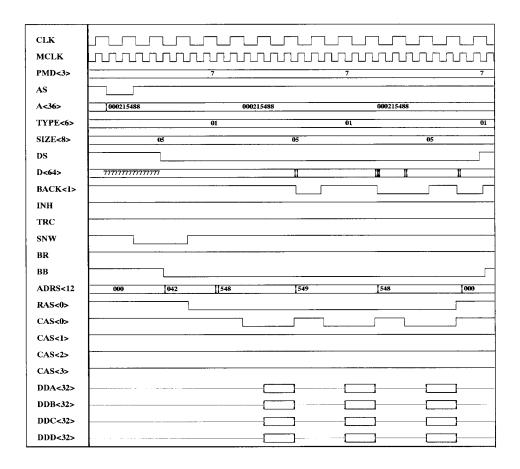

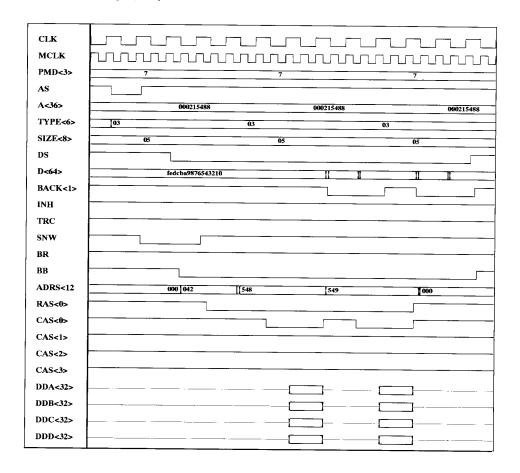

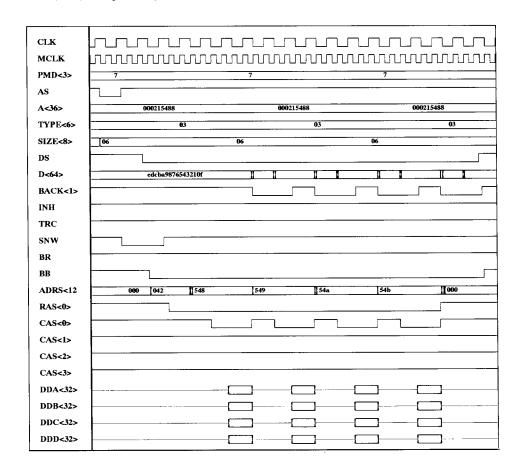

# DRAM Interface for the 32-Bit EDC

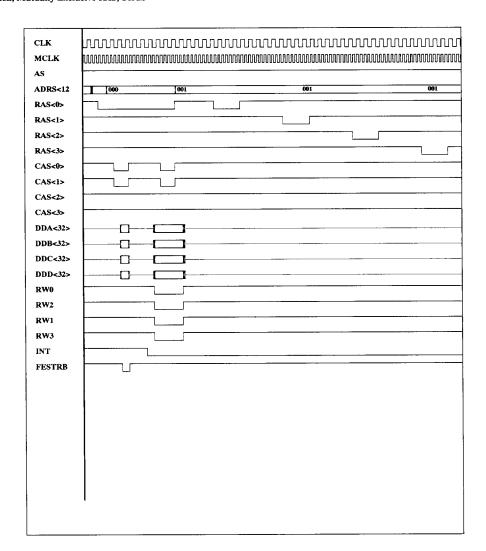

The controller supports an organization of DRAM that is 156 bits wide (four banks each consisting of 32 bits of data plus 7 error check bits) and up to four blocks deep. Each block is controlled by separate RAS and CAS signals (RAS[3:0]), CAS[3:0]). Each Bank is controlled by separate read/write signals (R/W[3:0]). The DRAM address outputs from the controller module consists of a 12-bit row/column multiplexed bus. This bus is intended to drive a symmetrical set of address driver devices, which in turn drive the DRAM array address lines. Timing for the RAS and CAS outputs as well as other DRAM related timing is programmable. A representation of the DRAM organization is shown in Figure 3.

Each square in Figure 3 represents a bank of memory that is 32 data bits wide plus 7 check bits. A block is a column of four banks

totalling 128 data bits wide plus 28 check bits. Each block is controlled by dedicated  $\overline{RAS}$  and  $\overline{CAS}$  signals. With 12 multiplexed row/column address lines, each bank can be up to 16 megabits deep. The row/column address multiplexing is programmable. The controller supports 256K-, 1M-, 4M-, and 16M-deep DRAMs.

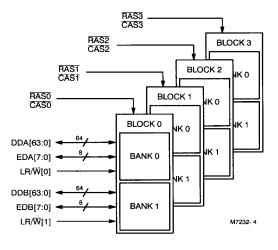

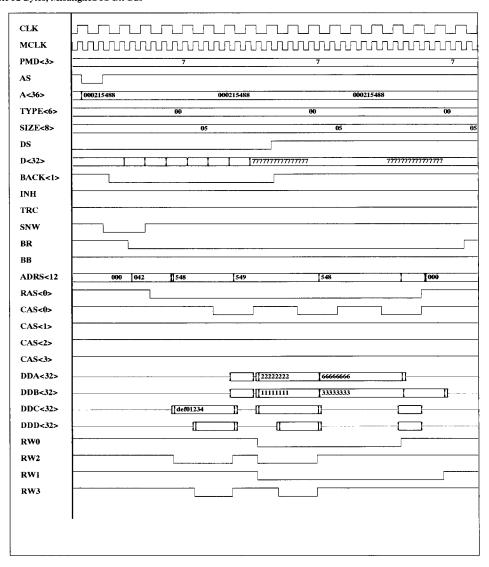

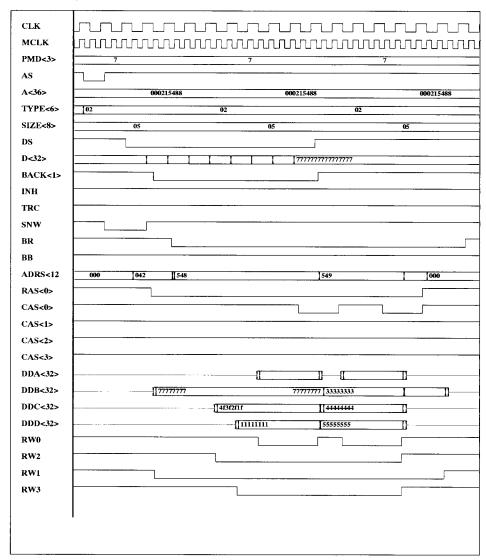

# DRAM Interface for the 64-Bit EDC

This controller supports an organization of DRAM that is 144 bits wide (two banks each consisting of 64 bits of data plus 8 error check bits) and up to four blocks deep. Each block is controlled by separate RAS and CAS signals (RAS[3:0], CAS[3:0]). Each bank is controlled by separate read/write signals (R/W[1:0]). Address outputs, RAS and CAS outputs and DRAM timing is identical to that in the 32-bit EDC version. A representation of the DRAM organization is shown in Figure 4.

Each square in Figure 4 represents a bank of memory that is 64 data bits wide plus 8 check bits. A block is a column of two banks totaling 128 data bits wide plus 16 check bits. Each block is controlled by dedicated RAS and CAS signals. With 12 multiplexed row/column address lines, each bank can be up to 16 megabits deep. As in the 32-bit EDC version, the row/column address multiplexing is programmable. The controller supports 256K-, 1M-, 4M-, and 16M-deep DRAMs.

# **DRAM Block Placement**

There are four physical DRAM blocks. Each block may be populated with an array of DRAMs that are 128 bits wide by 256K, 1M, 4M, or 16M deep. Physical block population need not be contiguous.

An array of five registers are used to specify the DRAM configuration. At power-up, the controller module is programmed with the Base address (the starting address of the entire memory array) and the Logical Block Displacement and Population (the address gap between logical blocks and their respective DRAM sizes). Finally, the physical/logical mapping is assigned and each block's RAS/CAS address split point is specified.

During operation, an incoming memory address is evaluated. Once the controller determines that this address is valid, the appropriate RAS signal for the selected block is asserted. The controller will remain inactive if the comparison is invalid. Refer to the register description for programming details.

# **DRAM Interface Signals**

# CYM7232 - 32-bit EDC

The module interface to the DRAM array is made through the signals described below.

**DDA**[31:0] — Data Bus (Bank 0). DDA[31:0] forms a 32-bit data bus that is connected to bank 0 in every populated block.

**DDB**[31:0] – Data Bus (Bank 1). DDB[31:0] forms a 32-bit data bus that is connected to bank 1 in every populated block.

**DDC[31:0]** – Data Bus (Bank 2). DDC[31:0] forms a 32-bit data bus that is connected to bank 2 in every populated block.

**DDD**[31:0] — Data Bus (Bank 3). DDD[31:0] forms a 32-bit data bus that is connected to bank 3 in every populated block.

**EDA[6:0]** – Check Bus (Bank 0). EDA[6:0] forms a 7-bit error check bit bus that is associated with the data on DDA[31:0].

**EDB**[6:0] — Check Bus (Bank 1). EDB[6:0] forms a 7-bit error check bit bus that is associated with the data on DDB[31:0].

(a)

CAS[3]

CAS[2]

CAS[1]

CAS[0]

R/W[3:0]

(R/W[1:0])

LAT

LR/W[3:0]

(b)

Figure 2. R/W Latch Configurations

Figure 3. DRAM Configuration for the CYM7232

Figure 4. DRAM Configuration for the CYM7264

# CYM7232 - 32-bit EDC (continued)

**EDC**[6:0] — Check Bus (Bank 2). EDC[6:0] forms a 7-bit error check bit bus that is associated with the data on DDC[31:0].

**EDD[6:0]** – Check Bus (Bank 3). EDD[6:0] forms a 7-bit error check bit bus that is associated with the data on DDD[31:0].

ADRS[11:0] — Address Bus. ADRS is a 12-bit row/column multiplexed address bus that supplies the address to the DRAM to access the proper 128-bit data word. The multiplexing is programmable for different depths of DRAM.

**R/W[3:0]** — Read/Write Control. R/W[3:0] are the read/write controls for the four banks of the DRAM array. R/W0 controls read/write for all blocks of DDA[31:0], R/W1 controls read/write for all blocks of DDB[31:0], R/W2 controls read/write for all blocks of DDC[31:0], and R/W3 controls read/write for all blocks of DDD[31:0].

$\overline{RAS}[3:0]$  — These signals are the four  $\overline{RAS}$  outputs to control each block of the DRAM.

**CAS**[3:0] – These signals are the four **CAS** outputs to control each block of the DRAM.

The address bus, ADRS[11:0], RAS[3:0], CAS[3:0] should be connected through a set of drivers to the appropriate DRAM inputs. R/W[3:0] should be connected through a set of latches, gated by the appropriate CAS to the DRAM R/W controls. The driver configuration is dependent upon the capacitance that must be driven.

The data bus, check bus, and read/write control signals are connected across the DRAM array. DDA[31:0] and EDA[6:0] are connected to the data I/O of all the Bank 0 DRAMs. The Bank 0 DRAMs are the top row of DRAMs in Figure 3. LR/W0 is connected to the Write Control input of all the Bank 0 DRAMs. DDB[31:0] and EDB[6:0] are connected to the data I/O of all the Bank 1 DRAMs. The bank 1 DRAMs are the second row of DRAMs. LR/W1 is connected to the Write Control input of all the Bank 1 DRAMs. This connected to the Write Control input of all the Bank 1 DRAMs. This connection pattern continues with Banks 2 and 3.

RAS0 and CAS0 are connected to the RAS and CAS inputs respectively of all of the DRAMs of Block 0. Block 0 is the left column of DRAMs in the array in Figure 3. Note that each block consists of Banks 0 through 3. Similarly, RAS1 and CAS1 are connected to the RAS and CAS inputs respectively of all of the DRAMs of Block 1. This connection pattern continues through Block 3.

# CYM7264 - 64-bit EDC

The module interface to the DRAM array is made through the signals described below.

**DDA[63:0]** — Data Bus (Bank 0). DDA[63:0] forms a 64-bit data bus that is connected to bank 0 in every populated block.

**DDB**[63:0] — Data Bus (Bank 1). DDB[63:0] forms a 64-bit data bus that is connected to bank 1 in every populated block.

**EDA[7:0]** – Check Bus (Bank 0). EDA[7:0] forms an 8-bit error check bit bus that is associated with the data on DDA[63:0].

**EDB**[7:0] — Check Bus (Bank 1). EDB[7:0] forms an 8-bit error check bit bus that is associated with the data on DDB[63:0].

ADRS[11:0] — Address Bus. ADRS is a 12-bit row/column multiplexed address bus that supplies the address to the DRAM to access the proper 128-bit data word. The multiplexing is programmable for different depths of DRAM.

# CYM7264 - 64-bit EDC (continued)

**R**\widetilde{W}[1:0] - Read/Write Control. R/\widetilde{W}[1:0] are the read/write controls for the two banks of the DRAM array. R/\widetilde{W}0 controls read/write for all blocks of DDA[63:0], R/\widetilde{W}1 controls read/write for all blocks of DDB[63:0].

**RAS**[3:0] – These signals are the four RAS outputs to control each block of the DRAM.

**CAS**[3:0] – These signals are the four **CAS** outputs to control each block of the DRAM.

The address bus, ADRS[11:0], RAS[3:0], CAS[3:0] should be connected through a set of drivers to the appropriate DRAM inputs. R/W[1:0] should be connected through a set of latches, gated by the appropriate CAS to the DRAM R/W controls. The driver configuration is dependent upon the capacitance that must be driver.

The data bus, check bus, and read/write control signals are connected across the DRAM array. DDA[64:0] and EDA[7:0] are connected to the data I/O of all the Bank 0 DRAMs. The Bank 0 DRAMs are the top row of DRAMs in Figure 4. LR/W0 is connected to the Write Control input of all the Bank 0 DRAMs. DDB[63:0] and EDB[7:0] are connected to the data I/O of all the Bank 1 DRAMs. LR/W[1] is connected to the read / write control inputs of all of the DRAMs of Bank 1.

RAS0 and CAS0 are connected to the RAS and CAS inputs respectively of all of the DRAMs of block 0. Block 0 is the left column of DRAMs in the array in Figure 4. Note that each block consists of Bank 0 and Bank 1. Similarly, RAS1 and CAS1 are connected to the RAS and CAS inputs respectively of all of the DRAMs of block 1.

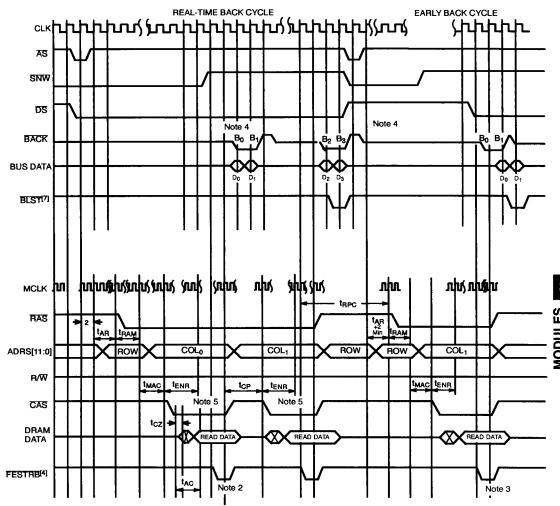

# DRAM Timing

The system bus clock rate determines the DRAM timing through an internal (X2, X4) phase locked loop, or an externally generated multiple clock (X1, X2, X3, X4 applied to MCLK input). Along with the multiplier selection, the appropriate VCO is selected to generate either a 66-MHz, 80-MHz, or 100-MHz internal clock. This selection is shown in *Table 3*. There are two versions, –H and –S. The –H version permits the use of the higher clock frequency multiples for maximum performance.

Table 3. Required PLL Frequency

| Bus Clock<br>(MHz) | Phase Lock Loop<br>Frequency (MHz)<br>– H | Phase Lock Loop<br>Frequency (MHz)<br>-S |

|--------------------|-------------------------------------------|------------------------------------------|

| 40                 | 80                                        | 80                                       |

| 33                 | 66 (int), 99 (ext)                        | 66                                       |

| 25                 | 100                                       | 50 (ext)                                 |

The phase lock loops should be operated close to their center frequency to guarantee operation. For deviations from the bus clock frequencies listed in *Table 3*, consult Command Register 4 (programming of VCO[1:0]). Refer to the CLM[1:0] field in the Command register for programming details.

DRAM timing is fully programmable through internal registers. The resolution of the timing is equal to the period of the internal clock. (This is normally twice the bus clock frequency for 40-MHz bus speeds.) The parameters listed in *Table 4* are programmable.

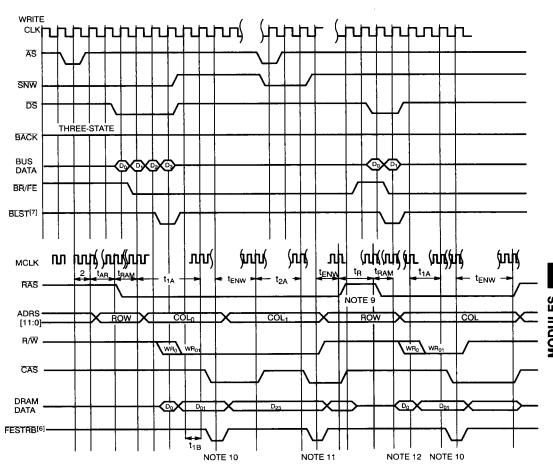

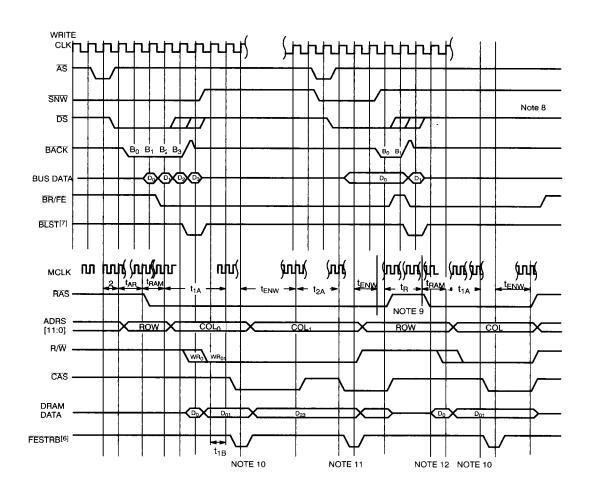

Refer to the timing diagrams at the end of this data sheet for the timing definitions. Refer to the Register Descriptions for details.

Table 4. DRAM Programmable Timing Parameters

| Parameter        | Description                                  |

|------------------|----------------------------------------------|

| t <sub>AR</sub>  | Address to RAS assertion                     |

| t <sub>RAM</sub> | RAS to multiplexed address                   |

| t <sub>MAC</sub> | Multiplexed address to CAS                   |

| t <sub>RAS</sub> | RAS pulse width                              |

| t <sub>RPR</sub> | RAS pre-charge width                         |

| t <sub>CP</sub>  | CAS pre-charge width                         |

| t <sub>DC</sub>  | FIFO data delay to CAS                       |

| t <sub>RIN</sub> | RAS completion during non-reflective inhibit |

| t <sub>ENR</sub> | Enable delay on read                         |

| t <sub>ENW</sub> | Enable delay on write                        |

# Refresh and Scrubbing

Refresh requirements vary depending on the density and organization of the DRAM chips in the system. However, rows must be refreshed at the same interval (approximately every 15 microseconds the next row is refreshed). The refresh requests are generated by two cascaded counters. A programmable 7-bit counter divides CLK down to create a 1-MHz clock signal. This clock is further divided by a 4-bit, modulo 15 counter, to generate a refresh request every 15 µsec. These refresh requests are synchronously arbitrated with memory requests.

The 26-bit Scrub Address counter is comprised of three smaller counters: the least significant 12 bits form a row scrub counter, the middle two bits form a block counter, and the most significant 12 bits form a column address counter.

All four banks of a given block are scrubbed simultaneously at a particular address. All error correction channels in the controller are used in parallel (4 channels in CYM7232, 2 channels in CYM7264). While one of the four DRAM blocks is scrubbed, the other three blocks undergo normal refresh. The 2-bit Scrub Block counter advances after all rows in a particular block are scrubbed. Finally, the column address is incremented so that all rows and blocks of the next column are refreshed and scrubbed. A fully populated memory using 16-Mbit devices to achieve 1-gigabyte capacity is scrubbed in little more than 15 minutes. When an error is detected during scrubbing operations, the correction address will be copied from the Refresh Address counter to the Error Location register. (Note that when an error occurs in a normal read operation, the corrected data is not written back into the memory array. Data is corrected inside the DRAMs during scrubbing cycles only.) When an error occurs during refresh/ scrubbing operations the refresh cycle (i.e., a read to check for errors) is turned into a scrub cycle (i.e., read-modify-write to correct the errors).

Each block of memory may be populated with different sized DRAM components however, all banks within a given block must be populated with the same depth memory chip. For simplicity, the Refresh Address counter treats every block as if it were populated with DRAMs of maximum (16-Mbit) capacity. When refreshing smaller memories, the same address location will be scrubbed multiple times before the counter advances to the next location.

### Refresh Modes

There are two modes of refresh/scrubbing. The four RAS signals are staggered differently in each mode. Staggering prevents noise problems when switching current simultaneously to multiple blocks of DRAM.

# Staggered RAS

The onset of each  $\overline{RAS}$  signal is staggered by one bus clock (four bus clocks overall) in the first mode. Once all  $\overline{RAS}$  lines are asserted a single  $\overline{CAS}$  signal is selected for presentation to the scrubbed block of memory. The strobe signal used to enable clocking of the scrubbed data into the controller is also delayed by an amount equal to the staggered  $\overline{RAS}$  delay.

### Mutually Exclusive RAS

Some SIMMs are constructed with multiple sections of RAS enabled DRAM (i.e., common CAS lines across sections) The controller offers a second non-overlapping RAS refresh mode that supports these SIMMs. This is essential so that the CAS that is asserted for the scrub operation will enable only the required SIMM section. Should this type of DRAM SIMM be used, pairs of blocks would be RAS enabled during refresh or normal DRAM accesses. Each block pair would share a common CAS. The controller may be configured to internally OR the appropriate CAS pairs to produce a single CAS output for each pair of blocks. Refresh in the non-overlapping RAS mode is longer than that of the staggered RAS refresh mode. Refer to the Register Descriptions for details.

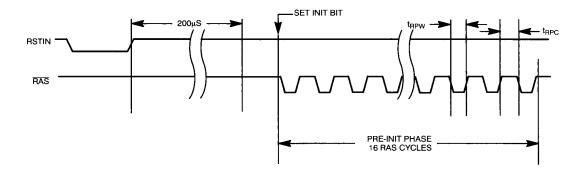

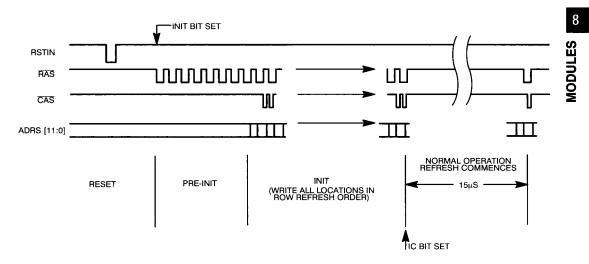

# Initialization

The DRAM is initialized when the INIT command is given. The DRAMs are energized with 15  $\overline{RAS}$  only cycles. All of DRAM can then optionally be filled with zeros and the associated error check bits.

# **Diagnostic Features**

For diagnostic purposes, the DRAM error check bits may be read or written by the system. The error check bits may be accessed by reading the EDC registers at any time. The error check bit fields will contain the error check bits from the previous DRAM read cycle. Error check bits may be directly written to DRAM by first writing the desired check bits to the Write Check Bit register and then setting the appropriate control bit in the Command register. All subsequent DRAM writes will write the check bits from this register. Clearing the control bit will return the check bit source to the data path's write error check bit generation circuitry.

# **Bus Interface Signal Description**

**D[63:0]** — Data. During the data phase, D[63:0] contains the transactions data. The system data bus signals are equipped with holding buffers. These buffers use a weak feedback buffer combined with an input buffer to form a latch. The latch holds the last value driven on the bus.

**DP[7:0]** — Data Parity. During the data phase, DP[7:0] reflects the parity of the transaction's data. During the address phase, DP[7:0] is ignored and the outputs are three-stated. Data parity is checked only over those bytes that are enabled. During a data phase write, DP[7:0] are inputs, receiving the parity as transferred across the bus. During a data phase read, DP[7:0] are outputs, indicating the parity of the data that has been applied to the bus. The parity output is enabled only when the relevant data byte is enabled. The parity outputs remain three-stated when the parity is disabled. The parity's sense (i.e., odd/even and enable/disable) is specified by the Parity Mode bits, PM[2:0]. DP[7:0] are assigned as given in *Table 5*.

The system data bus parity signals are equipped with holding buffers similar to those used by the system data bus.

**Table 5. Data Parity Assignments**

| Data Parity | Data Byte |

|-------------|-----------|

| DP[0]       | D[7:0]    |

| DP[1]       | D[15:8]   |

| DP[2]       | D[23:16]  |

| DP[3]       | D[31:24]  |

| DP[4]       | D[39:32]  |

| DP[5]       | D[47:40]  |

| DP[6]       | D[55:48]  |

| DP[7]       | D[63:56]  |

PMD[2:0] – Parity Mode. The Parity Mode bits specify the parity computation algorithm and identify those signals that participate in the parity computation. They must be hardwired for the correct configuration. The parity mode selection is applied to both the address and data buses. These bits are defined below.

| 0          | Even Parity Computed (sum of bits in byte and parity bit is even.) Odd Parity Computed (sum of bits in byte and parity bit is odd.) |

|------------|-------------------------------------------------------------------------------------------------------------------------------------|

| <u>PM1</u> | Data Parity Disabled                                                                                                                |

0 Data Parity Disabled

1 Data Parity Computed

PM0

0 Address Parity Disabled

1 Address Parity Computed

A[35:0] — Address. During the address phase, the system will supply the transaction's address on A[35:0] and assert AS.

AP[3:0] — Address Parity. During the address phase, the lowest 32 bits of the transaction's address can be checked for parity. The system can generate a set of parity inputs AP[3:0] that correspond to A[31:0]. Parity is not supported for A[35:32]. The parity's sense (i.e., odd/even and enable/disable) is specified by the Parity Mode bits, PM[2:0]. Note that the parity mode bits also define the parity mode for the data bus. AP[3:0] are assigned as given in Table 6.

**Table 6. Address Parity Assignments**

| Address Parity | Address Byte |

|----------------|--------------|

| AP[0]          | A[7:0]       |

| AP[1]          | A[15:8]      |

| AP[2]          | A[23:16]     |

| AP[3]          | A[31:24]     |

**TYPE**[5:0] — Transaction Type. During the address phase, TYPE[5:0] specify the Transaction Type (see *Table 7*). These are synchronous inputs. Note that the TYPE input may be changed on a transaction by transaction basis, consequently, different processors may be mixed within the system.

**TYPE0** - Read/Write. When 0, this bit indicates the transaction is a write. When 1, this bit indicates the transaction is a read.

**Table 7. Type Interpretation**

| Type Bits |   |   |   | Data Size | Transaction Type |               |                             |

|-----------|---|---|---|-----------|------------------|---------------|-----------------------------|

| 5         | 4 | 3 | 2 | 1         | 0                |               |                             |

| 0         | 0 | X | X | X         | 0                | Any           | Write                       |

| 0         | X | X | Х | X         | 1                | Any           | Read                        |

| 1         | 0 | X | X | X         | 0                | Default Burst | Write                       |

| 1         | X | X | X | X         | 1                | Default Burst | Read                        |

| X         | X | X | X | 0         | X                | ≥ Bus Width   | Sequential Burst Order      |

| X         | X | X | X | 1         | X                | ≥ Bus Width   | Intel Burst Order           |

| Х         | X | X | 0 | X         | X                | Any           | Size [3:0] are Size Bits    |

| 0         | X | X | 1 | X         | X                | ≤ Bus Width   | Size [7:0] are Byte Enables |

| X         | X | 0 | x | Х         | Х                | Any           | Little-Endian Bus           |

| X         | X | 1 | Х | X         | X                | Any           | Big-Endian Bus              |

| 0         | 1 | X | X | X         | 0                | Any           | Posted Write                |

| 1         | 1 | Х | X | X         | 0                | Default Burst | Posted Write                |

TYPE1 – Burst Order. Given a system bus of width N bytes (N = 4 or 8), any transaction as specified by the SIZE input which is greater than N constitutes a burst. Thus transactions of double words (8 bytes) and larger are bursts for a 32-bit bus and transactions of 16 bytes and larger are bursts for a 64-bit bus. The maximum burst length is 128 bytes. During bursts the lowest order bits of the address input are ignored. AD[1:0] are ignored for a 32 bit bus system and AD[2:0] are ignored for a 64 bit bus system. This is the alignment constraint.

The next higher set of address inputs are loaded into a counter, which generates the proper address as the burst proceeds. The counter length is given in *Table 8*. The generated burst address will wrap around at the cache line end and complete the burst access for the remainder of the cache line.

**Table 8. Burst Counter Length**

| Burst Length<br>(bytes) | Burst Counter Length<br>for 32-Bit Bus (bits) | Burst Counter<br>Length for 64-Bit<br>Bus (bits) |

|-------------------------|-----------------------------------------------|--------------------------------------------------|

| 8                       | 1                                             | Not Burst                                        |

| 16                      | 2                                             | 1                                                |

| 32                      | 3                                             | 2                                                |

| 64                      | 4                                             | 3                                                |

| 128                     | 5                                             | 4                                                |

A new address, in which the burst counter serves as the lowest portion, is formed. The counter extends the length of address bits as shown in *Table 8* and starts at AD2 for a 32-bit system bus and at AD3 for a 64-bit system bus. All higher address bits (above the counter) remain fixed throughout the burst transaction and are not affected by rollover of the burst counter. As an example, for a 64-bit system bus and a SIZE of 64 bytes, the system ignores AD[2:0], fixing these bits at 0. AD[5:3] form the internal burst counter starting from the address as transferred over the system bus, and AD[35:6] remain fixed as originally input. This address generation is shown for this example in *Table 9*.

Table 9. Burst Address Example

|  | AD[35:6]<br>Fixed | AD[5:3] AD[2<br>Counter 000 | , I |

|--|-------------------|-----------------------------|-----|

|--|-------------------|-----------------------------|-----|

When TYPE1 = 0 the burst order is sequential. Subsequent addresses are generated by sequentially incrementing the bits of the address within the range of the burst counter as determined above. After reaching the address in which all burst counter bits are ones, the counter wraps around to zero. Higher-order addresses remain fixed.

When TYPE1 = 1 the burst counter increments in the non-sequential fashion characteristic of Intel processors. In all other respects, the address for the burst is the same as that in the sequential case. The non-sequential burst counter algorithm extends the Intel scheme to any length burst. The nonsequential counting starts at the address specified by the address bus input. The counter bits are then incremented in the following fashion:

- 1. the lowest-order bit always toggles,

- 2. a bit toggles only if the next lowest order bit in the counter is toggling for the second time (independent of its value).

For example, if the burst counter is 3 bits in length (AD[5:3] as above) and begins at address 101, then the counting sequence is 101, 100, 111, 110, 001, 000, 011, 010

Notice that in this counting sequence, higher-order bits change the least often and therefore result in a minimum number of DRAM page mode accesses.

**TYPE2** – SIZE Interpretation. The SIZE bits have two alternative interpretations. When TYPE2 = 0, the transaction length in bytes is given by the value of SIZE[3:0]. When TYPE2 = 1, the byte(s) that are enabled in the transaction are specified when their respective size bits are asserted LOW (e.g., SIZE[N] means BYTE[N] participates in the transaction). For elaboration see the SIZE[7:0] definition.

**TYPE3** – Little Endian/Big Endian. Processors may define the position of BYTE 0 on the bus in either of two ways. Either BYTE 0 appears as the lowest byte on the bus (D[7:0] – little endian, TYPE3 = 0) or BYTE 0 appears as the highest byte on the bus (big endian – D[M:M-7], where M = Bw – 1. Bw is the bus width in bits, TYPE3 = 1). For elaboration see the definition of the SIZE[7:0] bits.

**TYPE4** – Write Posting. When TYPE4 = 1, the write data is posted into the Write FIFO, where it remains until the next read is completed. This can be used to postpone the actual DRAM write until after the DRAM read is completed, thereby speeding cache line fills.

TYPE5 – Default Burst Mode. When TYPE5 = 0, the transaction's size is specified by SIZE[7:0] (which are interpreted according to TYPE2). When TYPE5 = 1, the transaction's size is specified by the default burst size programmed into the Command register. The burst size defaults to this value regardless of TYPE5 during reflective reads transformed into writes and writes transformed to reads for ownership.

SIZE[7:0] — Transaction Size. During the address phase, SIZE[3:0] specify the number of bytes to be transferred during a bus transaction. These are synchronous inputs. SIZE[7:4] are an extended size control used to support byte enabled transfers. The expanded definition is compatible with 1486, 1860, SPARC, MIPS, 88K and 68040 processors. The interpretation of SIZE is determined by TYPE2 as in *Table 10* through *Table 16*. Note that for size specifications that are larger than the system bus size, the Transaction Size specifies the internal burst address generation wraparound.

Two interpretations are offered in the above table to support SPARC MBus and Motorola 88K processors.

Table 10. Size Interpretation with TYPE2 = 0, SIZE[7:4] = XXXX

| SIZE 3 | SIZE 2 | SIZE 1 | SIZE 0 | Transaction Size     |

|--------|--------|--------|--------|----------------------|

| 0      | 0      | 0      | 0      | Byte                 |

| 0      | 0      | 0      | 1      | Halfword (2 Bytes)   |

| 0      | 0      | 1      | 0      | Word (4 Bytes)       |

| 0      | 0      | 1      | 1      | Doubleword (8 Bytes) |

| 0      | 1      | 0      | 0      | 16-Byte Burst        |

| 0      | 1      | 0      | 1      | 32-Byte Burst        |

| 0      | 1      | 1      | 0      | 64-Byte Burst        |

| 0      | 1      | 1      | 1      | 128-Byte Burst       |

| 1      | 0      | 0      | 0      | 32-Byte Burst        |

| 1      | 0      | 0      | 1      | 32-Byte Burst        |

| 1      | 0      | 1      | 0      | 64-Byte Burst        |

| 1      | 0      | 1      | 1      | 64-Byte Burst        |

| 1      | 1      | 0      | 0      | Doubleword (8 Bytes) |

| 1      | 1      | 0      | 1      | Word (4 Bytes)       |

| 1      | 1      | 1      | 0      | Halfword (2 Bytes)   |

| 1      | 1      | 1      | 1      | Byte                 |

Table 11. 64 Bit Bus Address Interpretation Size = 1 Byte

| A2 | A1 | A0 | Byte # | Big Endian | Little Endian |

|----|----|----|--------|------------|---------------|

| 0  | 0  | 0  | 0      | D[63:56]   | D[7:0]        |

| 0  | 0  | 1  | 1      | D[55:48]   | D[15:8]       |

| 0  | 1  | 0  | 2      | D[47:40]   | D[23:16]      |

| 0  | 1  | 1  | 3      | D[39:32]   | D[31:24]      |

| 1  | 0  | 0  | 4      | D[31:24]   | D[39:32]      |

| 1  | 0  | 1  | 5      | D[23:16]   | D[47:40]      |

| 1  | 1  | 0  | 6      | D[15:8]    | D[55:48]      |

| 1  | 1  | 1  | 7      | D[7:0]     | D[63:56]      |

Table 12. 64 Bit Bus Address Interpretation Size = 2 Bytes

| A2 | A1 | A0 | Halfword # | Big Endian | Little Endian |

|----|----|----|------------|------------|---------------|

| 0  | 0  | X  | 0          | D[63:48]   | D[15:0]       |

| 0  | 1  | X  | 1          | D[47:32]   | D[31:16]      |

| 1  | 0  | Х  | 2          | D[31:16]   | D[47:32]      |

| 1  | 1  | X  | 3          | D[15:0]    | D[63:48]      |

Table 13. 64 Bit Bus Address Interpretation Size = 4 Bytes

| A2 | A1 | A0 | Word # | Big Endian | Little Endian |

|----|----|----|--------|------------|---------------|

| 0  | X  | X  | 0      | D[63:32]   | D[31:0]       |

| 1  | X  | X  | 1      | D[31:0]    | D[63:32]      |

Table 14. 32 Bit Bus Address Interpretation Size = 1 Byte

|   | A2 | <b>A1</b> | A0 | Byte # | Big Endian | Little Endian |

|---|----|-----------|----|--------|------------|---------------|

| Γ | X  | 0         | 0  | 0      | D[31:24]   | D[7:0]        |

|   | X  | 0         | 1  | 1      | D[23:16]   | D[15:8]       |

| Γ | X  | 1         | 0  | 2      | D[15:8]    | D[23:16]      |

|   | X  | 1         | 1  | 3      | D[7:0]     | D[31:24]      |

Table 15. 32 Bit Bus Address Interpretation Size = 2 Bytes

| A2 | A1 | A0 | Half-<br>Word # | Big Endian | Little Endian |

|----|----|----|-----------------|------------|---------------|

| X  | 0  | X  | 0               | D[31:16]   | D[15:0]       |

| X  | 1  | X  | 1               | D[15:0]    | D[31:16]      |

Table 16. Size Interpretation with TYPE2 = 1

|   |   |   | Size |   | Byte |   |   |          |

|---|---|---|------|---|------|---|---|----------|

| 7 | 6 | 5 | 4    | 3 | 2    | 1 | 0 |          |

| X | Х | X | X    | Х | X    | X | 0 | D[7:0]   |

| X | Х | Х | X    | X | X    | 0 | Х | D[15:8]  |

| X | X | X | X    | X | 0    | X | X | D[23:16] |

| X | X | X | X    | 0 | X    | X | X | D[31:24] |

| X | X | X | 0    | X | X    | X | X | D[39:32] |

| X | Х | 0 | X    | X | X    | X | Х | D[47:40] |

| X | 0 | X | X    | Х | X    | Х | X | D[55:48] |

| 0 | X | Х | X    | X | X    | X | X | D[63:56] |

Processors generally require their byte enable signals to be contiguous. No checking is performed to distinguish invalid combinations from valid combinations.

$\overline{\rm AS}$  – Address Strobe. This signal is asserted by the bus master during the address phase of the transaction. The address and transaction attributes are strobed into the Controller Module during the address phase. The address phase is one clock cycle long and is normally followed by one or more data phases.

DS — Data Strobe. This signal is asserted by the bus master to begin the data phase of the transaction. Data strobe is recognized in certain modes and can be used by the system to delay the onset of the transaction. If the transaction is a burst, data strobe can not be used to interrupt or delay individual data phases of the burst. Data Strobe may be permanently asserted in those applications that do not need this function. Refer to the section on Bus Acknowledge and Data Strobe Modes for details.

BLST – Burst Last. The burst length is specified by SIZE[3:0] or the programmed default burst length by way of the TYPE input during the address phase of every transaction. BLST may be used by the bus master to override the default or SIZE specified burst length by prematurely terminating the bus transaction. BLST must be asserted in the same cycle as the last data transfer.

INH — Inhibit. This signal may be asserted by a cache controller in multiprocessing environments to abort a bus transaction already in progress. When INH is received before the snoop window ends, the operation is terminated. If the transaction is a memory read, no data is transferred over the system bus while the snoop window is open. If the transaction is a memory write and data has already been transferred, the internal FIFOs are cleared. Inhibit may be used to prematurely terminate I/O opera-

tions before data is transferred.  $\overline{\text{INH}}$  should not be asserted after the snoop window closes.

TRC – Transform Cycle. This signal, when asserted along with INH, transforms an inhibited read cycle into a write cycle (reflective) or an inhibited write cycle into a read cycle (read-for-owner-ship). Transformed transactions use the programmed default burst length and ignore the SIZE specified in the original transaction. The burst begins at the address specified at the transaction start.

**SNW** – Snoop Window. This input may be used to define the duration of the snoop window. Operations may be inhibited and transformed in any cycles in which this signal is asserted. As an alternative, the duration of the snoop window may be defined by an internal counter.

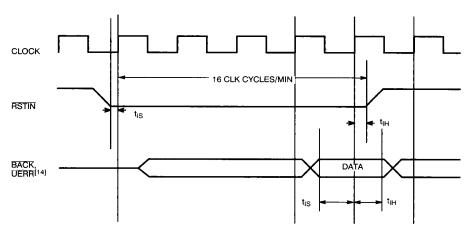

RSTIN – Reset In. This signal is used to reset the controller. The signal must last for at least 16 clocks. This signal is internally synchronized to the bus clock.

BACK[1:0] — Bus Acknowledge. These signals supply the transaction acknowledge to the bus master. They are defined in *Table 17*. These signals also receive acknowledges from the system during reflective reads thereby acting as data strobes. During system reset BACK[1:0] act as inputs to program bus acknowledge modes and select the source of the snoop window signal.

BACK[1:0] are used as inputs during Reset to select the Bus Acknowledge and Data Strobe modes. BACK[1:0] must be driven according to Table 18 when Reset is asserted to invoke the desired mode.

$\overline{\text{UERR}}$  – Uncorrectable Error Interrupt. This signal indicates the presence of an unrecoverable error condition on a read operation. The signal is asserted at the same time as the associated acknowledge is sent to the system bus. As with  $\overline{\text{BACK}}[1:0]$ ,  $\overline{\text{UERR}}$  may serve as an input. The signal must be driven to select the source of the Snoop Window signal during system reset.  $\overline{\text{UERR}}$  should be pulled up with a 1K-ohm resistor to  $V_{CC}$ .

Table 17. BACK[1:0] Outputs

| BACK1       | BACK0       | Definition          |

|-------------|-------------|---------------------|

| 0           | 1           | Valid Data Transfer |

| 1           | 1           | Wait States         |

| Three-state | Three-state | Idle Cycles         |

Table 18. BACK[1:0] Inputs When RSTIN is Asserted

| BACK1 | BACK0 | DS Mode           | BACK Mode          |

|-------|-------|-------------------|--------------------|

| 0     | 0     | MBus (DS Gnd)     | With Data          |

| 0     | 1     | Early DS (1 Clk)  | With Data          |

| 1     | 0     | Real-Time DS      | None (Uses BR/FE)  |

| 1     | 1     | Early DS (2 Clks) | Early BACK (1 Clk) |

Table 19. UERR Inputs When RSTIN is Asserted

| UERR (SNW) | Snoop Window Source |

|------------|---------------------|

| 0          | External            |

| 1          | Internal            |

When a read is inhibited and transformed into a write, the BACK[1:0] signals become inputs and are used to strobe the bus data into the Reflective FIFO. *Table 20* gives the interpretation of the BACK[1:0] inputs when the reflective writes are in progress.

Table 20. BACK[1:0] Inputs as Reflective Reads are Transformed Into Writes

| BACK1 | BACK0 | Definition          |

|-------|-------|---------------------|

| 0     | 1     | Valid Data Transfer |

| 1     | 1     | Idle Cycle          |

| Other | Modes | Invalid             |

**BERR** — Bus Error. This signal indicates that a parity error condition has occurred during the address or data phase of a transaction. This signal is asynchronous (i.e., it will occur one cycle after the corresponding address parity error or two cycles after the corresponding data parity error). **BERR** may be programmed to last for one clock cycle or until cleared. Due to the nature of **BERR** internal to the module, the controller will log a parity error in its status register if any other device pulls **BERR** LOW.