|                                                                                               |                                                                            |                            |         |                             |                                                          |                                  |              | F            | REVISI  | ONS          |              |                      |                         |                   |                                |                                     |                                |                   |         |              |

|-----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------|---------|-----------------------------|----------------------------------------------------------|----------------------------------|--------------|--------------|---------|--------------|--------------|----------------------|-------------------------|-------------------|--------------------------------|-------------------------------------|--------------------------------|-------------------|---------|--------------|

| LTR                                                                                           | DESCRIPTION                                                                |                            |         |                             |                                                          |                                  |              |              |         | D            | ATE (Y       | /R-MO-E              | DA)                     |                   | APPROVED                       |                                     | )                              |                   |         |              |

| Α                                                                                             | Char                                                                       | nges ir                    | n acco  | rdance                      | e with                                                   | NOR (                            | 5962-F       | 3051-9       | 94.     |              |              |                      | 93-11-30                |                   |                                | K. A. Cottongim                     |                                |                   |         |              |

| В                                                                                             | Add                                                                        | device                     | types   | s 09 th                     | rough                                                    | 24.                              |              |              |         |              |              |                      |                         | 95-0              | 1-19                           |                                     | K. A. Cottongim                |                   |         |              |

| С                                                                                             | Char                                                                       | nges ir                    | n acco  | rdance                      | e with                                                   | NOR :                            | 5962-F       | 3121-9       | 95.     |              |              |                      |                         | 95-0              | 4-27                           |                                     | к                              | (, A, C           | ottong  | im           |

| D                                                                                             | Char                                                                       | nges ir                    | n acco  | rdance                      | e with                                                   | NOR :                            | 5962-F       | 3014-9       | 96.     |              |              |                      |                         | 95-1              | 2-15                           |                                     | K. A. Cottongim                |                   |         | im           |

| E                                                                                             | Add                                                                        | device                     | types   | 25 ar                       | nd 26.                                                   | Add o                            | case o       | utlines      | Tano    | d U.         |              |                      |                         | 98-0              | 06-1 <b>1</b>                  |                                     | K. A. Cottongim                |                   |         | im           |

| F                                                                                             | Corre                                                                      | ect fig                    | ure 1,  | case c                      | outline                                                  | Z, pin                           | 1 inde       | ex.          |         |              |              |                      |                         | 98-0              | 9-11                           |                                     | l ĸ                            | . A. C            | ottong  | im           |

|                                                                                               |                                                                            |                            |         |                             |                                                          |                                  |              |              |         |              |              |                      |                         |                   |                                |                                     |                                |                   |         |              |

|                                                                                               |                                                                            |                            |         |                             |                                                          |                                  |              |              |         |              |              |                      |                         |                   |                                |                                     |                                |                   |         |              |

| REV                                                                                           |                                                                            |                            |         |                             |                                                          |                                  |              |              |         |              |              |                      |                         |                   |                                |                                     |                                |                   |         | <b></b>      |

| SHEET                                                                                         |                                                                            |                            |         |                             |                                                          |                                  |              |              |         |              |              |                      |                         |                   |                                |                                     |                                |                   |         |              |

| SHEET                                                                                         | F                                                                          | F                          | F       | F                           | F                                                        | F                                | F            | F            | F       | F            | F            | F                    | F                       |                   |                                |                                     |                                |                   |         |              |

| SHEET<br>REV<br>SHEET                                                                         | 15                                                                         | F<br>16                    | F 17    | 18                          | 18                                                       | F 20                             | 21           | 22           | 23      | 24           | 25           | 26                   | 27                      |                   |                                |                                     |                                |                   |         |              |

| SHEET                                                                                         | 15<br>JS                                                                   |                            |         | 18<br>RE\                   | 18                                                       |                                  | 21<br>F      | 22<br>F      | 23<br>F | 24<br>F      | 25<br>F      | 26<br>F              | 27<br>F                 | F                 | F                              | F                                   | F                              | F 12              | F 12    | F 14         |

| SHEET REV SHEET REV STATE                                                                     | 15<br>JS                                                                   |                            |         | 18<br>RE\<br>SHE            | 18                                                       | 20<br>BY                         | 21           | 22           | 23      | 24           | 25<br>F<br>5 | 26<br>F<br>6         | 27<br>F<br>7            | 8<br>UPPL<br>P. O | 9<br>.Y CEI                    | 10<br>NTER<br>3990                  | 11<br>COLU                     | 12<br>IMBUS       | 13      | <del></del>  |

| SHEET REV SHEET REV STATI OF SHEET PMIC N/A STA                                               | JS<br>S<br>NDA                                                             | RD<br>CUI                  | 17      | 18 RE\ SHE PREI             | 18  / EET  PARECeve Dur                                  | 20<br>DBY<br>ncan                | 21<br>F<br>1 | 22<br>F      | 23<br>F | 24<br>F      | 25<br>F<br>5 | 26<br>F<br>6         | 27<br>F<br>7            | 8<br>UPPL<br>P. O | 9<br>.Y CEI                    | 10<br>NTER<br>3990                  | 11                             | 12<br>IMBUS       | 13      | <del> </del> |

| SHEET REV SHEET REV STATIOF SHEET  PMIC N/A  STA MICRO DR  THIS DRAW FOR                      | JS<br>S<br>NDA<br>OCIR<br>AWIN                                             | RD<br>CUII<br>IG           | 17<br>T | 18 REN SHE PREI Ste CHE     | 18  / EET  PAREC eve Dur  CKED  chael C                  | 20<br>BY<br>can<br>BY            | 21<br>F      | 22<br>F      | 23<br>F | 24<br>F<br>4 | 25<br>F<br>5 | 26<br>F<br>6<br>DEFE | F<br>7<br>NSE S<br>COLU | 8 SUPPL P. O      | 9<br>.Y CEI<br>. BOX<br>S, OHI | 10<br>NTER<br>3990<br>O 432         | 11<br>COLU<br>216-50           | 12<br>IMBUS<br>00 | 13      | 14           |

| SHEET REV SHEET REV STATIOF SHEET  PMIC N/A  STA MICRO DR  THIS DRAW FOR                      | JS<br>S<br>NDA<br>OCIR<br>AWIN<br>ING IS A<br>USE BY<br>ARTMEN<br>ENCIES C | RD<br>CUI'<br>IG<br>VAILAI | T BLE   | 18 RE\ SHE PREI Ste CHE Mic | 18  / EET  PAREC  Ve Dur  CKED  Chael C  ROVEC  Idall A. | 20 DBY ncan BY Cotton            | 21<br>F      | 22<br>F<br>2 | 23<br>F | P 4 MIC BC/  | F<br>5       | 26<br>F<br>6<br>DEFE | F 7 NSE S COLU          | 8 SUPPL P. O      | 9<br>.Y CEI<br>. BOX<br>S, OHI | 10<br>NTER<br>3990<br>O 432<br>NEAR | 11<br>COLU<br>216-50           | 12<br>IMBUS<br>00 | 13<br>S | 14           |

| SHEET REV SHEET REV STATIOF SHEET  PMIC N/A  STA MICRO DR  THIS DRAW FOR DEP AND AGI DEPARTMI | JS<br>S<br>NDA<br>OCIR<br>AWIN<br>ING IS A<br>USE BY<br>ARTMEN<br>ENCIES C | RD<br>CUI'<br>IG<br>VAILAI | T BLE   | 18 RE\ SHE PREI Ste CHE Mic | 18  / EET  PAREC  Ve Dur  CKED  Chael C  ROVEC  Idall A. | 20 DBY Cotton  APPRO 93-0  LEVEL | gim  DVAL E  | 22<br>F<br>2 | 23<br>F | P 4 MIC BC/  | F<br>5       | 26<br>F<br>6<br>DEFE | F<br>7<br>NSE S<br>COLU | 8 SUPPL P. O      | 9<br>.Y CEI<br>. BOX<br>S, OHI | 10<br>NTER<br>3990<br>O 432<br>NEAR | 11<br>COLU<br>216-50<br>R, MIL | 12<br>IMBUS<br>00 | 13<br>S | 14           |

DSCC FORM 2233

APR 97

DISTRIBUTION STATEMENT A. Approved for public release; distribution is unlimited.

5962-E516-98

9004708 0039168 078

#### 1. SCOPE

- 1.1 <u>Scope</u>. This drawing documents five product assurance classes, class D (lowest reliability), class E, (exceptions), class G (lowest high reliability), class H (high reliability), and class K, (highest reliability) and a choice of case outlines and lead finishes are available and are reflected in the Part or Identifying Number (PIN). When available, a choice of radiation hardness assurance levels are reflected in the PIN.

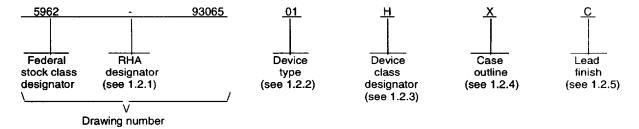

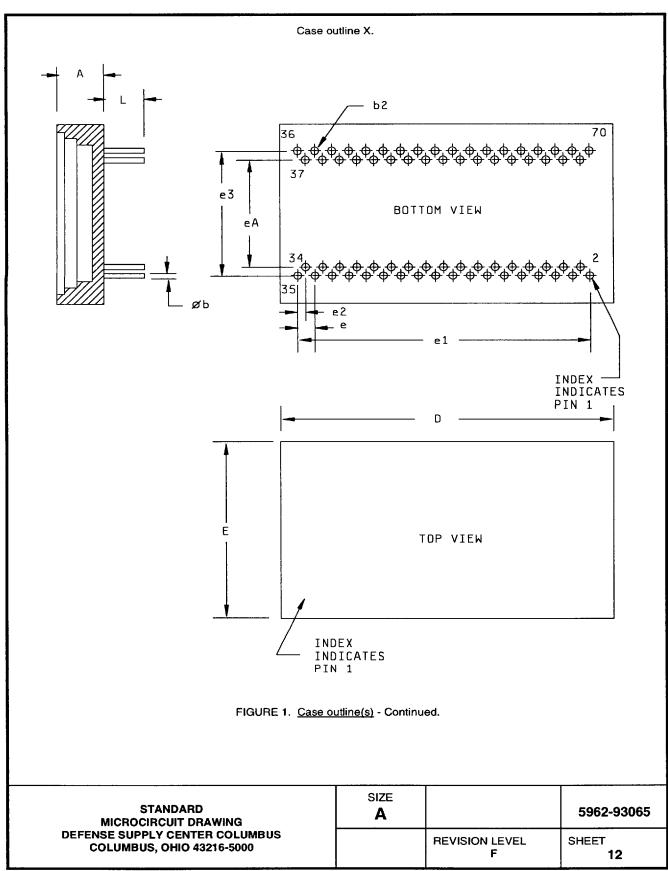

- 1.2 PIN. The PIN shall be as shown in the following example:

- 1.2.1 <u>Radiation hardness assurance (RHA) designator</u>. Device classes H and K RHA marked devices shall meet the MIL-PRF-38534 specified RHA levels and shall be marked with the appropriate RHA designator. A dash (-) indicates a non-RHA device.

- 1.2.2 Device type(s). The device type(s) shall identify the circuit function as follows:

| Device type | Generic number | <u>Circuit function</u>                                                 |

|-------------|----------------|-------------------------------------------------------------------------|

| 01          | BU-65170X1     | MIL-STD-1553, RT, 4K RAM, +5/-15 V transceiver                          |

| 02          | BU-65170X2     | MIL-STD-1553, RT, 4K RAM, +5/-12 V transceiver                          |

| 03          | BU-61580X1     | MIL-STD-1553, BC/RT/MT, 4K RAM, +5/-15 V transceiver                    |

| 04          | BU-61580X2     | MIL-STD-1553, BC/RT/MT, 4K RAM, +5/-12 V transceiver                    |

| 05          | BU-65171X1     | MIL-STD-1553, RT, 4K RAM, +5/-15 V transceiver, RT address latch        |

| 06          | BU-65171X2     | MIL-STD-1553, RT, 4K RAM, +5/-12 V transceiver, RT address latch        |

| 07          | BU-61581X1     | MIL-STD-1553, BC/RT/MT, 4K RAM, +5/-15 V transceiver, RT address latch  |

| 08          | BU-61581X2     | MIL-STD-1553, BC/RT/MT, 4K RAM, +5/-12 V transceiver, RT address latch  |

| 09          | BU-65170X3     | MIL-STD-1553, RT, 4K RAM, +5 V transceiver                              |

| 10          | BU-65170X6     | MIL-STD-1553, RT, 4K RAM, +5 V transceiver                              |

| 11          | BU-61580X3     | MIL-STD-1553, BC/RT/MT, 4K RAM, +5 V transceiver                        |

| 12          | BU-61580X6     | MIL-STD-1553, BC/RT/MT, 4K RAM, +5 V transceiver                        |

| 13          | BU-65171X3     | MIL-STD-1553, RT, 4K RAM, +5 V transceiver, RT address latch            |

| 14          | BU-65171X6     | MIL-STD-1553, RT, 4K RAM, +5 V transceiver, RT address latch            |

| 15          | BU-61581X3     | MIL-STD-1553, BC/RT/MT, 4K RAM, +5 V transceiver, RT address latch      |

| 16          | BU-61581X6     | MIL-STD-1553, BC/RT/MT, 4K RAM, +5 V transceiver, RT address latch      |

| 17          | BU-61585X1     | MIL-STD-1553, BC/RT/MT, 12K RAM, +5/-15 V transceiver                   |

| 18          | BU-61585X2     | MIL-STD-1553, BC/RT/MT, 12K RAM, +5/-12 V transceiver                   |

| 19          | BU-61586X1     | MIL-STD-1553, BC/RT/MT, 12K RAM, +5/-15 V transceiver, RT address latch |

| 20          | BU-61586X2     | MIL-STD-1553, BC/RT/MT, 12K RAM, +5/-12 V transceiver, RT address latch |

| 21          | BU-61585X3     | MIL-STD-1553, BC/RT/MT, 12K RAM, +5 V transceiver                       |

| 22          | BU-61585X6     | MIL-STD-1553, BC/RT/MT, 12K RAM, +5 V transceiver                       |

| 23          | BU-61586X3     | MIL-STD-1553, BC/RT/MT, 12K RAM, +5 V transceiver, RT address latch     |

| 24          | BU-61586X6     | MIL-STD-1553, BC/RT/MT, 12K RAM, +5 V transceiver, RT address latch     |

| 25          | BU-61588X3     | MIL-STD-1553, BC/RT/MT, 4K RAM, +5 V transceiver                        |

| 26          | BU-65178X3     | MIL-STD-1553, RT, 4K RAM, +5 V transceiver                              |

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                     | 5962-93065 |

|-------------------------------------------------------------|------------------|---------------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL<br>F | SHEET 2    |

DSCC FORM 2234 APR 97

■ 9004708 0039169 TO4 ■

1.2.3 <u>Device class designator</u>. This device class designator shall be a single letter identifying the product assurance level as follows:

Device class

Device performance documentation

D, E, G, H, or K

Certification and qualification to MIL-PRF-38534

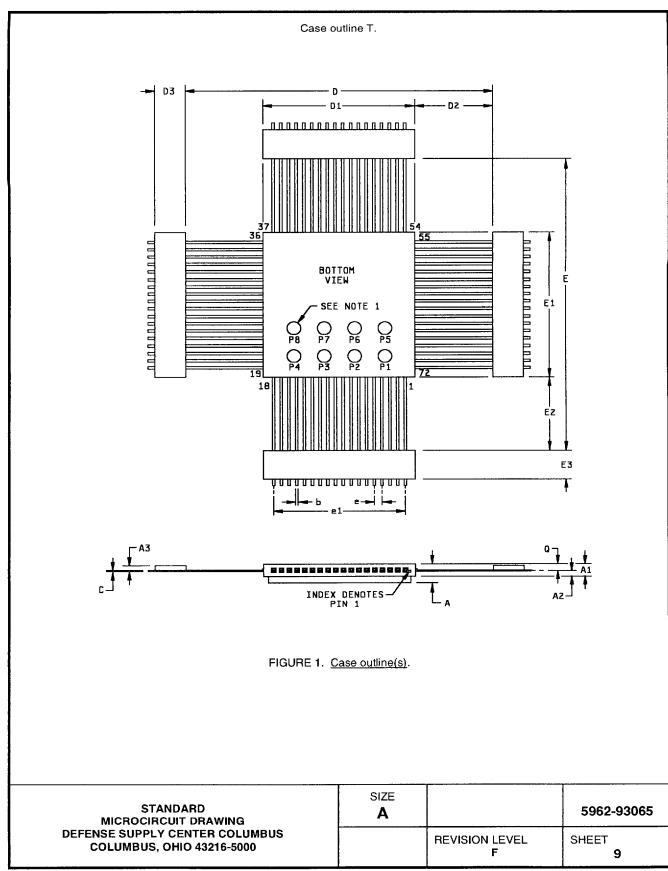

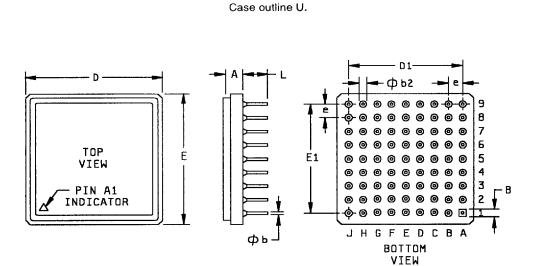

1.2.4 Case outline(s). The case outline(s) shall be as designated in MIL-STD-1835 and as follows:

| Outline letter | Descriptive designator | <u>Terminals</u> | Package style                   |

|----------------|------------------------|------------------|---------------------------------|

| Т              | See figure 1           | 72               | Quad flat package with tie bars |

| U              | See figure 1           | 81               | Pin grid array                  |

| X              | See figure 1           | 70               | Dual-in-line                    |

| Ÿ              | See figure 1           | 70               | Flat package                    |

| Z              | See figure 1           | 70               | Dual-in-line, J-lead            |

1.2.5 <u>Lead finish</u>. The lead finish shall be as specified in MIL-PRF-38534.

#### 1.3 Absolute maximum ratings. 1/

| Positive supply voltage range (+5VA, +5VB)                            | -0.3 V dc to +7.0 V dc |

|-----------------------------------------------------------------------|------------------------|

| Negative supply voltage range (-VA, -VB)                              | +0.3 V dc to -18 V dc  |

| Logic supply voltage range (+5 V logic)                               | -0.3 V dc to +6.0 V dc |

| Power dissipation (P <sub>D</sub> ): <u>2</u> / <u>3</u> / <u>4</u> / |                        |

| Device types 01, 03, 05, 07, 17, and 19                               | 2.23 W                 |

| Device types 02, 04, 06, 08, 18, and 20                               | 2.16 W                 |

| Device types 09 through 16 and 21 through 24                          | 2.85 W                 |

| Device types 25 and 26                                                | 1.97 W                 |

| Storage temperature range                                             | -65°C to +150°C        |

| Lead temperature (soldering, 10 seconds)                              | +300°C                 |

| Thermal resistance, junction to case $(\theta_{JC})$                  | 6.99°C/W <u>3</u> /    |

|                                                                       |                        |

## 1.4 Recommended operating conditions.

| Positive supply voltage range (+5VA, +5VB): Device types 01 through 08 and 17 through 20 | +4.5 V dc to +5.5 V dc     |

|------------------------------------------------------------------------------------------|----------------------------|

| Device types 09 through 16 and 21 through 26                                             | +4.75 V dc to +5.25 V dc   |

| Negative supply voltage range (-VA, -VB):                                                |                            |

| Device types 01, 03, 05, 07, 17, and 19                                                  | -14.25 V dc to -15.75 V dc |

| Device types 02, 04, 06, 08, 18, and 20                                                  | -11.40 V dc to -12.60 V dc |

| Logic supply voltage range (+5V logic)                                                   | +4.5 V dc to +5.5 V dc     |

| Minimum logic high input voltage (VIH)                                                   | 2.0 V dc                   |

| Maximum logic low input voltage (VIL)                                                    | 0.8 V dc                   |

| Operating frequency (FOP)                                                                | 12 MHz or 16 MHz           |

| Case operating temperature range (T <sub>C</sub> )                                       | -55°C to +125°C            |

| •                                                                                        |                            |

<sup>1/</sup> Stresses above the absolute maximum rating may cause permanent damage to the device. Extended operation at the maximum levels may degrade performance and affect reliability.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-93065 |

|----------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43216-5000        |                  | F              | 3          |

DSCC FORM 2234 APR 97

9004708 0039170 726

<sup>2</sup>/ Applies up to  $T_C = +125$ °C.

<sup>3/</sup> Hottest die.

$<sup>\</sup>frac{1}{4}$  Assumes 100 percent transmitter duty cycle on one channel and 0 percent duty cycle on the other channel.

#### 2. APPLICABLE DOCUMENTS

2.1 <u>Government specification, standards, and handbook</u>. The following specification, standards, and handbook form a part of this drawing to the extent specified herein. Unless otherwise specified, the issues of these documents are those listed in the issue of the Department of Defense Index of Specifications and Standards (DoDISS) and supplement thereto, cited in the solitation.

#### **SPECIFICATION**

#### **DEPARTMENT OF DEFENSE**

MIL-PRF-38534 - Hybrid Microcircuits, General Specification for.

#### **STANDARDS**

#### DEPARTMENT OF DEFENSE

MIL-STD-883 - Test Methods and Procedures for Microelectronics.

MIL-STD-973 - Configuration Management.

MIL-STD-1553 - Aircraft Internal Time Division Command/Response Multiplex Data Bus.

MIL-STD-1835 - Microcircuit Case Outlines.

#### **HANDBOOK**

#### **DEPARTMENT OF DEFENSE**

MIL-HDBK-780 - Standard Microcircuit Drawings.

(Unless otherwise indicated, copies of the specification, standards, and handbook are available from the Standardization Document Order Desk, 700 Robbins Avenue, Building 4D, Philadelphia, PA 19111-5094.)

2.2 <u>Order of precedence</u>. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing takes precedence. Nothing in this document, however, supersedes applicable laws and regulations unless a specific exemption has been obtained.

### 3. REQUIREMENTS

- 3.1 Item requirements. The individual item performance requirements for device classes D, E, G, H, and K shall be in accordance with MIL-PRF-38534. Compliance with MIL-PRF-38534 may include the performance of all tests herein or as designated in the device manufacturer's Quality Management (QM) plan or as designated for the applicable device class. Therefore, the tests and inspections herein may not be performed for the applicable device class (see MIL-PRF-38534). Futhermore, the manufacturers may take exceptions or use alternate methods to the tests and inspections herein and not perform them. However, the performance requirements as defined in MIL-PRF-38534 shall be met for the applicable device class.

- 3.2 <u>Design, construction, and physical dimensions</u>. The design, construction, and physical dimensions shall be as specified in MIL-PRF-38534 and herein.

- 3.2.1 Case outline(s). The case outline(s) shall be in accordance with 1.2.4 herein and figure 1.

- 3.2.2 Terminal connections. The terminal connections shall be as specified on figure 2.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                     | 5962-93065 |

|-------------------------------------------------------------|------------------|---------------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL<br>F | SHEET 4    |

DSCC FORM 2234 APR 97

**9004708 0039171 662**

- 3.2.3 Pin functions. The pin functions shall be as specified in table III.

- 3.3 <u>Electrical performance characteristics</u>. Unless otherwise specified herein, the electrical performance characteristics are as specified in table I and shall apply over the full specified operating temperature range.

- 3.4 <u>Electrical test requirements</u>. The electrical test requirements shall be the subgroups specified in table II. The electrical tests for each subgroup are defined in table I.

- 3.5 <u>Marking of Device(s)</u>. Marking of device(s) shall be in accordance with MIL-PRF-38534. The device shall be marked with the PIN listed in 1.2 herein. In addition, the manufacturer's vendor similar PIN may also be marked as listed in QML-38534.

- 3.6 <u>Data</u>. In addition to the general performance requirements of MIL-PRF-38534, the manufacturer of the device described herein shall maintain the electrical test data (variables format) from the initial quality conformance inspection group A lot sample, for each device type listed herein. Also, the data should include a summary of all parameters manually tested, and for those which, if any, are guaranteed. This data shall be maintained under document revision level control by the manufacturer and be made available to the preparing activity (DSCC-VA) upon request.

- 3.7 <u>Certificate of compliance</u>. A certificate of compliance shall be required from a manufacturer in order to supply to this drawing. The certificate of compliance (original copy) submitted to DSCC-VA shall affirm that the manufacturer's product meets the performance requirements of MIL-PRF-38534 and herein.

- 3.8 <u>Certificate of conformance</u>. A certificate of conformance as required in MIL-PRF-38534 shall be provided with each lot of microcircuits delivered to this drawing.

# 4. QUALITY ASSURANCE PROVISIONS

- 4.1 <u>Sampling and inspection</u>. Sampling and inspection procedures shall be in accordance with MIL-PRF-38534 or as modified in the device manufacturer's Quality Management (QM) plan. The modification in the QM plan shall not affect the form, fit, or function as described herein.

- 4.2 Screening. Screening shall be in accordance with MIL-PRF-38534. The following additional criteria shall apply:

- a. Burn-in test, method 1015 of MIL-STD-883.

- (1) Test condition A, B, C, or D. The test circuit shall be maintained by the manufacturer under document revision level control and shall be made available to either DSCC-VA or the acquiring activity upon request. Also, the test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in test method 1015 of MIL-STD-883.

- (2) TA as specified in accordance with table I of method 1015 of MIL-STD-883.

- b. Interim and final electrical test parameters shall be as specified in table II herein, except interim electrical parameter tests prior to bum-in are optional at the discretion of the manufacturer.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-93065 |

|----------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43216-5000        |                  | F              | 5          |

DSCC FORM 2234 APR 97

9004708 0039172 519

| Test                                                                                | Symbol           | Conditions<br>-55°C ≤ T <sub>C</sub> ≤ +125°C                        | Group A subgroups | Device<br>type        | Lir        | nits | Unit     |

|-------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------|-------------------|-----------------------|------------|------|----------|

|                                                                                     |                  | unless otherwise specified                                           |                   |                       | Min        | Max  |          |

| +5 volt supply current,                                                             | ICC1             | +5V logic = +5.5 V, +5VA =                                           | 1, 2, 3           | 01-08                 | 5          | 190  | _ mA     |

| idle <u>1</u> /                                                                     |                  | +5VB = +5.5 V                                                        |                   | 09-16,<br>25, 26      | 5          | 200  |          |

|                                                                                     |                  |                                                                      |                   | 17-20 5 250           | 250        | _    |          |

|                                                                                     |                  |                                                                      |                   | 21-24                 | 5          | 260  |          |

| +5 volt supply current,                                                             | I <sub>CC2</sub> |                                                                      | 1, 2, 3           | 01-08                 | 5          | 190  | mA       |

| channel A = 25% duty<br>cycle, channel B =<br>idle $\underline{1}$ /                |                  |                                                                      |                   | 09-16,<br>25, 26      | 5          | 350  |          |

|                                                                                     |                  | :                                                                    |                   | 17-20                 | 5          | 250  | _        |

|                                                                                     |                  |                                                                      |                   | 21-24                 | 5          | 398  |          |

| +5 volt supply current,                                                             | ССЗ              |                                                                      | 1, 2, 3           | 01-08                 | 5          | 190  | _ mA     |

| channel A = idle,<br>channel B = 25% duty<br>cycle <u>1</u> /                       |                  |                                                                      |                   | 09-16,<br>25, 26      | 5          | 350  | _        |

|                                                                                     |                  |                                                                      |                   | 17-20                 | 5          | 250  | _        |

|                                                                                     |                  |                                                                      |                   | 21-24                 | 5          | 398  |          |

| Negative supply 2/<br>current                                                       | lEE1             | -V <sub>A</sub> = -12 V for device types 02, 04, 06, 08, 18, and 20. | 1, 2, 3           | 01-08,<br>17-20       | 5          | 60   | mA       |

| Negative supply current, channel A = 25% duty                                       | I <sub>EE2</sub> | -V <sub>A</sub> = -15 V for device types 01, 03, 05, 07, 17, and 19. | 1, 2, 3           | 01,03,05,<br>07,17,19 | 25         | 108  | mA       |

| cycle, channel B = idle 2/                                                          |                  | -                                                                    |                   | 02,04,06,<br>08,18,20 | 25         | 120  |          |

| Negative supply current,<br>channel B = 25% duty                                    | IEE3             |                                                                      | 1, 2, 3           | 01,03,05,<br>07,17,19 | 25         | 108  | mA       |

| cycle, channel A = idle 2/                                                          |                  |                                                                      |                   | 02,04,06,<br>08,18,20 | 25         | 120  |          |

| Low level input 3/                                                                  | liL1             | +5V logic = +5.5 V, +5VA =<br>+5VB = +5.5 V, V <sub>IN</sub> = 0 V   | 1, 2, 3           | All                   | -397       | -50  | μΑ       |

| Low level input 4/                                                                  | l <sub>IL2</sub> |                                                                      |                   |                       | -794       | -100 |          |

| See footnotes at end of ta                                                          | adie.            |                                                                      |                   |                       |            |      |          |

|                                                                                     | STANDAR          |                                                                      | SIZE<br><b>A</b>  |                       |            | 59   | 962-9306 |

| MICROCIRCUIT DRAWING<br>DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  |                                                                      |                   | REVISION              | LEVEL<br>F | SHE  | ET<br>6  |

| Test                                            | Symbol           | Conditions<br>-55°C ≤ T <sub>C</sub> ≤ +125°C                             | Group A subgroups | Device<br>type | Lin  | Unit |    |

|-------------------------------------------------|------------------|---------------------------------------------------------------------------|-------------------|----------------|------|------|----|

|                                                 |                  | unless otherwise specified                                                | oung.cupo         | ,,,,,          | Min  | Max  | •  |

| High level input 3/                             | liH1             | +5V logic = +5.5 V, +5VA =<br>+5VB = +5.5 V, V <sub>IN</sub> = 2.4 V      | 1, 2, 3           | All            | -346 | -42  | μА |

| High level input <u>4</u> /<br>current          | l <sub>IH2</sub> |                                                                           |                   |                | -692 | -84  |    |

| Output voltage low 5/                           | VOL1             | +5V logic = +5.5 V, +5VA =<br>+5VB = +5.5 V, I <sub>OL</sub> = -6.4 mA    | 1, 2, 3           | All            |      | 0.4  | V  |

| Output voltage low <u>6</u> /                   | V <sub>OL2</sub> | +5V logic = +5.5 V, +5VA =<br>+5VB = +5.5 V,<br>I <sub>OL</sub> = -3.2 mA | 1, 2, 3           | All            |      | 0.4  | V  |

| Output voltage high <u>5</u> /                  | VOH1             | +5V logic = +5.5 V, +5VA =<br>+5VB = +5.5 V, I <sub>OH</sub> = 6.4 mA     | 1, 2, 3           | All            | 2.4  |      | V  |

| Output voltage high <u>6</u> /                  | V <sub>OH2</sub> | +5V logic = +5.5 V, +5VA =<br>+5VB = +5.5 V,<br>I <sub>OH</sub> = 3.2 mA  | 1, 2, 3           | All            | 2.4  |      | V  |

| IOEN low pulse width<br>(memory read)           | t <sub>PW1</sub> | +5V logic = +5.5 V, +5VA =<br>+5VB = +5.5 V                               | 9, 10, 11         | All            | 475  | 625  | ns |

| READYD low pulse width (memory read)            | tPW2             |                                                                           |                   |                | 225  | 375  | ns |

| MEMOE low pulse width (memory read)             | tPW3             |                                                                           |                   |                | 350  | 500  | ns |

| MEMWR low pulse width (memory write)            | <sup>t</sup> PW4 |                                                                           |                   |                | 37   | 87   | ns |

| MEMENA-OUT low<br>pulse width<br>(memory read)  | tPW5             |                                                                           |                   |                | 412  | 562  | ns |

| MEMENA-OUT low<br>pulse width<br>(memory write) | tPW6             |                                                                           |                   |                | 435  | 695  | ns |

| INCMD low pulse width (receive command)         | t <sub>PW7</sub> |                                                                           |                   |                | 45.5 | 47.5 | μs |

| INCMD low pulse width (transmit command)        | tPW8             |                                                                           |                   |                | 45.5 | 47.5 | μs |

| INT low pulse width                             | t <sub>PW9</sub> |                                                                           |                   |                | 450  | 550  | ns |

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-93065 |

|----------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43216-5000        |                  | F              | 7          |

9004708 0039174 371

|                                            | T#             | ABLE I. <u>Electrical performance</u>                                                                    | characteristics | <u>i</u> - Continued | J    |      |               |

|--------------------------------------------|----------------|----------------------------------------------------------------------------------------------------------|-----------------|----------------------|------|------|---------------|

| Test                                       | Symbol         | -55°C ≤ T <sub>C</sub> ≤ +125°C                                                                          |                 | Device<br>type       | Lin  | nits | Unit          |

|                                            |                | unless otherwise specified                                                                               |                 |                      | Min  | Мах  |               |

| DTREQ low pulse width                      | tPW10          | +5V logic = +5.5 V, +5VA =<br>+5VB = +5.5 V                                                              | 9, 10, 11       | All                  | 2.07 | 2.19 | μs            |

| DTACK low pulse width                      | tPW11          |                                                                                                          |                 |                      | 2.0  | 2.23 | μs            |

| Functional tests                           |                | +5V logic = +5.5 V, +5VA =<br>+5VB = +5.5 V, see 4.3.1b                                                  | 7, 8            | All                  |      |      | Pass/<br>fail |

| Receiver threshold                         | VTH            | +5V logic = +5.5 V, +5VA =<br>+5VB = +5.5 V, transformer<br>coupled into a 70 $\Omega$<br>resistive load | 4, 5, 6         | All                  | 500  | 700  | mVp-p         |

| Transmitter differential output voltage 7/ | VO             | +5V logic = +5.5 V, +5VA =<br>+5VB = +5.5 V, transformer<br>coupled into a 70 Ω<br>resistive load        | 4, 5, 6         | All                  | 18   | 27   | Vp-p          |

| Transmitter output rise time               | t <sub>R</sub> |                                                                                                          |                 | Ali                  | 100  | 300  | ns            |

| Transmitter output fall time               | tĘ             | _                                                                                                        |                 | All                  | 100  | 300  | ns            |

| Transmitter output 8/ offset voltage       | vos            |                                                                                                          |                 | Ali                  | -250 | +250 | mVp-p         |

- 1/ Measured at the following pins: Case outline T: pins 20, 37, and 72. Case outline U: pins A9, D3, and J3. Case outlines X, Y, and Z: pins 38, 54, and 68.

- 2/ Measured at the following pins: Case outlines X, Y, and Z: pins 36 and 70.

- Measured at the following pins: Device types 01 08, 10, 12, 14, 16 20, 22, and 24: pins 3-17, 19-26, 29-33, 39-44, 46-53, and 55-64. Device types 09, 11, 13, 15, 21, and 23: pins 3-17, 19-26, 29-33, 36, 39-44, 46-53, 55-64, and 70. Device types 25 and 26, case outline T: pins 1-4, 6, 8-12, 14, 15, 21-24, 27-31, 33-36, 38-55, 59-64, 66, and 68-71. Device types 25 and 26, case outline U: pins A1, A2, A5, A6, B1-B5, B7, B9, C2-C7, C9, D2, D7-D9, E1-E3, E7-E9, F1-F3, F7-F9, G2-G9, H5-H9, J1, J2, J4-J7, and J9.

- 4/ Measured at the following pin. Case outline T: pin 32. Case outline U: pin H2. Case outlines X, Y, and Z: pin 27.

- 5/ Measured at the following pins: Case outline T: pins 3, 4, 6, 8-12, 14, 15, 22-24, 27, 29, 36, 38, 39, 42-54, 66, and 68-71. Case outline U: pins A1, A2, B1-B3, B9, C2-C5, D2, D7-D9, E1-E3, E7-E9, F1-F3, F7-F9, G2-G6, H5, H9, J1, J2, and J4, J6. Case outlines X, Y, and Z: pins 8-17, 20-25, 29-32, 46-53, and 55-62.

- 6/ Measured at the following pins: Case outline T: pins 56, 57, and 58. Case outline U: pins A3, B8, and C8. Case outline X, Y, and Z: pins 28, 45, and 65-67.

- 7/ For device types 01, 03, 05, 17, 19:

- In case outline X, the limits are 20 Vp-p minimum and 27 Vp-p maximum.

- In case outlines Y and Z, the limits are 18 Vp-p minimum and 27 Vp-p maximum.

- 8/ Parameter shall be tested as part of the initial characterization of these devices and after design and process changes. Parameter shall be guaranteed to the limits specified in table I for all lots not specifically tested.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                     | 5962-93065 |

|-------------------------------------------------------------|------------------|---------------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL<br>F | SHEET 8    |

9004708 0039175 208

9004708 0039176 144

#### Case outline T - Continued.

| Symbol | Millin  | neter   | Inc     | hes     |

|--------|---------|---------|---------|---------|

|        | Minimum | Maximum | Minimum | Maximum |

| А      |         | 3.94    | •••     | 0.155   |

| A1     | 2.03    | 2.54    | 0.080   | 0.100   |

| A2     | 1.14    | 1.40    | 0.045   | 0.055   |

| А3     | 0.76    | 1.02    | 0.030   | 0.040   |

| b      | 0.41    | 0.51    | 0.016   | 0.020   |

| С      | 0.20    | 0.30    | 0.008   | 0.012   |

| e      | 1.14    | 1.40    | 0.045   | 0.055   |

| e1     | 18.35   | 25.40   | 0.842   | 0.858   |

| D/E    | 50.42   | 51.18   | 1.985   | 2.015   |

| D1/E1  | 25.15   | 25.65   | 0.990   | 1.010   |

| D2/E2  | 12.19   | 13.21   | 0.480   | 0.520   |

| D3/E3  | 4.95    | 5.21    | 0.195   | 0.205   |

# NOTES:

- 1. There are eight test pads located on the bottom of the package. Each pad measures 0.100 inch (2.54 mm) in diameter. These pads are recessed so as to not interfere when mounting the package.

- 2. The U.S. government preferred system of measurement is the metric SI. This case outline was designed using inchpound units of measurement. In case of problems involving conflicts between the metric and inch-pound units, the inch-pound units shall rule.

- 3. Package material is Alumina (AL<sub>2</sub>O<sub>3</sub>).

FIGURE 1. Case outline(s) - Continued.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-93065 |

|----------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43216-5000        |                  | F              | 10         |

DSCC FORM 2234 APR 97

9004708 0039177 080

| Symbol | Millin  | neter   | Inc     | ches    |

|--------|---------|---------|---------|---------|

|        | Minimum | Maximum | Minimum | Maximum |

| Α      |         | 3.94    |         | 0.155   |

| В      | 1.61    | 1.91    | 0.065   | 0.075   |

| øb     | 0.41    | 0.51    | 0.016   | 0.020   |

| øb2    | 1.61    | 1.91    | 0.065   | 0.075   |

| D/E    | 25.15   | 25.65   | 0.990   | 1.010   |

| D1/E1  | 20.19   | 20.48   | 0.795   | 0.805   |

| е      | 2.41    | 2.67    | 0.095   | 0.105   |

| L      | 4.37    | 4.78    | 0.172   | 0.188   |

### NOTES:

- 1. The U.S. government preferred system of measurement is the metric SI. This case outline was designed using inchpound units of measurement. In case of problems involving conflicts between the metric and inch-pound units, the inch-pound units shall rule.

- 2. Package material is Alumina (AL<sub>2</sub>O<sub>3</sub>).

FIGURE 1. Case outline(s) - Continued.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-93065 |

|----------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43216-5000        |                  | F              | 11         |

DSCC FORM 2234 APR 97

**■ 9004708 0039178 T17 ■**

9004708 0039179 953

Case outline X - Continued.

| Symbol | Millin  | neter   | lno     | ches    |

|--------|---------|---------|---------|---------|

|        | Minimum | Maximum | Minimum | Maximum |

| Α      |         | 5.46    |         | 0.215   |

| ⊘b     | 0.406   | 0.508   | 0.016   | 0.020   |

| b2     | 1.65    | 1.91    | 0.065   | 0.075   |

| D      |         | 48.26   |         | 1.900   |

| е      | 2.41    | 2.67    | 0.095   | 0.105   |

| eA     | 10.03   | 10.29   | 0.395   | 0.405   |

| e1     | 43.05   | 43.31   | 1.695   | 1.705   |

| e2     | 1.14    | 1.40    | 0.045   | 0.055   |

| e3     | 15.11   | 15.37   | 0.595   | 0.605   |

| E      |         | 25.40   |         | 1.000   |

| L      | 4.32    | 4.83    | 0.170   | 0.190   |

# NOTES:

- The U.S. government preferred system of measurement is the metric SI. This case outline was designed using inchpound units of measurement. In case of problems involving conflicts between the metric and inch-pound units, the inch-pound units shall rule.

- 2. Pin numbers are for reference only.

FIGURE 1. Case outline(s) - Continued.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-93065 |

|----------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43216-5000        |                  | F              | 13         |

DSCC FORM 2234 APR 97

9004708 0039180 675

**9004708 0039181 501**

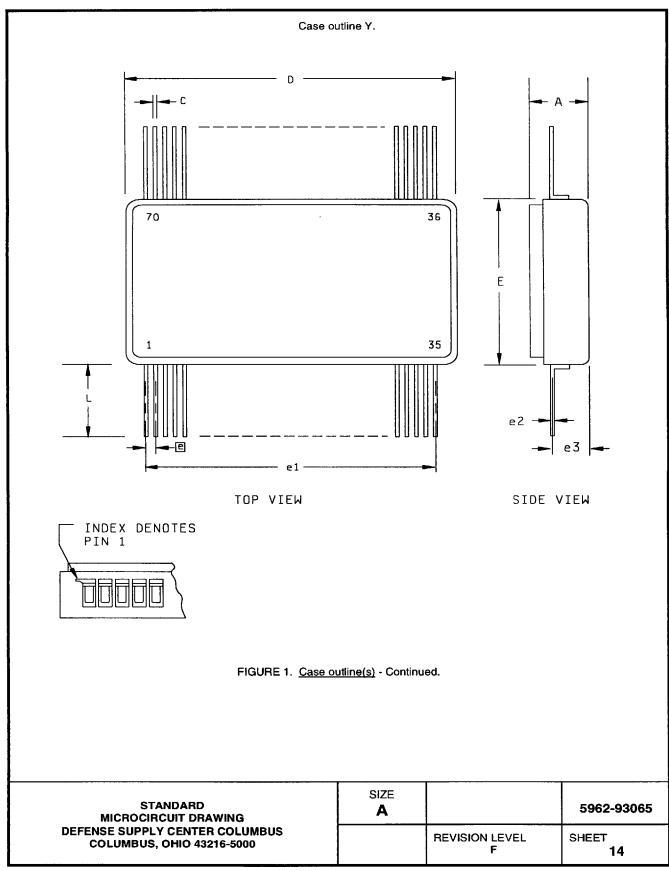

## Case outline Y - Continued.

| Symbol | Millimeter |         | Inc     | hes     |

|--------|------------|---------|---------|---------|

|        | Minimum    | Maximum | Minimum | Maximum |

| А      |            | 5.46    |         | 0.215   |

| С      | 0.330      | 0.432   | 0.013   | 0.017   |

| D      |            | 48.26   |         | 1.900   |

| е      | 1.14       | 1.40    | 0.045   | 0.055   |

| e1     | 43.05      | 43.31   | 1.695   | 1.705   |

| e2     | 0.20       | 0.30    | 0.008   | 0.012   |

| e3     | 1.52       | 2.03    | 0.060   | 0.080   |

| E      |            | 25.40   |         | 1.000   |

| L      | 10.16      |         | 0.400   | •••     |

#### NOTES:

- The U.S. government preferred system of measurement is the metric SI. This case outline was designed using inchpound units of measurement. In case of problems involving conflicts between the metric and inch-pound units, the inch-pound units shall rule.

- 2. Pin numbers are for reference only.

FIGURE 1. Case outlines - Continued.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                     | 5962-93065      |

|-------------------------------------------------------------|------------------|---------------------|-----------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL<br>F | SHEET <b>15</b> |

DSCC FORM 2234 APR 97

9004708 0039182 448

9004708 0039183 384

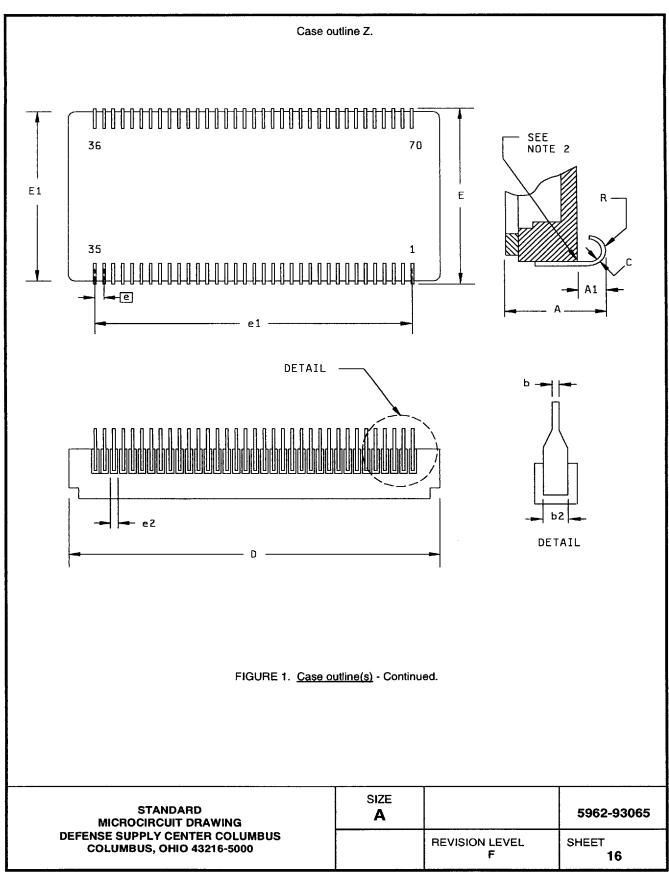

## Case outline Z - Continued.

| Symbol | Millir  | neter   | Inc       | hes     |

|--------|---------|---------|-----------|---------|

|        | Minimum | Maximum | Minimum   | Maximum |

| А      | 6.05    | 7.06    | 0.238     | 0.278   |

| A1     | 1.52    | 1.93    | 0.060     | 0.076   |

| b      | 0.38    | 0.48    | 0.015     | 0.019   |

| b2     | 0.58    | 0.69    | 0.023     | 0.027   |

| С      | 0.15    | 0.25    | 0.006     | 0.010   |

| D      |         | 48.26   |           | 1.900   |

| е      | 1.27    | BSC     | 0.050 BSC |         |

| e1     | 43.05   | 43.31   | 1.695     | 1.705   |

| e2     | 0.84    | 1.09    | 0.033     | 0.043   |

| E      |         | 25.98   |           | 1.023   |

| E1     |         | 25.40   |           | 1.000   |

| R      | 0.635   | 0.889   | 0.025     | 0.035   |

## NOTES:

- The U.S. government preferred system of measurement is the metric SI. This case outline was designed using

inch-pound units of measurement. In case of problems involving conflicts between the metric and inch-pound

units, the inch-pound units shall rule.

- 2. Braze fillet shall be concave and is .020 ±.005 inches, (.508 ±.127 mm) at an angle of 45 degrees.

- 3. Pin numbers are for reference only.

FIGURE 1. Case outline(s) - Continued.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                     | 5962-93065      |

|-------------------------------------------------------------|------------------|---------------------|-----------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL<br>F | SHEET <b>17</b> |

DSCC FORM 2234

9004708 0039184 210

| Device types    | 25 and 26             |                 |                      |  |  |  |  |

|-----------------|-----------------------|-----------------|----------------------|--|--|--|--|

| Case outline    | Т                     |                 |                      |  |  |  |  |

| Terminal number | Terminal symbol       | Terminal number | Terminal symbol      |  |  |  |  |

| 4               | MEM/REG               | 37              | +5 V LOGIC           |  |  |  |  |

| 1               | I MSTCLR              | 38              | D01                  |  |  |  |  |

| 2<br>3          | I A11                 | 39              | D04                  |  |  |  |  |

|                 |                       |                 | ,                    |  |  |  |  |

| 4               | A10                   | 40              | RTADP                |  |  |  |  |

| 5               | TX/RX-A               | 41              | RTADI                |  |  |  |  |

| 6               | A08                   | 42              | D00                  |  |  |  |  |

| 7               | TX/RX-A               | 43              | D02                  |  |  |  |  |

| 8               | A14                   | 44              | D03                  |  |  |  |  |

| 9               | A04                   | 45              | D05                  |  |  |  |  |

| 10              | A03                   | 46              | D08                  |  |  |  |  |

| 11              | A07                   | 47              | D07                  |  |  |  |  |

| 12              | A02                   | 48              | D13                  |  |  |  |  |

| 13              | TX/RX-B               | 49              | D12                  |  |  |  |  |

| 14              | MEMOE/ADDR_LAT        | 50              | D14                  |  |  |  |  |

| 15              | A00                   | 51              | D09                  |  |  |  |  |

| 16              | TX/RX-B               | 52              | D11                  |  |  |  |  |

| . 17            | LOGIC GND             | 52              | D15                  |  |  |  |  |

| 18              | LOGIC GND             | 54              | D10                  |  |  |  |  |

| _               |                       | 55              |                      |  |  |  |  |

| 19              | LOGIC GND             |                 | TRANSPARENT/BUFFERED |  |  |  |  |

| 20              | +5 V LOGIC            | 56              | READYD               |  |  |  |  |

| 21              | RTAD2                 | 57              | INT                  |  |  |  |  |

| 22              | <u>A06</u>            | 58              | IOEN                 |  |  |  |  |

| 23              | MEMWR/ZERO_WAIT       | 59              | TX_INH_A             |  |  |  |  |

|                 |                       | 60              | TX_INH_B             |  |  |  |  |

| 24              | DTREQ/16/8            |                 |                      |  |  |  |  |

| 25              | Test output (RX_B)    | 61              | SELECT               |  |  |  |  |

|                 |                       | 62              | STR <u>BD</u>        |  |  |  |  |

| 26              | Test output (RX_B)    | 63              | RD/WR                |  |  |  |  |

| 27              | A01                   | 64              | DTGRT/MSB/LSB        |  |  |  |  |

| 28              | MENENA_IN/TRIGGER_SEL | 65              | Test output (RX-A)   |  |  |  |  |

| 29              | DTACK/POLARITY_SEL    | 66              | A15                  |  |  |  |  |

| 30              | CLOCK_IN              | 67              | Test output (RX-A)   |  |  |  |  |

| 31              | RT_AD_LAT             | 68              | A05                  |  |  |  |  |

| 31              | W_00_E0               | 69              | A09                  |  |  |  |  |

| 20              | SSELAC/EXT TRIC       |                 |                      |  |  |  |  |

| 32              | SSFLAG/EXT_TRIG       | 70              | A12                  |  |  |  |  |

| 33              | RTAD0                 | 71              | A13                  |  |  |  |  |

| 34              | TRAD3                 | 72              | +5 V LOGIC           |  |  |  |  |

| 35              | RTAD4                 | 1               |                      |  |  |  |  |

| 36              | D06                   | ł               | Į.                   |  |  |  |  |

FIGURE 2. Terminal connections.

| STANDARD<br>MICROCIRCUIT DRAWING<br>DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 | SIZE<br><b>A</b> |                     | 5962-93065  |

|-------------------------------------------------------------------------------------------------|------------------|---------------------|-------------|

|                                                                                                 |                  | REVISION LEVEL<br>F | SHEET<br>18 |

| Device types    |                                              | 25 and 26       |                                                          |

|-----------------|----------------------------------------------|-----------------|----------------------------------------------------------|

| Case outline    |                                              | υ               |                                                          |

| Terminal number | Terminal symbol                              | Terminal number | Terminal symbol                                          |

| A1              | D10                                          | E6              | Test output (AB Tstck)                                   |

| A2              | D11                                          | E7              | D08                                                      |

| A3              | IOEN                                         | E8              | D06                                                      |

| A4              | Test output (RX-A)                           | E9              | D07                                                      |

| A5              | RD/WR                                        | F1              | A06                                                      |

| A6              | STRBD                                        | F2              | A03                                                      |

| A7              | LOGIC GND                                    | F3              | A02                                                      |

| A8              | LOGIC GND                                    | F4              | Test output(AB_Test2)                                    |

| A9              | +5 V LOGIC                                   | F5              | Test output(AB_Test3)                                    |

| B1              | A13                                          | F6              | Test output(B_Test1)                                     |

| B2              | D12                                          | F7              | D03                                                      |

| B3              | A12                                          | F8              | D01                                                      |

| B4              | MEM/REG                                      | F9              | D02                                                      |

| B5              | MSTCLR                                       | ĞĬ              | TX/RX-B                                                  |

| B6              | Test output (RX-A)                           | G2              | A01                                                      |

| B7              | TX INH A                                     | G3              | AOO                                                      |

| J 7             | 17_1111_7                                    | G4              | MEMOE/ADDR_LAT                                           |

| В8              | READYD                                       | G5              | D05                                                      |

| B9              | D09                                          | G6              | D03                                                      |

| C1              | TX/RX-A                                      | G7              | RT_AD_LAT                                                |

| C2              | A11                                          | G8              | RTAD3                                                    |

| C3              | A10                                          | G9              | RTADE                                                    |

| C4              | A14                                          | Hi              | TX/RX-B                                                  |

| C5              | A15                                          | H2              | SSFLAG/EXT TRIG                                          |

| C5              | Alb                                          | H3              | Test output (RX-B)                                       |

| C6              | SELECT                                       | H4              | Test output ( <u>I-X-B</u> ) Test output (R <u>X</u> -B) |

| C7              |                                              | H5              | DTREQ/16//8                                              |

| 67              | TX_INH_B                                     | H6              | CLOCK IN                                                 |

| C8              | 1NT                                          | H7              | RTAD0                                                    |

| C9              | TRANPARENT/BUFFERED                          | H8              | RTAD4                                                    |

| D1              | TX/RX-A                                      | H9              | D00                                                      |

| D2              | A08                                          | J1              | DOU<br>DTGRT/MSB/LSB                                     |

| D3              | +5 V LOGIC                                   | J2              | MEMWR/ZERO WAIT                                          |

| D3<br>D4        |                                              | J3              | +5 V LOGIC                                               |

| D5              | Test output (A_RExt)                         | J4              | 43 V EOGIC<br>A09                                        |

| D6              | Test output (A_Test1) Test output (AB_Test4) | J5              | MEMNA IN/TRIGGER SEL                                     |

| D7              | D13                                          | J6              | DTACK/POLARITY_SEL                                       |

| D8              | D15                                          | J7              | RTAD2                                                    |

| D9              | D13                                          | J8              | LOGIC GND                                                |

| E1              | A07                                          | J9              | RTAD1                                                    |

|                 |                                              | 79              | I INADI                                                  |

| E2              | A05                                          |                 |                                                          |

| E3              | A04                                          |                 |                                                          |

| E4              | Test output(B_RExt)                          |                 |                                                          |

| E5              | No connect                                   |                 |                                                          |

FIGURE 2. <u>Ternimal connections</u>- Continued.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                  | 5962-93065  |

|-------------------------------------------------------------|------------------|------------------|-------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL F | SHEET<br>19 |

9004708 0039186 093 📟

| Device<br>types                                                                            | 01 through 24                                                                                                                                                                                                                                                            |                                                                                                                                                                            |                                                                                                                                                                                                        |  |  |  |

|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Case<br>outlines                                                                           | X, Y, and Z                                                                                                                                                                                                                                                              |                                                                                                                                                                            |                                                                                                                                                                                                        |  |  |  |

| Terminal number                                                                            | Terminal symbol                                                                                                                                                                                                                                                          | Terminal number                                                                                                                                                            | Terminal symbol                                                                                                                                                                                        |  |  |  |

| 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 6 17 18 19 20 1 22 22 24 25 26 27 28 29 30 31 32 33 34 | TX/RX-A TX/RX-A SELECT STRBD MEM/REG RD/WR MSTCLR A15 A14 A13 A12 A11 A10 A09 A08 A07 A06 LOGIC GND CLOCK_IN A05 A04 A03 A02 A01 A00 DTGRT/MSB/LSB SSFLAG/EXT_TRIG MEMENA_OUT MEMOE/ADDR_LAT MEMWR/ZERO_WAIT DTREQ/16/8 DTACK/POLARITY_SEL MEMENA_IN/TRIGGER_SEL TX/RX-B | 36<br>37<br>38<br>39<br>40<br>41<br>42<br>43<br>44<br>45<br>46<br>47<br>48<br>49<br>51<br>52<br>53<br>54<br>55<br>56<br>61<br>62<br>63<br>64<br>65<br>66<br>67<br>68<br>69 | -VB (see note 1) GNDB +5VB RTAD0 RTAD1 RTAD2 RTAD3 RTAD4 RTADP INCMD D00 D01 D02 D03 D04 D05 D06 D07 +5 V LOGIC D08 D09 D10 D11 D12 D13 D14 D15 TAG_CLK TRANSPARENT/BUFFERED INT READYD IOEN +5VA GNDA |  |  |  |

# NOTE:

1. For device types 01, 03, 05, 07, 17, and 19; pin 36 and pin 70 are -15 V.

For device types 02, 04, 06, 08, 18, and 20; pin 36 and pin 70 are -12 V.

For device types 09, 11, 13, 15, 21, and 23; pin 36 and pin 70 are no connects.

For device types 10, 12, 14, 16, 22, and 24: pin 36 and pin 70 are TX\_INH\_B and TX\_INH\_A, respectively.

FIGURE 2. Terminal connections - Continued.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                     | 5962-93065 |

|-------------------------------------------------------------|------------------|---------------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL<br>F | SHEET 20   |

DSCC FORM 2234 APR 97

🖿 9004708 0039187 T2T 🚾

#### TABLE II. Electrical test requirements.

| MIL-PRF-38534 test requirements                                            | Subgroups<br>(in accordance with<br>MIL-PRF-38534, group<br>A test table) |

|----------------------------------------------------------------------------|---------------------------------------------------------------------------|

| Interim electrical parameters                                              | 1,2,3,4,5,6,7,8,9,10,11                                                   |

| Final electrical parameters                                                | 1*,2,3,4,5,6,7,8,9,10,11                                                  |

| Group A test requirements                                                  | 1,2,3,4,5,6,7,8,9,10,11                                                   |

| Group C end-point electrical parameters                                    | 1,2,3,4,5,6,7,8,9,10,11                                                   |

| MIL-STD-883, group E end-point<br>electrical parameters for RHA<br>devices | Subgroups**<br>(in accordance with<br>method 5005, group A<br>test table) |

- \* PDA applies to subgroup 1.

- \*\* When applicable to this standard microcircuit drawing, the subgroups shall be defined.

- 4.3 <u>Conformance and periodic inspections</u>. Conformance inspection (CI) and periodic inspection (PI) shall be in accordance with MIL-PRF-38534 and as specified herein.

- 4.3.1 Group A inspection (CI). Group A inspection shall be in accordance with MIL-PRF-38534 and as follows:

- a. Tests shall be as specified in table II herein.

- b. Subgroups 7 and 8 shall consist of verifying the functionality of the device. It forms a part of the vendors test tape and shall be maintained and available from the aprroved source of supply.

- 4.3.2 Group B inspection (PI). Group B inspection shall be in accordance with MIL-PRF-38534.

- 4.3.3 Group C inspection (PI). Group C inspection shall be in accordance with MIL-PRF-38534 and as follows:

- a. End-point electrical parameters shall be as specified in table II herein.

- b. Steady-state life test, method 1005 of MIL-STD-883.

- (1) Test condition A, B, C, or D. The test circuit shall be maintained by the manufacturer under document revision level control and shall be made available to either DSCC-VA or the acquiring activity upon request. Also, the test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in test method 1005 of MIL-STD-883.

- (2) TA as specified in accordance with table I of method 1005 of MIL-STD-883.

- (3) Test duration: 1,000 hours, except as permitted by method 1005 of MIL-STD-883.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                  | 5962-93065      |

|-------------------------------------------------------------|------------------|------------------|-----------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL F | SHEET <b>21</b> |

DSCC FORM 2234 APR 97

9004708 0039188 966

- 4.3.4 Group D inspection (PI). Group D inspection shall be in accordance with MIL-PRF-38534.

- 4.3.5 <u>Group E inspection</u>. Group E inspection is required only for parts intended to be marked as radiation hardness assured (see 3.5 herein). RHA levels shall be M, D, R, and H. RHA quality conformance inspection sample tests shall be performed at the RHA level specified in the acquisition document.

- a. RHA tests for levels M, D, R, and H shall be performed through each level to determine at what levels the devices meet the RHA requirements. These RHA tests shall be performed for initial qualification and after design or process changes which may affect the RHA performance of the device.

- b. End-point electrical parameters shall be as specified in table II herein.

- c. Prior to total dose irradiation, each selected sample shall be assembled in its qualified package. It shall pass the specified group A electrical parameters in table I for subgroups specified in table II herein.

- d. The devices shall be subjected to radiation hardness assured tests as specified in MIL-PRF-38534 for RHA level being tested, and meet the postirradiation end-point electrical parameter limits as defined in table I at T<sub>A</sub> = +25°C ±5 percent, after exposure.

- e. Prior to and during total dose irradiation testing, the devices shall be biased to establish a worst case condition as specified in the radiation exposure circuit.

- f. For device classes H and K, subgroups 1 and 2 in table V, method 5005 of MIL-STD-883 shall be tested as appropriate for device construction.

- g. When specified in the purchase order or contract, a copy of the RHA delta limits shall be supplied.

- 5. PACKAGING

- 5.1 Packaging requirements. The requirements for packaging shall be in accordance with MIL-PRF-38534.

- 6. NOTES

- 6.1 <u>Intended use</u>. Microcircuits conforming to this drawing are intended for use for Government microcircuit applications (original equipment), design applications, and logistics purposes.

- 6.2 <u>Replaceability</u>. Microcircuits covered by this drawing will replace the same generic device covered by a contractor-prepared specification or drawing.

- 6.3 <u>Configuration control of SMD's</u>. All proposed changes to existing SMD's will be coordinated with the users of record for the individual documents. This coordination will be accomplished in accordance with MIL-STD-973 using DD Form 1692, Engineering Change Proposal.

- 6.4 <u>Record of users</u>. Military and industrial users shall inform Defense Supply Center Columbus when a system application requires configuration control and the applicable SMD. DSCC will maintain a record of users and this list will be used for coordination and distribution of changes to the drawings. Users of drawings covering microelectronic devices (FSC 5962) should contact DSCC-VA, telephone (614) 692-7603.

- 6.5 <u>Comments</u>. Comments on this drawing should be directed to DSCC-VA, P. O. Box 3990, Columbus, Ohio 43216-5000, or telephone (614) 692-0512.

- 6.6 <u>Sources of supply</u>. Sources of supply are listed in QML-38534. The vendors listed in QML-38534 have submitted a certificate of compliance (see 3.7 herein) to DSCC-VA and have agreed to this drawing.

STANDARD

MICROCIRCUIT DRAWING

DEFENSE SUPPLY CENTER COLUMBUS

COLUMBUS, OHIO 43216-5000

SIZE

A

5962-93065

REVISION LEVEL

F

22

DSCC FORM 2234 APR 97

9004708 0039189 8T2 **33**

# TABLE III. Pin functions.

| Terminal symbol        | 1/0  | Description                                                                                                                                     |

|------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| D00                    | 1/0_ | Data bus bit 0 (LSB).                                                                                                                           |

| D02                    | 1/0  | Data bus bit 2.                                                                                                                                 |

| D04                    | 1/0  | Data bus bit 4.                                                                                                                                 |

| D06                    | 1/0  | Data bus bit 6.                                                                                                                                 |

| D08                    | 1/0  | Data bus bit 8.                                                                                                                                 |

| D10                    | 1/0  | Data bus bit 10.                                                                                                                                |

| D12                    | 1/0  | Data bus bit 12.                                                                                                                                |