# Triple ALBO PCM Repeater

### **GENERAL DESCRIPTION**

The XR-T5600/T5620 is a bipolar monolithic repeater IC designed for PCM carrier systems operating at 1.544 MBPS (T1), 2 MBPS, or 2.37 MBPS (T148C). it provides all of the active circuits required for one side of a PCM repeater.

#### **FEATURES**

Single 5.1V Power Supply Less than 10ns Sampling Pulse over the Operating Range Triple Matched ALBO Ports 2 MBPS Capability

### **APPLICATIONS**

T1 PCM Repeater

T148C PCM Repeater

European 2 MBPS PCM Repeater

T1C PCM Repeater (requires external preamplifier)

#### **ABSOLUTE MAXIMUM RATINGS**

| Storage Temperature                    | -65°C to +150°C |

|----------------------------------------|-----------------|

| Supply voltage                         | -0.5 to +10V    |

| Supply Voltage Surge (10ms)            | +25V            |

| Input Voltage (except Pin 2, 3, 4, 17) | −0.5 to 7V      |

| Input Voltage (Pin 2, 3, 4, 17)        | -0.5 to +0.5V   |

| Data Output Voltage (Pin 10, 11)       | 20V             |

| Voltage Surge (Pin 5, 6, 10, 11) (10 m | nsec only) 50V  |

#### ORDERING INFORMATION

| Part Number | Package       | <b>Operating Temperature</b> |

|-------------|---------------|------------------------------|

| XR-T5600    | Plastic       | -40°C to 85°C                |

| XR-T5620    | Plastic or Ce | ramic -40°C to 85°C          |

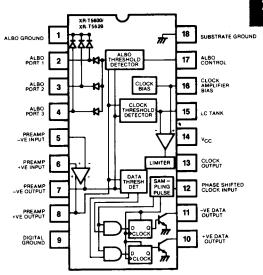

#### PIN ASSIGNMENT

#### SYSTEM DESCRIPTION

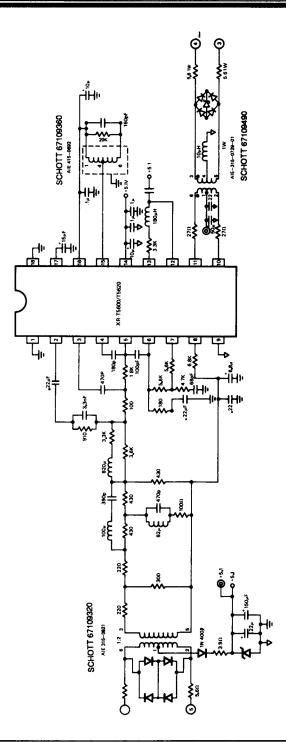

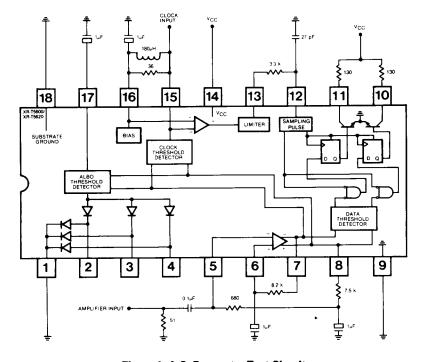

The XR-T5600/T5620 performs most of the functions required for one side of a PCM repeater operating at 2 Mbit/s or similar baud rate. The integrated circuit amplifies the received positive and negative pulses and feeds them into Automatic Line Build Out (ALBO), clock and data threshold detectors, see Figure 1. The ALBO threshold detector ensures that the received pulses at Pins 7 and 8 have the correct amplitude and shape. This is carried out by controlling the gain and frequency shaping of the ALBO network with three variable impedance ALBO ports.

The clock threshold detector extracts timing information from the pulses received at Pins 7 and 8 and passes it into the external tank coil at Pin 15. The sinusoidal-type waveform is amplified into a square wave at Pin 13, and forwarded through an external phase shift network into Pin 12. This waveform provides the data sampling pulse which opens latches into which the data from the data threshold detectors is passed. The resulting pulses are stored for half a bit period (normally 488ns) in the latches. They appear as half-width output pulses at Pins 10 and 11.

# XR-T5600/T5620

## **ELECTRICAL CHARACTERISTICS**

Test Conditions:  $T_A = 25^{\circ}C$ ,  $V_{CC} = 5.1V \pm 5\%$ , unless specified otherwise (see Figure 1).

| PARAMETERS                       | PINS       | MIN.  | TYP. | MAX. | UNIT | CONDITIONS                                      |

|----------------------------------|------------|-------|------|------|------|-------------------------------------------------|

| Supply Current                   | 14         |       | 22   | 30   | mA   |                                                 |

| Data Output Leakage Current      | 10, 11     | Ì     | 0    | 100  | μA   | $V_{pull-up} = 15V, V_{CC} = 5.35V$             |

| ALBO Port Off Voltage            | 2, 3, 4    |       | 0    | 0.1  | ٧    |                                                 |

| Amplifier Pin Voltage            | 5, 6, 7, 8 | 2.4   | 2.9  | 3.4  | ٧    |                                                 |

| Dynamic Characteristics Amplific | or         |       |      |      |      |                                                 |

| Output Offset Voltage            |            | -50   | 0    | 50   | mV   | $R_S = 8.2k\Omega$                              |

| AC Gain @ 1MHz                   |            | 47    | 50   | 53   | ₫B   |                                                 |

| Input Impedance                  |            | 20    |      |      | kΩ   |                                                 |

| Output Impedance                 |            |       |      | 200  | Ω    |                                                 |

| ALBO                             |            |       |      | •    |      |                                                 |

| ALBO Off Impedance               |            | 20    |      | 25   | kΩ   |                                                 |

| ALBO On Impedance                |            |       |      | 25   | Ω    | •                                               |

| Thresholds                       |            |       |      |      |      |                                                 |

| ALBO Threshold                   |            | 1.4   | 1.5  | 1.6  | V    |                                                 |

| Clock Threshold as % of ALBO Thr | eshold     | 68    |      | 80   | %    |                                                 |

| DATA Threshold as % of ALBO The  | reshold    | 42    |      | 49   | %    |                                                 |

| Clock Drive Current              |            | 0.7   |      | 1.4  | mA   | At V <sub>O</sub> = V <sub>ALBO</sub> Threshold |

| Output Stages                    |            |       |      |      |      | $R_L = 130\Omega$ , $V_{pull-up} = 5.1 \pm 5\%$ |

| Output Pulse Rise Time           |            |       |      | 40   | ns   |                                                 |

| Output Pulse Fall Time           |            |       |      | 40   | ns   |                                                 |

| Output Pulse Width               |            | 224   | 244  | 264  | ns   |                                                 |

| Output Pulse Width Differential  |            | -10   |      | +10  | ns   |                                                 |

| Buffer Gate Voltage (Low)        |            | 0.65  |      | 0.95 | V    |                                                 |

| Buffer Gate Voltage Differential |            | -0.15 |      | 0.15 | l v  |                                                 |

### **ELECTRICAL CHARACTERISTICS**

Test Conditions: Unless otherwise stated, all characteristics shall apply over the operating temperature range of  $-40^{\circ}$ C to  $+85^{\circ}$ C with  $V_{CC} = 5.1 \text{V} \pm 5\%$ , all voltages referred to ground = 0V.

| SYMBOL                | PARAMETERS                                                                               | PINS                                  | MIN | TYP                 | MAX                     | UNIT               | CONDITIONS                       |

|-----------------------|------------------------------------------------------------------------------------------|---------------------------------------|-----|---------------------|-------------------------|--------------------|----------------------------------|

| General (i            | Ref. Figure 2)                                                                           |                                       |     |                     |                         |                    |                                  |

| Is<br>I <sub>LD</sub> | Supply Current Data Output Leakage Current Amplifier Pin Voltages ALBO Ports Off Voltage | 14<br>10, 11<br>5, 6, 7, 8<br>2, 3, 4 | 2.4 | 22<br>6<br>2.9<br>0 | 30<br>100<br>3.4<br>0.1 | mΑ<br>μΑ<br>∨<br>∨ | From V <sub>S</sub> (See Note 1) |

**Note:** 1)  $V_S=15V$ ,  $V_{CC}=5.35V$

| Amplifier (Ref. Figure 2, Only Pins 1, 9, 10 | 18 connect | ed) |   |     |            |                                        |

|----------------------------------------------|------------|-----|---|-----|------------|----------------------------------------|

| Input Offset Voltage                         | 5&6        | -10 |   | +10 | m <b>V</b> | R <sub>S</sub> = 8.2kΩ<br>(See Note 1) |

| Input Bias Current                           | 5 & 6      | 0   |   | 5   | μΑ         | R <sub>S</sub> = 8.2kΩ<br>(See Note 1) |

| Input Offset Current                         | 5 & 6      | -1  |   | 1   | μΑ         | R <sub>S</sub> = 8.2kΩ<br>(See Note 1) |

| Output Offset Voltage                        | 7 & 8      | -50 | 0 | 50  | mV         | R <sub>S</sub> = 8.2kΩ<br>(See Note 1) |

| Common Mode Rejection Ratio                  | 7 & 8      | 30  |   |     | dB         | V <sub>CC</sub> ± 10%                  |

| Output Voltage Swing                         | 788        | 2.2 |   |     | V          |                                        |

Note: 1) R<sub>S</sub> = Source Resistance

| Clock Amplifier (Ref. Figure 2, Disc | onnect Pin 15 from Pin | 16) |    |    |                                       |

|--------------------------------------|------------------------|-----|----|----|---------------------------------------|

| Input Offset Voltage                 | 15 & 16                | 0.5 | 6  | mV | R <sub>S</sub> = 10kΩ<br>(See Note 1) |

| Input Bias Current                   | 15 & 16                |     | 10 | μА | T = 25°C (See Note 2)                 |

| Max. Output Voltage                  | 13                     | 0.7 |    | ·v | (See Note 3)                          |

| Min. Output Voltage                  | 13                     | 0.7 |    | ٧  | (See Note 4                           |

| Max./Min. Output Voltage             | Difference —           | 0.7 | 50 | mV | (See Note 5)                          |

Notes:

- 1. R<sub>S</sub> = Source resistance, Pin 15 positive with respect to Pin 16

- 2. Pin 15 = Pin 16 = 3.6V

- 3. Pin 15 = 2.6V, Pin 16 = 3.6V

- 4. Pin 15 = 4.6V, Pin 16 = 3.6V

- 5. Calculation only

# XR-T5600/T5620

| SYMBOL  | PARAMETERS                  | PINS | MIN | TYP | MAX | UNIT | CONDITIONS              |

|---------|-----------------------------|------|-----|-----|-----|------|-------------------------|

| LBO (Re | f. Figure 2)                |      |     |     |     |      | <b></b>                 |

|         | On Current                  | 1    | 3   |     |     | mA   | $V_8 - V_7 = \pm 1.75V$ |

|         | Drive Current               | 17   | 0.4 |     | 1.4 | mA   | $V_8 - V_7 = \pm 1.75V$ |

|         | Resistance Pin 17 to Ground |      | 35  | 50  | 70  | kΩ   | Not Powered             |

#### DYNAMIC CHARACTERISTICS

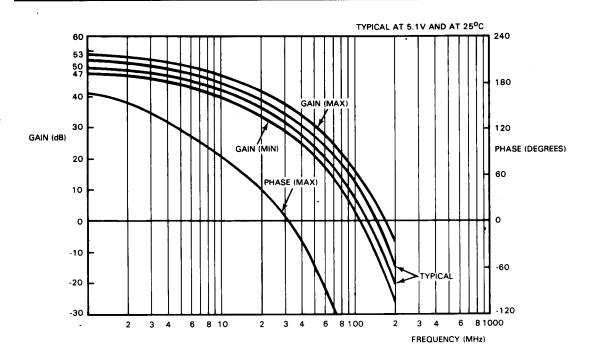

| Amplifier (Ref. Figure 3)                                   |                     |          |    |           |               |                              |

|-------------------------------------------------------------|---------------------|----------|----|-----------|---------------|------------------------------|

| Ao AC Gain @ 1MHz Zin Input Impedance Zout Output Impedance | 5 to 8<br>5<br>7, 8 | 47<br>20 | 50 | 53<br>200 | dB<br>kΩ<br>Ω | (See Note 1)<br>(See Note 2) |

Notes:

1) At 1 MHz, AC ground Pins 7 and 8, disconnect 51Ω resistor, allow for in-circuit R, C

2) At 1MHz, use Figure 2

| lock An                                                    | nplifier (Ref. Figure 3)                      |                                              |               |           |                      |                                                             |

|------------------------------------------------------------|-----------------------------------------------|----------------------------------------------|---------------|-----------|----------------------|-------------------------------------------------------------|

| A <sub>o</sub><br>BW<br>t <sub>d</sub><br>Z <sub>out</sub> | AC Gain -3dB Bandwidth Delay Output Impedance | 15,16 to 13<br>15,16 to 13<br>15 to 13<br>13 | 32<br>10<br>8 | 12<br>200 | dB<br>MHz<br>ns<br>Ω | (See Note 1<br>(See Note 2)<br>(See Note 3)<br>(See Note 4) |

Notes:

- 1) Remove dc offset, at 2.048MHz, Pin 13 = 1Vpk-pk sine wave

- 2) Remove dc offset, Pin 13 = 1Vpk-pk sine wave

- 3) Remove dc offset, Pin 15 = 2Vpk-pk sine wave; delay from Pin 15 negative-going zero crossover to Pin 13 positive edge

- 4) Remove dc offset, at 2.048MHz

| LBO (Ref. Figure 2)               |          |    |      |    |              |

|-----------------------------------|----------|----|------|----|--------------|

| Off Impedance                     | 2,3,4    | 20 |      | kΩ | (See Note 1) |

| Intermediate Impedance Difference | 2,3,4    |    | 5    | %  | (See Note 2) |

| On Impedance                      | 2,3,4    |    | 25   | Ω  | (See Note 3) |

| Transconductance                  | 7/8 to 1 |    | 0.03 | dB | (See Note 4) |

Notes:

- 1) At 1MHz, allow for in-circuit R, C

- 2) At 1MHz, V<sub>8</sub>-V<sub>7</sub> adjusted for current at Pin 1 = 100μA

- 3) At 1MHz, V<sub>8</sub>-V<sub>7</sub> adjusted for ±1.75V

- 4) At 1MHz, change in  $V_8-V_7$  for current at Pin 1 = 10 $\mu$ A to 100 $\mu$ A

| SYMBOL    | PARAMETERS                        | PINS | MIN | TYP | MAX | UNIT | CONDITIONS             |

|-----------|-----------------------------------|------|-----|-----|-----|------|------------------------|

| Threshold | Voltages (Ref. Figure 3)          |      |     |     |     |      |                        |

|           | ALBO Threshold +ve                | 8-7  | 1.4 | 1.5 | 1.6 | V    | (See Notes 1 & 2)      |

|           | ALBO Threshold -ve                | 7-8  | 1.4 | 1.5 | 1.6 | V    | (See Notes 1 & 2)      |

|           | ALBO Threshold Difference         | _    | -5  | o   | 5   | %    | (See Note 3)           |

|           | Clock Drive on Current (peak) +ve | 18   |     | 1.0 | 1.4 | mA   | (See Note 4)           |

|           | Clock Drive on Current (peak) -ve | 18   |     | 1.0 | 1.3 | mA   | (See Note 5)           |

|           | Clock Drive on Current Difference | _    | -5  | 0   | 5   | %    | (See Note 3)           |

|           | Clock Threshold +ve               | 87   | 68  |     | 80  | %    | (See Notes 1, 6, 8)    |

|           | Clock Thresholdve                 | 7-8  | 68  |     | 80  | %    | (See Notes 1, 7, 8)    |

|           | Clock Threshold Difference        | _    | -5  | 0   | 5   | %    | (See Note 3)           |

|           | Data Threshold +ve                | 8-7  | 44  | 46  | 48  | %    | (See Notes 1, 8, 9, 11 |

|           | Data Threshold -ve                | 7-8  | 44  | 46  | 48  | %    | (See Notes 1, 8, 10, 1 |

|           | Data Threshold Difference         | _    | -3  | 0   | 3   | %    | (See Note 3)           |

Notes:

- Pk/pk voltage at Pins 7 and 8 of a 1MHz sine wave derived through amplifier and measured differentially

- 2) Pk/pk voltage at Pins 7 and 8 adjusted for current at Pin 1 = 3mA

- 3) Calculation only percentage difference calculated from  $\left(\frac{\text{higher value}}{\text{lower value}} 1\right) \times 100\%$

- V<sub>8</sub>-V<sub>7</sub> adjusted to ALBO threshold +ve voltage, ref. Pin 16 = 3.6V

- 5)  $V_7$ - $V_8$  adjusted to ALBO threshold -ve voltage, ref. Pin 16 = 3.6V

- 6)  $V_8-V_7$  adjusted to peak current at Pin 18 = 1/2 (clock drive on current peak +ve)

- 7)  $V_7 V_8$  adjusted to peak current at Pin 18 = 1/2 (clock drive on current peak -ve)

- 8) Figure taken as a percentage of lower ALBO threshold

- 9) V<sub>8</sub>-V<sub>7</sub> increased until 1MHz PRF on counter at Pin 10

- 10) V7-V8 increased until 1MHz PRF on counter at Pin 11

- 11) With 2,048MHz 2Vpk-pk sine wave to Pin 15 with 180 $\mu$ H parallel with 36 $\Omega$  to Pin 16 = 3.6V

| t <sub>r</sub>  | Output Pulse Rise Time +ve     | 10 |       |     | 40   | ns | 10%-90% |

|-----------------|--------------------------------|----|-------|-----|------|----|---------|

| t,              | Output Pulse Rise Time -ve     | 11 |       |     | 40   | ns | 10%-90% |

| t <sub>i</sub>  | Output Pulse Fall Time +ve     | 10 |       |     | 40   | ns | 10%-90% |

| t <sub>f</sub>  | Output Pulse Fall Time -ve     | 11 |       |     | 40   | ns | 10%-90% |

| t <sub>w</sub>  | Output Pulse Width +ve         | 10 | 224   | 244 | 264  | ns | at 50%  |

|                 | Output Pulse Width -ve         | 11 | 224   | 244 | 264  | ns | at 50%  |

| ∆t <sub>w</sub> | Output Pulse Width Difference  | _  | -10   |     | 10   | ns |         |

| VoL             | Buffer Gate Voltage (low) +ve  | 10 | 0.65  |     | 0.95 | ٧  |         |

| VoL             | Buffer Gate Voltage (low) -ve  | 11 | 0.65  |     | 0.95 | ٧  |         |

| ΔVOL            | Buffer Gate Voltage Difference |    | -0.15 |     | 0.15 | V  |         |

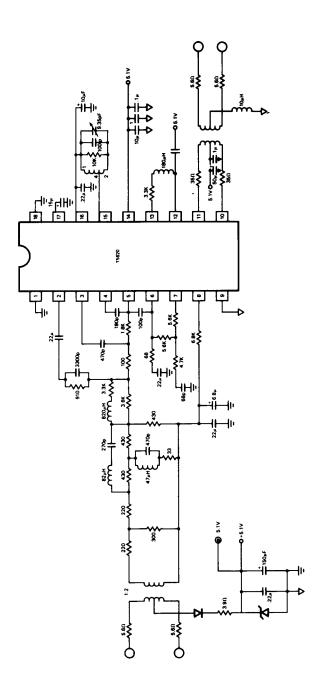

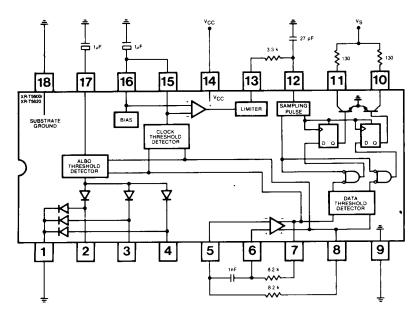

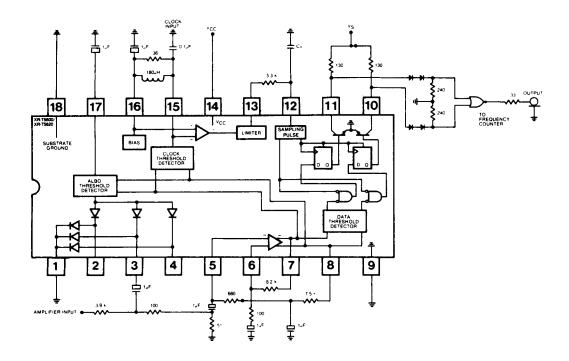

Figure 2. D.C. Parameter Test Circuit

Figure 3. A.C. Parameter Test Circuit

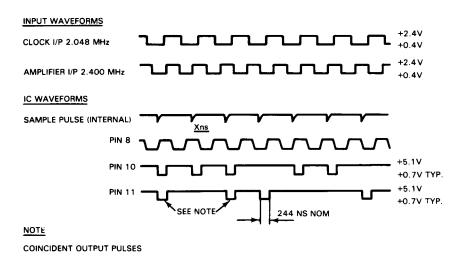

| SYMBOL PARAMETERS PINS MIN TYP MAX UNIT CONDITIONS        |                  |  |  |    |  |    | CONDITIONS      |  |  |

|-----------------------------------------------------------|------------------|--|--|----|--|----|-----------------|--|--|

| Sample Pulse Width (Ref. Figure 4, C <sub>Y</sub> = 27pF) |                  |  |  |    |  |    |                 |  |  |

| Sar                                                       | nple Pulse width |  |  | 10 |  | ns | (See Notes 1 5) |  |  |

#### Notes:

- 1) The sample pulse width is the period during which the output latches are opened to accept a signal above the data hold at Pin 7 or 8 and cause a half-width output pulse at Pin 11 or 10 respectively.

- 2) Sample pulse width is specified with a 2.048MHz TTL waveform at clock input (Pin 15) and a 2,400MHz Schottky TTL waveform at amplifier input in the circuit of Figure 4. Figure 7 shows the relevant IC waveforms.

- Monitor the frequency of coincident output pulses at Pins 10 and 11 either directly or through output circuit to frequency counter.

- 4) Sample pulse width = X ns + (0,1 x measured frequency in kHz) ns where X is the mean rise/fail times of the waveform at Pin 8 between 25% and 75%.

- 5) X to be within the range of 10nx < X < 12ns. THis requires HF layout techniques with the amplifier operated closed loop.

|                                                                  | Sample Pulse Generator Input Waveform (Pin 12 — Ref. Figure 4, C <sub>Y</sub> = 40pF) |                        |        |       |       |       |     |              |  |  |  |

|------------------------------------------------------------------|---------------------------------------------------------------------------------------|------------------------|--------|-------|-------|-------|-----|--------------|--|--|--|

| Output Pulse Frequency 10, 11 1.024 1.024 1.024 MHz (See Note 1) |                                                                                       | Output Pulse Frequency | 10, 11 | 1.024 | 1.024 | 1.024 | MHz | (See Note 1) |  |  |  |

Note:

1) With 2.048MHz ± 100ppm TTL waveform at clock input. With half of above waveform frequency at amplifier input.

Figure 4. Sampling Pulse Test Circuit

Figure 5. Typical and Limiting Values of Gain and Phase

Figure 6. IC Waveforms for Measuring Sampling Pulse Width