# MOS INTEGRATED CIRCUIT $\mu PD705101$

# V831™ 32-BIT MICROPROCESSOR

#### **DESCRIPTION**

The  $\mu$ PD70501 (V831) is a 32-bit RISC microprocessor for embedded control applications, with a high-performance 32-bit V830<sup>TM</sup> processor core and many peripheral functions such as a DRAM/ROM controller, 4-channel DMA controller, real-time pulse unit, serial interface, and interrupt controller.

In addition to high interrupt response speed and optimized pipeline structure, the V831 offers sum-of-products operation instructions, concatenated shift instructions, and high-speed branch instructions to realize multimedia functions, and therefore, can provide high performance in multimedia systems such as internet/intra-net systems, car navigation systems, high-performance televisions, and color FAXes.

Detailed explanations of the functions, etc. are given in the following user's manuals. Be sure to read the manuals before designing your systems.

V831 User's Manual -Handware : U12273E V830 Family<sup>TM</sup> User's Manual -Architecture : U12496E

#### **FEATURES**

• CPU function

· V830-compatible instructions

Instruction cache : 4 KBInstruction RAM : 4 KB

• Data cache : 4 KB

Data RAM : 4 KBMinimum number of instruction

execution cycles : 1 cycle

• Number of general purpose registers :  $32 \text{ bits} \times 32$

• Memory space and I/O space : 4 GB each

· Interrupt/exception function

Non-maskable: External input: 1

Maskable : External input : 8 (of which 4 are multiplexed with internal sources)

Internal source: 11 types

· Bus control function

· Wait control function

Memory access control function

• DMA controller : 4 channel

· Serial interface function

· Asynchronous serial interface (UART): 1 channel

Clocked serial interface (CSI) : 1 channel

• Dedicated baud rate generator (BRG): 1 channel

· Timer/counter function

• 16-bit timer/event counter: 1 channel

• 16-bit interval timer : 1 channel

Port function : 3 I/O ports

· Clock generation function: PLL clock synthesizer

Standby function : HALT and STOP modes

Debug function

Debug-dedicated synchronous serial

interface : 1 channel

• Trace-dedicated interface : 1 channel

The information in this document is subject to change without notice.

## ORDERING INFORMATION

| Part Number         | Package                                        |

|---------------------|------------------------------------------------|

| μPD705101GM-100-8ED | 160-pin plastic LQFP (fine pitch) (24 × 24 mm) |

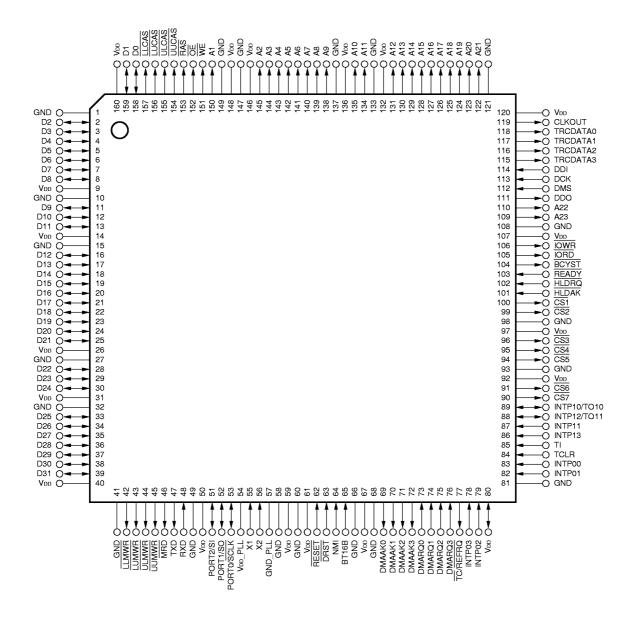

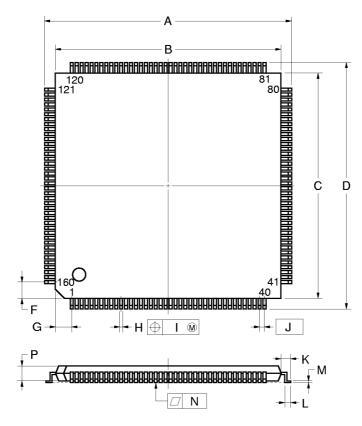

# PIN CONFIGURATION (TOP VIEW)

• 160-pin plastic LQFP (fine pitch) (24  $\times$  24 mm)  $\mu$ PD705101GM-100-8ED

#### PIN NAMES

BT16B : Boot Bus Size 16 bit PORT0-PORT2 : Port

CLKOUT : Clock Out RAS : Row Address Strobe

CS1-CS7 : Chip Select READY : Ready

D0-D31 : Data Bus REFRQ : Refresh Request

DCK : Debug Clock RESET : Reset

DDI : Debug Data Input RXD : Receive Data

: Debug Data Output **SCLK** : Serial Clock DDO DMAAK0-DMAAK3: DMA Acknowledge SI : Serial Input DMARQ0-DMARQ3: DMA Request SO : Serial Output TC **DMS** : Debug Mode Select : Terminal Count : Debug Reset **TCLR** : Timer Clear

DRST: Debug ResetTCLR: Timer ClearGND: GroundTI: Timer InputGND PLL: PLL GroundTO10, TO11: Timer Output

HLDAK : Hold Acknowledge TRCDATA0-TRCDATA3

HLDRQ : Hold Request : Trace Data

INTP00-INTP03, INTP10-INTP13 TXD : Transmit Data

IOWR : I/O Write UUMWR : Upper Upper Memory Write

LLCAS

: LowerLowerColumnAddressStrobe

VDD

: Power Supply

LLMWR

: Lower Lower Memory Write

VDD\_PLL

: PLL Power Supply

LUCAS

: LowerUpperColumnAddressStrobe

WE

: Write Enable

LUMWR : Lower Upper Memory Write X1, X2 : Crystal Oscillator

MRD : Memory Read

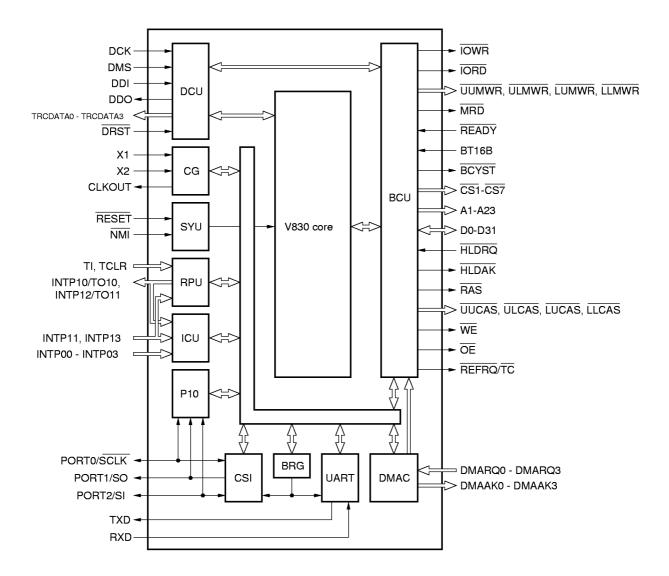

# **BLOCK DIAGRAM**

# **CONTENTS**

| 1.  | PIN FUNCTIONS LIST                                                                                                                                                       | 6                |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 2.  | INTERNAL UNITS                                                                                                                                                           | 8                |

| 3.  | CPU FUNCTION                                                                                                                                                             | . 10             |

| 4.  | INTERRUPT/EXCEPTION PROCESSING FUNCTION                                                                                                                                  | . 11             |

| 5.  | BUS CONTROL FUNCTION                                                                                                                                                     | . 13             |

| 6.  | WAIT CONTROL FUNCTION                                                                                                                                                    | . 13             |

| 7.  | MEMORY ACCESS CONTROL FUNCTION                                                                                                                                           | 14               |

| 8.  | DMA FUNCTION                                                                                                                                                             | . 16             |

| 9.  | SERIAL INTERFACE FUNCTION  9.1 Asynchronous Serial Interface (UART)  9.2 Clocked Serial Interface (CSI)  9.3 Baud Rate Generator (BRG)  9.3.1 Configuration and function | . 18<br>20<br>21 |

| 10. | TIMER/COUNTER FUNCTION                                                                                                                                                   | . 22             |

| 11. | PORT FUNCTION                                                                                                                                                            | . 25             |

| 12. | CLOCK GENERATION FUNCTION                                                                                                                                                | . 27             |

| 13. | STANDBY FUNCTION                                                                                                                                                         | . 28             |

| 14. | RESET/NMI CONTROL FUNCTION                                                                                                                                               | . 30             |

| 15. | INSTRUCTIONS                                                                                                                                                             | 31               |

| 16. | ELECTRICAL SPECIFICATIONS                                                                                                                                                | . 43             |

|     | PACKAGE DRAWINGS                                                                                                                                                         |                  |

| 10  | DECOMMENDED SOLDEDING CONDITIONS                                                                                                                                         | 66               |

# 1. PIN FUNCTIONS LIST

(1/2)

| Pin Name      | 1/0            | Function                                       | (1/2) Multiplexed Pin |

|---------------|----------------|------------------------------------------------|-----------------------|

| D0-D31        | 3-state I/O    | Data bus                                       | -                     |

| A1-A23        | 3-state output | Address bus                                    | _                     |

| UUCAS         | 1              | Column address strobe (most significant byte)  | _                     |

| ULCAS         | 1              | Column address strobe (most significant byte)  | _                     |

| LUCAS         | 1              | Column address strobe (third byte)             | _                     |

| LLCAS         | ]              | Column address strobe (least significant byte) | _                     |

| RAS           | ]              | Row address strobe/chip select                 | _                     |

| UUMWR         |                | Memory write strobe (most significant byte)    | _                     |

| ULMWR         | ]              | Memory write strobe (second byte)              | _                     |

| LUMWR         | ]              | Memory write strobe (third byte)               | _                     |

| LLMWR         |                | Memory write strobe (least significant byte)   | _                     |

| MRD           |                | Memory read strobe                             | _                     |

| WE            |                | DRAM write strobe                              | _                     |

| ŌĒ            |                | DRAM read strobe                               | _                     |

| ĪORD          |                | I/O read strobe                                | _                     |

| ĪOWR          |                | I/O write strobe                               | _                     |

| REFRQ         |                | DRAM refresh request                           | TC                    |

| CS1, CS2, CS7 | ]              | Memory chip select                             | _                     |

| CS3-CS6       |                | Memory chip select / I/O chip select           | _                     |

| BCYST         |                | Bus cycle start                                | _                     |

| BT16B         | Input          | Specifies bus size on boot                     | _                     |

| READY         |                | Enables end of bus cycle                       | _                     |

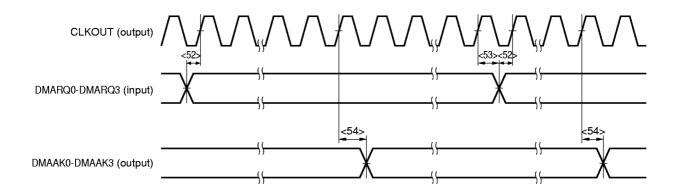

| DMARQ0-DMARQ3 |                | DMA request (CH0 through CH3)                  | _                     |

| DMAAK0-DMAAK3 | Output         | DMA enable (CH0 through CH3)                   | _                     |

| TC            |                | DMA transfer end                               | REFRQ                 |

| RXD           | Input          | UART data input                                | _                     |

| TXD           | Output         | UART data output                               | -                     |

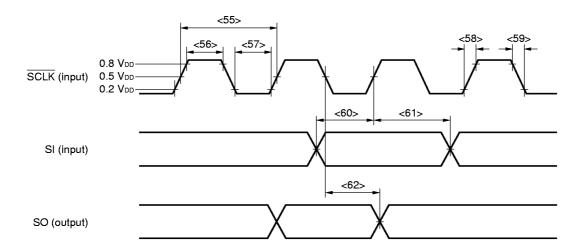

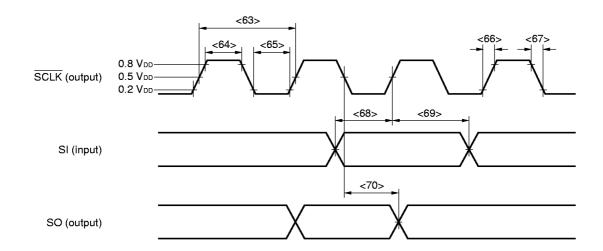

| SI            | Input          | CSI data input                                 | PORT2                 |

| so            | Output         | CSI data output                                | PORT1                 |

| SCLK          | 1/0            | CSI clock I/O                                  | PORT0                 |

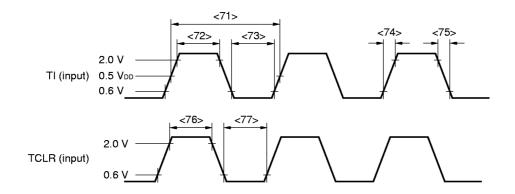

| ТІ            | Input          | Timer 1 count clock input –                    |                       |

| TCLR          |                | Timer 1 clear, start                           | -                     |

| TO10          | Output         | RPU pulse output                               | INTP10                |

| TO11          |                |                                                | INTP12                |

(2/2)

| Pin Name              | I/O            | Function                                                           | Multiplexed Pin |

|-----------------------|----------------|--------------------------------------------------------------------|-----------------|

| INTP10                | Input          | Interrupt request                                                  | TO10            |

| INTP11                |                |                                                                    | _               |

| INTP12                |                |                                                                    | TO11            |

| INTP13                |                |                                                                    | _               |

| INTP00-INTP03         |                |                                                                    | _               |

| HLDRQ                 |                | Bus request                                                        | _               |

| HLDAK                 | Output         | Bus enable                                                         | _               |

| NMI                   | Input          | Non-maskable interrupt request                                     | _               |

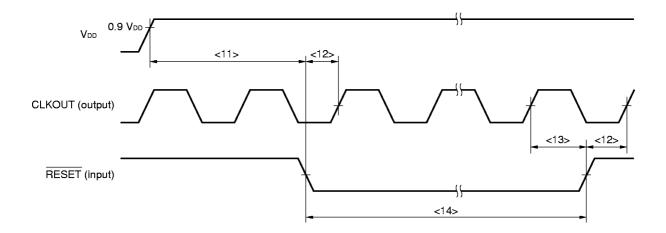

| RESET                 |                | System reset                                                       | _               |

| PORT0                 | 1/0            | Port                                                               | SCLK            |

| PORT1                 |                |                                                                    | so              |

| PORT2                 |                |                                                                    | SI              |

| X1                    | _              | Connects crystal resonator. (Opened when external clock is input.) | -               |

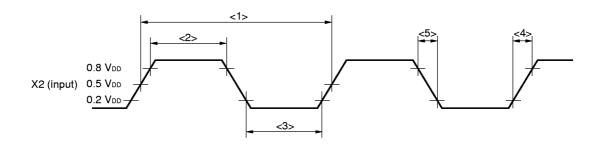

| X2                    | Input          | Connects crystal resonator or inputs external clock.               | _               |

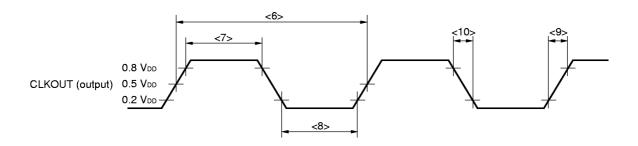

| CLKOUT                | Output         | Bus clock output                                                   | _               |

| DCK                   | Input          | Debug clock input                                                  | _               |

| DDI                   |                | Debug data input                                                   | _               |

| DDO                   | 3-state output | Debug data output                                                  | _               |

| DMS                   | Input          | Debug mode select                                                  | _               |

| DRST                  |                | Reset input (debug module)                                         | _               |

| TRCDATA0-<br>TRCDATA3 | Output         | Trace data output                                                  | -               |

| V <sub>DD</sub>       | _              | Positive power supply                                              | _               |

| GND                   |                | Ground potential                                                   | -               |

| V <sub>DD</sub> _PLL  |                | Positive power supply for PLL (internal clock generator)           | -               |

| GND_PLL               |                | Ground potential for PLL (internal clock generator)                | _               |

#### 2. INTERNAL UNITS

#### (1) Bus control unit (BCU)

Controls the address bus, data bus, and control bus pins. The major functions of BCU are as follows:

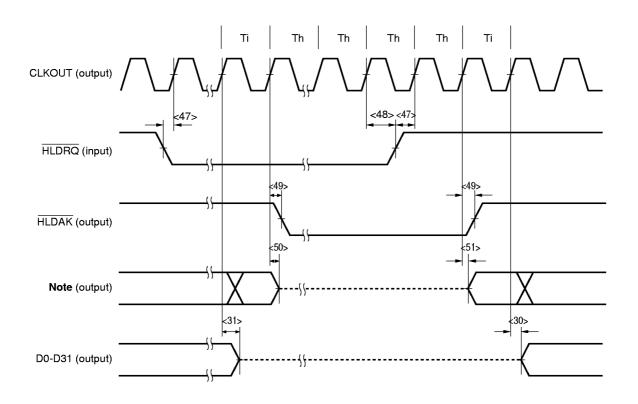

#### (a) Bus arbitration

Arbitrates the bus mastership among bus masters (CPU, DRAMC, DMAC, and external bus masters). The bus mastership can be changed after completion of the bus cycle under execution, and in an idle state.

#### (b) Wait control

Controls eight areas in the 16M-byte space corresponding to  $\overline{RAS}$  and seven chip select signals ( $\overline{CS1}$  through  $\overline{CS7}$ ). Generates chip select signals, controls wait states, and selects the type of bus cycle.

#### (c) DMA controller

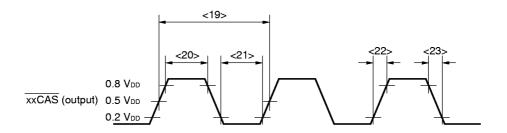

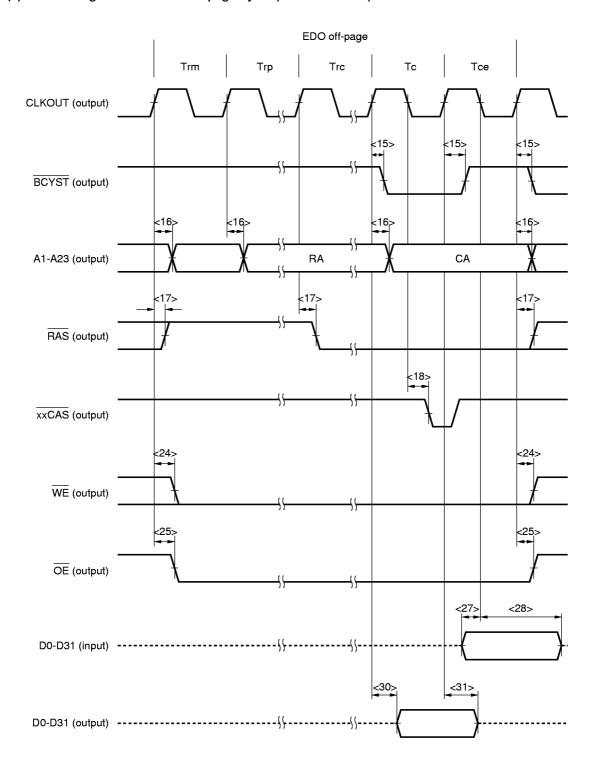

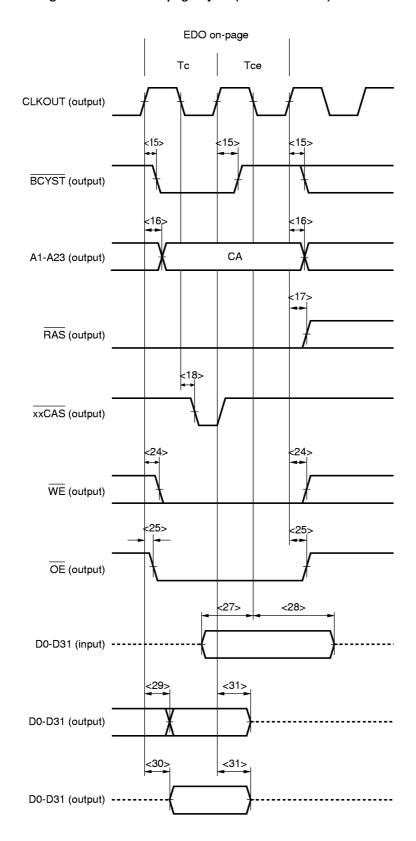

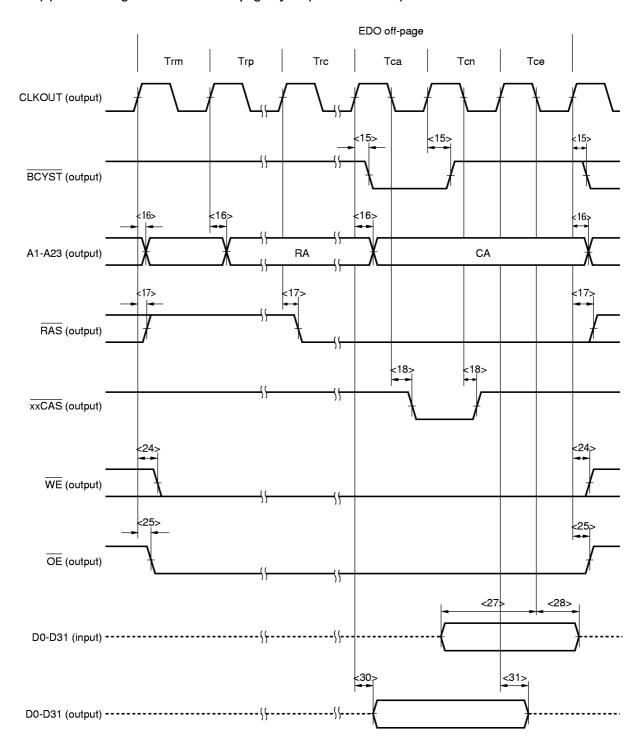

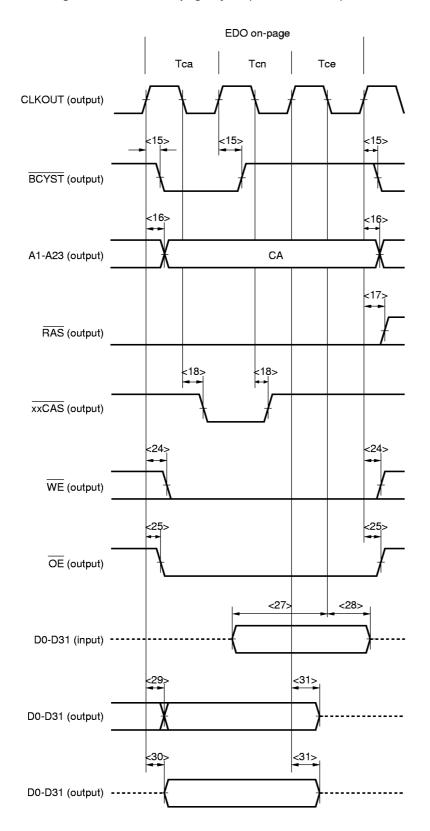

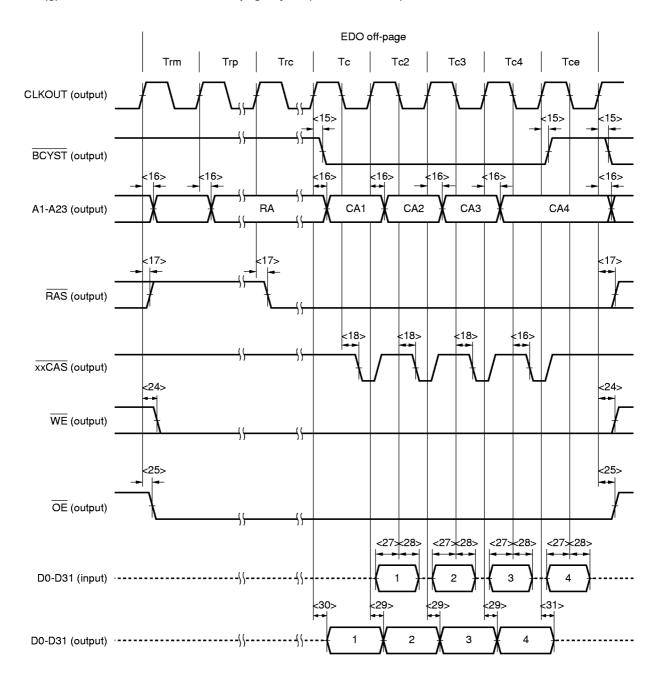

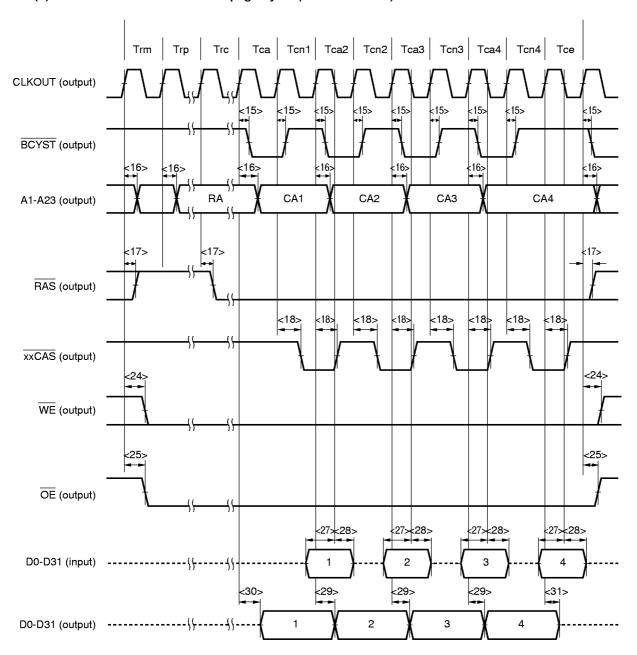

Generates RAS and four CAS signals, and controls access to DRAM. The hyper page mode of DRAM is supported and DRAM can be accessed in two types of cycle: normal access (off-page) and hyper page (on-page).

#### (d) ROM controller

Accessing ROM with page access function is supported. The bus cycle immediately before and addresses are compared, and wait states are controlled in the normal access (off-page) and page access (on-page) modes. A page width of 8 bytes to 16 bytes can be supported.

#### (2) Interrupt controller (ICU)

Services maskable interrupt requests (INTP00 through INTP03, and INTP10 through INTP13) from internal peripheral hardware and external sources. The priorities of these interrupt requests can be specified in units of four groups, and edge-triggered or level-triggered interrupts can be nested.

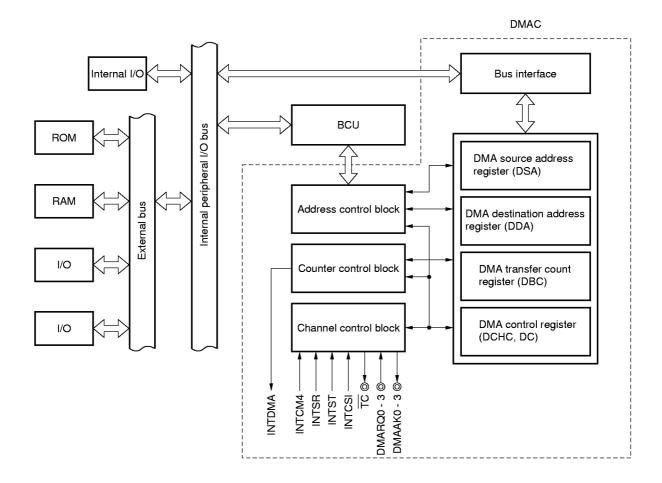

#### (3) DMA controller (DMAC)

Transfers data between memory and I/O in the place of the CPU. The transfer type is 2-cycle transfer. Two transfer modes, single transfer and demand transfer, are available.

## (4) Serial interface (UART/CSI/BRG)

One asynchronous serial interface (UART) channel and one clocked serial interface (CSI) channel is provided. As the serial clock source, the output of the baud rate generator (BRG) and the bus clock can be selected.

## (5) Real-time pulse unit (RPU)

Provides timer/counter functions. The on-chip 16-bit time/event counter and 16-bit interval timer can be used to calculate pulse intervals and frequencies, and to output programmable pulses.

#### (6) Clock generator (CG)

A frequency three times higher than that of an oscillator connected to the X1 and X2 pins is supplied as the operating clock of the CPU. In addition, a bus clock (with the same cycle as the input clock) is also supplied as the operating clock of the peripheral units. An external clock can be also input instead of connecting an oscillator.

## (7) Port (PIO)

Provides port functions. Three I/O ports are available. The pins of these ports can be used as port pins or serial control pins.

# (8) System control unit (SYU)

A circuit that rejects noise on the  $\overline{\text{RESET}}$  signal (input)/ $\overline{\text{NMI}}$  signal (input) is provided.

# (9) Debug control unit (DCU)

A circuit to realize mapping and trace functions is provided to implement basic debugging functions.

**NEC**  $\mu$ PD705101

## 3. CPU FUNCTION

The features of the CPU function are as follows:

• High-performance 32-bit architecture for embedded control applications

· Cache memory

Instruction cache: 4K bytes

Data cache: 4K bytes

Internal RAM

Instruction RAM : 4K bytes

Data RAM : 4K bytes

• 1-clock pitch pipeline structure

- 16-/32-bit length instruction format

- 10732 bit length matruction forma

- Address/data separated type bus

- · 4GB linear address

- Thirty-two 32-bit general register

- · Register/flag hazard interlock is handled by hardware

- 16 levels of interrupt response

- 16-bit bus fixed function

- 16-bit bus system can be constructed

- Ideal instructions for any application field:

- · Sum-of-products operation

- · Saturation operation

- · Branch prediction

- · Concatenation shift

- · Block transfer instruction

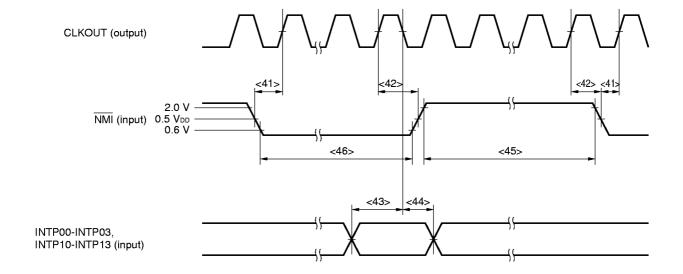

#### 4. INTERRUPT/EXCEPTION PROCESSING FUNCTION

The features of the interrupt/exception processing function are as follows:

Interrupt

Non-maskable interrupt: 1 sourceMaskable interrupt : 15 sources

- · Priority of the programmable interrupt can be specified in four levels

- · Nesting interrupt can be controlled according to the priority

- · Mask can be specified for each maskable interrupt request

- · Valid edge of an external interrupt request can be specified

- Noise rejection circuit provided for the non-maskable interrupt pin (NMI)

- Exception

Software exception: 32 sourcesException trap : 4 sources

The interrupt/exception sources are shown in Tables 4-1 and 4-2.

Table 4-1. Reset/Non-maskable Interrupt/Exception Source List

| Туре               | Classification | Source of In      | terrupt/Exception        | Exception Code | Handler   | Restore       |

|--------------------|----------------|-------------------|--------------------------|----------------|-----------|---------------|

| туре               | Classification | Name Note 1 Cause |                          | (ECR)          | Address   | PCNote 2      |

| Reset              | Interrupt      | RESET             | Reset input              | FFF0H          | FFFFFF0H  | Undefined     |

| Non-maskable       | Interrupt      | NMI               | NMI input                | FFD0H          | FFFFFFD0H | next PCNote 3 |

| Software exception | Exception      | TRAP 1nH          | TRAP instruction         | FFBnH          | FFFFFB0H  | next PC       |

|                    |                | TRAP 0nH          | TRAP instruction         | FFAnH          | FFFFFA0H  |               |

| Exception trap     | Exception      | NMI               | Dual exception           | Note 4         | FFFFFD0H  | current PC    |

|                    |                | FAULT             | Fatal exception          | Not affected   | FFFFFE0H  |               |

|                    |                | I-OPC             | Illegal instruction code | FF90H          | FFFFF90H  |               |

|                    |                | DIV0              | Zero division            | FF80H          | FFFFFF80H |               |

**Notes 1.** Handler names used in development tools or software.

- 2. The PC value saved to EIPC/FEPC/DPC when interrupt/exception processing is started.

- 3. Execution of all instructions cannot be stopped by an interrupt.

- 4. The exception code of an exception causing a dual exception.

Remark n = 0H to FH

**Table 4-2. Maskable Interrupt List**

| Type  | Classifi- | Group | In-<br>Group | Source of Interrupt Exception Handler Addres |                                                                             |                  |           | ldress <sup>Note 3</sup> | Restore    |          |

|-------|-----------|-------|--------------|----------------------------------------------|-----------------------------------------------------------------------------|------------------|-----------|--------------------------|------------|----------|

| Туре  | cation    | Group | Priority     | Name                                         | Cause Unit                                                                  |                  | Code      | HCCW.IHA=0               | HCCW.IHA=1 | PCNote 1 |

| Mask- | Interrupt | GR3   | 3            | RESERVED                                     | Reserved                                                                    | _                | FEF0H     | FFFFFEF0H                | FE0000F0H  | next     |

| able  |           |       | 2            | INTOV1                                       | Timer 1 overflow                                                            | RPU              | FEE0H     | FFFFFEE0H                | FE0000E0H  | PCNote 2 |

|       |           |       | 1            | INTSER                                       | UART receive error                                                          | UART             | FED0H     | FFFFFED0H                | FE0000D0H  |          |

|       |           |       | 0            | INTP03                                       | INTP03 pin input                                                            | External         | FEC0H     | FFFFEC0H                 | FE0000C0H  |          |

|       |           | GR2   | 3            | INTSR                                        | UART receive end                                                            | UART             | FEB0H     | FFFFFEB0H                | FE0000B0H  |          |

|       |           |       | 2            | INTST                                        | UART transmit end                                                           | UART             | FEA0H     | FFFFFEA0H                | FE0000A0H  |          |

|       |           |       | 1            | INTCSI                                       | CSI transmit/receive end                                                    | CSI              | FE90H     | FFFFFE90H                | FE000090H  |          |

|       |           |       | 0            | INTP02                                       | INTP02 pin input                                                            | External         | FE80H     | FFFFFE80H                | FE000080H  |          |

|       |           | GR1   | 3            | INTDMA                                       | DMA transfer end                                                            | DMAC             | FE70H     | FFFFFE70H                | FE000070H  |          |

|       |           |       | 2            | INTP10/<br>INTCC10                           | INTP10 pin input/<br>coincidence of CC10                                    | External/<br>RPU | FE60H     | FFFFE60H                 | FE000060H  |          |

|       |           |       | 1            | INTP11/<br>INTCC11                           | INTP11 pin input/ External/ FE50H FFFFE50H FE000050 coincidence of CC11 RPU |                  | FE000050H |                          |            |          |

|       |           |       | 0            | INTP01                                       | INTP01 pin input                                                            | External         | FE40H     | FFFFFE40H                | FE000040H  |          |

|       |           | GR0   | 3            | INTCM4                                       | Coincidence of CM4                                                          | RPU              | FE30H     | FFFFFE30H                | FE000030H  |          |

|       |           |       | 2            | INTP12/<br>INTCC12                           | INTP12 pin input/<br>coincidence of CC11                                    | External/<br>RPU | FE20H     | FFFFFE20H                | FE000020H  |          |

|       |           |       | 1            | INTP13/<br>INTCC13                           | INTP13 pin input/<br>coincidence of CC13                                    | External/<br>RPU | FE10H     | FFFFFE10H                | FE000010H  |          |

|       |           |       | 0            | INTP00                                       | INTP00 pin input                                                            | External         | FE00H     | FFFFE00H                 | FE000000H  |          |

Notes 1. The PC value saved to EIPC when interrupt processing is started.

- 2. Execution of all instructions cannot be stopped by an interrupt.

- 3. FFFFEn0H can be selected as a handler address when HCCW.IHA = 0, and FE0000n0H can be selected when HCCW.IHA = 1 (N = 0H to FH).

Caution The exception codes and handler addresses of the maskable interrupts shown above are the values if the default priority is used.

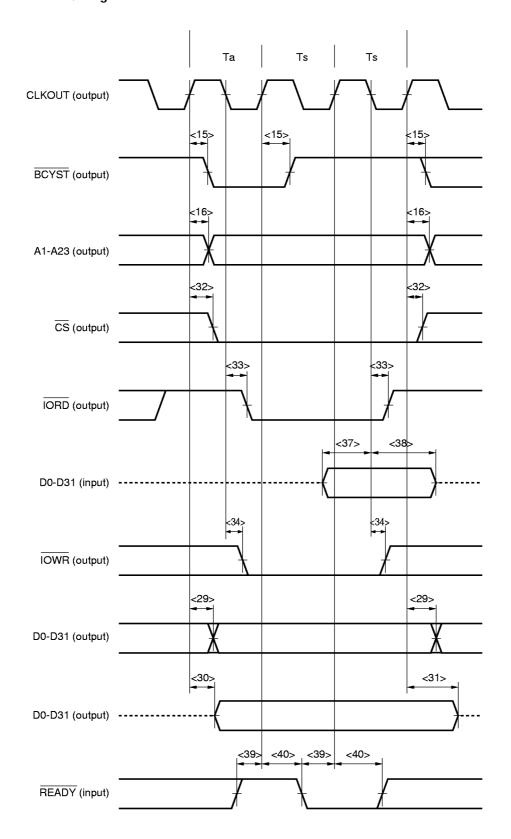

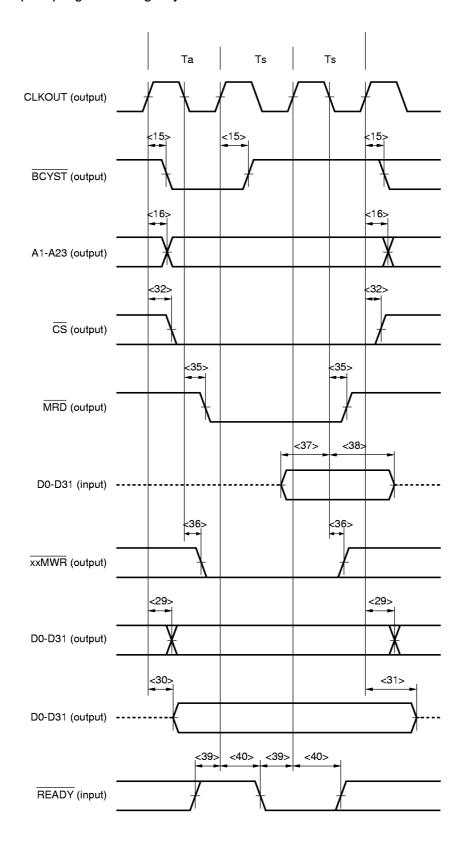

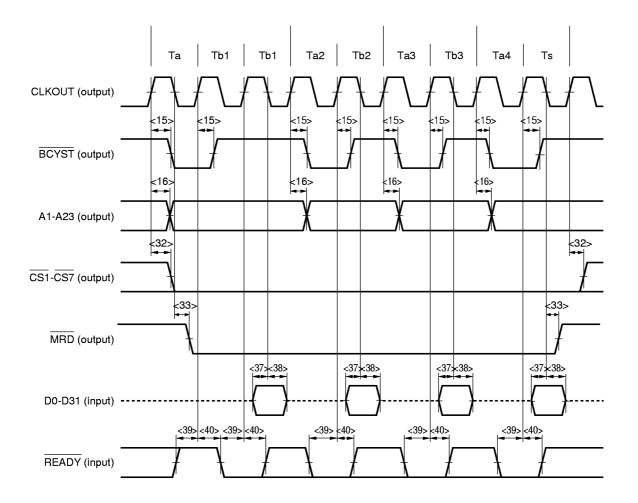

## 5. BUS CONTROL FUNCTION

The features of the bus control function are as follows:

- Directly connects to EDO DRAM, Page-ROM, SRAM (ROM), or I/O

- · CAS access with 1 bus clock minimum

- DRAM byte access control with four CAS signals

- Wait control by READY signal

- 32-/16-bit bus width can be set every CS space

- When the 16-bit memory or I/O are accessed by data bus, the external data bus width can be set by the data bus width control register (DBC).

#### 6. WAIT CONTROL FUNCTION

The features of the wait control function are as follows:

- Controls 8 blocks in accordance with I/O and memory spaces

- Linear address space of each block: 16M bytes

- Bus cycle select function

Block 0 : EDO DRAM

Blocks 1 and 2 : SRAM (ROM)

Blocks 3 through 6 : I/O or SRAM (ROM) selectable

Block 7 : Page-ROM or SRAM (ROM) selectable

· Data bus width select function

Data bus width selectable between 32 bits and 16 bits for each block

• Wait control function

Block 0 : Can control EDO DRAM access timing

Blocks 1 through 4 and 7: 0 to 7 wait states

Blocks 5 and 6: 0 to 15 wait states

• Idle state insertion function

0 to 3 states for each block (bus clock)

## 7. MEMORY ACCESS CONTROL FUNCTION

The features of the memory access control function are as follows:

• DRAM control function

• Generates RAS, LLCAS, LUCAS, ULCAS, UUCAS, REFRQ, OE, and WE signals

• Address multiplex: 8, 9, or 10 bits

· Timing control of DRAM access

CAS access period : 1 or 2 bus clocks selectable

RAS-CAS delay period : 1.5 or 2.5 bus clocks selectable

RAS precharge period : 2 or 3 bus clocks selectable

· CBR refresh and CBR self-refresh functions

• Page-ROM control function

• Page size : 8 or 16 bytes

· Wait control during page access: 0 or 1 wait states

## 7.1 DRAM Control Function

The BCU generates RAS, LLCAS, LUCAS, ULCAS, UUCAS, REFRQ, OE, and WE signals and controls access to the DRAM. Addresses are output to the DRAM from the address pins by multiplexing row and column addresses.

The connected DRAM must be of x8 bits or more and have a hyper page mode (EDO).

The refresh mode is a  $\overline{\text{CAS}}$ -before- $\overline{\text{RAS}}$  (CBR) mode, and the refresh cycle can be arbitrarily set.

CBR self refresh is performed in the STOP mode.

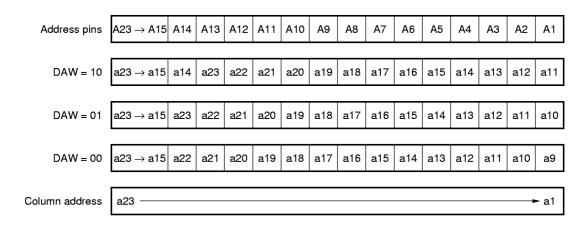

## (1) Address multiplex function

An address is multiplexed as shown in Figure 7-1 when a row and column addresses are output in the DMA cycle, depending on the value of the DAW bit of the DRAM configuration register (DRC). In this figure, a1 through a23 indicate the address output by the CPU, and A1 through A23 indicate the address pins of the V831.

Figure 7-1. Output of Row Address and Column Address

# (2) Decision of on-page/off-page

If the RAS signal is active when page access is enabled because the HPAE bit of the DRAM configuration register (DRC) is 1, whether the DRAM access to be started is in the same page as the previous DRAM access is decided. Table 7-1 shows the relation between an address to be compared and address shift.

Table 7-1. Address Compared by on-page/off-page Decision

| Address Shift   | Data Bus Width |         |  |

|-----------------|----------------|---------|--|

| 71001000 011111 | 16 bits        | 32 bits |  |

| 8               | a23-a9         | a23-a10 |  |

| 9               | a23-a10        | a23-a11 |  |

| 10              | a23-a11        | a23-a12 |  |

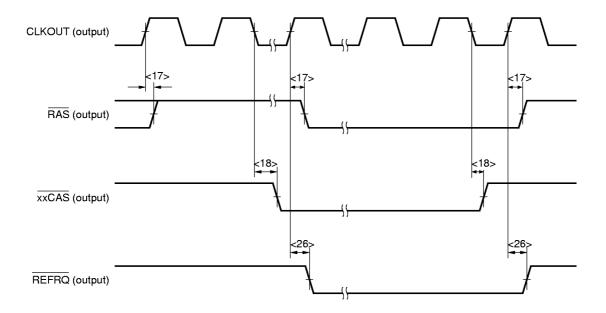

## (3) Refresh function

The BCU can automatically generate the distributed CBR refresh cycle necessary for refreshing the external DRAM. Whether refreshing is enabled or disabled and the refresh interval are set by the refresh control register (RFC).

The BCU has a refresh request queue that can store refresh requests up to seven times.

## 7.2 Page-ROM Control Function

The BCU controls page access to the Page-ROM. Page access to the Page-ROM is valid during burst access. The page size (8 bytes/16 bytes) and the number of wait states (0 wait/1 wait) during page access can be set by using the Page-ROM configuration register (PRC).

## 8. DMA FUNCTION

The features of the DMA function are as follows:

- Four independent DMA channels

- Transfer unit: Bytes, half words (2 bytes), words (4 bytes)

- Maximum number of transfers: 16,777,216 (224) times

- Transfer type: 2-cycle transfer

- Two transfer modes

- · Single transfer mode

- · Demand transfer mode

- Transfer request

- External DMARQ pin (×4)

- Request from internal peripheral hardware (serial interface (x3 channels) and timer)

- · Request from software

- Transfer source and destination

- Between memory and I/O

- · Between memory and memory

- Programmable wait function

- DMA transfer end output signal (TC)

The configuration of the DMA controller (DMAC) is shown below.

Figure 8-1. DMAC Block Diagram

#### 9. SERIAL INTERFACE FUNCTION

The following channels are provided for the serial interface function.

Asynchronous serial interface (UART): 1 channel

Clocked serial interface (CSI): 1 channel

Baud rate generator (BRG): 1 channel

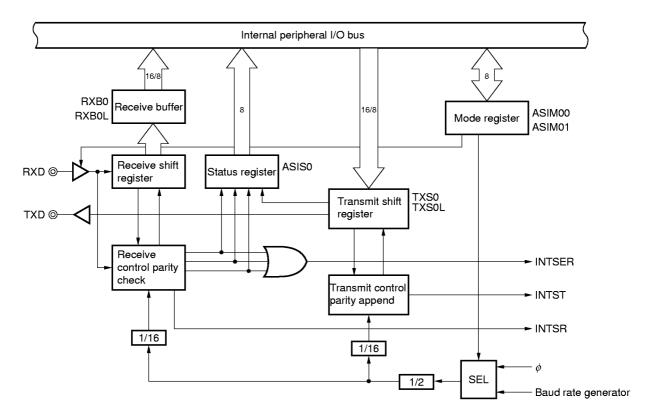

#### 9.1 Asynchronous Serial Interface (UART)

The features of the asynchronous serial interface (UART) are as follows:

- Full duplex communication. Receive buffer (RXB) is provided (transmit buffer (TXB) is not provided).

- Two-pin configuration (The UART of the V831 does not have the SCLK and CTS pins.)

- TXD: Transmit data output pin

- · RXD: Receive data input pin

- Transfer rate: 150 bps to 76800 bps (bus clock: 33 MHz, with BRG)

- Baud rate generator

Serial clock source can be selected from band rate generator output or bus clock  $(\phi)$

- · Receive error detection function

- · Parity error

- · Framing error

- · Overrun error

- Three interrupt sources

- Receive error interrupt (INTSER)

The interrupt is generated by ORing three types of receive errors.

• Receive end interrupt (INTSR)

The receive end interrupt request is generated after completion of receive data transfer from the shift register to the receive buffer in the reception enabled status.

• Transmit end interrupt (INTST)

The transmit end interrupt is generated after completion of serial transfer of transmit data (9, 8, or 7 bits) from the shift register. The character length of the transmit/receive data is specified by the ASIM00 and ASIM01 registers.

• Character length: 7 or 8 bits

: 9 bits (with extension bit appended)

• Parity function : Odd, even, 0, or none

• Transmit stop bit: 1 or 2 bits

The configuration of the asynchronous serial interface (UART) is shown below.

Figure 9-1. Block Diagram of UART

**Remark**  $\phi$  = bus clock (33 M to 16.7 MHz)

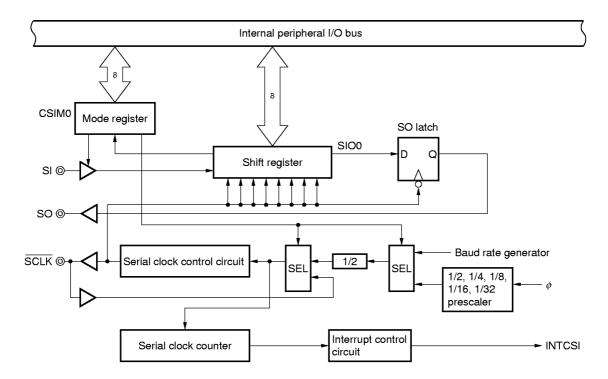

## 9.2 Clocked Serial Interface (CSI)

The features of the clocked serial interface (CSI) are as follows:

- High-speed transfer: 8.25 Mbps MAX. (bus clock: 33 MHz)

- Half duplex communication for transmission/reception (buffer is not provided)

- Character length: 8 bits

- External or internal clock selectable

The configuration of the clocked serial interface (CSI) is shown below.

Figure 9-2. Block Diagram of CSI

**Remark**  $\phi$  = bus clock (33 M to 16.7 MHz)

μ**PD705101**

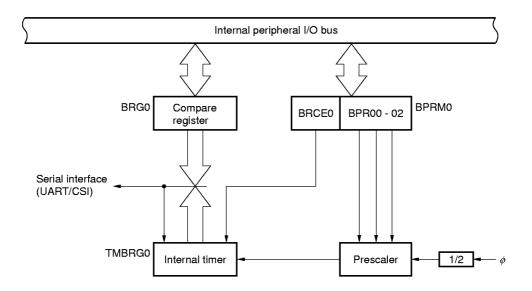

## 9.3 Baud Rate Generator (BRG)

## 9.3.1 Configuration and function

The serial interface can use the serial clock output by the baud rate generator or the divided value of  $\phi$  (bus clock) as a baud rate.

The serial clock source is specified by the following registers.

- In the case of UART: Specified by the SCLS0 bit of the ASIM00 register.

- In the case of CSI : Specified by the CLS02 through CLS00 bits of the CSIM0 register.

- The baud rate generator is shared by the UART and CSI.

The configuration of the baud rate generator (BRG) is shown below.

Figure 9-3. Block Configuration of Baud Rate Generator (BRG)

**Remark**  $\phi$  = bus clock (33 M to 16.7 MHz)

# 10. TIMER/COUNTER FUNCTION

The features of the timer/counter function are as follows:

- Measures pulse interval and frequency and outputs programmable pulse

- 16-bit measurement

- Can generate pulses of various shapes (interval pulse, one-shot pulse)

- Timer 1

- 16-bit timer/event counter

• Source of count clock : 2 types (selected by dividing system clock, external pulse input)

Capture/compare register: × 4

Count clear pin : TCLR

Interrupt source : 5 types

External pulse output : 2 pins

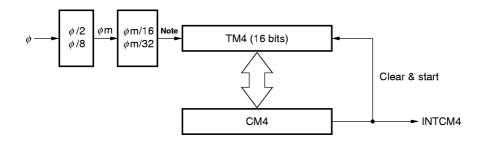

- Timer 4

- · 16-bit interval timer

- · Count clock selected by dividing system clock

- Compare register: × 1Interrupt source : 1 type

The configurations of timer 1 and timer 4 are shown below.

Edge TCLR1 ⊚ detection Clear & start  $\phi$  m  $\phi/2$ Note 1  $\phi$  m/4  $\phi/4$  $\phi$  m/16 TM1 (16 bits) ► INTOV1 TI ⊚ Note 2 Edge detection ► INTCC10 ► INTCC11 INTP10 ⊚-CC10 Edge detection -⊚ TO10 INTP11 ⊚-Edge detection CC11 C INTP12 ⊚-Edge detection CC12 ⊕ TO11 INTP13 ⊚-Edge detection CC13 ► INTCC12 - INTCC13

Figure 10-1. Block Configuration of Timer 1

Notes 1. Internal count clock

2. External count clock (TI: 4.125 MHz MAX.)

3. Reset priority

**Remarks 1.**  $\phi$  = bus clock (33 M to 16.7 MHz)

**2.**  $\phi$ m = intermediate clock

Figure 10-2. Block Configuration of Timer 4

Note Internal count clock

**Remarks 1.**  $\phi$  = bus clock (33 M to 16.7 MHz)

**2.**  $\phi$ m = intermediate clock

# 11. PORT FUNCTION

The features of the port function are as follows:

- 3-bit input/output port which can be specified in 1-bit units

- In addition to the port function, the port can operate as the I/O of the serial interface (CSI) in the control mode

- Port 0 (control mode): operates as SCLK

- · Port 1 (control mode): operates as SO

- Port 2 (control mode): operates as SI

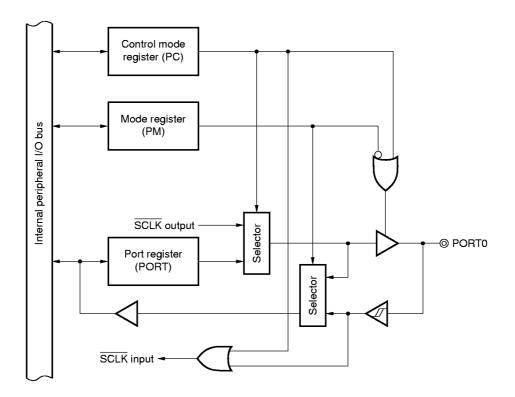

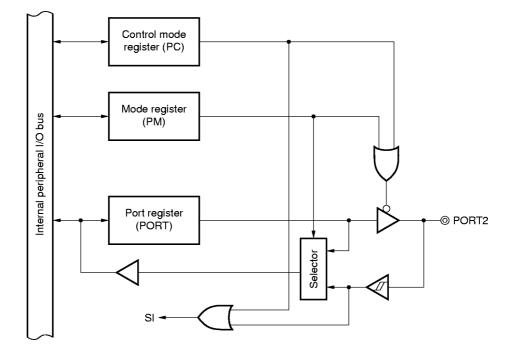

The configurations of port 0 through 2 are shown below.

Figure 11-1. Block Diagram of Port 0

Figure 11-2. Block Diagram of Port 1

Figure 11-3. Block Diagram of Port 2

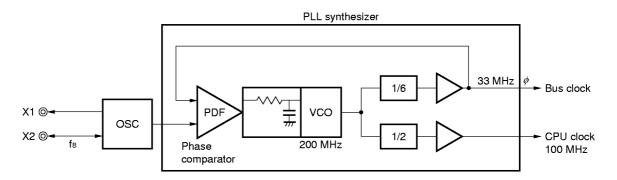

## 12. CLOCK GENERATION FUNCTION

The features of the clock generation function are as follows:

• Generation and control of CPU clock and bus clock supplied to each hardware unit

Bus clock (φ): 16.7-33 MHz (f<sub>B</sub>)

CPU clock : 50-100 MHz (3 × f<sub>B</sub>)

The configuration of the clock generation function is shown below.

Figure 12-1. Block Diagram of Clock Generation Function

fB : Oscillation frequency or external clock frequency

$\phi$  : Bus clock OSC : Oscillator

PFD: Phase Frequency Detector VCO: Voltage Controlled Oscillator

## 13. STANDBY FUNCTION

The following two standby modes can be used.

#### (1) HALT mode

In this mode, the clock generator (oscillation circuit and PLL synthesizer) operates, but the operating clock of the CPU is stopped. The other internal peripheral functions are supplied with the clock and continue operation. By using this mode in combination with the normal mode, the power consumption of the entire system can be reduced.

#### (2) STOP mode

In this mode, the clock generator (PLL synthesizer) is stopped and the entire system is stopped. Because the PLL synthesizer and internal peripheral functions are stopped, the power consumption can be reduced more than in the HALT mode.

Because the clock output of the PLL synthesizer is stopped, make sure that sufficient time elapses after the STOP mode is released until the oscillation circuit, CPU clock, and bus clock are stabilized. The PLL circuit may require lock up time depending on the program.

Table 13-1 shows the operations of the clock generator in the HALT and STOP modes. By selecting each mode as the application requires, the power consumption of the system can be efficiently reduced.

Table 13-1. Operation of Clock Generator in Standby Mode

| Standby Mode | Oscillation Circuit (OSC) | PLL Synthesizer | Clock Supply to<br>Peripheral I/O | Clock Supply to<br>CPU |

|--------------|---------------------------|-----------------|-----------------------------------|------------------------|

| Normal mode  | 0                         | 0               | 0                                 | 0                      |

| HALT mode    | 0                         | 0               | 0                                 | ×                      |

| STOP mode    | 0                         | ×               | ×                                 | ×                      |

Remark ○ : Operates × : Stopped

Table 13-2. Operating Status in HALT/STOP Mode

| Function                                | Ор           | erating StatusNote 1           | STOP Mode                           |

|-----------------------------------------|--------------|--------------------------------|-------------------------------------|

| Oscillation circuit                     | Operates     |                                |                                     |

| PLL synthesizer                         | Operates     |                                | Stops                               |

| Bus clock                               | Operates     |                                | Stops                               |

| CPU                                     | Stops        |                                |                                     |

| Port output                             | Retained     |                                |                                     |

| Peripheral function                     | Operates     |                                | Stops                               |

| Internal data                           | Internal dat | a such as registers of CPU ret | ain status before HALT mode is set. |

| A1-A23                                  | Undefined    | High impedance when HLDAK = 0  | Undefined                           |

| D0-D31                                  | High imped   | ance                           |                                     |

| BCYST                                   | 1            | High impedance when            | 1                                   |

| <u>CS1-CS7</u>                          |              | HLDAK = 0                      |                                     |

| ĪORD, ĪOWR                              |              | <br>                           |                                     |

| MRD, WE, OE, LLMWR, LUMWR, ULMWR, UUMWR |              |                                |                                     |

| REFRQ, LLCAS, LUCAS, ULCAS, ULCAS,      | 1 Note 2     |                                | CBR self refreshNote 4              |

| RAS                                     | Note 3       |                                |                                     |

| HLDRQ                                   | Operates     |                                | Not accept                          |

| CLKOUT                                  | Clock outpu  | ut (when clock output is not   | 0                                   |

**Notes 1.** Each pin is in the operating status during DMA transfer.

- 2. Other than CBR refresh

- 3. The previous status is retained before CBR refresh is executed. This pin is set to "1" after CBR refresh.

- **4.** CBR self refresh is not executed when it is disabled. In this case, the status of this pin before the STOP mode is set is retained.

# 14. RESET/NMI CONTROL FUNCTION

The features of the reset/NMI control function are as follows:

- RESET and NMI pins have noise rejection circuit that samples clock.

- Performs forced reset, reset mask, and NMI mask processing from debug control unit

Table 14-1 shows the status of the output pins during the system reset period and immediately after reset. This status is retained during the reset period.

Table 14-1. Status of Output Pin Immediately after Reset

| Function                   | Operating Status |

|----------------------------|------------------|

| A1-A23                     | Undefined        |

| D0-D31                     | High impedance   |

| CS1-CS7                    | 1                |

| BCYST                      | 1                |

| IORD, IOWR                 | 1                |

| WE, OE                     | 1                |

| LLMWR, LUMWR, ULMWR, UUMWR | 1                |

| LLCAS, LUCAS, ULCAS, UUCAS | 1                |

| RAS                        | 1                |

| CLKOUT                     | Clock output     |

| HLDAK                      | 1                |

| DMAAKO-DMAAK3              | 1                |

| PORT2/SI                   | High impedance   |

| PORT1/SO                   | High impedance   |

| PORTO/SCLK                 | High impedance   |

| TXD                        | 1                |

| DDO                        | Undefined        |

| TRCDATA0-TRCDATA3          | Undefined        |

| TC/REFRQ                   | 1                |

| TO10/INTP10, TO11/INTP12   | High impedance   |

#### 15. INSTRUCTIONS

#### 15.1 Instruction Format

The V831 uses two instruction formats: 16-bit and 32-bit. The 16-bit instructions include binary operation, control, and conditional branch instructions, while the 32-bit instructions include load/store and I/O operation instructions, instructions for handling 16 bits of immediate data, and jump-and-link instructions.

Some instructions contain unused fields, which must be fixed to 0, which are provided for future use. When an instruction is actually loaded into memory, its configuration is as follows:

- Low-order part of each instruction format (including bit 0) → Low-order address

- High-order part of each instruction format (including bit 15 or 31) → High-order address

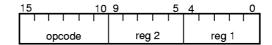

## (1) reg-reg instruction format [FORMAT I]

This instruction format has a six-bit operation code field and two general-purpose register designation fields for operand specification, giving a total length of 16 bits.

## (2) imm-reg instruction format [FORMAT II]

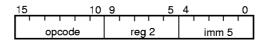

This instruction format has a six-bit operation code field, a five-bit immediate data field, and a general-purpose register designation field, giving a total length of 16 bits.

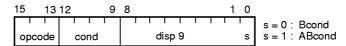

#### (3) Conditional branch instruction format [FORMAT III]

This instruction format has a three-bit operation code field, a four-bit condition code field, a nine-bit branch displacement field (bit 0 is handled as 0 and need not be specified), and a one-bit sub-operation code, giving a total length of 16 bits.

s: sub-opcode

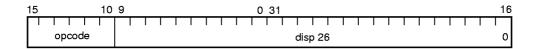

## (4) Medium-distance jump instruction format [FORMAT IV]

This instruction format has a six-bit operation code field and a 26-bit displacement field (the lowest-order bit must be 0), giving a total length of 32 bits.

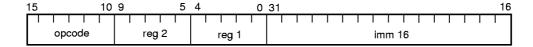

## (5) Three-operand instruction format [FORMAT V]

This instruction format has a six-bit operation code field, two general-purpose register designation fields, and a 16-bit immediate data field, giving a total length of 32 bits.

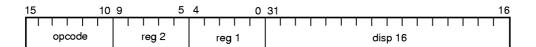

## (6) Load/store instruction format [FORMAT VI]

This instruction format has a six-bit operation code field, two general-purpose register designation fields, and a 16-bit displacement field, giving a total length of 32 bits.

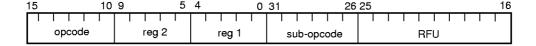

## (7) Extended instruction format [FORMAT VII]

This instruction format has a six-bit operation code field, two general-purpose register designation fields, and a six-bit sub-operation code field, giving a total length of 32 bits.

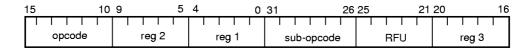

#### (8) Three-register operand instruction format [FORMAT VIII]

This instruction format has a six-bit operation code field, three general-purpose register designation fields, and a six-bit sub-operation code field, giving a total length of 32 bits.

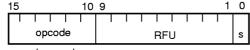

## (9) No-operand instruction format [FORMAT IX]

This instruction format has a six-bit operation code field and a one-bit sub-operation code field, giving a total length of 16 bits.

s : sub-opcode

# 15.2 Instructions (Listed Alphabetically)

The instructions are listed below in alphabetic order of their mnemonics.

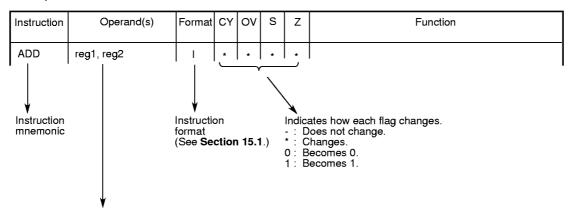

# Explanation of list format

## Abbreviations of operands

|              | ·                                                                                                                     |  |  |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Abbreviation | Meaning                                                                                                               |  |  |  |  |

| reg1         | General-purpose register (used as a source register)                                                                  |  |  |  |  |

| reg2         | General-purpose register (used mainly as a destination register, but in some instructions, used as a source register) |  |  |  |  |

| reg3         | General-purpose register (used mainly as a destination register, but in some instructions, used as a source register) |  |  |  |  |

| imm×         | × bits of immediate data                                                                                              |  |  |  |  |

| disp×        | x-bit displacement                                                                                                    |  |  |  |  |

| regID        | System register number                                                                                                |  |  |  |  |

| vector adr   | Trap handler address corresponding to trap vector                                                                     |  |  |  |  |

| Instruction | Operand(s)           | Format | CY | ov | s | Z | Function                                                                                      |

|-------------|----------------------|--------|----|----|---|---|-----------------------------------------------------------------------------------------------|

| ABC         | disp9                | 111    | -  | _  | - | - | High-speed conditional branch (if Carry) relative to PC.                                      |

| ABE         | disp9                | III    | _  | _  | - | _ | High-speed conditional branch (if Equal) relative to PC.                                      |

| ABGE        | disp9                | III    | -  | _  | - | _ | High-speed conditional branch (if Greater than or Equal) relative to PC.                      |

| ABGT        | disp9                | III    | -  | _  | - | _ | High-speed conditional branch (if Greater than) relative to PC.                               |

| ABH         | disp9                | III    | -  | -  | - | _ | High-speed conditional branch (if Higher) relative to PC.                                     |

| ABL         | disp9                | III    | -  | _  | - | _ | High-speed conditional branch (if Lower) relative to PC.                                      |

| ABLE        | disp9                | III    | -  | _  | - | _ | High-speed conditional branch (if Less than or Equal) relative to PC.                         |

| ABLT        | disp9                | III    | -  | _  | - | _ | High-speed conditional branch (if Less than) relative to PC.                                  |

| ABN         | disp9                | III    | _  | _  | - | _ | High-speed conditional branch (if Negative) relative to PC.                                   |

| ABNC        | disp9                | III    | -  | _  | - | _ | High-speed conditional branch (if Not Carry) relative to PC.                                  |

| ABNE        | disp9                | III    | -  | _  | - | _ | High-speed conditional branch (if Not Equal) relative to PC.                                  |

| ABNH        | disp9                | III    | -  | _  | - | _ | High-speed conditional branch (if Not Higher) relative to PC.                                 |

| ABNL        | disp9                | III    | -  | _  | - | _ | High-speed conditional branch (if Not Lower) relative to PC.                                  |

| ABNV        | disp9                | III    | -  | _  | - | _ | High-speed conditional branch (if Not Overflow) relative to PC.                               |

| ABNZ        | disp9                | III    | _  | _  | - | _ | High-speed conditional branch (if Not Zero) relative to PC.                                   |

| ABP         | disp9                | III    | -  | _  | - | - | High-speed conditional branch (if Positive) relative to PC.                                   |

| ABR         | disp9                | III    | -  | _  | - | - | High-speed unconditional branch (Always) relative to PC.                                      |

| ABV         | disp9                | III    | _  | _  | _ | _ | High-speed conditional branch (if Overflow) relative to PC.                                   |

| ABZ         | disp9                | III    | _  | _  | _ | _ | High-speed conditional branch (if Zero) relative to PC.                                       |

| ADD         | reg1, reg2           | I      | *  | *  | * | * | Addition. reg1 is added to reg2 and the sum is written into reg2.                             |

|             | imm5, reg2           | II     | *  | *  | * | * | Addition. imm5, sign-extended to a word, is added to reg2 and the sum is written into reg2.   |

| ADDI        | imm16,<br>reg1, reg2 | V      | *  | *  | * | * | Addition. imm16, sign-extended to a word, is added to reg1, and the sum is written into reg2. |

| Instruction | Operand(s)            | Format | CY | ΟV | s | Z | Function                                                                                          |

|-------------|-----------------------|--------|----|----|---|---|---------------------------------------------------------------------------------------------------|

| AND         | reg1, reg2            | I      | -  | 0  | * | * | AND. reg2 and reg1 are ANDed and the result is written into reg2.                                 |

| ANDI        | imm16,<br>reg1, reg2  | V      | -  | 0  | 0 | * | AND. reg1 is ANDed with imm16, zero-extended to a word, and result is written into reg2.          |

| ВС          | disp9                 | Ш      | _  | -  | - | _ | Conditional branch (if Carry) relative to PC.                                                     |

| BDLD        | [reg1], [reg2]        | VII    | -  | _  | - | _ | Block transfer. 4 words of data are transferred from external memory to built-in data RAM.        |

| BDST        | [reg2], [reg1]        | VII    | -  | -  | - | - | Block transfer. 4 words of data are transferred from built-in data RAM to external memory.        |

| BE          | disp9                 | Ш      | _  | -  | - | _ | Conditional branch (if Equal) relative to PC.                                                     |

| BGE         | disp9                 | Ш      | _  | _  | - | _ | Conditional branch (if Greater than or Equal) relative to PC.                                     |

| BGT         | disp9                 | Ш      | _  | _  | - | _ | Conditional branch (if Greater than) relative to PC.                                              |

| вн          | disp9                 | Ш      | _  | -  | - | _ | Conditional branch (if Higher) relative to PC.                                                    |

| BILD        | [reg1], [reg2]        | VII    | -  | _  | _ | - | Block transfer. 4 words of data are transferred from external memory to built-in instruction RAM. |

| BIST        | [reg2], [reg1]        | VII    | -  | _  | - | - | Block transfer. 4 words of data are transferred from built-in instruction RAM to external memory. |

| BL          | disp9                 | Ш      | _  | -  | - | _ | Conditional branch (if Lower) relative to PC.                                                     |

| BLE         | disp9                 | III    | _  | _  | - | _ | Conditional branch (if Less than or Equal) relative to PC.                                        |

| BLT         | disp9                 | Ш      | -  | -  | - | _ | Conditional branch (if Less than) relative to PC.                                                 |

| BN          | disp9                 | Ш      | _  | -  | _ | _ | Conditional branch (if Negative) relative to PC.                                                  |

| BNC         | disp9                 | Ш      | _  | -  | - | _ | Conditional branch (if Not Carry) relative to PC.                                                 |

| BNE         | disp9                 | Ш      | _  | -  | - | - | Conditional branch (if Not Equal) relative to PC.                                                 |

| BNH         | disp9                 | Ш      | _  | -  | - | _ | Conditional branch (if Not Higher) relative to PC.                                                |

| BNL         | disp9                 | Ш      | _  | -  | _ | _ | Conditional branch (if Not Lower) relative to PC.                                                 |

| BNV         | disp9                 | Ш      | -  | -  | - | - | Conditional branch (if Not Overflow) relative to PC.                                              |

| BNZ         | disp9                 | Ш      | _  | -  | - | - | Conditional branch (if Not Zero) relative to PC.                                                  |

| BP          | disp9                 | Ш      | _  | -  | - | _ | Conditional branch (if Positive) relative to PC.                                                  |

| BR          | disp9                 | Ш      | -  | -  | _ | _ | Unconditional branch (Always) relative to PC.                                                     |

| BRKRET      |                       | IX     | -  | -  | _ | _ | Return from fatal exception handling.                                                             |

| BV          | disp9                 | III    | _  | _  | _ | _ | Conditional branch (if Overflow) relative to PC.                                                  |

| BZ          | disp9                 | III    | _  | _  | _ | _ | Conditional branch (if Zero) relative to PC.                                                      |

| CAXI        | disp16[reg1],<br>reg2 | VI     | *  | *  | * | * | Inter-processor synchronization in multi-<br>processor system.                                    |

| Instruction | Operand(s)            | Format | CY | ov | s | Z | Function                                                                                                                                                                                                                                                                    |

|-------------|-----------------------|--------|----|----|---|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| СМР         | reg1, reg2            | I      | *  | *  | * | * | Comparison. reg2 is compared with reg1 sign-extended to a word and the condition flag is set according to the result.  The comparison involves subtracting reg1 from reg2.                                                                                                  |

|             | imm5, rag2            | II     | *  | *  | * | * | Comparison. reg2 is compared with imm5 sign-extended to a word and the condition flag is set according to the result.  The comparison involves subtracting imm5, sign-extended to a word, from reg2.                                                                        |

| DI          |                       | II     | -  | _  | - | _ | Disable interrupt. Maskable interrupts are disabled. DI instruction cannot disable nonmaskable interrupts.                                                                                                                                                                  |

| DIV         | reg1, reg2            | I      | _  | *  | * | * | Division of signed operands. reg2 is divided by reg1 (signed operands).  The quotient is stored in reg2 and the remainder in r30. The division is performed so that the sign of the remainder will match that of the dividend.                                              |

| DIVU        | reg1, reg2            |        | _  | 0  | * | * | Division of unsigned operands. reg2 is divided by reg1 (unsigned operands). The quotient is stored in reg2 and the remainder in r30. The division is performed so that the sign of the remainder will match that of the dividend.                                           |

| EI          |                       | II     | _  | _  | _ | _ | Enable interrupt. Maskable interrupts are enabled. The El instruction cannot enable nonmaskable interrupts.                                                                                                                                                                 |

| HALT        |                       | IX     | -  | -  | - | _ | Processor halt. The processor is placed in sleep mode.                                                                                                                                                                                                                      |

| IN.B        | disp16[reg1],<br>reg2 | VI     | _  | _  | _ | _ | Port input. disp16, sign-extended to a word, is added to reg1 to produce an unsigned 32-bit port address. A byte of data is read from the resulting port address, zero-extended to a word, then stored in reg2.                                                             |

| IN.H        | disp16[reg1],<br>reg2 | VI     | _  | _  | _ | _ | Port input. disp16, sign-extended to a word, is added to reg1 to produce an unsigned 32-bit port address. A halfword of data is read from the produced port address, zero-extended to a word, and stored in reg2. Bit 0 of the unsigned 32-bit port address is masked to 0. |

| IN.W        | disp16[reg1],<br>reg2 | VI     | _  | _  | _ | - | Port input. disp16, sign-extended to a word, is added to reg1 to produce an unsigned 32-bit port address. A word of data is read from the resulting port address, then written into reg2.  Bits 0 and 1 of the unsigned 32-bit port address are masked to 0.                |

| Instruction | Operand(s)            | Format | CY | ΟV | s | z | Function                                                                                                                                                                                                                                                            |

|-------------|-----------------------|--------|----|----|---|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JAL         | disp26                | IV     | -  | -  | - | - | Jump and link. The sum of the current PC and 4 is written into r31. disp26, sign-extended to a word, is added to the PC and the sum is set to the PC for control transfer. Bit 0 of disp26 is masked.                                                               |

| JMP         | [reg1]                | I      | _  | _  | _ | _ | Indirect unconditional branch via register.  Control is passed to the address designated by reg1. Bit 0 of the address is masked to 0.                                                                                                                              |

| JR          | disp26                | IV     | -  | -  | - | - | Unconditional branch. disp26, sign-extended to a word, is added to the current PC and control is passed to the address specified by that sum. Bit 0 of disp26 is masked to 0.                                                                                       |

| LD.B        | disp16[reg1],<br>reg2 | VI     | -  | -  | - | _ | Byte load. disp16, sign-extended to a word, is added to reg1 to produce an unsigned 32-bit address. A byte of data is read from the produced address, sign-extended to a word, then written into reg2.                                                              |

| LD.H        | disp16[reg1],<br>reg2 | VI     | -  | ı  | _ | - | Halfword load. disp16, sign-extended to a word, is added to reg1 to produce an unsigned 32-bit address. A halfword of data is read from the produced address, sign-extended to a word, then written into reg2. Bit 0 of the unsigned 32-bit address is masked to 0. |

| LD.W        | disp16[reg1],<br>reg2 | VI     | -  | -  | - | - | Word load. disp16, sign-extended to a word, is added to reg1 to produce an unsigned 32-bit address. A word of data is read from the produced address, then written into reg2. Bits 0 and 1 of the unsigned 32-bit address are masked to 0.                          |

| LDSR        | reg2, regID           | II     | *  | *  | * | * | Load into system register. The contents of reg2 are set in the system register identified by the system register number (regID).                                                                                                                                    |

| МАСЗ        | reg1, reg2,<br>reg3   | VIII   | _  | _  | _ | - | Saturatable operation on signed 32-bit operands. reg1 and reg2 are multiplied together as signed integers and the product is added to reg3.                                                                                                                         |

|             |                       |        |    |    |   |   | [If no overflow has occurred:]  The result is stored in reg3.                                                                                                                                                                                                       |

|             |                       |        |    |    |   |   | [If an overflow has occurred:]  The SAT bit is set. If the result is positive, the positive maximum is written into reg3; if the result is negative, the negative maximum is written into reg3.                                                                     |

| Instruction | Operand(s)           | Format | CY | ΟV | s | Z | Function                                                                                                                                                                                                         |

|-------------|----------------------|--------|----|----|---|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MACI        | imm16,<br>reg1, reg2 | V      | -  | -  | - | - | Sum-of-products operation on signed 32-bit operands. reg1 and imm16, sign-extended to 32 bits, are multiplied together as signed integers and the product is added to reg2 as a signed integer.                  |

|             |                      |        |    |    |   |   | [If no overflow has occurred:]  The result is written into reg2.                                                                                                                                                 |

|             |                      |        |    |    |   |   | [If an overflow has occurred:]  The SAT bit is set. If the result is positive, the positive maximum is written into reg2; if the result is negative, the negative maximum is written into reg2.                  |

| МАСТЗ       | reg1, reg2,<br>reg3  | VIII   | _  | -  | - | _ | Saturatable operation on signed 32-bit operands. reg1 and reg2 are multiplied together as signed integers and the high-order 32 bits of the product are added to reg3 as signed integers.                        |

|             |                      |        |    |    |   |   | [If no overflow has occurred:]  The result is written into reg3.                                                                                                                                                 |

|             |                      |        |    |    |   |   | [If an overflow has occurred:]  The SAT bit is set. If the result is positive, the positive maximum is written into reg3; if the result is negative, the negative maximum is written into reg3.                  |

| MAX3        | reg1, reg2,<br>reg3  | VIII   | _  | _  | _ | _ | Maximum. reg2 and reg1 are compared as signed integers. The larger value is written into reg3.                                                                                                                   |

| MIN3        | reg1, reg2,<br>reg3  | VIII   | -  | -  | - | - | Minimum. reg2 and reg1 are compared as signed integers. The smaller value is written into reg3.                                                                                                                  |

| MOV         | reg1, reg2,          | I      | -  | -  | - | - | Data transfer. reg1 is copied to reg2 for data transfer.                                                                                                                                                         |

|             | imm5, reg2           | II     | -  | -  | - | - | Data transfer. imm5, sign-extended to a word, is copied into reg2 for data transfer.                                                                                                                             |

| MOVEA       | imm16,<br>reg1, reg2 | V      | -  | -  | - | _ | Addition. The high-order 16 bits (imm16), sign-extended to a word, are added to reg1 and the sum is written into reg2.                                                                                           |

| MOVHI       | imm16,<br>reg1, reg2 | V      | _  | -  | - | _ | Addition. A word consisting of the high-order 16 bits (imm16) and low-order 16 bits (0) is added to reg1 and the sum is written into reg2.                                                                       |

| MUL         | reg1, reg2           | ı      | -  | *  | * | * | Multiplication of signed operands, reg2 and reg1 are multiplied together as signed values. The high-order 32 bits of the product (double word) are written into r30 and low-order 32 bits are written into reg2. |

| MUL3        | reg1, reg2,<br>reg3  | VIII   | _  | _  | _ | _ | Multiplication of signed 32-bit operands. reg2 and reg1 are multiplied together as signed integers. The high-order 32 bits of the product are written into reg3.                                                 |

| Instruction | Operand(s)            | Format | CY | ΟV | s | Z | Function                                                                                                                                                                                                                                                   |

|-------------|-----------------------|--------|----|----|---|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MULI        | imm16,<br>reg1, reg2  | V      | -  | -  | _ | - | Saturatable multiplication of signed 32-bit operands. reg1 and imm16, sign-extended to 32 bits, are multiplied together as signed integers.                                                                                                                |

|             |                       |        |    |    |   |   | [If no overflow has occurred:]  The result is written into reg2.                                                                                                                                                                                           |

|             |                       |        |    |    |   |   | [If an overflow has occurred:]  The SAT bit is set. If the result is positive, the positive maximum is written into reg2; if the result is negative, the negative maximum is written into reg2.                                                            |

| MULT3       | reg1, reg2,<br>reg3   | VIII   | _  | -  | - | _ | Saturatable multiplication of signed 32-bit operands. reg1 and reg2 are multiplied together as signed integers. The high-order 32 bits of the product are written into reg3.                                                                               |

| MULU        | reg1, reg2            | I      | _  | *  | * | * | Multiplication of unsigned operands. reg1 and reg2 are multiplied together as unsigned values. The high-order 32 bits of the product (double word) are written into r30 and the low-order 32 bits are written into reg2.                                   |

| NOP         |                       | III    | _  | _  | _ | _ | No operation.                                                                                                                                                                                                                                              |

| NOT         | reg1, reg2            | 1      | -  | 0  | * | * | NOT. The NOT (ones complement) of reg1 is taken and written into reg2.                                                                                                                                                                                     |

| OR          | reg1, reg2            | 1      | -  | 0  | * | * | OR. The OR of reg2 and reg1 is taken and written into reg2.                                                                                                                                                                                                |

| ORI         | imm16,<br>reg1, reg2  | V      | -  | 0  | * | * | OR. The OR of reg1 and imm16, zero-<br>extended to a word, is taken and written into<br>reg2.                                                                                                                                                              |

| OUT.B       | reg2,<br>disp16[reg1] | VI     | _  | _  | _ | _ | Port output. disp16, sign-extended to a word, is added to reg1 to produce an unsigned 32-bit port address. The low-order one byte of the data in reg2 is output to the resulting port address.                                                             |

| OUT.H       | reg2,<br>disp16[reg1] | VI     | -  | -  | - | - | Port output. disp16, sign-extended to a word, is added to reg1 to produce an unsigned 32-bit port address. The low-order two bytes of the data in reg2 are output to the resulting port address. Bit 0 of the unsigned 32-bit port address is masked to 0. |

| OUT.W       | reg2,<br>disp16[reg1] | VI     | -  | -  | - | - | Port output. disp16, sign-extended to a word, is added to reg1 to produce an unsigned 32-bit port address. The word of data in reg2 is output to the produced port address. Bits 0 and 1 of the unsigned 32-bit port address are masked to 0.              |

| RETI        |                       | IX     | *  | *  | * | * | Return from trap/interrupt handling routine. The return PC and PSW are read from the system registers so that program execution will return from the trap or interrupt handling routine.                                                                   |

| Instruction | Operand(s)          | Format | CY | ΟV | s | Z | Function                                                                                                                                                                                                                                                      |

|-------------|---------------------|--------|----|----|---|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SAR         | reg1 ,reg2          | I      | *  | 0  | * | * | Arithmetic right shift. reg2 is arithmetically shifted to the right by the displacement specified by the low-order five bits of reg1 (MSB value is copied to the MSB in sequence). The result is written into reg2.                                           |

|             | imm5, reg2          | II     | *  | 0  | * | * | Arithmetic right shift. reg2 is arithmetically shifted to the right by the displacement specified by imm5, zero-extended to a word. The result is written into reg2.                                                                                          |

| SATADD3     | reg1, reg2,<br>reg3 | VIII   | *  | *  | * | * | Saturatable addition. reg1 and reg2 are added together as signed integers.                                                                                                                                                                                    |

|             |                     |        |    |    |   |   | [If no overflow has occurred:] The result is written into reg3.                                                                                                                                                                                               |

|             |                     |        |    |    |   |   | [If an overflow has occurred:]  The SAT bit is set. If the result is positive, the positive maximum is written into reg3; if the result is negative, the negative maximum is written into reg3.                                                               |

| SATSUB3     | reg1, reg2,<br>reg3 | VIII   | *  | *  | * | * | Saturatable subtraction. reg1 is subtracted from reg2 as signed integers.                                                                                                                                                                                     |