### Description

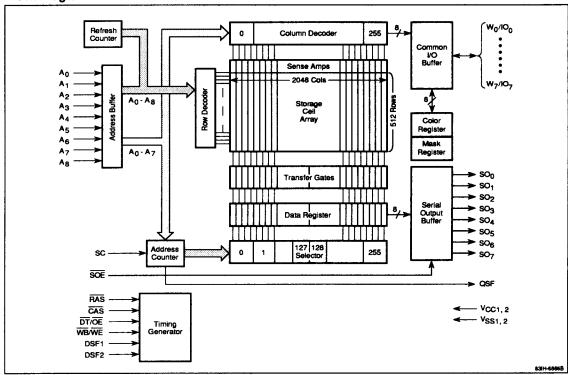

The  $\mu$ PD42275 is a dual-port graphics buffer equipped with a random access port and a serial read port. The serial read port is connected to an internal 2048-bit data register through a 256 x 8-bit serial read output circuit. The 128K x 8-bit random access port is used by the host CPU to read or write data addressed in any desired order.

A write-per-bit capability allows each of the eight data bits to be individually selected or masked for a write cycle. Block write cycles can also be used to write the eight data bits to four consecutive column addresses. Selection and masking of the eight data bits and four column addresses is provided. A flash write option with write-per-bit control enables data in the color register to be written to a selected row in the random access port.

The µPD42275 features fully asynchronous dual access, except when transferring graphics data from a selected row of the storage array to the data register. During a data transfer, the random access port requires a special cycle using a transfer clock; the serial port continues to operate normally. Following the clock transition of a data transfer, serial output data changes from an old line to a new line and the starting location on the new line is addressable in the data transfer cycle.

An advanced CMOS silicon-gate process using polycide technology and trench capacitors provides high storage cell density, high performance, and high reliability. Refreshing is accomplished by means of RAS-only refresh cycles or by normal read or write cycles on the 512 address combinations of  $A_0$  through  $A_8$  during an 8-ms period. Automatic internal refreshing, by means of either hidden refreshing or the  $\overline{\text{CAS}}$  before  $\overline{\text{RAS}}$  timing and on-chip internal refresh circuitry, is also available. The transfer of a row of data from the storage array to the data register also refreshes that row automatically.

All inputs and outputs, including clocks, are TTL-compatible. All address and data-in signals are latched on-chip to simplify system design. Data-out is unlatched to allow greater system flexibility. The  $\mu$ PD42275 is available in a 400-mil, 40-pin plastic SOJ and is guaranteed for operation at 0 to +70°C.

#### **Features**

- □ Three functional blocks

- 128K x 8-bit random access storage array

- 2048-bit data register

- 256 x 8-bit serial read output circuit

- Two data ports: random access and serial read

- Dual-port accessibility except during data transfer

- Addressable start of serial read operation

- □ Real-time data transfer

- On-chip substrate bias generator

- Random access port

- -Two main clocks: RAS and CAS

- Multiplexed address inputs

- Direct connection of I/O and address lines allowed by OE to simplify system design

- 512 refresh cycles every 8 ms

- Read, early write, late write, read-write/readmodify-write, RAS-only refresh, and fast-page cycles

- Automatic internal refreshing by means of the <del>CAS</del> before <del>RAS</del> on-chip address counter

- CAS-controlled hidden refreshing

- Persistent and nonpersistent write-per-bit option regarding eight I/O bits

- Write bit selection multiplexed on IO<sub>0</sub> IO<sub>7</sub>

- Block write option with write-per-bit control and column mask function

- Flash write option with write-per-bit control

- Split serial data register to allow shifting from lower half while simultaneously loading upper half

- RAS-activated data transfer

- Same cycle time as for random access

- Row data transferred to data register as specified by row address inputs

- Starting location of following serial read cycle specified by column address inputs

- Transfer of 2048 bits of data on one row to the data register, and the starting location of the serial read circuit, activated by a low-to-high transition of DT

- Data transfer during real-time operation or standby of serial port

- □ Fast serial read operation by means of SC pins

- □ Serial data output on SO<sub>0</sub> SO<sub>7</sub>

- Direct connection of multiple serial outputs for extension of data length

- □ Fully TTL-compatible inputs, outputs, and clocks

- Three-state outputs for random and serial access

- CMOS silicon-gate process with trench capacitors

12F - 1

## **Block Diagram**

#### Pin Identification

| Function                                      |

|-----------------------------------------------|

| Address inputs                                |

| Write-per-bit selects/data inputs and outputs |

| Row address strobe                            |

| Column address strobe                         |

| Write-per-bit/write enable                    |

| Data transfer/output enable                   |

| Special function enable                       |

| Serial read outputs                           |

| Serial control                                |

| Serial output enable                          |

| Special function output                       |

| Ground                                        |

| +5-volt ±10% power supply                     |

| No connection                                 |

|                                               |

## **Ordering Information**

| Part Number   | Row Access<br>Time (max) | Serial Access<br>Time (max) | Package        |

|---------------|--------------------------|-----------------------------|----------------|

| μPD42275LE-80 | 80 ns                    | 25 ns                       | 40-pin plastic |

| LE-10         | 100 ns                   | 25 ns                       | SOI            |

| LE-12         | 120 ns                   | 40 ns                       | •              |

#### Pin Configuration

#### 40-Pin Plastic SOJ

| SC   1                                                                                                                                           |                                                                                                                                                                                                                                                                                                  |                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| RAS   14   27   CAS   DSF2   15   26   QSF   A8   16   25   A0   A6   17   24   A1   A5   18   23   A2   A4   19   22   A3   VCC2   20   21   A7 | SO <sub>0</sub> □ 2<br>SO <sub>1</sub> □ 3<br>SO <sub>2</sub> □ 4<br>SO <sub>3</sub> □ 5<br>DT/O∈ 0 6<br>W <sub>0</sub> /IO <sub>0</sub> □ 7<br>W <sub>1</sub> /IO <sub>1</sub> □ 8<br>W <sub>2</sub> /IO <sub>2</sub> □ 9<br>W <sub>3</sub> /IO <sub>3</sub> □ 10 22<br>V <sub>CC1</sub> □ 11 0 | 39                                     |

| A <sub>8</sub>                                                                                                                                   | NC ☐ 13<br>RAS ☐ 14                                                                                                                                                                                                                                                                              | 28 NC<br>27 CAS                        |

| A <sub>4</sub> □ 19 22 □ A <sub>3</sub> V <sub>CC2</sub> □ 20 21 □ A <sub>7</sub>                                                                | A <sub>8</sub> ☐ 16<br>A <sub>6</sub> ☐ 17                                                                                                                                                                                                                                                       | 25 A <sub>0</sub><br>24 A <sub>1</sub> |

|                                                                                                                                                  | A4 ☐ 19                                                                                                                                                                                                                                                                                          | 22 A <sub>3</sub>                      |

| 83H-6865A                                                                                                                                        |                                                                                                                                                                                                                                                                                                  | 83IH-6865A                             |

#### Pin Functions

A<sub>0</sub>-A<sub>8</sub> (Address Inputs). These pins are multiplexed as row and column address inputs. Each of eight data bits in the random access port corresponds to 131,072 storage cells, which means that nine row addresses and eight column addresses are required to decode one cell location. Nine row addresses are first used to select one of the 512 possible rows for a read, write, data transfer, or refresh cycle. Eight column addresses are then used to select the one of 256 possible column decoders for a read or write cycle or the one of 256 possible starting locations for the next serial read cycle. (Column addresses are not required in RAS-only refresh cycles.)

W<sub>0</sub>/IO<sub>0</sub>-W<sub>7</sub>/IO<sub>7</sub> (Write-Per-Bit Inputs/Common Data Inputs and Outputs). Each of the eight data bits can be individually latched by these inputs at the falling edge of RAS in any write cycle, and then updated at the next falling edge of RAS. In a read cycle, these pins serve as outputs for the selected storage cells. In a write cycle, data input on these pins is latched by the falling edge of CAS or WE.

RAS (Row Address Strobe). This pin is functionally equivalent to a chip enable signal in that whenever it is activated, the 2048 storage cells of a selected row are

sensed simultaneously and the sense amplifiers restore all data. The nine row address bits are latched by this signal and must be stable on or before its falling edge. CAS, DT/OE, WB/WE, DSF<sub>1</sub> and DSF<sub>2</sub> are simultaneously latched to determine device operation.

CAS (Column Address Strobe). This pin serves as a chip selection signal to activate the column decoder and the input/output buffers. The eight column address bits are latched at the falling edge of CAS.

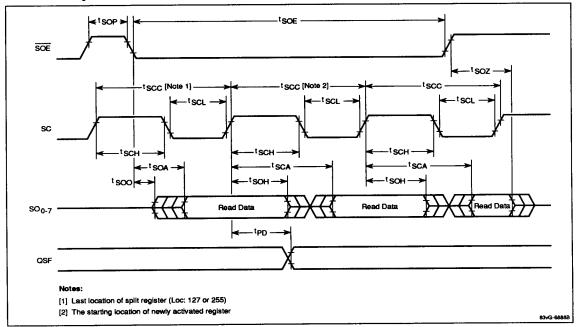

QSF (Special Function Output). This pin indicates which side of the split register is active. QSF high shows that the upper half (addresses 128 through 255) is active, while QSF low indicates the lower half (addresses 0 through 127).

DSF<sub>1</sub> and DSF<sub>2</sub> (Special Function Control). At the leading edge of RAS and CAS, the high or low level of these pins is latched to initiate one of the operations shown in the Truth Table. Holding both pins low causes the device to operate without any special functions.

WB/WE (Write-Per-Bit Control/Write Enable). At the falling edge of RAS, the WB/WE and DSF<sub>1</sub> inputs must be low and CAS and DT/OE high to enable the write-per-bit option. When CAS, DT/OE, and DSF<sub>1</sub> are high at the falling edge of RAS, the level of this signal indicates either a color register set cycle or flash write cycle. A high WB/WE can be used at the beginning of a standard write or read cycle.

$\overline{\text{DT}}/\overline{\text{OE}}$  (Data Transfer/Output Enable). At the  $\overline{\text{RAS}}$  falling edge,  $\overline{\text{CAS}}$  and  $\overline{\text{WB}}/\overline{\text{WE}}$  high and  $\overline{\text{DT}}/\overline{\text{OE}}$  low initiate a data transfer.  $\overline{\text{DT}}/\overline{\text{OE}}$  high initiates conventional read or write cycles and controls the output buffer in the random access port. The level of DSF<sub>1</sub> determines whether this is a read or split read data transfer.

SO<sub>0</sub>-SO<sub>7</sub> (Serial Data Outputs). Eight-bit data is read from these pins and remains valid until the next SC signal is activated.

SC (Serial Control). Repeatedly activating this signal causes serial read cycles (starting from the location specified in the data transfer cycle) to be executed within the 2048 bits in the data register. The rising edge of SC activates serial read operation, in which 8 of the 2048 data bits are transferred to eight serial data buses, respectively, and read out. Whenever SC is low, the serial port is in standby.

SOE (Serial Output Enable). This signal controls the serial data output buffer.

#### **OPERATION**

The µPD42275 consists of a random access port and a serial read port. The random access port executes standard read and write cycles, as well as data transfer, block write and flash write cycles, all of which are based on conventional PAS/CAS timing.

In a data transfer, data in each storage cell on the selected row is transferred simultaneously through a transfer gate to its corresponding register location. The serial read port shows the contents of the data register in serial order. The random access and serial read ports can operate asynchronously, except when the transfer gate is turned on during the data transfer period.

#### Addressing

The storage array is arranged in a 512-row by 2048-column matrix, whereby each of 8 data bits in the random access port corresponds to 131,072 storage cells and 17 address bits are required to decode one cell location. Nine row address bits are set up on pins  $A_0$  through  $A_8$  and latched onto the chip by  $\overline{RAS}$ . Eight column address bits then are set up on pins  $A_0$  through  $A_7$  and latched onto the chip by  $\overline{CAS}$ . All addresses must be stable, on or before the falling edges of  $\overline{RAS}$  and  $\overline{CAS}$ . Whenever  $\overline{RAS}$  is activated, 2048 cells on the selected row are sensed simultaneously and the sense amplifiers automatically restore the data.  $\overline{CAS}$  serves as a chip selection signal to activate the column decoder and the input and output buffers.

Through one of 256 column decoders, eight storage cells on the row are connected to eight data buses, respectively. In a data transfer cycle, 9 row address bits are used to select one of the 512 possible rows involved in the transfer of data to the data register. Eight column address bits are then used to select the one of 256 possible serial decoders that corresponds to the starting location of the next serial read cycle. In the serial read port, when SC is activated, 8 data bits in the 2048-bit data register are transferred to eight serial data buses and read out. Activating SC repeatedly causes serial read cycles (starting from the location specified in the data transfer cycle) to be executed within the 2048 bits in the data register.

#### Random Access Port

An operation in the random access port begins with a negative transition of RAS. Both RAS and CAS have minimum pulse widths, as specified in the timing table, which must be maintained for proper device operation and data integrity. Once begun, a cycle must meet

all specifications, including minimum cycle time. To reduce the number of pins, the following are multiplexed.

- DT/OE

- WB/WE

- $W_i/IO_i$  (i = 0, 1, 2, 3, 4, 5, 6, 7)

The  $\overline{OE}$ ,  $\overline{WE}$ , and  $\overline{IO}_i$  functions represent standard operations, while  $\overline{DT}$ ,  $\overline{WB}$ , and  $W_i$  are special inputs to be applied in the same way as row address inputs with setup and hold times referenced to the negative transition of  $\overline{RAS}$ .

The level of  $\overline{DT}$  determines whether a cycle is a random access operation or a data transfer operation.  $\overline{WB}$  affects only write cycles and determines whether or not the write-per-bit capability is used. W<sub>i</sub> defines data bits to be written with the write-per-bit option. In the following discussions, these multiplexed pins are designated as  $\overline{DT}(\overline{OE})$ , for example, depending on the function being described.

To use the  $\mu$ PD42275 for random access,  $\overline{DT}(\overline{OE})$  must be high as RAS falls. Holding  $\overline{DT}(\overline{OE})$  high disconnects the 2048-bit register from the corresponding 2048-digit lines of the storage array. Conversely, to execute a data transfer,  $\overline{DT}(\overline{OE})$  must be low as RAS falls to open the 2048 transfer gates and transfer data from one of the rows to the register.

### **Glossary of Special Functions**

Masked Write Cycle with New Mask. When the write-per-bit function is enabled as shown in the following table, mask data on the W/IO $_{\rm I}$  pins is latched by  $\overline{\rm RAS}$  and loaded directly into the write mask register. A masked write cycle is then executed using  $\overline{\rm CAS}$  or  $\overline{\rm WB}/\overline{\rm WE}$  to strobe the W/IO $_{\rm I}$  data into the on-chip data latch.

#### Write-Per-Bit Function

| Mask Register Data | Action       |   |

|--------------------|--------------|---|

| 1                  | Write        | _ |

| 0                  | Do not write |   |

Write Mask Register Set Cycle. In this cycle, data on W<sub>i</sub>/IO<sub>i</sub> is written to an 8-bit write mask register, where it is retained and used by subsequent masked write and masked block write cycles.

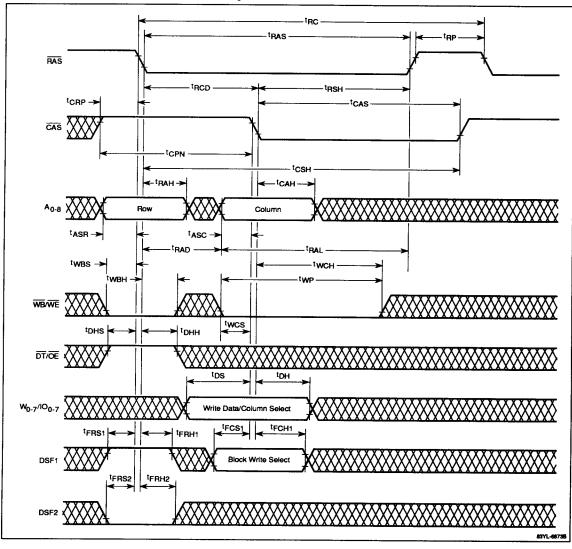

Masked Write Cycle with Old Mask. This write-per-bit cycle, commonly referred to as a persistent mask write cycle, uses the mask data previously set by the last write mask register set cycle.

#### **Truth Table for Random Access Port**

|                                 | Musi | Be Valid | at Falling | g Edge o         | f RAS            | Must be Valid at Falling Edge of CAS |               |

|---------------------------------|------|----------|------------|------------------|------------------|--------------------------------------|---------------|

| Cycle                           | CAS  | DT/OE    | WB/WE      | DSF <sub>1</sub> | DSF <sub>2</sub> | DSF <sub>1</sub>                     | Mnemonic Code |

| Read/write cycle                | н    | Н        | Н          | L                | Х                | L                                    | RW            |

| Block write cycle               | н    | н        | Н          | L                | Х                | Н                                    | BW            |

| Write mask register set cycle   | Н    | Н        | Н          | Н                | Х                | L                                    | LWR           |

| Color register set cycle        | Н    | н        | Н          | н                | Х                | Н                                    | LCR           |

| Write cycle with new mask       | Н -  | Н        | L          | L                | Х                | L                                    | RWNM          |

| Block write cycle with new mask | Н    | Н        | L          | L                | Х                | Н                                    | BWNM          |

| Write cycle with old mask       | Н    | Н        | L          | Н                | L                | L                                    | RWOM          |

| Block write cycle with old mask | Н    | Н        | L          | н                | L                | Н                                    | BWOM          |

| Read data transfer cycle        | Н    | L        | Н          | L                | Х                | X                                    | RT            |

| Split read data transfer cycle  | Н    | L        | Н          | Н                | Х                | X                                    | SRT           |

| CAS before RAS refresh cycle    | L    | Х        | Н          | Х                | Х                | ×                                    | CBR           |

| Flash write cycle with new mask | Н    | Н        | L          | Н                | Н                | X                                    | FWT           |

#### Notes:

- (1) X = don't care.

- (2) Combinations not shown are used for refresh operation.

#### **Block Write Addresses**

| te    | $A_1 = 1, A_0 = 1$ |

|-------|--------------------|

|       |                    |

| write |                    |

| te    | $A_1 = 1, A_0 = 0$ |

| Write |                    |

| te    | $A_1 = 0, A_0 = 1$ |

| write |                    |

| te    | $A_1 = 0, A_0 = 0$ |

| write |                    |

|       |                    |

#### Notes:

(1) Data on  $1/O_7$  -  $1/O_4$  are don't care at the falling edge of  $\overline{CAS}$ .

Color Register Set Cycle. This cycle is executed in the same fashion as a conventional read or write cycle, with a read or write cycle available to the color register under the control of  $\overline{WE}$ . In read operation, color register data is read on the common  $W_f|O_1$  pins. In write operation, common  $W_f|O_1$  data can be written into the color register.  $\overline{RAS}$ -only refreshing is internally performed on the row selected by  $A_0$  through  $A_8$ . This setup cycle precedes the first flash write or block write cycle supplying the 8 write data bits.

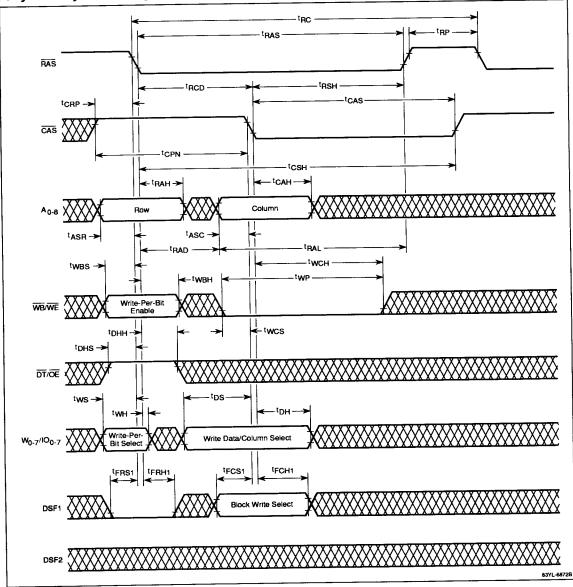

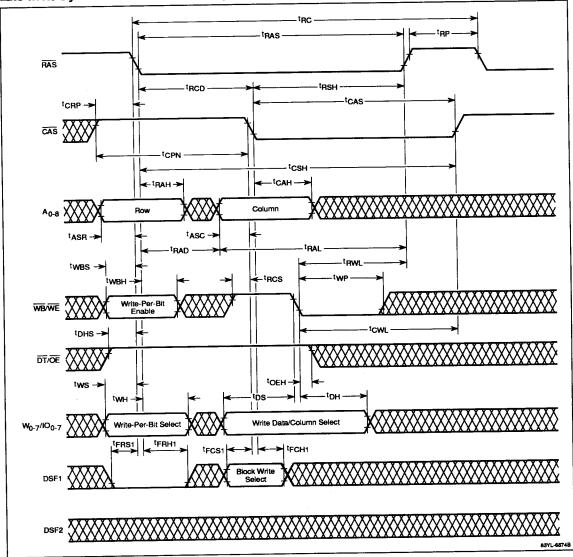

**Block Write Cycle.** In a block write cycle,  $A_1$  and  $A_0$  are ignored.  $I/O_0$  -  $I/O_3$  are used to select one or a combination of four column addresses for writing in an early

write, late write, page early write, or page late write cycle. Block write data is previously stored in the color register using a set color register cycle. Column select data is latched by the W/IO<sub>i</sub> pins at the falling edge of CAS or WE. Block write cycles are useful for clearing windows and for accelerating polygon fill operations.

Masked Block Write Cycle with New Mask. This cycle allows for W/I/O<sub>0</sub> - W/I/O<sub>7</sub> masking during a block write cycle. The masking function is identical to a standard masked write cycle with new mask, except that four consecutive columns are written.

Masked Block Write Cycle with Old Mask. This cycle uses the masked data previously set by the last write mask register set cycle to write four consecutive columns.

Flash Write Cycle. A flash write cycle can clear or set each of the eight 256-bit data sets on the selected one of 512 possible rows according to data stored in the previously set color register. Bit mask inputs are latched as RAS. This cycle is useful in graphics processing applications when the screen should be cleared or set to some uniform value as quickly as possible.

Read Data Transfer Cycle. In a full row read data transfer cycle, one of the possible 512 rows, as well as the starting location of the following serial read cycle, is defined by address inputs. The low-to-high transition of DT/(OE) causes the 2048 bits of cell data to be transferred to the serial data register.

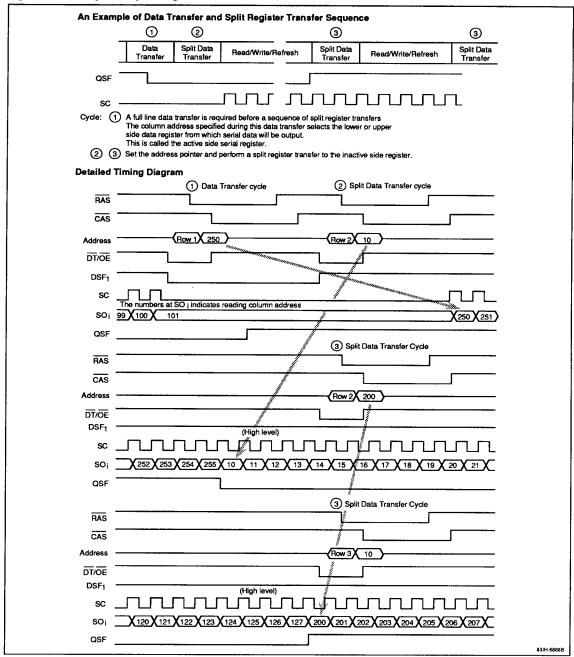

Split Read Transfer Cycle. This cycle is a half-row data transfer in which one of the 512 rows, the starting location of the following serial read cycle, and either of the split registers are specified by the address inputs. On-chip control circuitry causes the previously specified half row to be transferred to the selected upper or lower split register.

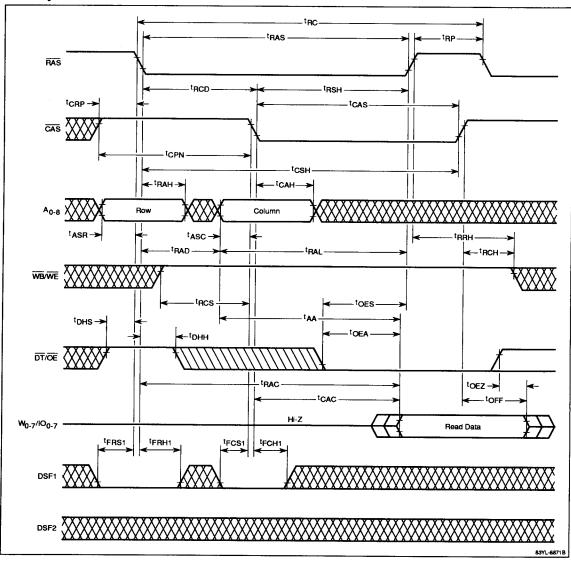

Read Cycle. A read cycle is executed by activating RAS, CAS, and OE and by maintaining (WB/)WE while CAS is active. The (W<sub>i</sub>/)IO<sub>i</sub> pin (i = 0 through 7) remains in high impedance until valid data appears at the output at access time. Device access time, t<sub>ACC</sub>, will be the longest of the following four calculated intervals:

- tpac

- RAS to CAS delay (t<sub>RCD</sub>) + t<sub>CAC</sub>

- RAS to column address delay (t<sub>RAD</sub>) + t<sub>AA</sub>

- RAS to OE delay + t<sub>OEA</sub>

Access times from  $\overline{\text{RAS}}$  ( $t_{\text{RAC}}$ ), from  $\overline{\text{CAS}}$  ( $t_{\text{CAC}}$ ), from the column addresses ( $t_{\text{AA}}$ ), and from  $\overline{\text{OE}}$  ( $t_{\text{CEA}}$ ) are device parameters. The  $\overline{\text{RAS}}$ -to- $\overline{\text{CAS}}$ ,  $\overline{\text{RAS}}$ -to-column address, and  $\overline{\text{RAS}}$ -to- $\overline{\text{OE}}$  delays are system-dependent timing parameters. Output becomes valid after the access time has elapsed and it remains valid while both  $\overline{\text{CAS}}$  and  $\overline{\text{OE}}$  are low. Either  $\overline{\text{CAS}}$  or  $\overline{\text{OE}}$  high returns the output pins to high impedance.

**Write Cycle.** A write cycle is executed by bringing  $\overline{(WB)/WE}$  low during the  $\overline{AAS/CAS}$  cycle. The falling edge of  $\overline{CAS}$  or  $\overline{(WB)/WE}$  strobes the data on  $\overline{(W_i/)O_i}$  into the on-chip data latch. To make use of the write-per-bit option,  $\overline{WB}/\overline{WE}$  must be low as  $\overline{AAS}$  falls. In this case, write data bits can be specified by keeping  $\overline{W_i/(O_i)}$  high, with setup and hold times referenced to the negative transition of  $\overline{RAS}$ .

**Write-Per-Bit Cycle.** The falling edge of  $\overline{\text{RAS}}$  latches the write-per-bit mask data input on  $W_0$  through  $W_7$ . If DSF<sub>1</sub> is low at the falling edge of  $\overline{\text{RAS}}$ , mask data must be reloaded every write-per-bit mask cycle. If DSF<sub>1</sub> is high and DSF<sub>2</sub> is low at the falling edge of  $\overline{\text{RAS}}$ , mask data is not reloaded from  $W_0$  through  $W_7$  but is retained from the previous write mask set cycle. The latter is called a persistent write-per-bit cycle.

Early Write Cycle. An early write cycle is executed by bringing (WB/)WE low before CAS falls. Data is strobed by CAS, with setup and hold times referenced to this signal, and the output remains in high impedance for the entire cycle. As RAS falls, (DT/)OE must meet the setup and hold times of a high DT, but otherwise (DT/)OE does not affect any circuit operation while CAS is active.

Read-Write/Read-Modify-Write Cycle. This cycle is executed by bringing  $(\overline{WB})/\overline{WE}$  low with the RAS and CAS signals low.  $(W_i/)|O_i|$  shows read data at access time. Afterward, in preparation for the upcoming write cycle,  $(W_i/)|O_i|$  returns to high impedance when  $(\overline{DT})/\overline{OE}$  goes high. The data to be written is strobed by  $(\overline{WB})/\overline{WE}$  with setup and hold times referenced to this signal.

Late Write Cycle. This cycle shows the timing flexibility of (DT/)OE, which can be activated just after (WB/)WE falls, even when (WB/)WE is brought low after CAS.

**Refresh Cycle.** A cycle at each of the 512 row addresses ( $A_0$  through  $A_8$ ) will refresh all storage cells. Any cycle executed in the random access port (i.e., read, write, refresh, data transfer, color register set, flash write or block write) refreshes the 2048 bits selected by the  $\overline{\text{PAS}}$  addresses or by the on-chip address counter.

RAS-Only Refresh Cycle. A cycle having only RAS active refreshes all cells in one row of the storage array. A high CAS is maintained while RAS is active to keep (W<sub>i</sub>/)IO<sub>i</sub> in high impedance. This method is preferred for refreshing, especially when the host system consists of multiple rows of random access devices. The data outputs may be OR-tied with no bus contention when RAS-only refresh cycles are executed.

CAS Before RAS Refresh Cycle. This cycle executes internal refreshing using the on-chip control circuitry. Whenever CAS is low as RAS falls, this circuitry automatically refreshes the row addresses specified by the internal counter. In this cycle, the circuit operation based on CAS is maintained in a reset state. When internal refreshing is complete, the address counter automatically increments in preparation for the next CAS before RAS cycle.

Hidden Refresh Cycle. This cycle is executed after a read cycle, without disturbing the read data output. Once valid, the data output is controlled by CAS and OE. After the read cycle, CAS is held low while RAS goes high for precharge. A RAS-only cycle is then executed (except that CAS is held at a low level instead of a high level) and the data output remains valid. Since hidden refreshing is the same as CAS before RAS refreshing, the data output remains valid during either operation.

Fast-Page Cycle. This feature allows faster data access by keeping the same row address while successive column addresses are strobed onto the chip. Maintaining RAS low while successive CAS cycles are executed causes data to be transferred at a faster rate because

row addresses are maintained internally and do not have to be reapplied. In fast-page operation, read, write, and read-write/read-modify-write cycles may be executed. Additionally, the write-per-bit control specified in the entry write cycle is maintained throughout the next fast-page write cycle.

During a fast-page read cycle, the  $(W_i)IO_i$  data pin (i = 0 through 7) remains in a state of high impedance until valid data appears at the output pin at access time. Device access time in this cycle will be the longest of the following intervals:

- t<sub>ACP</sub>

- t<sub>CP</sub> + t<sub>T</sub> + t<sub>CAC</sub>

- CAS high to column address delay + t<sub>AA</sub>

#### Serial Read Port

The serial read port is used to serially read the previously loaded contents of the data register starting from a specified location. Other graphics buffers require very tight timing to synchronize this port with the random access port, but the  $\mu$ PD42275 has been designed with a split register to eliminate the need for synchronized timing between the two ports.

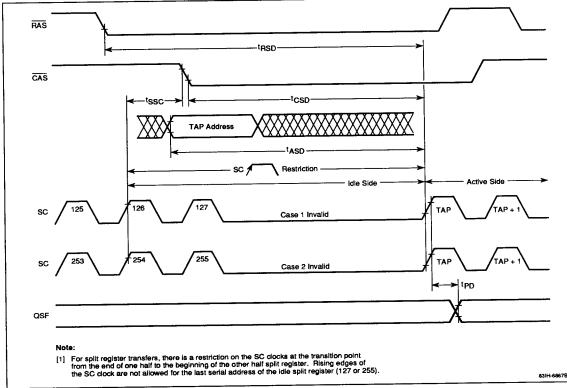

Split Register Data Transfer. A review of the split register architecture shows that the lower register (addresses 0 - 127) and upper register (addresses 128 - 255) are selected by the most significant bit of the column addresses (A7). With the serial port split in half, data transfers can be executed to the inactive side (no SC clocks) while SC clocks are input to access data from the active side. This sequence allows for a longer time window to perform the transfer, i.e., 128 x  $t_{SCC}$ , or 3.84  $\mu$ s. Column address bits A0 through A6 are latched on-chip to provide the tap address pointer for each split register.

QSF Special Function Output. This pin outputs a signal indicating which half of the data register is active and is synchronized with the SC clock.

### Split Data Transfer Cycle

| Portion of Split Register | QSF  |

|---------------------------|------|

| 0 through 127             | Low  |

| 128 through 255           | High |

#### Notes:

- A full data transfer cycle must precede all split register operations.

- (2) Column address A<sub>7</sub> must be specified for a split data transfer cycle.

Data in the data register is clocked serially by SC, starting from the first specified address of either register. After the last specified address has been transferred, QSF changes its level at the next rising edge of SC, and serial data transfer switches to the other (formerly inactive) register. Serial data output is maintained until the next SC clock.

SC clocks at the transition point, i.e., the end of one half and the beginning of the new half of the split registers, are restricted. Rising edges of the SC clock are not allowed for the last serial address (either 127 or 255) of the active register and for the first address (any address depending on current address pointer) of the next active register (figure 2).

$\overline{\text{SOE}}$  controls impedance of the serial output to allow multiplexing of more than one bank of  $\mu\text{PD42275s}$  on the same bus and has no effect on SC. When  $\overline{\text{SOE}}$  is low, SO<sub>i</sub> is disabled and in a state of high impedance.

Figure 1. Example of Split Register Transfer

125.8

Figure 2. Restrictions on Rising Edges of SC

| Absolute | Maximum | Ratings |

|----------|---------|---------|

| Ansolnie Maximani Harings                                   |                |

|-------------------------------------------------------------|----------------|

| Voltage on any pin relative to GND, V <sub>R1</sub>         | -1.0 to +7.0 V |

| Voltage on V <sub>CC</sub> relative to GND, V <sub>R2</sub> | -1.0 to +7.0 V |

| Operating temperature, T <sub>OPR</sub>                     | 0 to +70°C     |

| Storage temperature, T <sub>STG</sub>                       | -55 to + 125°C |

| Short-circuit output current, I <sub>OS</sub>               | 50 mA          |

| Power dissipation, P <sub>D</sub>                           | 1.5 W          |

Exposure to Absolute Maximum Ratings for extended periods may affect device reliability; exceeding the ratings could cause permanent damage. The device should be operated within the limits specified under DC and AC Characteristics.

#### **Recommended Operating Conditions**

| Parameter           | Symbol          | Min  | Тур | Max | Unit |

|---------------------|-----------------|------|-----|-----|------|

| Supply voltage      | Vcc             | 4.5  | 5.0 | 5.5 | ٧    |

| Input voltage, high | V <sub>IH</sub> | 2.4  |     | 5.5 | ٧    |

| Input voltage, low  | V <sub>IL</sub> | -1.0 |     | 0.8 | ٧    |

| Ambient temperature | TA              | 0    |     | 70  | °C   |

#### Capacitance

$T_A = 0 \text{ to } +70^{\circ}\text{C}; V_{CC} = +5.0 \text{ V } \pm 10\%; f = 1 \text{ MHz}; \text{GND} = 0 \text{ V}$

| Parameter                | Symbol                | Max (pF) | Pins Under<br>Test                                                |

|--------------------------|-----------------------|----------|-------------------------------------------------------------------|

| Input capacitance        | C <sub>I(A)</sub>     | 5        | A <sub>0</sub> - A <sub>8</sub>                                   |

|                          | C <sub>I(DT/OE)</sub> | 8        | DT/OE                                                             |

|                          | C <sub>I(WB/WE)</sub> | 8        | WB/WE                                                             |

|                          | C <sub>I(DSF)</sub>   | 8        | DSF <sub>1</sub> and DSF <sub>2</sub>                             |

|                          | C <sub>I(RAS)</sub>   | 8        | RAS                                                               |

|                          | C <sub>I(CAS)</sub>   | 8        | CAS                                                               |

|                          | C <sub>I(SOE)</sub>   | 8        | SOE                                                               |

|                          | C <sub>I(SC)</sub>    | 8        | sc                                                                |

| Input/output capacitance | C <sub>IO(W/IO)</sub> | 7        | W <sub>0</sub> /IO <sub>0</sub> - W <sub>7</sub> /IO <sub>7</sub> |

| Output capacitance       | C <sub>O(SO)</sub>    | 7        | SO <sub>0</sub> - SO <sub>7</sub>                                 |

|                          | C <sub>O(QSF)</sub>   | 7        | QSF                                                               |

12F - 9

Power Supply Current  $T_A = 0 \text{ to } +70^{\circ}\text{C}; V_{CC} = +5.0 \text{ V } \pm 10\%; \text{ GND} = 0 \text{ V}$

| Port Oper                       | ation       | _                 |           |           |           |      |                                                                                                                                                                                                                                              |

|---------------------------------|-------------|-------------------|-----------|-----------|-----------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Random Access                   | Serial Read | Parameter         | -80 (max) | -10 (max) | -12 (max) | Unit | Test Conditions                                                                                                                                                                                                                              |

| Read/write cycle                | Standby     | lcc1              | 95        | 85        | 70        | mA   | RAS and CAS cycling: DSF <sub>1</sub> and DSF <sub>2</sub> low as RAS falls; t <sub>RC</sub> = t <sub>RC</sub> min; SOE = V <sub>IH</sub> ; SC = V <sub>IH</sub> or V <sub>IL</sub>                                                          |

| Standby                         | Standby     | lcc2              | 10        | 10        | 10        | mA   | $\begin{array}{ll} D_{OUT} = \text{ high impedance;} \\ \text{address cycling; } t_{RC} = t_{RC} \text{ min} \\ \hline CAS = \overline{RAS} = V_{IH}; \\ \hline SOE = V_{IH}; SC = V_{IH} \text{ or } V_{IL} \\ \text{(Note 4)} \end{array}$ |

| RAS-only refresh<br>cycle       | Standby     | lccs              | 85        | 80        | 65        | mA   | $\overline{RAS}$ cycling; $\overline{CAS} = V_{IH}$ ; DSF <sub>1</sub><br>and DSF <sub>2</sub> low as $\overline{RAS}$ falls; $t_{RC}$<br>= $t_{RC}$ min; $\overline{SOE} = V_{IH}$ ;<br>SC = $V_{IH}$ or $V_{IL}$ (Note 2)                  |

| Fast-page cycle                 | Standby     | lcc4              | 85        | 80        | 65        | mA   | $\overline{RAS} = V_{IL}; \overline{CAS} \text{ cycling};$ $t_{PC} = t_{PC} \text{ min}; \overline{SOE} = V_{IH};$ $SC = V_{IH} \text{ or } V_{IL} \text{ (Note 3)}$                                                                         |

| CAS before RAS refresh cycle    | Standby     | lcc5              | 85        | 75        | 60        | mA   | CAS low as RAS falls;<br>t <sub>RC</sub> = t <sub>RC</sub> min; SOE = V <sub>IH</sub> ;<br>SC = V <sub>IH</sub> or V <sub>IL</sub>                                                                                                           |

| Data transfer cycle             | Standby     | lcce              | 115       | 100       | 85        | mA   | DT low as RAS falls;<br>t <sub>RC</sub> = t <sub>RC</sub> min; SOE = V <sub>IH</sub> ;<br>SC = V <sub>IH</sub> or V <sub>IL</sub>                                                                                                            |

| Read/write cycle                | Active      | lcc7              | 125       | 110       | 90        | mA   | RAS and CAS cycling; DSF <sub>1</sub><br>and DSF <sub>2</sub> low as RAS falls;<br>t <sub>RC</sub> = t <sub>RC</sub> min; SOE = V <sub>IL</sub> ;<br>SC cycling; t <sub>SCC</sub> = t <sub>SCC</sub> min                                     |

| Standby                         | Active      | Іссв              | 40        | 35        | 30        | mA   | D <sub>OUT</sub> = high impedance;<br>address cycling; t <sub>RC</sub> = t <sub>RC</sub> min;<br>CAS = RAS = V <sub>IH</sub> ;<br>SOE = V <sub>IL</sub> ; SC cycling;<br>t <sub>SCC</sub> = t <sub>SCC</sub> min (Note 4)                    |

| RAS-only refresh<br>cycle       | Active      | lcce              | 115       | 105       | 85        | mA   | RAS cycling; CAS = V <sub>IH</sub> ; DSF <sub>1</sub><br>and DSF <sub>2</sub> low as RAS falls;<br>t <sub>RC</sub> = t <sub>RC</sub> min; SOE = V <sub>IL</sub> ;<br>SC cycling; t <sub>SCC</sub> = t <sub>SCC</sub> min                     |

| Fast-page cycle                 | Active      | <sup>[</sup> CC10 | 105       | 90        | 75        | mA   | RAS = V <sub>IL</sub> ; CAS cycling;<br>tpc = tpc min; SOE = V <sub>IL</sub> ;<br>SC cycling; tscc = tscc min<br>(Note 3)                                                                                                                    |

| CAS before RAS<br>refresh cycle | Active      | lcc11             | 115       | 100       | 80        | mA   | CAS low as RAS falls;<br>t <sub>RC</sub> = t <sub>RC</sub> min; SOE = V <sub>IL</sub> ;<br>SC cycling; t <sub>SCC</sub> = t <sub>SCC</sub> min                                                                                               |

| Data transfer cycle             | Active      | lcc12             | 145       | 125       | 105       | mA   | DT low as RAS falls; t <sub>RC</sub> = t <sub>RC</sub> min; SOE = V <sub>IL</sub> ; SC cycling; t <sub>SCC</sub> = t <sub>SCC</sub> min                                                                                                      |

| Color register set<br>cycle     | Standby     | l <sub>CC13</sub> | 80        | 70        | 55        | mA   | t <sub>RC</sub> = t <sub>RC</sub> min; <del>SOE</del> = V <sub>IH</sub> ;<br>SC = V <sub>IH</sub> or V <sub>IL</sub>                                                                                                                         |

| Flash write cycle               | Standby     | lCC14             | 80        | 70        | 55        | mA   | $t_{RC} = t_{RC} \text{ min; } \overline{SOE} = V_{IH};$<br>$SC = V_{IH} \text{ or } V_{IL}$                                                                                                                                                 |

| Color register set<br>cycle     | Active      | I <sub>CC15</sub> | 110       | 95        | 75        | mA   | t <sub>RC</sub> = t <sub>RC</sub> min; <del>SOE</del> = V <sub>IL</sub> ;<br>SC cycling; t <sub>SCC</sub> = t <sub>SCC</sub> min                                                                                                             |

## **Power Supply Current (cont)**

| Port Operation    |             |                   |           |           |           |      |                                                                                                         |  |  |

|-------------------|-------------|-------------------|-----------|-----------|-----------|------|---------------------------------------------------------------------------------------------------------|--|--|

| Random Access S   | Serial Read | -<br>Parameter    | -80 (max) | ~10 (max) | -12 (max) | Unit | Test Conditions                                                                                         |  |  |

| Flash write cycle | Active      | lCC16             | 110 95 75 |           | 75        | mA   | $t_{RC} = t_{RC} \text{ min}; \overline{SOE} = V_{IL};$<br>SC cycling; $t_{SCC} = t_{SCC} \text{ min}$  |  |  |

| Block write cycle | Standby     | I <sub>CC17</sub> | 95        | 85        | 75        | mA   | $t_{RC} = t_{RC} \text{ min; } \overline{SOE} = V_{IH};$<br>$SC = V_{IH} \text{ or } V_{IL}$            |  |  |

| Block write cycle | Active      | I <sub>CC18</sub> | 125       | 110       | 95        | mA   | $t_{RC} = t_{RC} \text{ min; } \overline{SOE} = V_{IL};$<br>SC cycling; $t_{SCC} = t_{SCC} \text{ min}$ |  |  |

#### Notes:

- No load on IO<sub>i</sub> or SO<sub>i</sub>. Except for I<sub>CC2</sub>, I<sub>CC3</sub>, I<sub>CC6</sub>, and I<sub>CC14</sub>, real values depend on output loading in addition to cycle rates.

- (2) CAS is not clocked, but is kept at a stable high level. The column addresses are also assumed to be kept stable, at either a high or low level.

- (3) A change in column addresses must not occur more than once in a fast-page cycle.

- (4) A change in row addresses must not occur more than once in a read or write cycle.

#### **DC Characteristics**

$T_A = 0 \text{ to } +70^{\circ}\text{C}; V_{CC} = +5.0 \text{ V} \pm 10\%; \text{ GND} = 0 \text{ V}$

| Parameter                               | Symbol             | Min | Тур | Max | Unit | Test Conditions                                                                                  |

|-----------------------------------------|--------------------|-----|-----|-----|------|--------------------------------------------------------------------------------------------------|

| Input leakage current                   | l <sub>IL</sub>    | -10 |     | 10  | μΑ   | V <sub>IN</sub> = 0 to 5.5 V; all other pins<br>not under test = 0 V                             |

| Output leakage current                  | loL                | -10 |     | 10  | μΑ   | D <sub>OUT</sub> (IO <sub>i</sub> , SO <sub>i</sub> ) disabled;<br>V <sub>OUT</sub> = 0 to 5.5 V |

| Random access port output voltage, high | V <sub>OH(R)</sub> | 2.4 |     |     | V    | $I_{OH(R)} = -1 \text{ mA}$                                                                      |

| Random access port output voltage, low  | V <sub>OL(R)</sub> |     |     | 0.4 | V    | $I_{OL(R)} = 2.1 \text{ mA}$                                                                     |

| Serial read port output voltage, high   | V <sub>OH(S)</sub> | 2.4 |     |     | ٧    | $I_{OH(S)} = -1 \text{ mA}$                                                                      |

| Serial read port output voltage, low    | V <sub>OL(S)</sub> |     |     | 0.4 | V    | I <sub>OL(S)</sub> = 2.1 mA                                                                      |

#### **AC Characteristics**

$T_A = 0 \text{ to } +70^{\circ}\text{C}; V_{CC} = +5.0 \text{ V} \pm 10\%; \text{ GND} = 0 \text{ V}$

|                                                |                   | μPD4    | 2275-80 | μPD42275-10 |        | μPD42275-12 |        |      |                   |

|------------------------------------------------|-------------------|---------|---------|-------------|--------|-------------|--------|------|-------------------|

| Parameter                                      | Symbol            | Min     | Max     | Min         | Max    | Min         | Max    | Unit | Test Conditions   |

| Access time from column address                | tAA               | <u></u> | 45      |             | 50     |             | 65     | ns   | (Notes 3 and 4)   |

| Access time from rising edge of CAS            | tACP              |         | 45      |             | 55     |             | 65     | ns   | (Notes 3 and 4)   |

| DT low hold time after address                 | t <sub>ADD</sub>  | 35      |         | 35          |        | 45          |        | ns   | (Note 15)         |

| Column address setup time                      | tasc              | 0       |         | 0           |        | 0           |        | ns   |                   |

| Address to SC high delay                       | t <sub>ASD</sub>  | 55      |         | 60          |        | 75          |        | ns   | (Notes 16 and 18) |

| Row address setup time                         | tASR              | 0       |         | 0           |        | 0           |        | ns   |                   |

| Column address to WE delay                     | t <sub>AWD</sub>  | 70      |         | 85          |        | 100         |        | ns   | (Note 7)          |

| Access time from falling edge of CAS           | t <sub>CAC1</sub> |         | 20      |             | 25     |             | 30     | ns   | (Notes 3 and 4    |

| Access time from CAS, mask register read cycle | tCAC2             |         | 30      |             | 35     |             | 40     | ns   | (Note 14)         |

| Column address hold time                       | tCAH              | 15      |         | 15          |        | 25          |        | ns   |                   |

| CAS pulse width                                | t <sub>CAS</sub>  | 25      | 10,000  | 30          | 10,000 | 35          | 10,000 | ns   |                   |

| DT low hold time after CAS low                 | tcDH              | 25      |         | 30          |        | 35          |        | ns   | (Note 15)         |

| CAS before RAS refresh hold time               | tchr              | 12      |         | 12          |        | 15          |        | ns   |                   |

# AC Characteristics (cont)

|                                                       |                   | μPD4: | 2275-80 | μPD42275-10 |     | μPD42275-12 |             |      |                                       |

|-------------------------------------------------------|-------------------|-------|---------|-------------|-----|-------------|-------------|------|---------------------------------------|

| Parameter                                             | Symbol            | Min   | Max     | Min         | Max | Min         | Max         | Unit | Test Conditions                       |

| Fast-page CAS precharge time                          | t <sub>CP</sub>   | 10    |         | 10          |     | 15          |             | ns   |                                       |

| CAS precharge time (nonpage cycle)                    | t <sub>CPN</sub>  | 10    |         | 10          |     | 15          |             | ns   |                                       |

| CAS to QSF delay time                                 | tcqp              |       | 70      |             | 70  |             | 100         | ns   | (Notes 16 and 19)                     |

| CAS high to RAS low precharge time                    | t <sub>CRP</sub>  | 10    |         | 10          |     | 10          |             | ns   | (Note 12)                             |

| CAS low to SC high delay                              | tcsp              | 45    |         | 55          |     | 65          | -           | ns   | (Notes 16 and 18)                     |

| CAS hold time                                         | tcsH              | 80    |         | 100         |     | 120         | <del></del> | ns   |                                       |

| CAS before RAS refresh setup time                     | tcsn              | 0     |         | 0           |     | 0           |             | ns   |                                       |

| CAS to WE delay                                       | tcwp              | 45    |         | 55          |     | 65          |             | ns   | (Note 7)                              |

| Write command to CAS lead time                        | tcwL              | 30    |         | 30          |     | 35          |             | ns   |                                       |

| Data-in hold time                                     | <sup>t</sup> DH   | 15    |         | 20          |     | 25          |             | ns   | (Note 8)                              |

| DT high hold time                                     | t <sub>DHH</sub>  | 12    |         | 12          |     | 15          |             | ns   |                                       |

| DT high setup time                                    | t <sub>DHS</sub>  | 0     |         | 0           |     | 0           |             | ns   |                                       |

| DT low setup time                                     | tDLS              | 0     | ·····   | 0           |     | 0           |             | ns   |                                       |

| Propagation delay time from DT/OE to QSF              | <sup>†</sup> DQD  |       | 35      |             | 35  |             | 55          | ns   | (Note 20)                             |

| Propagation delay time from RAS to QSF                | t <sub>DQR</sub>  |       | 45      |             | 55  |             | 70          | ns   | (Note 20)                             |

| Data-in setup time                                    | t <sub>DS</sub>   | 0     |         | 0           |     | 0           |             | ns   | (Note 8)                              |

| DT high pulse width                                   | t <sub>DTP</sub>  | 25    |         | 30          |     | 35          |             | ns   |                                       |

| DT high to RAS high delay                             | t <sub>DTR</sub>  | 0     |         | 0           |     | 0           |             | ns   | (Note 15)                             |

| DSF <sub>1</sub> hold time from CAS                   | t <sub>FCH1</sub> | 15    |         | 15          |     | 25          |             | ns   |                                       |

| DSF <sub>1</sub> setup time from CAS                  | t <sub>FCS1</sub> | 0     |         | 0           |     | 0           |             | ns   | ,                                     |

| DSF <sub>1</sub> hold time from RAS                   | t <sub>FBH1</sub> | 12    |         | 12          |     | 15          |             | ns   |                                       |

| DSF <sub>2</sub> hold time from RAS                   | tFRH2             | 12    |         | 12          |     | 15          |             | ns   |                                       |

| DSF <sub>1</sub> setup time from RAS                  | t <sub>FRS1</sub> | 0     |         | 0           |     | 0           |             | ns   |                                       |

| DSF <sub>2</sub> setup time from RAS                  | t <sub>FRS2</sub> | 0     |         | 0           | ,   | 0           |             | ns   |                                       |

| Access time from OE                                   | toEA              |       | 20      |             | 25  |             | 30          | ns   | (Notes 3 and 4)                       |

| OE high to data-in setup delay                        | toED              | 20    |         | 25          |     | 30          |             | ns   |                                       |

| OE high hold time after WE low                        | toEH              | 20    |         | 20          |     | 30          |             | ns   |                                       |

| OE to RAS inactive setup time                         | toes              | 10    |         | 10          |     | 10          |             | ns   |                                       |

| Output disable time from OE high                      | toez              | 0     | 20      | 0           | 25  | 0           | 30          | ns   | (Note 5)                              |

| Output disable time from CAS high                     | toff              | 0     | 20      | 0           | 20  | 0           | 30          | ns   | (Note 5)                              |

| Fast-page cycle time                                  | t <sub>PC</sub>   | 50    |         | 60          |     | 70          | <del></del> | ns   | (Note 11)                             |

| Propagation delay time from SC to<br>QSF              | t <sub>PD</sub>   |       | 25      |             | 25  |             | 40          | ns   |                                       |

| Fast-page read-write/read-modify-<br>write cycle time | t <sub>PRWC</sub> | 105   |         | 125         |     | 145         |             | ns   | (Note 11)                             |

| Access time from RAS                                  | tRAC              |       | 80      |             | 100 |             | 120         | ns   | (Notes 3 and 4)                       |

| RAS to column address delay time                      | tRAD              | 17    |         | 17          |     | 20          |             | ns   | (Note 9)                              |

| Row address hold time                                 | t <sub>RAH</sub>  | 12    |         | 12          |     | 15          |             | ns   | · · · · · · · · · · · · · · · · · · · |

**AC Characteristics (cont)**

|                                                                                   |                   | μPD42275-80 |         | μPD42275-10 |         | μPD4 | 2275-12 |      |                                                    |

|-----------------------------------------------------------------------------------|-------------------|-------------|---------|-------------|---------|------|---------|------|----------------------------------------------------|

| Parameter                                                                         | Symbol            | Min         | Max     | Min         | Max     | Min  | Max     | Unit | Test Conditions                                    |

| Column address to RAS lead time                                                   | tRAL              | 45          |         | 55          |         | 65   |         | ns   |                                                    |

| RAS pulse width                                                                   | tRAS              | 80          | 10,000  | 100         | 10,000  | 120  | 10,000  | ns   |                                                    |

| Fast-page RAS pulse width                                                         | tRASP             | 80          | 100,000 | 100         | 100,000 | 120  | 100,000 | ns   |                                                    |

| Random read or write cycle time                                                   | t <sub>RC</sub>   | 160         |         | 180         |         | 220  |         | ns   | (Note 11)                                          |

| RAS to CAS delay time                                                             | t <sub>RCD1</sub> | 22          | 60      | 25          | 75      | 25   | 90      | ns   | (Note 4)                                           |

| RAS to CAS delay time, mask register read cycle                                   | <sup>†</sup> RCD2 | 22          | 50      | 25          | 65      | 25   | 80      | ns   | (Note 14)                                          |

| Read command hold time after                                                      | <sup>t</sup> RCH  | 0           |         | 0           |         | 0    |         | ns   | (Note 6)                                           |

| Read command setup time                                                           | tRCS              | 0           |         | 0           |         | 0    |         | ns   |                                                    |

| DT low hold time after RAS low,<br>serial port active                             | t <sub>RDH</sub>  | 65          |         | 80          |         | 95   |         | ns   | (Note 15)                                          |

| DT low hold time after RAS low,<br>serial port in standby, split data<br>transfer | t <sub>RDHS</sub> | 12          |         | 12          |         | 15   |         | ns   | (Notes 16 and 18                                   |

| Refresh interval                                                                  | tREF              |             | 8       |             | 8       |      | 8       | ms   | Addresses A <sub>0</sub><br>through A <sub>8</sub> |

| RAS precharge time                                                                | t <sub>RP</sub>   | 70          |         | 70          |         | 90   |         | ns   |                                                    |

| RAS high to CAS low precharge                                                     | tRPC              | 0           |         | 0           |         | 0    |         | ns   |                                                    |

| RAS to QSF delay time                                                             | tRQD              |             | 105     |             | 120     |      | 155     | ns   | (Notes 16 and 19                                   |

| Read command hold time after                                                      | t <sub>RRH</sub>  | 0           |         | 0           |         | 0    |         | ns   | (Note 6)                                           |

| RAS low to SC high delay                                                          | tRSD              | 85          |         | 105         |         | 125  |         | ns   | (Note 18)                                          |

| RAS hold time                                                                     | tRSH              | 20          |         | 25          |         | 30   |         | ns   |                                                    |

| Read-write/read-modify-write cycle time                                           | <sup>t</sup> RWC  | 220         |         | 245         |         | 295  |         | ns   | (Note 11)                                          |

| RAS to WE delay                                                                   | t <sub>RWD</sub>  | 105         |         | 130         |         | 155  |         | ns   | (Note 7)                                           |

| Write command to RAS lead time                                                    | t <sub>RWL</sub>  | 30          |         | 30          |         | 35   |         | ns   |                                                    |

| Serial output access time from SC                                                 | tsca              |             | 25      |             | 25      |      | 40      | ns   | (Note 3)                                           |

| Serial clock cycle time                                                           | tscc              | 25          |         | 30          |         | 40   |         | ns   | (Note 11)                                          |

| SC pulse width                                                                    | t <sub>SCH</sub>  | 7           |         | 10          |         | 15   |         | ns   |                                                    |

| SC precharge time                                                                 | tscL              | 7           |         | 10          |         | 15   |         | ns   |                                                    |

| SC high to DT high delay                                                          | tsDD              | 5           |         | 5           |         | 5    |         | ns   | (Note 15)                                          |

| SC low hold time after DT high                                                    | tsph              | 10          |         | 15          |         | 20   |         | ns   | (Note 15)                                          |

| SC low hold time after RAS high                                                   | tsDHR             | 25          |         | 30          |         | 40   |         | ns   | (Note 16)                                          |

| Serial output access time from SOE                                                | tsoA              |             | 20      |             | 25      |      | 30      | ns   | (Note 3)                                           |

| SOE pulse width                                                                   | †SOE              | 7           |         | 10          |         | 15   |         | ns   |                                                    |

| Serial output hold time after SC high                                             | tsон              | 5           |         | 7           |         | 7    |         | ns   |                                                    |

| SOE low to serial output setup                                                    | tsoo              | 5           |         | 5           |         | 5    |         | лѕ   |                                                    |

| SOE precharge time                                                                | tsop              | 7           |         | 10          |         | 15   |         | ns   |                                                    |

#### AC Characteristics (cont)

|                                          |                 | μPD42275-80 |     | μPD42275-10 |     | μPD42275-12 |     |      |                   |

|------------------------------------------|-----------------|-------------|-----|-------------|-----|-------------|-----|------|-------------------|

| Parameter                                | Symbol          | Min         | Max | Min         | Max | Min         | Max | Unit | Test Conditions   |

| Serial output disable time from SOE high | tsoz            | 0           | 10  | 0           | 15  | 0           | 20  | ns   | (Note 5)          |

| SC high to CAS low delay                 | tssc            | 10          |     | 10          |     | 10          |     | ns   | (Notes 16 and 18) |

| Rise and fall transition time            | t <sub>T</sub>  | 3           | 50  | 3           | 50  | 3           | 50  | ns   | (Notes 3 and 10)  |

| Write-per-bit hold time                  | twBH            | 12          |     | 12          |     | 15          |     | ns   |                   |

| Write-per-bit setup time                 | twss            | 0           |     | 0           |     | 0           |     | ns   |                   |

| Write command hold time                  | twch            | 15          |     | 20          |     | 25          |     | ns   |                   |

| Write command setup time                 | twcs            | 0           |     | 0           |     | 0           |     | ns   | (Note 7)          |

| Write bit selection hold time            | twH             | 12          |     | 12          |     | 15          |     | ns   |                   |

| Write command pulse width                | t <sub>WP</sub> | 15          |     | 20          |     | 25          |     | ns   | (Note 13)         |

| Write bit selection setup time           | tws             | 0           |     | 0           |     | 0           |     | ns   |                   |

#### Notes:

- (1) All voltages are referenced to GND.

- (2) An initial pause of 100 µs is required after power-up, followed by any eight RAS cycles, before proper device operation is achieved.

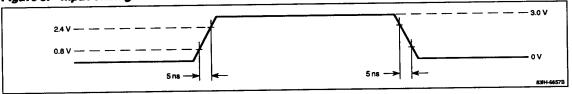

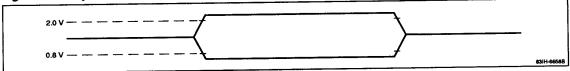

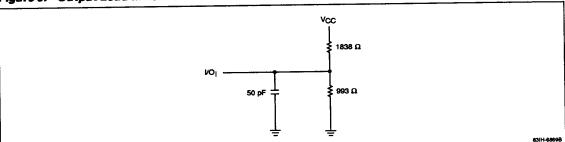

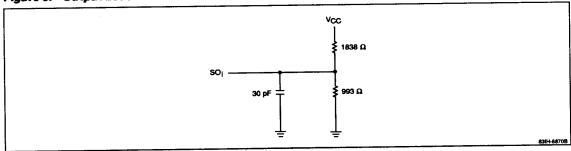

- (3) See figures 3 and 4 for reference voltages and figures 5 and 6 for output loads.

- (4) Operation within the t<sub>RCD</sub> (max) limit ensures that t<sub>RAC</sub> (max) can be met. The t<sub>RCD</sub> (max) limit is specified as a reference point only. If t<sub>RCD</sub> is greater than the specified t<sub>RCD</sub> (max) limit, access time is controlled exclusively by t<sub>CAC</sub> or t<sub>AA</sub>.

- (5) An output disable time defines the time at which the output achieves the open-circuit condition and is not referenced to output voltage levels.

- (6) Either t<sub>RRH</sub> or t<sub>RCH</sub> must be satisfied for a read cycle.

- (7) t<sub>WCS</sub>, t<sub>CWD</sub>, and t<sub>RWD</sub> are restrictive operating parameters in read-write and read-modify-write cycles only. If t<sub>WCS</sub> ≥ t<sub>WCS</sub> (min), the cycle is an early write cycle and the data output will remain open-circuit throughout the entire cycle. If t<sub>CWD</sub> ≥ t<sub>CWD</sub> (min) and t<sub>RWD</sub> ≥ t<sub>RWD</sub> (min), the cycle is a read-write cycle and the data output will contain data read from the selected cell. If neither of the above conditions is met, the condition of the data output (at access time and until CAS returns to V<sub>IH</sub>) is indeterminate.

- (8) These parameters are referenced to the falling edge of CAS in early write cycles and to the falling edge of (WB/)WE in delayed write or read-modify-write cycles.

- (9) Assumes that t<sub>RAD</sub> (min) = t<sub>RAH</sub> (min) + typical t<sub>T</sub> of 5 ns.

- (10)  $V_{IH}$  (min) and  $V_{IL}$  (max) are reference levels for measuring the timing of input signals. Additionally, transition times are measured between  $V_{IH}$  and  $V_{II}$ .

- (11) The minimum specifications are used only to indicate the cycle time at which proper operation over the full temperature range (T<sub>A</sub> = 0 to +70°C) is assured.

- (12) The t<sub>CRP</sub> requirement is applicable for RAS/CAS cycles preceded by any cycle.

- (13) Parameter t<sub>WP</sub> is applicable for a delayed write cycle such as a read-write/read-modify-write cycle. For early write operation, both t<sub>WCS</sub> and t<sub>WCH</sub> must be met.

- (14) Only for mask register read operation during register read cycles.

- (15) For real-time data transfer operation (data transfer with SC active).

- (16) For read data transfers with serial port in standby.

- (17) Ac measurements assume  $t_T = 5$  ns.

- (18) For split data transfer cycles.

- (19) If t<sub>CDH</sub> ≤ t<sub>CDH</sub> (min) or t<sub>RDHS</sub> ≤ t<sub>RDH</sub> (min), then the delay time for the switching of QSF is determined by t<sub>RQD</sub> or t<sub>CQD</sub>, whichever occurs later.

- (20) If t<sub>CDH</sub> ≥ t<sub>CDH</sub> (min) and t<sub>RDHS</sub> ≥ t<sub>RDH</sub> (min), then the switching delay time of QSF is determined by t<sub>DQD</sub> or t<sub>DQR</sub>, whichever occurs first.

Figure 3. Input Timing

Figure 4. Output Timing

Figure 5. Output Load in Random Access Port

Figure 6. Output Load in Serial Read Port

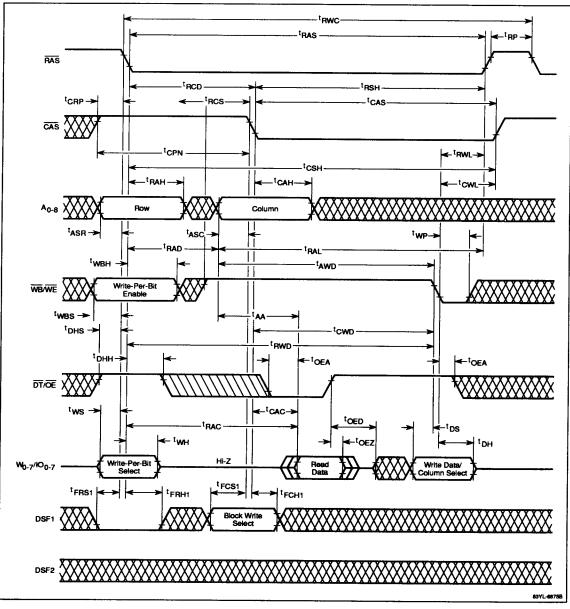

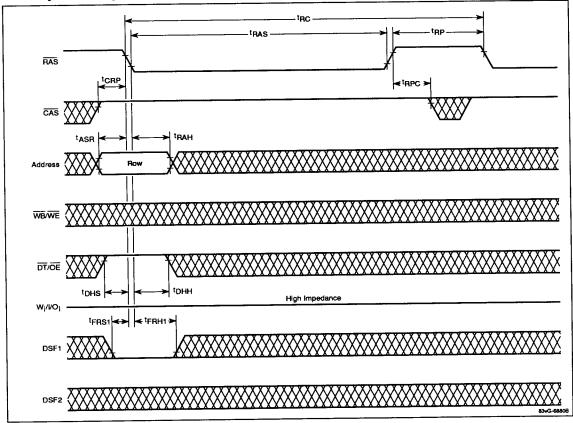

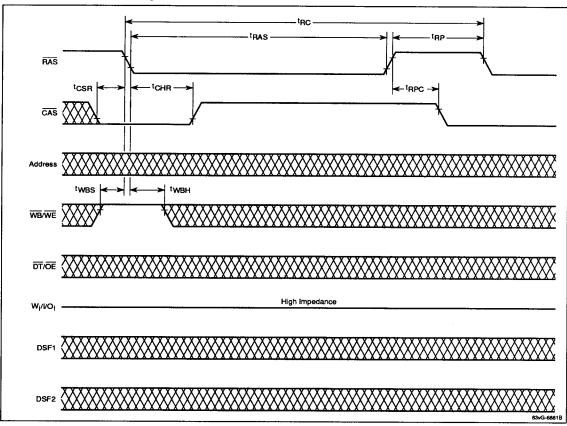

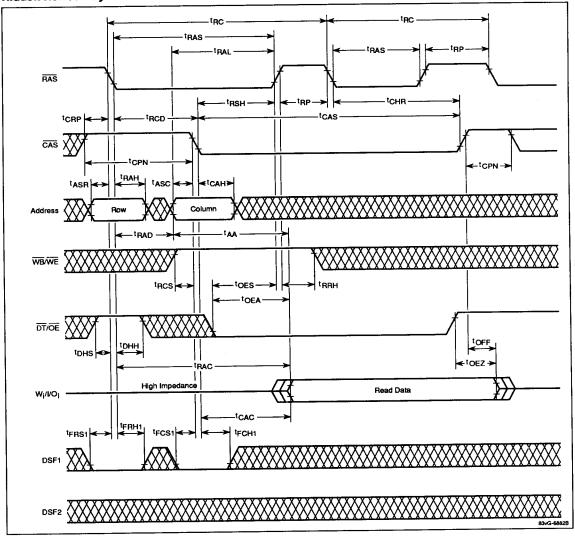

# **Timing Waveforms**

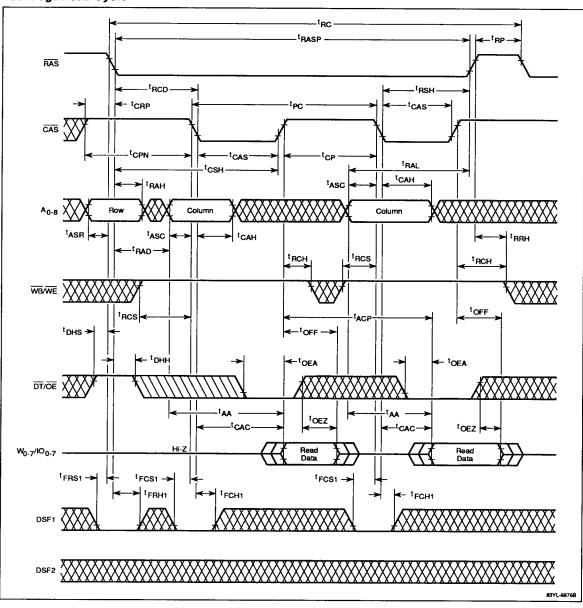

# Read Cycle

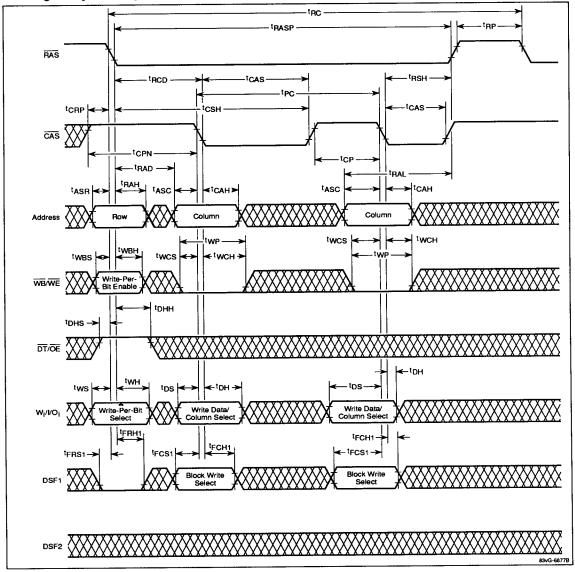

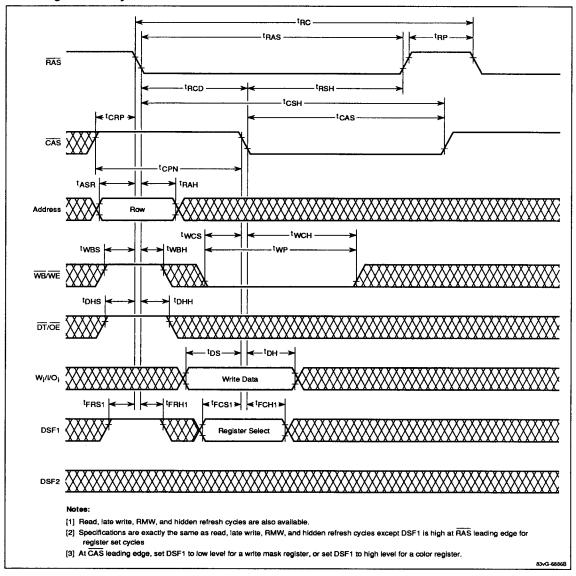

# Early Write Cycle and Early Block Write Cycle

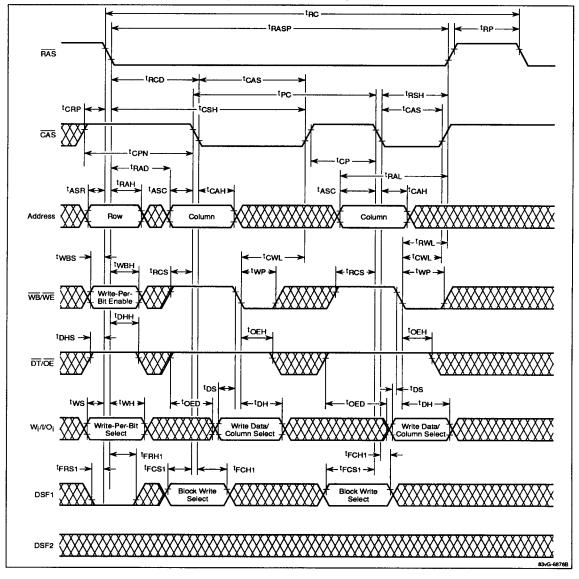

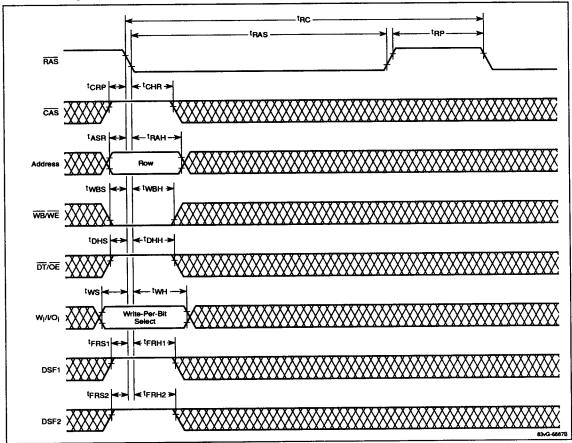

# Early Write Cycle and Early Block Write Cycle With Old Mask

# Late Write Cycle and Late Block Write Cycle

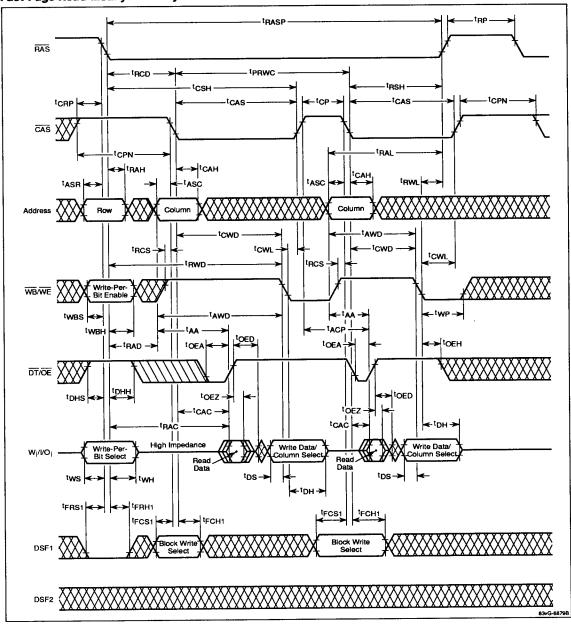

# Read-Write/Read-Modify-Write Cycle

# RAS-Only Refresh Cycle

# CAS Before RAS Refresh Cycle

## Hidden Refresh Cycle

# Fast-Page Read Cycle

# Fast-Page Early Write Cycle and Fast-Page Early Block Write Cycle

## Fast-Page Late Write Cycle and Fast-Page Late Block Write Cycle

## Fast-Page Read-Modify-Write Cycle

### Color Register Set Cycle

## Flash Write Cycle

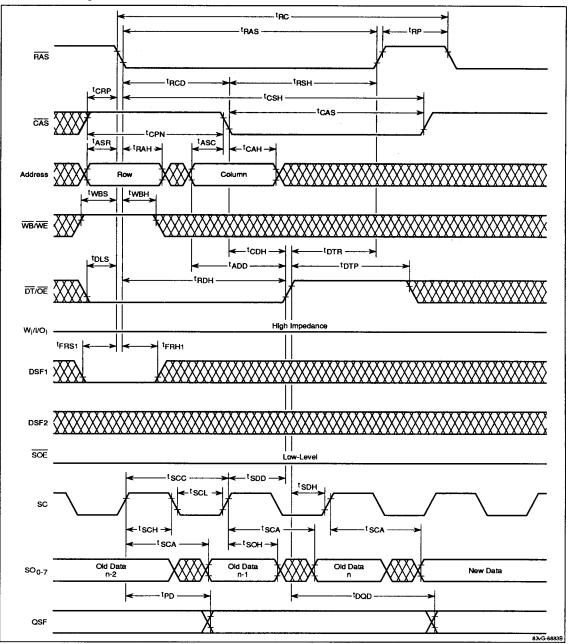

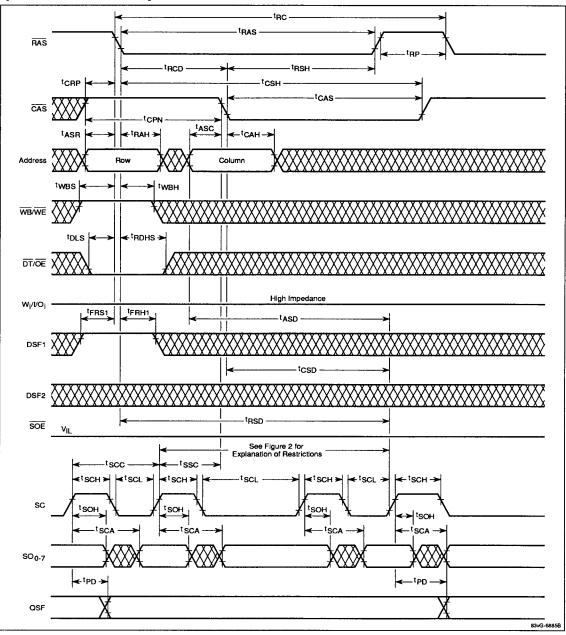

# Data Transfer Cycle with Serial Port Active

12F- 30

# Data Transfer Cycle with Serial Port in Standby

12F - 31

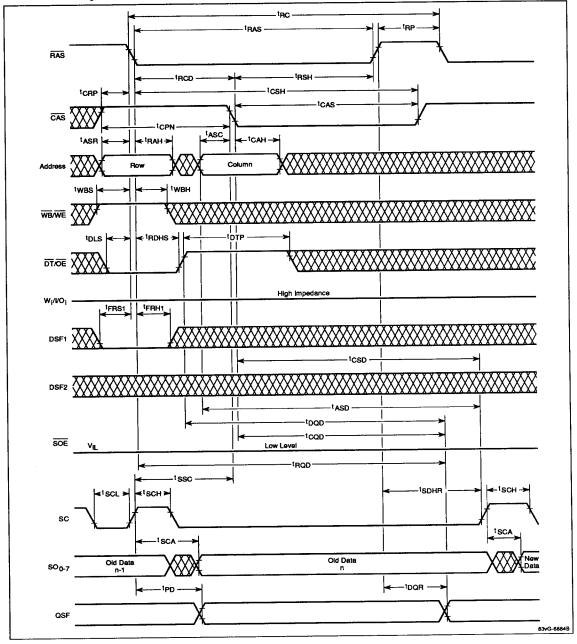

## Split Read Data Transfer Cycle

12F-32

## Serial Read Cycle