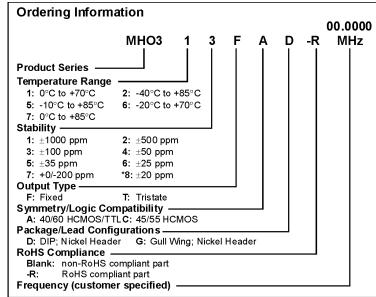

## **MHO3 Series**

## 14 pin DIP, 3.3 Volt, HCMOS/TTL, Clock Oscillator

<sup>\*</sup>Contact factory for availability.

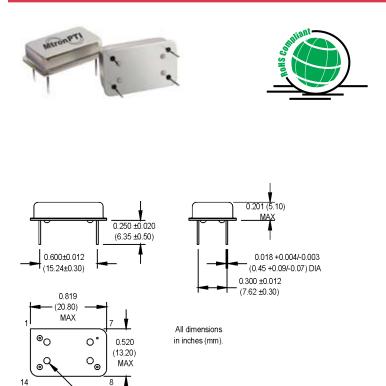

## **Pin Connections**

INSULATED STANDOFFS

| PIN | FUNCTION            |  |  |  |  |

|-----|---------------------|--|--|--|--|

| 1   | N/C or Tristate     |  |  |  |  |

| 7   | Circuit/Case Ground |  |  |  |  |

| 8   | Output              |  |  |  |  |

| 14  | +Vdd                |  |  |  |  |

|                | PARAMETER             | Symbol | Min.                                                                                     | Тур. | Max.    | Units  | Condition/Notes      |

|----------------|-----------------------|--------|------------------------------------------------------------------------------------------|------|---------|--------|----------------------|

|                | Frequency Range       | F      | 1.5                                                                                      |      | 80      | MHz    | See Note 1           |

|                | Operating Temperature | TA     | (See Ordering Information)                                                               |      |         |        |                      |

|                | Storage Temperature   | Ts     | -55                                                                                      |      | +125    | °C     |                      |

|                | Frequency Stability   | ∆F/F   | (See Ordering Information)                                                               |      |         |        |                      |

|                | Aging                 |        |                                                                                          |      |         |        |                      |

|                | 1st Year              |        |                                                                                          | ±3   |         | ppm    |                      |

| Specifications | Thereafter (per year) |        |                                                                                          | ±2   |         | ppm    |                      |

| cati           | Input Voltage         | Vdd    | 3.135                                                                                    | 3.3  | 3.465   | ٧      |                      |

| ςij            | Input Current         | ldd    |                                                                                          |      | 25      | mA     | 1.500 to 50.000 MHz  |

| Spe            |                       |        |                                                                                          |      | 35      | mA     | 50.001 to 67.000 MHz |

| la<br>E        | Output Type           |        |                                                                                          |      |         |        | HCMOS/TTL            |

| ij             | Load                  |        | 2 TTL or 15 pF (See Ordering Information)                                                |      |         |        | See Note 2           |

| Electrical     | Symmetry (Duty Cycle) |        |                                                                                          |      |         |        | See Note 3           |

| "              | Logic "1" Level       | Voh    | 90% Vdd                                                                                  |      |         | ٧      | HCMOS Load           |

|                |                       |        | Vdd -0.4                                                                                 |      |         | ٧      | TTL Load             |

|                | Logic "0" Level       | Vol    |                                                                                          |      | 10% Vdd | V      | HCMOS Load           |

|                |                       |        |                                                                                          |      | 0.4     | ٧      | TTL Load             |

|                | Output Current        |        |                                                                                          |      | ±4      | mA     |                      |

|                | Rise/Fall Time        | Tr/Tf  |                                                                                          |      | 10      | ns     | See Note 4           |

|                | Tristate Function     |        | Input Logic "1" or floating; output active<br>Input Logic "0"; output disables to high-Z |      |         |        |                      |

|                | Start up Time         |        |                                                                                          | 5    |         | ms     |                      |

|                | Random Jitter         | Rj     |                                                                                          | 5    | 12      | ps RMS | 1-Sigma              |

- 1. Consult factory for availability of higher frequencies.

- TTL load See load circuit diagram #1. HCMOS load See load circuit diagram #2.

Symmetry is measured at 1.4 V with TTL load, and at 50% Vdd with HCMOS load.

- 4. Rise/Fall times are measured between 0.4 V and 2.4 V with TTL load, and between 10% Vdd and 90% Vdd with HCMOS load.

MtronPTI reserves the right to make changes to the product(s) and service(s) described herein without notice. No liability is assumed as a result of their use or application.

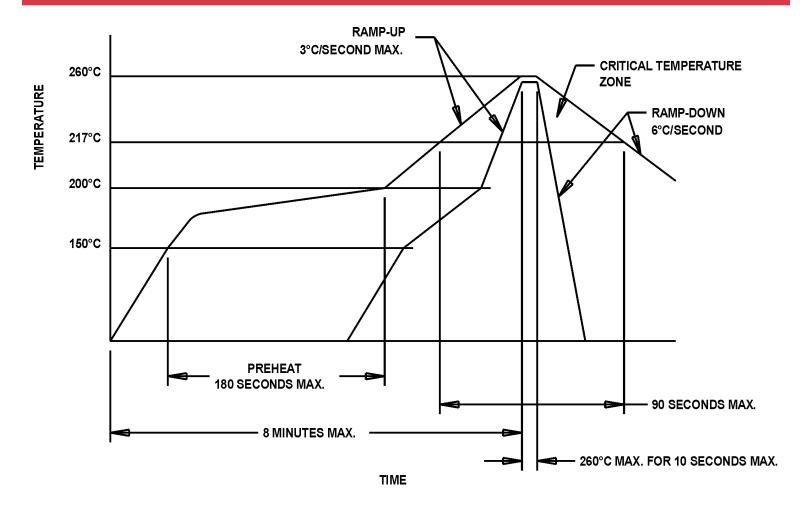

## MtronPTI Lead Free Solder Profile