# **HPL-82C338**

# Programmable Chip Select Decoder (PCSD™)

#### Features

- . Memory or I/O Chip Select Decoding, Replaces 3-6 (Cs

- Superset of the Industry Standard 74138

- Microprocessor Bus Oriented Interface

- Harris Advanced Scaled SAJI IV CMOS Process

- Faster than Low-Power Schottky at CMOS Power Consumption

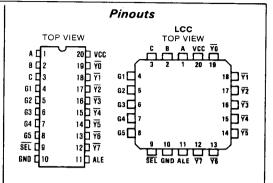

- 20 Pin Slimline DIP

- Wide Operating Temperature Ranges:

- ▶ HPL-82C338-8.....--550C to +1250C

- Simple Programming Algorithm

- Mask Programmable for Volume Users

### Description

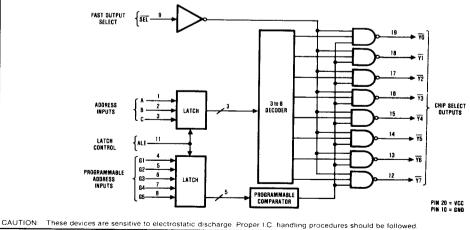

The HPL-82C338 is a high performance Programmable Chip Select Decoder (PCSD) which is intended to be used for both memory and I/O chip select decoder applications. Utilizing the Harris advanced scaled SAJI IV CMOS process, this circuit provides bipolar speed with CMOS power consumption.

In a typical application, this circuit can replace six 74HCXX SSI/MSI ICs. The associated reductions in board area, chip count and power consumption result in a substantial increase in system reliability and an attendant decrease in system cost. A speed improvement of a factor of four over an equivalent implementation with 74HCXX logic is also realized. The faster decode provided by the

82C338 can result in improved system performance or a dramatic reduction in total system cost since less expensive, slower memories and I/O devices can be used.

The five "Gx" inputs are field programmable for either high or low true address decoding. The Harris fuse link technology used in this product provides a permanent fuse with stable storage characteristics over the full temperature ranges of 0°C to +75°C, -40°C to +85°C and -55°C to +125°C.

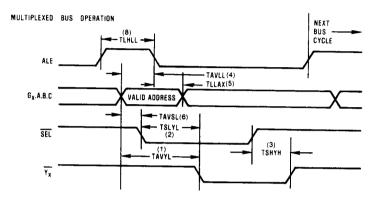

Transparent latches are utilized on all address inputs which permits the 82C338 to be used with both multiplexed and non-multiplexed address/data bus microprocessors.

# Block Diagram

HPL, PCSD are trademarks of Harris Corporation

# Specifications HPL-82C338

### **Absolute Maximum Ratings**

| Supply Voltage                                                                                                     |                      | +7.0 Volts                   |

|--------------------------------------------------------------------------------------------------------------------|----------------------|------------------------------|

| Input, Output or I/O Voltage Applied                                                                               |                      | GND -0.3V to VCC +0.3V       |

| Storage Temperature Range                                                                                          |                      |                              |

| Maximum Package Power Dissipation                                                                                  |                      |                              |

| θ <sub>iC</sub> 24°C/W (CERDIP Package),                                                                           | 19°C/W (LCC Package) | 29°C/W (Plastic DIP Package) |

| θja81°C/W (CERDIP Package),<br>Gate Count                                                                          | 76°C/W (LCC Package) | 75°C/W (Plastic DIP Package) |

| Junction Temperature                                                                                               |                      |                              |

| Lead Temperature (Soldering, Ten Seconds)                                                                          |                      | +275°C                       |

| CAUTION: Stresses above those listed in the "Absolute I is a stress only rating and operation of the device at the |                      |                              |

#### **Operating Conditions**

| Operating Voltage Range     | +4.5V to +5.5V |

|-----------------------------|----------------|

| Operating Temperature Range |                |

| HPL-82C338-5                | 0°C to +70°C   |

| HPL-82C338-9                |                |

| HPL-82C338-8                |                |

# D.C. Electrical Specifications (Operating)

sections of this specification is not implied.

HPL-82C338-5 (VCC =  $5.0V \pm 10\%$ , TA =  $0^{\circ}$ C to +75°C) HPL-82C338-9 (VCC =  $5.0V \pm 10\%$ , TA = -40°C to +85°C) HPL-82C338-8 (VCC =  $5.0V \pm 10\%$ , TA = -55°C to +125°C)

| SYMBOL              | PARAMETER                       |                   | MIN            | MAX | UNITS       | TEST CONDITIONS                                                              |  |  |

|---------------------|---------------------------------|-------------------|----------------|-----|-------------|------------------------------------------------------------------------------|--|--|

| IIH<br>IIL          | Dedicated                       |                   | "1"<br>"0"     |     | μA<br>μA    | VIH = VCC MAX<br>VIL = 0V VCC = VCC MAX                                      |  |  |

| VIH<br>VIL          | Input Threshold Voltage         | "1"<br>"1"<br>"0" | 2.0<br>2.2     | 0.8 | V<br>V<br>V | VCC = VCC MAX HPL-82C338-5/-5<br>VCC = VCC MAX HPL-82C338-8<br>VCC = VCC MIN |  |  |

| VOH1<br>VOH2<br>VOL | Output Voltage Output Voltage   | "1"<br>"1"<br>"0" | 3.0<br>VCC-0.4 | 0.4 | V<br>V      | IOH1 = -5mA<br>IOH2 = -1mA<br>VCC MIN, VIL MAX, VIH MIN<br>IOL = +5mA        |  |  |

| ICCSB*              | Standby Power<br>Supply Current |                   |                | 50  | μА          | VIH = VCC MAX<br>IF = 0.0μA, VCC = VCC MAX                                   |  |  |

| ICCOP*              | Operating Power Supply Current  |                   |                | 2   | mA/MHz      | VI = VCC or GND<br>IF = 0.0μA, VCC = VCC MAX                                 |  |  |

<sup>\*</sup> ICCSB, ICCOP specifications are achieved only after complete programming of the device. These specifications are sampled and guaranteed but not 100% tested. While testing these specifications, output pins should be left open circuit.

# A.C. Switching Specifications

(Operating)

HPL-82C338-5 (VCC =  $5.0V \pm 10\%$ , TA =  $0^{\circ}$ C to +75°C) HPL-82C338-9 (VCC =  $5.0V \pm 10\%$ , TA = -40°C to +85°C) HPL-82C338-8 (VCC =  $5.0V \pm 10\%$ , TA = -55°C to +125°C)

| SYMBOL    |                                                       | HPL-82C338-5 |     | HPL-82C338-9 |     | HPL-82C338-8 |     |       |

|-----------|-------------------------------------------------------|--------------|-----|--------------|-----|--------------|-----|-------|

|           | PARAMETER                                             | MIN          | MAX | MIN          | MAX | MIN          | MAX | UNITS |

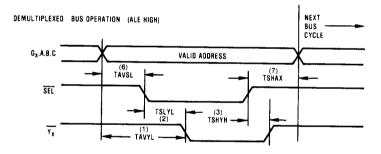

| (1) TAVYL | Propagation delay A, B, C, or<br>G to Output Low      | -            | 50  | _            | 50  | _            | 50  | ns    |

| (2) TSLYL | Select Access Time to Output Low                      |              | 35  | _            | 35  | _            | 35  | ns    |

| (3) TSHYH | Select Access Time to Output High                     |              | 35  | _            | 35  | _            | 35  | ns    |

| (4) TAVLL | Address Set-Up to ALE Trailing Edge                   | 15           |     | 15           | _   | 15           | _   | ns    |

| (5) TLLAX | Address Hold From ALE Trailing Edge                   | 15           | _   | 15           | _   | 15           | _   | ns    |

| (6) TAVSL | Address Set-Up to SEL Low<br>(Glitch-Free Operation)  | 15           | _   | 15           | _   | 15           | _   | ns    |

| (7) TSHAX | Address Hold From SEL High<br>(Glitch-Free Operation) | 15           |     | 15           |     | 15           | _   | ns    |

| (8) TLHLL | ALE Pulse Width                                       | 15           |     | 15           | _   | 15           | _   | ns    |

Capacitance T<sub>A</sub> = +25°C (NOTE: Sampled and guaranteed - but not 100% tested.)

| SYMBOL | YMBOL PARAMETER TYP UNITS TEST CONDITIONS |    |    |                            |  |  |

|--------|-------------------------------------------|----|----|----------------------------|--|--|

| CI     | Input Capacitance                         | 5  | pF | VI = VCC or GND, f = 1 MHz |  |  |

| CO     | Output Capacitance                        | 10 | pF | VO = VCC or GND, f = 1 MHz |  |  |

# **Switching Time Definitions**

NOTES: 1. In order to ensure glitch-free operation of the \( \frac{\frac{1}{2}}{2} \) outputs, set-up and hold times should be observed.

2. AC switching characteristics are measured with inputs switching between GND and 3.0V. t<sub>f</sub>, t<sub>f</sub> = 5ns (10% -90%).

# A.C. Test Load

## **Programming**

Following is the programming procedure which is used for the HPL-82C338 programmable logic device. This device is manufactured with all fuses intact. Any desired fuse can be programmed by following the simple procedure shown on the following page. One may build a pro-

grammer to satisfy the specifications described in the table, or use any of the commercially available programmers which meets these specifications. Please contact Harris for a list of approved programmers.

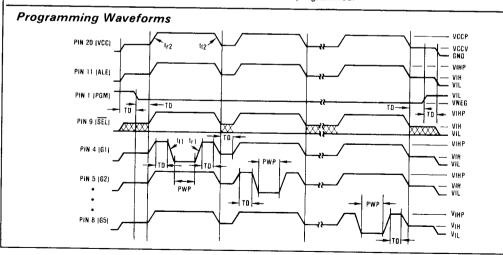

# **Programming Specifications**

TABLE 1.

| SYMBOL                                | PARAMETER                                                                                                       | TEST CONDITIONS                                      | MIN                                      | TYP                                  | MAX                          | UNITS                                |

|---------------------------------------|-----------------------------------------------------------------------------------------------------------------|------------------------------------------------------|------------------------------------------|--------------------------------------|------------------------------|--------------------------------------|

| VCCP                                  | VCC Voltage During<br>Programming                                                                               |                                                      | 11.50                                    | 12.00                                | 12.00                        | V                                    |

| vccv                                  | VCC Voltage During<br>Verify                                                                                    |                                                      | 4.75                                     | 5.00                                 | 5.25                         | V                                    |

| ICCP                                  | ICC Limit During<br>Programming                                                                                 |                                                      | _                                        | 100                                  | 200                          | mA                                   |

| VNEG                                  | Edit Enable &<br>Mode Select Voltage                                                                            |                                                      | -6.00                                    | -6.00                                | -7.00                        | ٧                                    |

| INEG                                  | Edit Enable &<br>Mode Select Current                                                                            |                                                      | _                                        | _                                    | -5.00                        | mA                                   |

| VIL<br>VIHV<br>VIHP                   | Input Voltage Low<br>Input Voltage High<br>Input Voltage High                                                   | verify ①<br>programming ①                            | 0.00<br>VCCV-2<br>VCCP-2                 | 0.00<br>VCCV<br>VCCP                 | 0.80<br>VCCV<br>VCCP         | V<br>V                               |

| IILP<br>IIHV<br>IIHP                  | Input Current Low<br>Input Current High<br>Input Current High                                                   | VIL = 0.0V<br>verify<br>programming                  | =                                        | 0<br>0<br>0                          | 1<br>1<br>1                  | μΑ<br>μΑ<br>μΑ                       |

| PWP<br>TD<br>tr1<br>tr2<br>tf1<br>tf2 | Programming Width<br>Pulse Seq. Delay<br>Signal Rise Time<br>VCC Rise Time<br>Signal Fall Time<br>VCC Fall Time | 10% to 90%<br>10% to 90%<br>90% to 10%<br>90% to 10% | 4.5<br>1<br>0.01<br>0.01<br>0.01<br>0.01 | 5.0<br>1<br>0.1<br>0.1<br>0.1<br>0.1 | 5.5<br>—<br>1<br>5<br>1<br>5 | msec<br>µsec<br>µsec<br>µsec<br>µsec |

| TPP<br>FL                             | Programming Period<br>Fuse Attempts/Link                                                                        |                                                      | _<br>1                                   | 5.1<br>1                             | _<br>2                       | msec<br>cycles                       |

① Inputs defined as logic "1" (VIHV or VIHP) must track the VCC power supply when the supply is raised or lowered. The input levels should never exceed the level on the VCC Pin.

NOTE: While programming the CMOS HPL device, no input pins should be left floating. Output pins (12-19) should be left unconnected. It is suggested that a  $0.1\mu\mathrm{F}$  capacitor be placed between VCC and GND to minimize VCC voltage spikes.

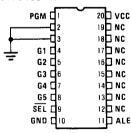

FIGURE 1. HPL-82C338 EDIT MODE PINOUT

# Programming Procedure

#### 1. Set Up:

- a. During programming or operation, no input pins should be left floating.

- No input pin voltage should ever be greater than the voltage applied to the device VCC pin.

- c. The device should be decoupled with a 0.1µF or greater capacitor located at the device socket and placed between the VCC and GND pins.

#### 2. Power up:

- a. Initially, all input pins including power supply pins should be at ground potential.

- b. Normally, the input pins (pins 4-9, 11) are driven with an open collector driver with a pull-up resistor to the VCC pin (pin 20) so that these inputs automatically track the voltage on the VCC pin when they are set to the high state. This prevents the voltage level on the input pins from exceeding the voltage applied to the VCC pin.

- Ramp the VCC pin (pin 20) to VCCV and the input pins (pins 4-9, 11) to VIHV.

#### 3. Programming Sequence

- After a delay TD, the programming mode is entered by taking the programming enable pin (pin 1) to VNEG. Pin 1 must remain at VNEG throughout the entire programming sequence.

- b. Wait TD and raises pin 20 to VCCP and pins 4-8, 11 to VIHP. At the same time, the SEL input (pin 9) is set to either VIHP or VIL in order to select the desired polarity of the input which is to be programmed. When SEL is at VIHP, the input will be programmed high true. When SEL is at VIL, the input will be programmed low true.

- c. Wait TD and pulse the input to be programmed to ground for PWP milliseconds. It should be noted that only one input should be programmed at a time.

- d. After a delay TD, return pin 20 to VCCV and pins 4-8, 11 to VIHV.

- e. Repeat steps b), c), and d) until pins 4-8 have been programmed with the appropriate polarity.

- When all inputs have been programmed as explained above, wait TD and return the programming enable pin (pin 1) to VIL.

#### 4. Fuse Integrity Testing

- Correct programming of the device should be verified by applying test vectors to the input pins.

- b. Fuse integrity is tested by applying VCC to the device and measuring the static power consumption of the device. With all inputs at VCC or GND and the output pins unloaded, the measured ICCSB of the device should be less than 50 µA at VCC = 5V and T = 25°C. This guarantees that all fuses have been blown to a final state which is not marginal and will not create a reliability problem over the life of the device. NOTE: Any device which fails this test should be rejected even if it passes functional testing in order to ensure no future reliability problems associated with marginally blown fuses.

**IMPORTANT:** All five inputs must be programmed regardless of desired high or low input polarity. The advanced design of the fuse select circuitry (Patent Pending) provides for ultra-low post programming ICCSB and requires that one fuse on each input be programmed.