# E<sup>2</sup>PROM CMOS PROGRAMMABLE LOGIC DEVICE

- ELECTRICALLY ERASABLE CELL TECHNOLOGY

- Instantly reconfigurable logic

- Instantly reprogrammable cells

- Guaranteed 100% yields

- HIGH PERFORMANCÉ E<sup>2</sup>CMOS TECHNOLOGY

- Low power: 90mA typical

- High speed: 12ns max. clock to output delay, 25ns max. setup time, 30ns max. propagation delay

- TTL COMPATIBLE INPUTS AND OUTPUTS

- UNPRECEDENTED FUNCTIONAL DENSITY

- 10 Output Logic Macrocells

- 8 Buried Logic Macrocells

- 20 Input and I/O Logic Macrocells

- HIGH-LEVEL DESIGN FLEXIBILITY

- 78 × 64 × 36 FPLA Architecture

- Separate buried register and input clock pins

- Functionally supersets existing 24 pin PAL® and IFL™ devices

- Asynchronous or Synchronous clocking

- SPAĆE SAVING 24 PINS, 300 MILS DIP

- HIGH SPEED PROGRAMMING ALGORITHM

- 20 YEAR DATA RETENTION

#### DESCRIPTION

Using a high performance E<sup>2</sup>CMOS technology, SGS-THOMSON has produced a next-generation programmable logic device, the GAL6001S. Using FPLA architecture known for its superior flexibility in state machine design, the GAL6001S offers the highest degree of functional integration and flexibility currently available in a 24 pin, 300 mils package.

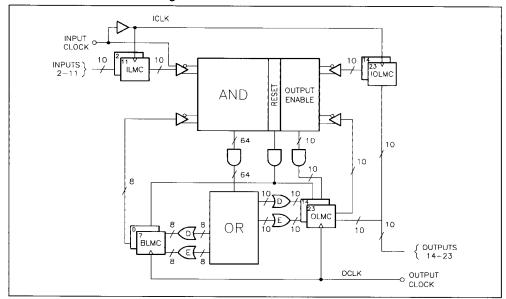

The GAL6001S has 10 programmable Output Logic Macrocells (OLMCs) and 8 programmable Buried Logic Macrocells (BLMCs). In addition, there are 10 Input Logic Macrocells (ILMCs) and 10 I/O Logic Macrocells (IOLMC). Two Clock inputs are provided for independent control of the Input and Output Macrocells.

Advanced features that simplify programming and reduce test time, coupled with E<sup>2</sup>PROM CMOS reprogrammable cells, enable complete AC, DC, programmability, and functionality test of each GAL6001S during manufacture. This allows SGS-THOMSON to guarantee 100% field programmability and functionality to datasheet specifications.

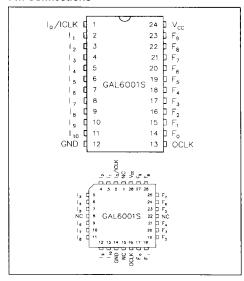

#### Pin Connections

#### Pin Names

| lo-l <sub>10</sub> | Input        |

|--------------------|--------------|

| Fo-F9              | I/O          |

| ICLK               | Input Clock  |

| OCLK               | Output Clock |

| Vcc                | Power        |

| GND                | Ground       |

GAL® is a registered trademark of Lattice Semiconductor Corp.; PAL® is a registered trademark of Monolithic Memories Inc.

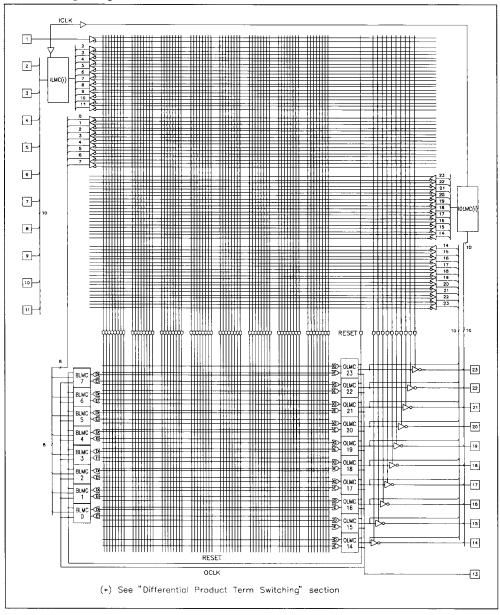

# **GAL6001S Logic Diagram**

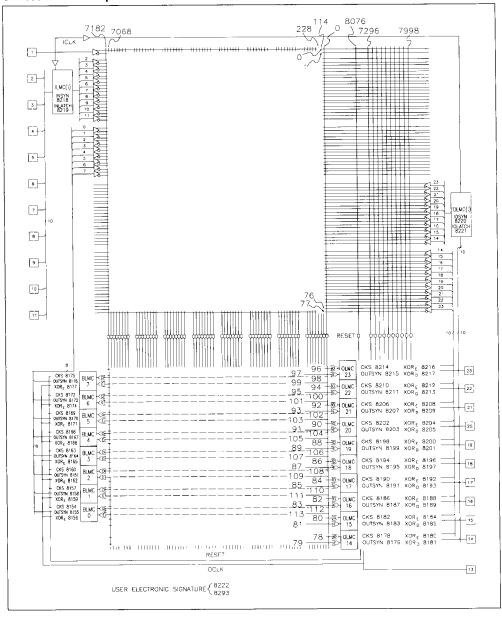

## GAL6001S Jedec Map

Programming is accomplished using standard hardware and software tools. SGS-THOMSON guarantees a minimum of 100 erase write cycles, and data retention to exceed 20 years. An Electronic Signa-

ture word has been provided for user-defined data. In addition, a security cell is available to protect proprietary designs.

## **GAL6001S Functional Block Diagram**

#### **Macrocells Names**

| ILMC  | Input Logic Macrocell  |

|-------|------------------------|

| IOLMC | I/O Logic Macrocell    |

| BLMC  | Buried Logic Macrocell |

| OLMC  | Output Logic Macrocell |

## **Absolute Maximum Ratings**

| Symbol                                          | Parameter                                        | Value                     | Unit |

|-------------------------------------------------|--------------------------------------------------|---------------------------|------|

| Vcc                                             | Supply Voltage                                   | -0.5 to +7                | V    |

| · VI                                            | Input Voltage Applied                            | -2.5 to V <sub>CC+1</sub> | V    |

| VB                                              | Off-State Output (Bidirectional) Voltage Applied | -2.5 to V <sub>CC+1</sub> | V    |

| TstG                                            | Storage Temperature                              | -65 to +125               | ·c   |

| T <sub>J</sub> Junction Temperature (Operating) |                                                  | -40 to +125               | ·c   |

| T <sub>L</sub> Lead Temperature (Soldering)     |                                                  | 260 (for 10s max.)        | .c   |

Stresses above those listed under the "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress only ratings and functional operation of the device at these or at any other conditions above those indicated in the operational sections of this specification is not implied.

4/13

**∠77** 8 8

SGS-THOMSON MICROELECTRONIC

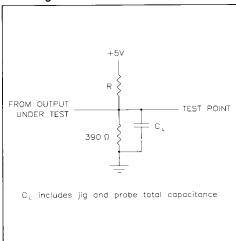

# **Switching Test Conditions**

| Input Pulse Levels                | GND to 3.0V |

|-----------------------------------|-------------|

| Input Rise and Fall Times         | 3ns 10%-90% |

| Input Timing Reference<br>Levels  | 1.5V        |

| Output Timing Reference<br>Levels | 1.5V        |

| Output Load                       | See figure  |

3-state levels are measured 0.5V from steady-state active level.

## **Test Conditions**

| # | <b>R</b> [Ω]                      | C <sub>L</sub> [pF] |

|---|-----------------------------------|---------------------|

| 1 | 300                               | 50                  |

| 2 | Active High: ∞<br>Active Low: 300 | 50                  |

| 3 | Active High: ∞<br>Active Low: 300 | 5                   |

# **Switching Test Circuit**

Capacitance (TA=25°C, f=1.0MHz, Vcc=5V)

| Symbol | Parameter                     | Test Conditions    | Maximum <sup>+</sup> | Units |

|--------|-------------------------------|--------------------|----------------------|-------|

| Cı     | Input Capacitance             | V <sub>I</sub> =2V | 8                    | pF    |

| CB     | Bidirectional Pin Capacitance | V <sub>B</sub> =2V | 10                   | pF    |

<sup>\*</sup> Guarantied but not 100% tested.

# **DC Operating Conditions**

| Symbol | Parameter                 | Commercial<br>Temperature Range    |       | Indus<br>Temperati                | Units              |    |

|--------|---------------------------|------------------------------------|-------|-----------------------------------|--------------------|----|

|        |                           | Min.                               | Max.  | Min.                              | Max.               |    |

| Vcc    | Supply Voltage            | 4.75                               | 5.25  | 4.5                               | 5.5                | ٧  |

| TA     | Ambient Temperature       | 0                                  | 70    | -40                               | 85                 | ņ  |

| VIL    | Input Low Voltage         | V <sub>SS</sub> <sup>\$</sup> -0.5 | 0.8   | V <sub>SS</sub> <sup>♦</sup> -0.5 | 0.8                | ٧  |

| ViH    | Input High Voltage        | 2.0                                | Vcc+1 | 2.0                               | V <sub>CC</sub> +1 | ٧  |

| loL    | Low Level Output Current  | _                                  | 16    | -                                 | 16                 | mA |

| ЮН     | High Level Output Current | -3.2                               | -     | -3.2                              | _                  | mA |

$<sup>^{\</sup>diamond}$  Vss is the voltage applied to the GND pin.

**Electrical Characteristics Over Operating Conditions**

| Symbol   | Parameter                         | Test Conditions                                                    | Commercial<br>Temperature Range |      | Indu<br>Temperat | Units |    |

|----------|-----------------------------------|--------------------------------------------------------------------|---------------------------------|------|------------------|-------|----|

|          |                                   |                                                                    | Min.                            | Max. | Min.             | Max.  |    |

| IH, IIL  | Input Leakage Current             | GND≤V <sub>I</sub> ≤V <sub>CC Max</sub>                            | -                               | ±10  | -                | ±10   | μА |

| IBH, IBL | Bidirectional Pin Leakage Current | GND≤VI≤V CC Max                                                    | _                               | ±10  | _                | ±10   | μА |

| lcc      | Operating Power Supply Current    | f=15 <b>M</b> Hz<br>V <sub>IL</sub> =0.5V<br>V <sub>IH</sub> =3.0V | -                               | 150  | _                | 180   | mA |

| los*     | Output Short Circuit Current      | V <sub>CC</sub> =5.0V, V <sub>B</sub> =0.5V                        | -130                            | -30  | -130             | -30   | mA |

| Vol      | Output Low Voltage                | _                                                                  | -                               | 0.5  | -                | 0.5   | ٧  |

| Vон      | Output High Voltage               | _                                                                  | 2.4                             | _    | 2.4              | _     | ٧  |

<sup>\*</sup>One output at a time for a maximum duration of one second.

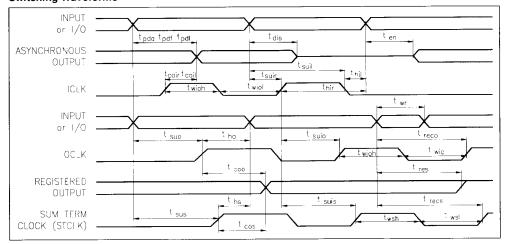

# **Switching Characteristics Over Operating Conditions**

| Symbol            | Parameter                                                        | From                            | То                              | 6001S-30          | 6001S-35 |       | Test   |  |

|-------------------|------------------------------------------------------------------|---------------------------------|---------------------------------|-------------------|----------|-------|--------|--|

| Symbol            | Parameter                                                        | From 10                         |                                 | Max. <sup>☆</sup> | Max.**   | Units | Cond.* |  |

| tpda              | Combinational<br>Propagation Delay<br>(ILMC Async.)              | Input                           | Output                          | 30                | 35       | ns    | 1      |  |

| tpdf              | Combinational<br>Propagation Delay<br>(With Feedback)            | Output,<br>Registered<br>Output | Output                          | 30                | 35       | ns    | 1      |  |

| tpdl              | Combinational<br>Propagation Delay<br>(ILMC Latch)               | Input                           | Output                          | 35                | 40       | ns    | 1      |  |

| tcoir             | Input Clock to<br>Output Delay<br>(ILMC Reg., OLMC<br>Comb.)     | ICLK                            | Output                          | 35                | 40       | ns    | 1      |  |

| t <sub>coil</sub> | Input Clock to<br>Output Delay<br>(ILMC Latch, OLMC<br>Comb.)    | ICLK                            | Output                          | 35                | 40       | ns    | 1      |  |

| tcoo              | Output Clock to<br>Registered Output<br>Delay (OLMC D/E Reg.)    | OCLK                            | Registered<br>Output            | 12                | 13.5     | ns    | 1      |  |

| tcos              | Sum Term Clock<br>to Registered<br>Output Delay<br>(OLMC D Reg.) | STCLK                           | Registered<br>Output            | 35                | 40       | ns    | 1      |  |

| ten               | Product Term<br>Output Enable to<br>Output Delay                 | Input, I/O                      | Output,<br>Registered<br>Output | 25                | 30       | ns    | 2      |  |

| tdis              | Product Term Output<br>Disable to<br>Output Delay                | Input, I/O                      | Output,<br>Registered<br>Output | 25                | 30       | ns    | 3      |  |

| t <sub>res</sub>  | Register Reset Delay                                             | Input, I/O                      | Registered<br>Output            | 35                | 35       | ns    | 1      |  |

<sup>\*</sup> Refer to Switching Test Conditions".

6/13

<sup>&</sup>lt;sup>3</sup> Commercial Temperature range only.

<sup>\*</sup> Industrial Temperature range only.

# **AC Operating Conditions**

|        |                                                               | 6001 | 6001S-30 <sup>3</sup> |      | 6001S-35 <sup>⊕</sup> |       |

|--------|---------------------------------------------------------------|------|-----------------------|------|-----------------------|-------|

| Symbol | Parameter                                                     | Min. | Max.                  | Min. | Max.                  | Units |

| tsuil  | Input Setup Time Before ICLK Fall (ILMC Latch)                | -    | 2.5                   | -    | 3.5                   | ns    |

| tsuir  | Input Setup Time Before ICLK Rise (ILMC Reg.)                 | -    | 2.5                   | _    | 3.5                   | ns    |

| tsuo   | Input or Feedback Setup Time Before OCLK Rise (OLMC D/E Reg.) | -    | 25                    | _    | 30                    | ns    |

| tsus   | Input or Feedback Setup Time Before STCLK Rise (OLMC D Reg.)  | -    | 7.5                   | _    | 10                    | ns    |

| tsuio  | ICLK Rise Setup Time Before OCLK Rise (OLMC D/E Reg.)         | -    | 30                    | _    | 35                    | ns    |

| tsuis  | ICLK Rise Setup Time Before STCLK Rise (OLMC D Reg.)          |      | 15                    | _    | 17                    | ns    |

| thil   | Hold Time After ICLK Fall (ILMC Latch)                        |      | 5                     | _    | 5                     | ns    |

| thir   | Hold Time After ICLK Rise (ILMC Reg.)                         |      | 5                     | -    | 5                     | ns    |

| tho    | Hold Time After OCLK Rise (OLMC D/E Reg.)                     |      | 5                     | -    | 5                     | ns    |

| ths    | Hold Time After STCLK Rise (OLMC D Reg.)                      | -    | 10                    | -    | 12.5                  | ns    |

| twich  | ICLK or OCLK Pulse Duration High                              | -    | 10                    | _    | 10                    | ns    |

| twiol  | ICLK or OCLK Pulse Duration Low                               | -    | 10                    | -    | 10                    | ns    |

| twsh   | STCLK Pulse Duration High                                     | -    | 15                    |      | 15                    | ns    |

| tws    | STCLK Pulse Duration Low                                      | -    | 15                    | -    | 15                    | ns    |

| twr    | Reset Pulse Duration                                          | -    | 15                    | _    | 15                    | ns    |

| treco  | Reset to OCLK Recovery Time                                   |      | 20                    | -    | 20                    | ns    |

| trecs  | Reset to STCLK Recovery Time                                  | -    | 10                    | -    | 10                    | ns    |

| fclk   | OCLK or STCLK Maximum Frequency                               | 27   | _                     | 22.9 | _                     | MHz   |

<sup>\*</sup> Commercial Temperature range only.

# **Switching Waveforms**

<sup>\*</sup> Industrial Temperature range only.

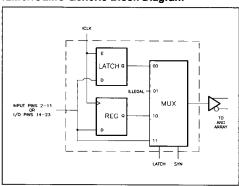

# INPUT LOGIC MACROCELL (ILMC) AND I/O LOGIC MACROCELL (IOLMC)

The GAL6001S features two configurable input sections.

The ILMC section corresponds to the dedicated input pins (2-11) and the IOLMC section to the I/O pins (14-23). Each input section is configurable as a block for asynchronous, latched, or registered inputs. Pin 1 (ICLK) is used as an enable input for latched macrocells (transparent when high) and as a clock for registered macrocells (positive edge triggered).

Configurable input blocks can be used to advantage by system designers. Registered inputs are popular for synchronization and data merging. Transparent

latches are useful when the input data is invalid outside a known time window. Direct inputs are used in systems where the input data is well ordered in time. With the GAL6001S, external registers and latches are not necessary.

The various configurations of the Input and I/O Macrocells are controlled by programming four architecture control bits (LATCH and SYN both for Input and I/O Macrocells) within the 68 bits Architecture Control Word. The SYN bits determine whether the macrocells will have register/latch capability or will be strictly asynchronous. The LATCH bits select between latched and registered inputs.

The three valid macrocell configurations are shown in the macrocell equivalent diagrams shown below.

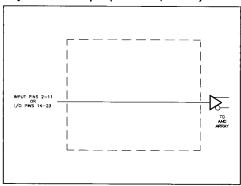

#### **ILMC/IOLMC Generic Block Diagram**

# Asynchronous Input (LATCH=1, SYN=1)

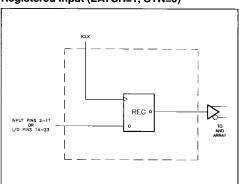

#### Registered Input (LATCH=1, SYN=0)

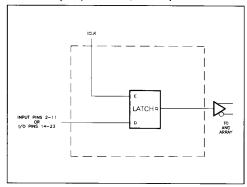

## Latched Input (LATCH=0, SYN=0)

# OUTPUT LOGIC MACROCELL (OLMC) AND BURIED LOGIC MACROCELL (BLMC)

The outputs of the OR array feed two groups of macrocells. One group of eight macrocells is buried; its output feed back directly into the AND array rather than to device pins. These cells are called the Buried Logic Macrocells (BLMC): they are useful for building state machines. The second group of macrocells consists of 10 cells whose outputs, in addition to feeding back into the AND array, are available at the device pins. Cells in this group are known as Output Logic Macrocells (OLMC).

Like the ILMCs and IOLMCs discussed above, Output and Buried Logic Macrocells are configured by programming specific bits in the Architecture Control Word (CKS(i), OUTSYN(i), XOR<sub>D</sub>(i), XOR<sub>E</sub>(i)),

but unlike the Input Macrocells which must be configured in blocks, these macrocells are configurable on a macrocell-by-macrocell basis. Throughout this data sheet, i=[14..23] for OLMCs and i=[0...7] for BLMCs.

Buried and Output Logic Macrocells may be set to one of three valid configurations: combinational, D type registered with sum term (asynchronous) clock or D/E type registered.

Output macrocells always have I/O capability, with directional control provided by the 10 output enable (OE) product terms. Additionally, the polarity of each OLMC output is selectable through the XOR<sub>D</sub>(i) architecture bits. Polarity selection is available for BLMCs, since both the true and complemented forms of their outputs are available in the AND array.

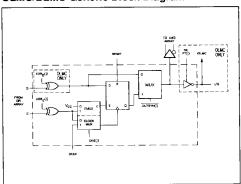

## **OLMC/BLMC Generic Block Diagram**

# Combinational (CKS(i)=0, OUTSYN(i)=1)

# D/E Type Registered (CKS(i)=1, OUTSYN(i)=0)

Polarity of all "E" sum terms is selectable through the XOR<sub>E</sub>(i) architecture control bits.

When CKS(i) = 1 and OUTSYN(i) = 0, macrocell "i" is set as "D/E type registered". In this configuration, the register is clocked from the common OCLK and the register clock enable input is controlled by the associated "E" sum term. This configuration is useful for building counters and state-machines with state hold functions.

When the macrocell is configured as a "D type registered with a sum term asynchronous clock" (CKS(i) = 0 and OUTSYN(i) = 0), the register is always enabled and its "E" sum term is routed directly to the clock input. This permits asynchronous programmable clocking, selected on a register-by-register basis.

When CKS(i) = 0 and OUTSYN(i) = 1, macrocell "i" is set as "combinational". Configuring a BLMC in this manner turns it into a complement array. Complement arrays are used to construct multi-level logic. Registers in both the Output and Buried Logic Macrocells feature a common RESET product term. This active high product term allows the registers to be asynchronously reset. Registers are reset to a logic zero. If connected to an output pin, a logic one will occur because of the inverting output buffer.

There are two possible feedback paths from each OLMC: one directly from the OLMC (this feedback is before the output buffer and always present), and one from OLMC after the output buffer through the IOLMC. The second path is usable as a feedback only when the associated bidirectional pin is being used as an output. With this dual feedback arrangement, the OLMC can be permanently buried (the associate OLMC pin is an input), or dynamically buried with the use of the output enable product term. The D/E registers used in this device offer the designer the ultimate in flexibility and utility. The D/E register architecture can emulate RS, JK, and T type registers with the same efficiency as a dedicated RS, JK, or T register.

The three valid macrocell configurations are shown in the macrocell equivalent diagrams shown in the previous page.

#### **ARRAY DESCRIPTION**

The GAL6001S E<sup>2</sup> reprogrammable array is subdivided into two smaller arrays; the first is an AND and the second is an OR array. These arrays are described in detail below.

#### AND ARRAY

The AND array is organized as 78 input terms by 75 product term outputs. The 10 ILMC, 10 I/O Logic Macrocells, 8 BLMC feedbacks, 10 OLMC feedbacks, and ICLK comprise the 39 inputs to this array (each available in true and complemented forms). Product terms 0-63 serve as inputs to the OR array. Product term 64 is the RESET PT; it generates the RESET signal described in the earlier discussion of Output and Buried Logic Macrocells. Product terms

65-74 are the output enable product terms; they control the output buffers, thus enabling device pins 14-23 to be bidirectional or 3-state.

### OR ARRAY

The OR array is organized as 64 inputs by 36 sum term outputs. 64 product terms from the AND array serve as the inputs to the OR array. Of the 36 sum term outputs, 18 are data ("D") terms and 18 are enable/clock ("E") terms. These terms feed into the 10 OLMCs and 8 BLMCs, one "D" term and one "E" term to each.

The programmable OR array offers unparalleled versatility in product term usage. This programmability allows from 1 to 64 product terms to be connected to a single sum term. A programmable OR array is more flexible than a fixed, shared, or variable product term architecture.

## ARCHITECTURE CONTROL WORD

The various configurations of the GAL6001S are enabled by programming cells within the Architecture Control Word. This 68 bits word contains all of the chip configuration data. This data includes: XOR<sub>D</sub>(i), XOR<sub>E</sub>(i), CKS(i), OUTSYN(i), and LATCH and SYN bits both for ILMCs and IOLMCs. The function of each of these bits has been previously explained.

#### **USER ELECTRONIC SIGNATURE WORD**

An User Electronic Signature word (UES) is provided with GAL6001S device. The User Electronic Signature word is a 72 bits user definable storage area, which can be used to save inventory control data, pattern revision numbers, manufacture date, etc. Signature data is always available to the user, regardless of the state of the security cell.

Note: UES is included in checksum calculations. Changing the UES will alter the checksum.

#### SECURITY CELL

A security cell is provided with GAL6001S device as a deterrent to unauthorized copying of the array patterns. Once programmed, this cell prevents further read access to the AND and OR arrays. This cell can be erased only during a bulk erase cycle, so the original configuration can never be examined once this cell is programmed. User Electronic Signature data is always available to the user, regardless of the state of this control cell.

#### **BULK ERASE**

Before writing a new pattern into a previously programmed part, the old pattern must first be erased. This erasure is done automatically by the programming hardware as part of the programming cycle and takes only 50 milliseconds.

#### REGISTERED PRELOAD

When testing state machine designs, all possible states and state transitions must be verified, not just those required during normal operations. This verification is necessary because in system operation

10/13

certain events may occur that cause the logic to assume an illegal state: power-up, brown out, line voltage glitches, etc. To test a design for proper management of these conditions, a method must be provided to break the feedback paths and force any desired state (e.g. an illegal state) into the registers. Then the machine can be sequenced and the outputs tested for correct next state generation. All registers in the GAL6001S can be preloaded, including the ILMC, IOLMC, OLMC, and BLMC registers. The programming hardware takes care or all preload timing and voltage requirements.

#### **INPUT BUFFERS**

GAL devices are designed with TTL level compatible input buffers. These buffers, with their characteristically high impedance, load driving logic much less than traditional bipolar devices.

This allows for a greater fan out from the driving

logic.

GĂL6001S does not include active pull-ups within its input structures. As a result, SGS-THOMSON recommends that all unused inputs and 3-state I/O pins be connected to another active input,  $V_{\rm CC}$ , or GND. This precaution improves the noise immunity and reduces the  $I_{\rm CC}$  consumption.

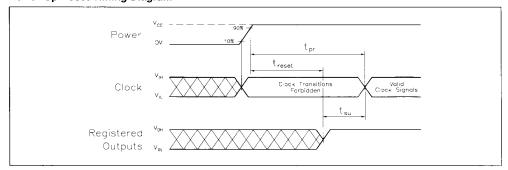

#### POWER-UP RESET

Circuitry within the GAL6001S provides a reset signal to all registers during power-up. All internal registers will have their Q outputs set low after a specified time (treset=10µs). As a result, the state on the registered output pins (if they are enabled) will always be high after power-up, regardless of the programmed polarity of the output pins. This feature can greatly simplify state machine design by providing a known state upon power-up.

The timing diagram for power-up is shown below. Because of the asynchronous nature of system power-up, the  $V_{\rm CC}$  rise must be monotonic to guarantee a valid power-up reset of the GAL6001S. The registers will reset within a maximum of  $t_{\rm reset}$  time. As in normal system operation, avoid clocking the

device until all input and feedback path setup times have elapsed (i.e. avoid clocking before the  $t_{\text{pr}}$ = $t_{\text{reset}}$ + $t_{\text{su}}$  time interval).

# DIFFERENTIAL PRODUCT TERM SWITCHING (DPTS)

The number of "Differential Product Term Switching" (DPTS) for a given design is calculated by taking the absolute value of:

- the total number of product terms that are switching from a logical level high to a logical level low

- minus the total number of those switching from a logical level low to a logical level high

within a 5ns time window.

The correct behaviour of the device is guaranteed for applications where the number of DPTS is not greater than 15. This limit is believed to be largely conservative. For the device to exhibit an incorrect behaviour, other conditions of supply voltage, clock timing, temperature, etc., should be simultaneously present. As each of these conditions may, to some extent, lay partly within the operating range limits, it is simpler to refer to a DPTS boundary that ensures ample margin in all conditions for a correct operation.

There is no limit on the number of product terms that can be used at the same time.

### **LATCH-UP PROTECTION**

GAL6001S devices are designed with an on-board charge pump to negatively bias the substrate. The negative bias is of sufficient magnitude to prevent external disturbances from causing the circuitry to latch. Additionally, outputs are designed with n-channel pull-ups instead of the traditional p-channel pull-ups to eliminate any possibility of SCR induced latching.

#### Power-Up Reset Timing Diagram

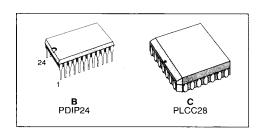

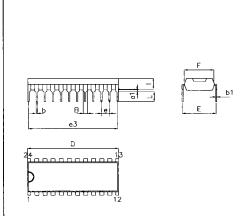

# PDIP 24 Pins

| Dim.   | mm   |       |       | inches |       |       |

|--------|------|-------|-------|--------|-------|-------|

| Dilli. | Min  | Тур   | Max   | Min    | Тур   | Max   |

| a1     | 0.38 |       |       | 0.015  |       |       |

| В      | 1.27 |       | 1.65  | 0.050  |       | 0.065 |

| b      |      | 0.46  |       |        | 0.018 |       |

| b1     |      | 0.25  |       |        | 0.010 |       |

| D      |      |       | 31.88 |        |       | 1.255 |

| E      |      | 7.62  |       |        | 0.300 |       |

| е      |      | 2.54  |       |        | 0.100 |       |

| е3     |      | 27.94 |       |        | 1.100 |       |

| F      |      |       | 6.86  |        |       | 0.27  |

| I      |      |       | 4.32  |        |       | 0.170 |

| L      |      | 3.30  |       |        | 0.130 |       |

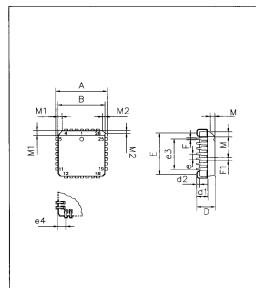

# PLCC 28 Pins

| Dim. |       | mm    |       | inches |       |       |  |

|------|-------|-------|-------|--------|-------|-------|--|

| Dim. | Min   | Тур   | Max   | Min    | Тур   | Max   |  |

| Α    | 12.32 |       | 12.57 | 0.485  |       | 0.495 |  |

| В    | 11.43 |       | 11.58 | 0.450  |       | 0.456 |  |

| D    | 4.20  |       | 4.57  | 0.165  |       | 0.180 |  |

| d1   | 2.29  |       | 3.04  | 0.090  |       | 0.120 |  |

| d2   | 0.51  |       |       | 0.020  |       |       |  |

| E    | 9.91  |       | 10.92 | 0.390  |       | 0.430 |  |

| е    |       | 1.27  |       |        | 0.050 |       |  |

| e3   |       | 7.62  |       |        | 0.300 |       |  |

| e4   |       |       | 1.99  |        |       | 0.078 |  |

| F    |       | 0.46  |       |        | 0.018 |       |  |

| F1   |       | 0.71  |       |        | 0.028 |       |  |

| М    |       | 1.24  |       |        | 0.049 |       |  |

| M1   |       | 1.143 |       |        | 0.045 |       |  |

| M2   |       |       | 0.51  |        |       | 0.020 |  |

Seating Plane: 0.101 mm/0.004 inches

12/13

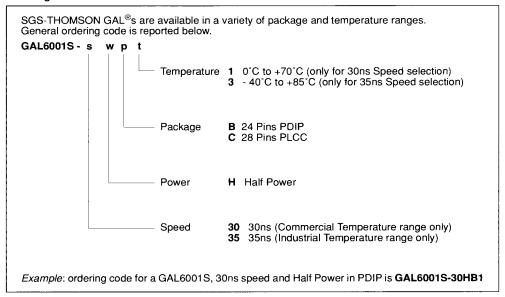

# Ordering Informations\*

<sup>\*</sup> Please contact local Product Marketing for latest update on package / temperature range availability.