# L64724 Satellite Receiver

# **Technical Manual**

April 2000

Orner Number I14030

This document contains proprietary information of LSI Logic Corporation. The information contained herein is not to be used by or disclosed to third parties without the express written permission of an officer of LSI Logic Corporation.

#### Document DB14-000032-03, April 2000

This document describes release B of LSI Logic Corporation's L64724 Satellite Receiver and will remain the official reference source for all revisions/releases of this product until rescinded by an update.

#### To receive product literature, visit us at http://www.lsilogic.com.

LSI Logic Corporation reserves the right to make changes to any products herein at any time without notice. LSI Logic does not assume any responsibility or liability arising out of the application or use of any product described herein, except as expressly agreed to in writing by LSI Logic; nor does the purchase or use of a product from LSI Logic convey a license under any patent rights, copyrights, trademark rights, or any other of the intellectual property rights of LSI Logic or third parties.

Copyright © 2000 by LSI Logic Corporation. All rights reserved.

#### TRADEMARK ACKNOWLEDGMENT

The LSI Logic logo design and G10 are registered trademarks of LSI Logic Corporation. All other brand and product names may be trademarks of their respective companies.

# **Contents**

| Chapter 1 | Intro | duction                                          |      |

|-----------|-------|--------------------------------------------------|------|

| •         | 1.1   | General Description                              | 1-1  |

|           | 1.2   | Typical Application                              | 1-3  |

|           | 1.3   | Features Summary                                 | 1-5  |

| Chapter 2 | L647  | 24 Signal Definitions                            |      |

| •         | 2.1   | Channel Interface                                | 2-3  |

|           | 2.2   | Channel Clock Interface                          | 2-4  |

|           | 2.3   | Phase-Locked Loop (PLL) Interface                | 2-4  |

|           | 2.4   | Control Signals Interface                        | 2-5  |

|           | 2.5   | AGC/Clock Control Interface                      | 2-6  |

|           | 2.6   | Channel Data Output Interface                    | 2-6  |

|           | 2.7   | Analog-to-Digital Converter (ADC) Interface      | 2-7  |

|           | 2.8   | Microcontroller Interfaceea                      | 2-8  |

| Chapter 3 | L647  | 24 Registers                                     |      |

| -         | 3.1   | L64724 Register Overview                         | 3-1  |

|           | 3.2   | Reset and How it Affects Registers               | 3-7  |

|           | 3.3   | Groups 0 and 1: Address Pointer Register         | 3-8  |

|           | 3.4   | Group 2: System Mode and System Status Registers | 3-9  |

|           | 3.5   | Group 3: Status Registers                        | 3-23 |

|           | 3.6   | Group 4: Configuration Registers                 | 3-33 |

|           | 3.7   | Group 5: Self-Tuning Microcontroller Registers   | 3-77 |

|           | 3.8   | Group 6: Reserved (Internal Use Only)            | 3-81 |

|           | 3.9   | Group 7: Arbiter Control Register                | 3-81 |

|           | 3.10  | Reset Effect on Register Bits                    | 3-82 |

|           | 3.11  | Internal Data Path Reset Effects                 | 3-84 |

Contents iii

| Chapter 4 | Chan  | nel Interfaces and Data Control                   |      |

|-----------|-------|---------------------------------------------------|------|

| •         | 4.1   | Data Control and Clocking Schemes                 | 4-2  |

|           | 4.2   | PLL Clock Generation                              | 4-3  |

|           | 4.3   | Data Path Input Interface                         | 4-12 |

|           | 4.4   | Data Output Interface                             | 4-14 |

| Chapter 5 | Demo  | odulator Module Functional Description            |      |

|           | 5.1   | Overview                                          | 5-2  |

|           | 5.2   | Analog to Digital Conversion                      | 5-2  |

|           | 5.3   | DC Offset Compensation and Coupling to ADC Output | 5-3  |

|           | 5.4   | Decimation Filters                                | 5-4  |

|           | 5.5   | Matched Filter                                    | 5-7  |

|           | 5.6   | Timing Clock Recovery                             | 5-8  |

|           | 5.7   | Carrier Recovery Loop                             | 5-12 |

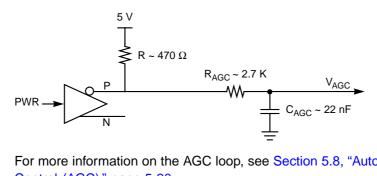

|           | 5.8   | Automatic Gain Control (AGC)                      | 5-20 |

|           | 5.9   | Output Control                                    | 5-22 |

|           | 5.10  | External Controls                                 | 5-23 |

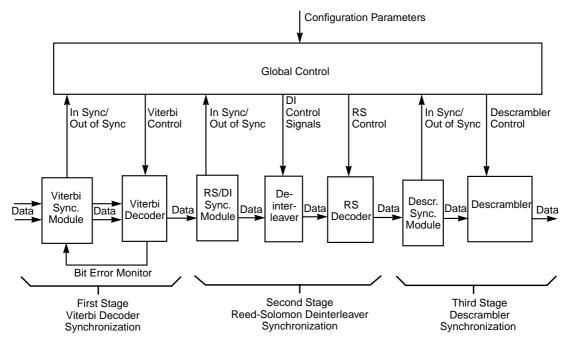

| Chapter 6 | Deco  | ding Pipeline Synchronization                     |      |

| •         | 6.1   | Synchronization Scheme                            | 6-1  |

|           | 6.2   | Viterbi Decoder Synchronization                   | 6-2  |

|           | 6.3   | Reed-Solomon Deinterleaver Synchronization        | 6-8  |

|           | 6.4   | Descrambler Synchronization                       | 6-13 |

| Chapter 7 | The I | FEC Decoder Pipeline                              |      |

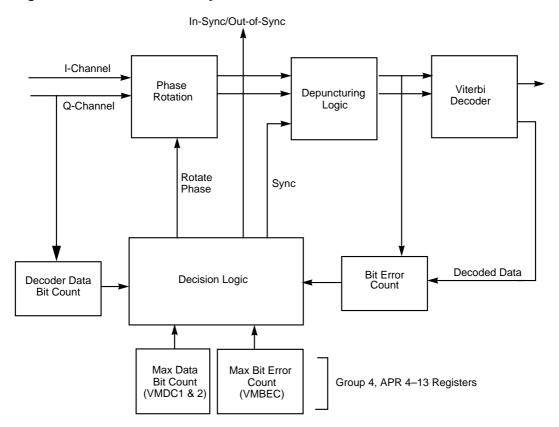

| •         | 7.1   | Viterbi Decoder Module                            | 7-1  |

|           | 7.2   | Deinterleaver Module                              | 7-8  |

|           | 7.3   | Reed-Solomon Decoder                              | 7-10 |

|           | 7.4   | Descrambler Module Architecture and Operation     | 7-15 |

|           | 7.5   | FEC Module Software Reset                         | 7-17 |

| Chapter 8 | L647  | 24 Specifications                                 |      |

| •         | 8.1   | Electrical Requirements                           | 8-1  |

|           | 8.2   | AC Timing                                         | 8-6  |

|           | 83    | L64724 Packaging                                  | 8-15 |

iv Contents

| Appendix A | Prog | ramming the L64724 Using the Serial Bus Protocol         |      |

|------------|------|----------------------------------------------------------|------|

|            | A.1  | Serial Bus Protocol Overview                             | A-2  |

|            | A.2  | Programming the Slave Address Using the Serial Bus       |      |

|            |      | Interface                                                | A-4  |

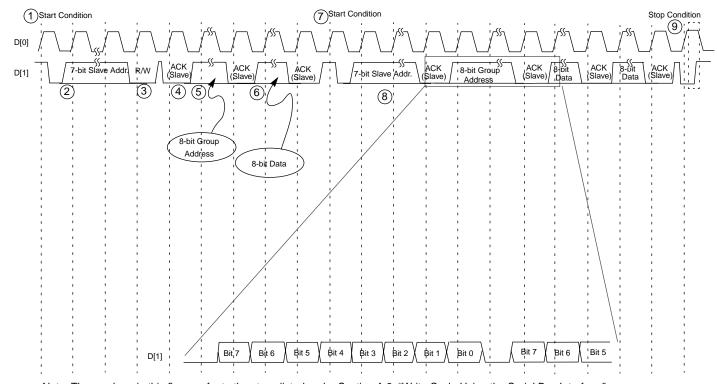

|            | A.3  | Write Cycle Using the Serial Bus Interface               | A-4  |

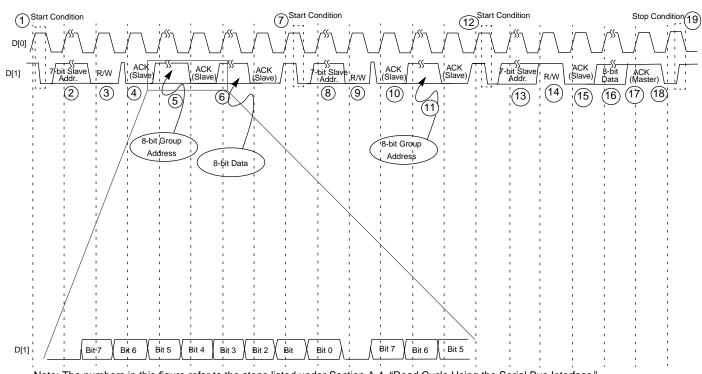

|            | A.4  | Read Cycle Using the Serial Bus Interface                | A-7  |

| Appendix B | L647 | 724 Application Notes                                    |      |

|            | B.1  | L64724 QPSK Demodulator Acquisition and Debugging        |      |

|            |      | Tips                                                     | B-1  |

|            | B.2  | Demodulator Configuration Tips                           | B-5  |

|            | B.3  | QPSK Demodulator and FEC Configuration Example:          |      |

|            |      | High Data Rates                                          | B-10 |

|            | B.4  | QPSK Demodulator and FEC Configuration Example:          |      |

|            |      | Low Data Rates                                           | B-30 |

| Appendix C | Prog | ramming the Serializer                                   |      |

|            | C.1  | Serializer Overview                                      | C-1  |

|            | C.2  | Serializer Interface Signals and Configuration Registers | C-2  |

|            | C.3  | Programming for Serial Mode (2-Wire Compliant)           | C-4  |

|            | C.4  | Programming for 3-Wire Mode                              | C-6  |

| Appendix D | A/D  | Converters                                               |      |

| •          | D.1  | ADC Overview                                             | D-2  |

|            | D.2  | Board Level Interface                                    | D-2  |

|            | D.3  | DC Characteristics                                       | D-5  |

|            | D.4  | AC Characteristics                                       | D-5  |

| Appendix E | L647 | 24 On-chip Microcontroller                               |      |

|            | E.1  | L64724 Microcontroller Instruction Set                   | E-2  |

|            | E.2  | Microcontroller Address Map                              | E-5  |

|            |      | •                                                        |      |

**Customer Feedback**

Contents

| _ |   |        |   |   |   |   |

|---|---|--------|---|---|---|---|

| _ |   | $\sim$ |   |   | ^ | • |

| г | ı | α      | u | • | c | 3 |

| - | - | 3      | • | • | _ | _ |

| 1.1  | L64724 Block Diagram                                  | 1-2  |

|------|-------------------------------------------------------|------|

| 1.2  | Set-Top Decoder Box Block Diagram                     | 1-4  |

| 2.1  | L64724 Logic Symbol                                   | 2-2  |

| 3.1  | Register File Structure                               | 3-3  |

| 3.2  | Issue a Hard Reset                                    | 3-5  |

| 3.3  | Initialize APR0 and APR1 to Zero                      | 3-5  |

| 3.4  | Write Locations 0 and 1 in Group 4                    | 3-6  |

| 3.5  | Read Back Group 4                                     | 3-6  |

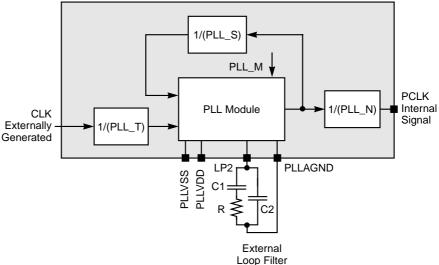

| 4.1  | L64724 Clocking: Internal PLL                         | 4-2  |

| 4.2  | PLL Clock Synthesis                                   | 4-4  |

| 4.3  | L64724 Functional Blocks in the Decoding Pipeline     | 4-12 |

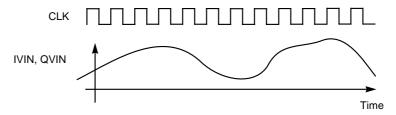

| 4.4  | CLK and Analog Inputs for Channel Data Input          | 4-13 |

| 4.5  | CLK and Digital Inputs for ADC Bypass Mode            | 4-13 |

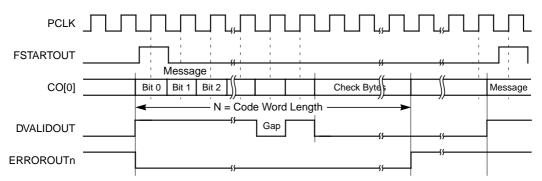

| 4.6  | Parallel Output Interface Waveforms                   | 4-15 |

| 4.7  | Descrambler Parallel Output Waveforms                 | 4-16 |

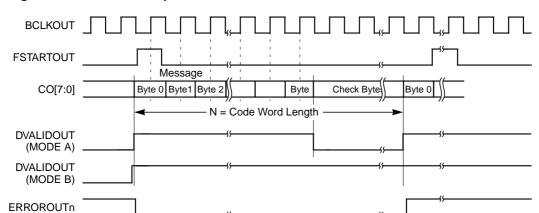

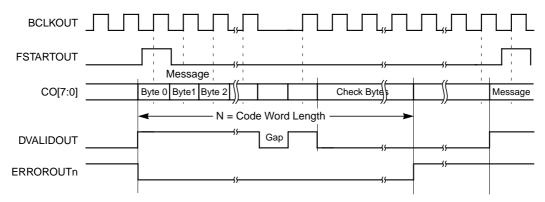

| 4.8  | Descrambler Serial Output Waveforms                   | 4-17 |

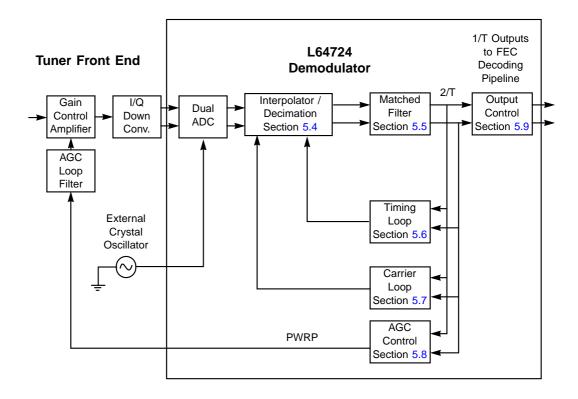

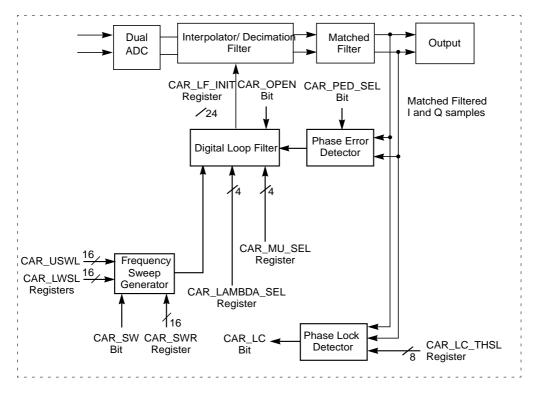

| 5.1  | Demodulator Module and Associated Circuitry           | 5-2  |

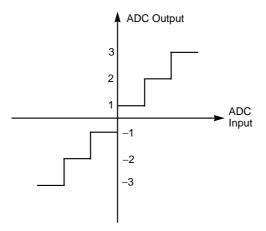

| 5.2  | Input Quantization                                    | 5-3  |

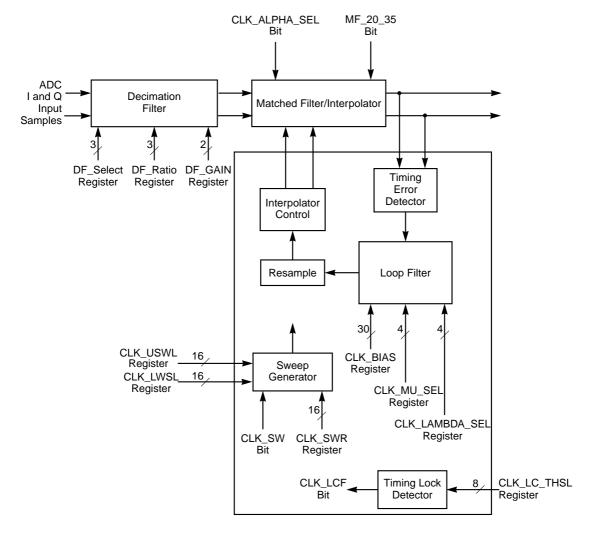

| 5.3  | Clock Recovery Loop                                   | 5-8  |

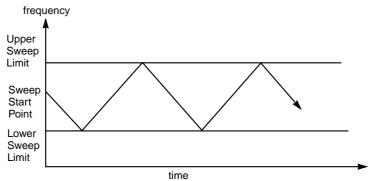

| 5.4  | Timing Loop Sweep Operation                           | 5-11 |

| 5.5  | Carrier Recovery Loop                                 | 5-12 |

| 5.6  | Frequency Sweeping                                    | 5-13 |

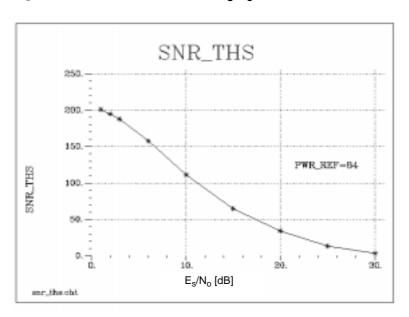

| 5.7  | SNR Threshold vs. E <sub>s</sub> /N <sub>o</sub>      | 5-17 |

| 5.8  | Carrier Loop Filter Parameters                        | 5-17 |

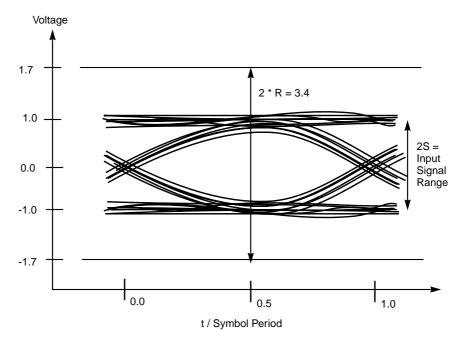

| 5.9  | Eye Pattern and ADC Range                             | 5-20 |

| 5.10 | AGC Loop Control                                      | 5-22 |

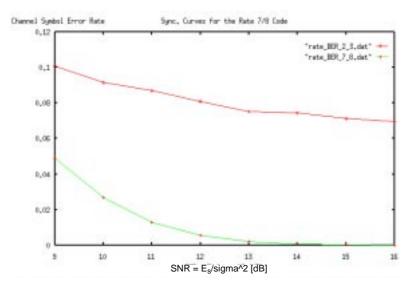

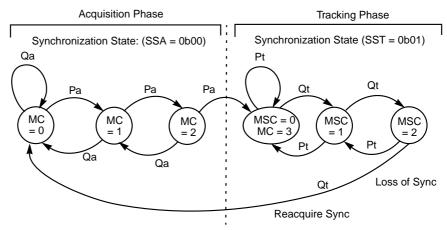

| 6.1  | Synchronization Module                                | 6-2  |

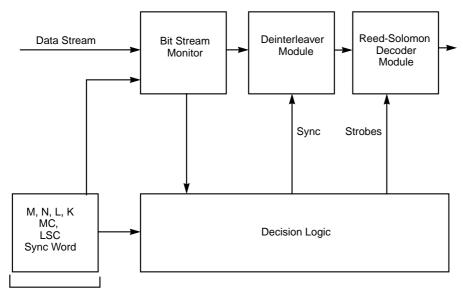

| 6.2  | Viterbi Decoder Synchronization                       | 6-3  |

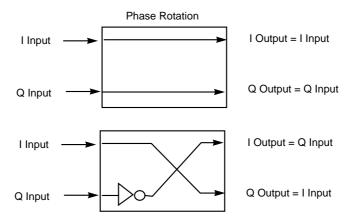

| 6.3  | Phase Rotation for Synchronization                    | 6-4  |

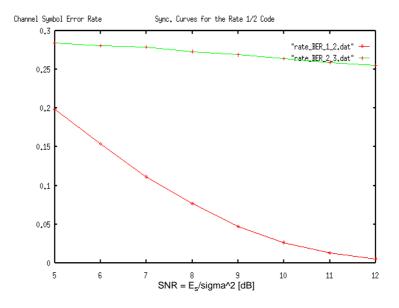

| 6.4  | Channel Symbol Error Rate vs. SNR for Rate = 1/2 Code | 6-5  |

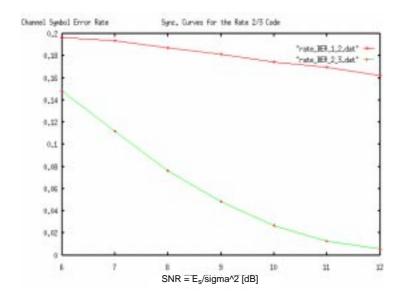

| 6.5  | Channel Symbol Error Rate vs. SNR for Rate = 2/3 Code | 6-5  |

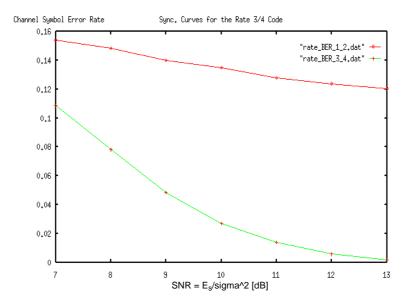

| 6.6  | Channel Symbol Error Rate vs. SNR for Rate = 3/4 Code | 6-6  |

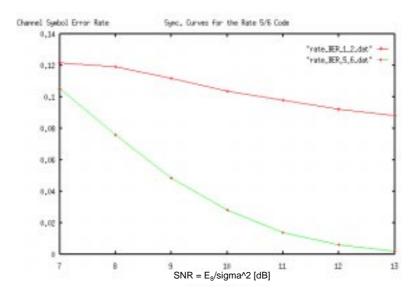

| 6.7  | Channel Symbol Error Rate vs. SNR for Rate = 5/6 Code | 6-6  |

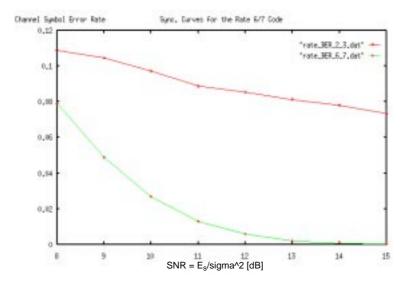

| 6.8  | Channel Symbol Error Rate vs. SNR for Rate = 6/7 Code | 6-7  |

| 6.9  | Channel Symbol Error Rate vs. SNR for Rate = 7/8 Code | 6-7  |

| 6.10 | Reed-Solomon, Deinterleaver Synchronization           | 6-8  |

vi Contents

| 6.11 | Synchronization, Tracking, and Loss of Sync for Three |      |

|------|-------------------------------------------------------|------|

|      | Missed Sync Words                                     | 6-9  |

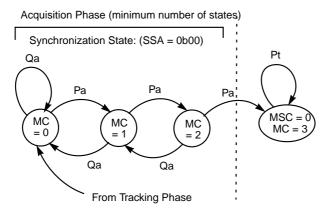

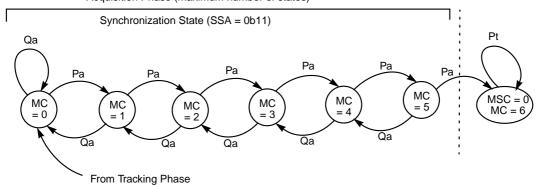

| 6.12 | Minimum and Maximum Number of States in the           |      |

|      | Acquisition Phase                                     | 6-10 |

| 6.13 | Minimum and Maximum Number of States in the           |      |

|      | Tracking Phase                                        | 6-11 |

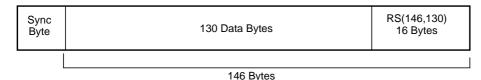

| 6.14 | DSS Packet                                            | 6-12 |

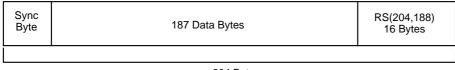

| 6.15 | MPEG-2 Transport Packet                               | 6-12 |

| 6.16 | L64724 Transport Packet                               | 6-12 |

| 6.17 | Descrambler Synchronization                           | 6-13 |

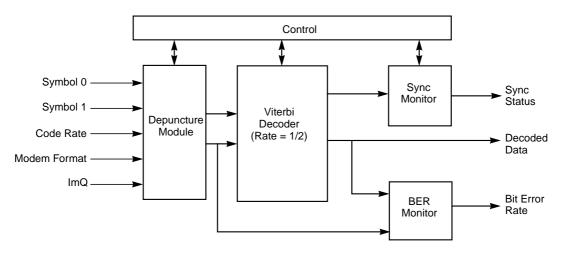

| 7.1  | Viterbi Decoder Block Diagram                         | 7-2  |

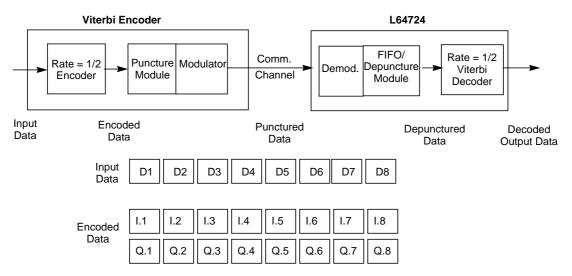

| 7.2  | Puncturing and Depuncturing Block Diagram             | 7-4  |

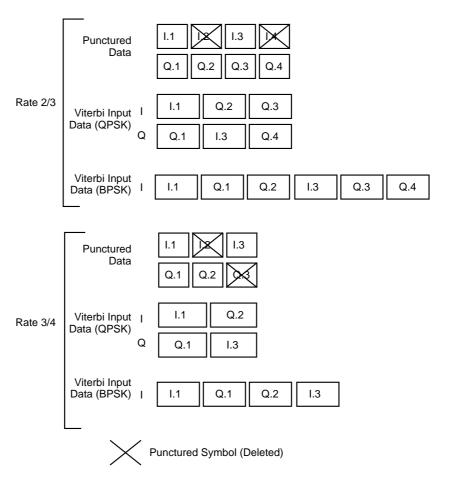

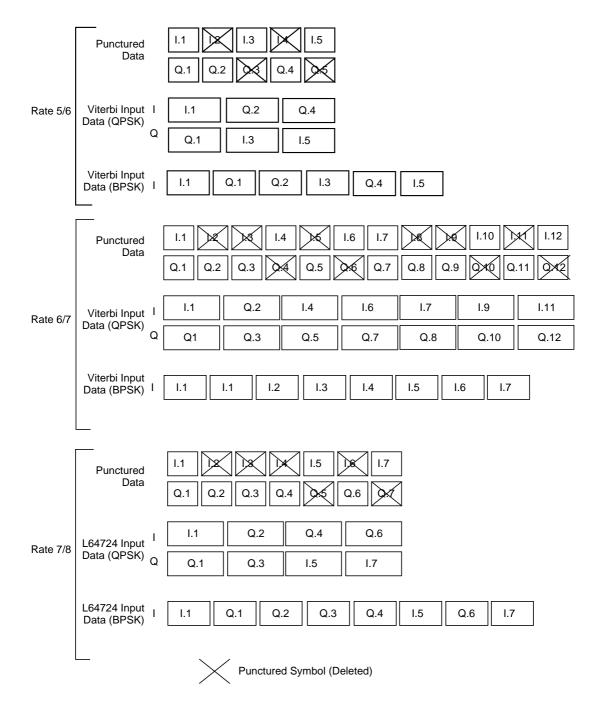

| 7.3  | Puncture Pattern for Different Code Rates             | 7-5  |

| 7.4  | Block Diagram of Viterbi Bit Error Detection Circuit  | 7-7  |

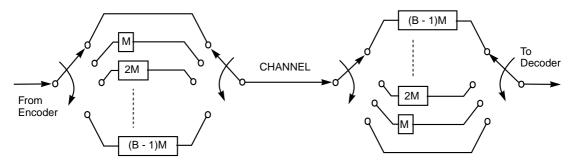

| 7.5  | Interleaving/Deinterleaving Operation for DVB         | 7-8  |

| 7.6  | Interleaving/Deinterleaving Operation for DSS         | 7-9  |

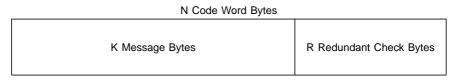

| 7.7  | Code Word Structure                                   | 7-12 |

| 7.8  | FEC Data Path                                         | 7-12 |

| 7.9  | 122-Bit Burst Example                                 | 7-14 |

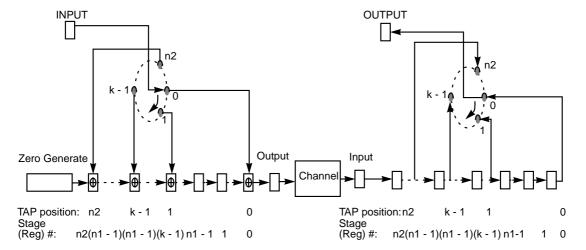

| 7.10 | Descrambler Block Diagram                             | 7-16 |

| 7.11 | 15-Bit Shift Register Initialization                  | 7-16 |

| 7.12 | Inverted Sync Words in Descrambler                    | 7-17 |

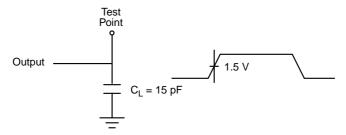

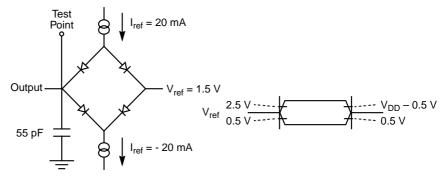

| 8.1  | AC Test Load and Waveform for Standard Outputs        | 8-6  |

| 8.2  | AC Test Load and Waveforms for 3-State Outputs        | 8-6  |

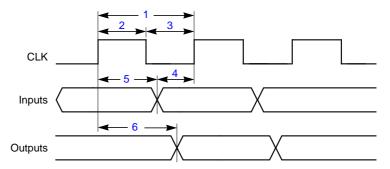

| 8.3  | L64724 Synchronous AC Timing                          | 8-7  |

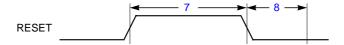

| 8.4  | L64724 RESET Timing Diagram                           | 8-7  |

| 8.5  | L64724 Bus 3-State Delay Timing                       | 8-7  |

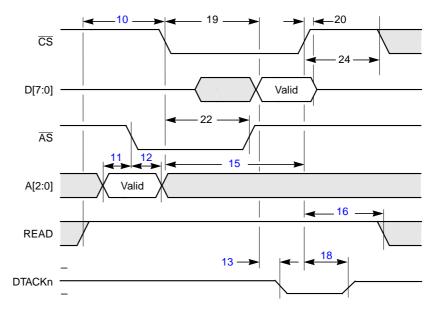

| 8.6  | L64724 Decoder Read Cycle                             | 8-8  |

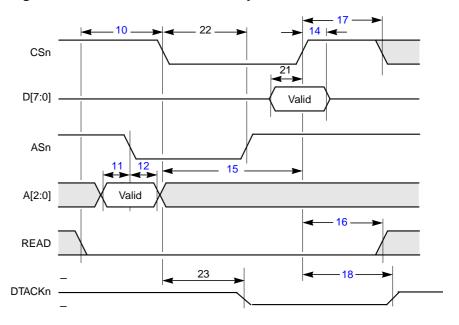

| 8.7  | L64724 Decoder Write Cycle                            | 8-8  |

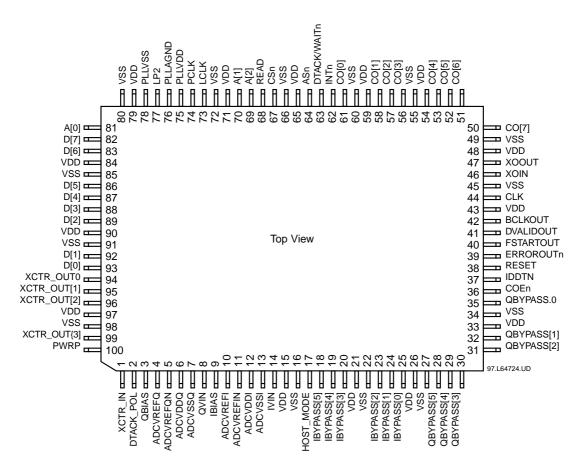

| 8.8  | 100-Pin PQFP/MQFP Pinout                              | 8-16 |

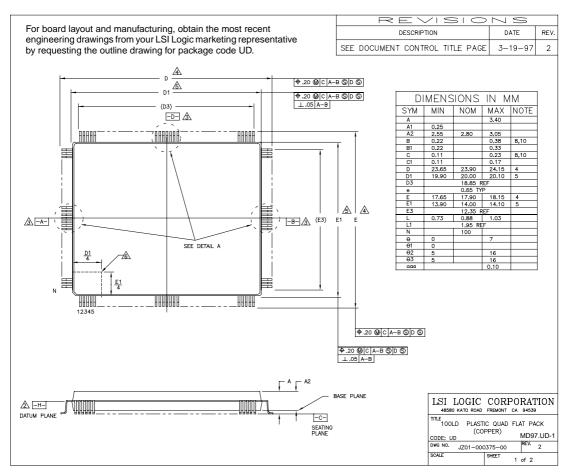

| 8.9  | 100-Pin PQFP/MQFP Mechanical Drawing                  | 8-17 |

| 8.9  | 100-Pin PQFP/MQFP Mechanical Drawing (Cont.)          | 8-18 |

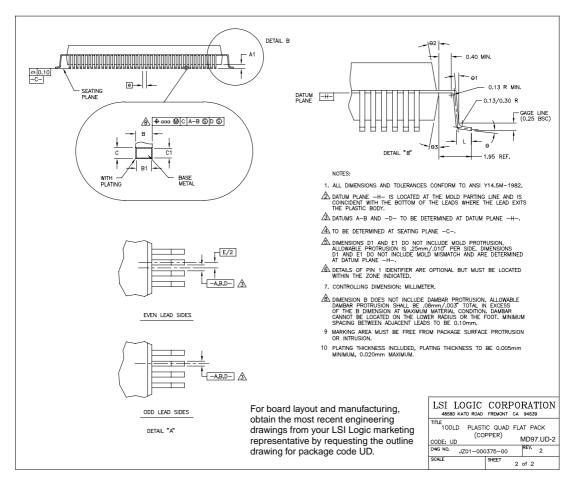

| A.1  | Serial Bus Architecture                               | A-2  |

| A.2  | 7-Bit Slave Address for the L64724 Serial Bus         | A-2  |

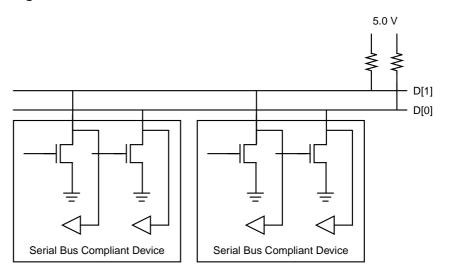

| A.3  | Serial Bus Write/Read Cycle Overview                  | A-3  |

| A.4  | General Call Structure                                | A-4  |

| A.5  | Burst Write or Single Write to Slave                  |      |

|      | (Master-Transmitter Slave-Receiver)                   | A-6  |

Contents vii

|        | A.6 | Burst Read or Single Read Cycle from Slave                      | A-8  |

|--------|-----|-----------------------------------------------------------------|------|

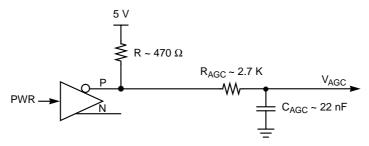

|        | B.1 | AGC Loop Control                                                | B-3  |

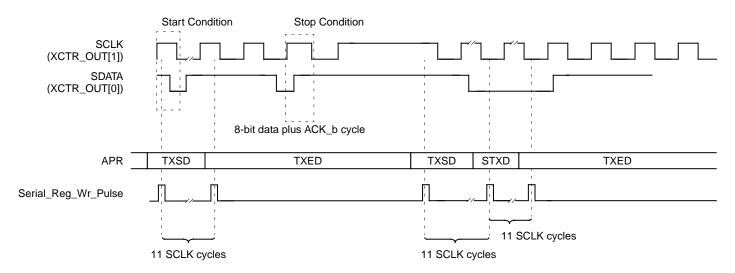

|        | C.1 | 2-Wire Compliant Interface                                      | C-5  |

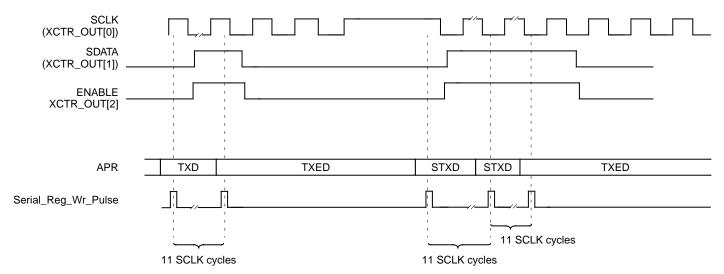

|        | C.2 | 3-Wire Interface                                                | C-7  |

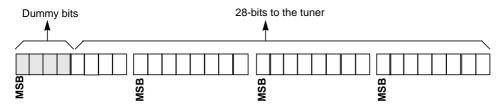

|        | C.3 | 28-Bit Write Using 3-Wire Mode                                  | C-8  |

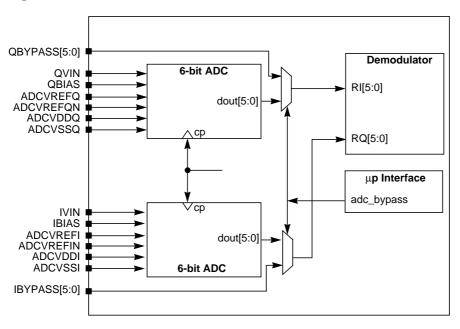

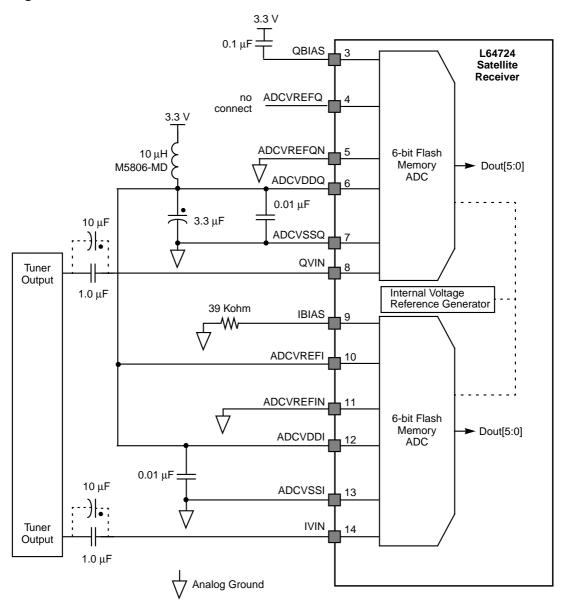

|        | D.1 | ADC Connections for L64724                                      | D-2  |

|        | D.2 | ADC Board Level Interface                                       | D-3  |

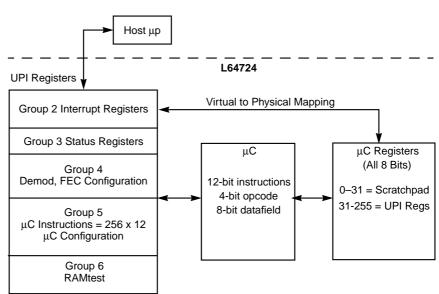

|        | E.1 | Registers Shared Between the Host uP and L64724 mC              | E-2  |

| Tables |     |                                                                 |      |

|        | 3.1 | Register Overview                                               | 3-2  |

|        | 3.2 | Group 2 System Mode Register Map (Write-Only)                   | 3-10 |

|        | 3.3 | Group 2 System Status Register Map (Read-Only)                  | 3-17 |

|        | 3.4 | Group 3 Register Map                                            | 3-23 |

|        | 3.5 | Group 4 Register Map                                            | 3-34 |

|        | 3.6 | Group 5 Register Map                                            | 3-77 |

|        | 3.7 | Reset Map                                                       | 3-83 |

|        | 4.1 | Parameters for Crystal Clock (CLK) = 15 MHz                     | 4-5  |

|        | 4.2 | Parameters for Crystal Clock (CLK) = 4 MHz                      | 4-8  |

|        | 4.3 | Input Configuration                                             | 4-13 |

|        | 4.4 | Output Selection                                                | 4-14 |

|        | 5.1 | Decimation Procedure                                            | 5-4  |

|        | 5.2 | Decimation Results                                              | 5-5  |

|        | 5.3 | Roll-Off Factor                                                 | 5-7  |

|        | 5.4 | PED Gain For Carrier Loop                                       | 5-19 |

|        | 5.5 | PWR_BW as a Function of Symbol Rate                             | 5-21 |

|        | 7.1 | Puncture Patterns for Various Code Rates                        | 7-3  |

|        | 8.1 | L64724 Absolute Maximum Rating (Referenced to V <sub>SS</sub> ) | 8-2  |

|        | 8.2 | L64724 Recommended Operating Conditions                         | 8-2  |

|        | 8.3 | L64724 Capacitance                                              | 8-2  |

|        | 8.4 | DC Characteristics of the L64724                                | 8-3  |

|        | 8.5 | L64724 Pin Description Summary                                  | 8-4  |

|        | 8.6 | L64724-75 AC Timing Parameters with Microcontroller Disabled    | 8-9  |

|        | 8.7 | L64724-75 AC Timing Parameters with Microcontroller<br>Enabled  | 8-11 |

|        | 8.8 | L64724-90 AC Timing Parameters with Microcontroller Disabled    | 8-12 |

|        | 8.9 | L64724-90 AC Timing Parameters with Microcontroller<br>Enabled  | 8-14 |

viii Contents

| 8.10 | L64724 Ordering Information                          | 8-15 |

|------|------------------------------------------------------|------|

| B.1  | PWR_LVL Register Setting                             | B-3  |

| B.2  | Decimation Procedure                                 | B-7  |

| B.3  | Decimation Results                                   | B-7  |

| B.4  | Carrier Loop Control 1 Register Bits                 | B-19 |

| B.5  | Clock Loop Configuration Register Bits               | B-22 |

| B.6  | Demodulator Configuration Register Bits              | B-23 |

| B.7  | External Output Control Bits and Reset Register Bits | B-23 |

| B.8  | High Data Rate Register Values                       | B-26 |

| B.9  | Carrier Loop Configuration Register Bits             | B-38 |

| B.10 | Clock Loop Configuration Register Bits               | B-42 |

| B.11 | Demodulator Configuration Register Bits              | B-43 |

| B.12 | External Output Control Bits and Reset Register Bits | B-43 |

| B.13 | Group 4, APR 62 Register Bits                        | B-44 |

| B.14 | Low Data Rate Register Values                        | B-45 |

| D.1  | DC Characteristics                                   | D-5  |

| D.2  | AC Characteristics                                   | D-5  |

| E.1  | L64724 mC Instruction Set                            | E-2  |

| E.2  | Microcontroller Address Map                          | E-5  |

Contents ix

# **Preface**

This manual is the primary reference and technical manual for the L64724 Satellite Receiver. It contains a complete functional description for the L64724 and includes complete physical and electrical specifications.

#### **Audience**

This document assumes that you have some familiarity with digital satellite communications, microprocessors, and related support devices. The people who benefit from this book are:

- Engineers and managers who are evaluating the L64724 for possible use in a digital satellite receiver

- Engineers who are designing the L64724 into a digital satellite receiver

# Organization

This document has the following chapters and appendices:

- Chapter 1, Introduction, defines the general characteristics and capabilities of the L64724 Satellite Receiver.

- Chapter 2, L64724 Signal Definitions, describes the characteristics

of the L64724 signals that are used to interface with an external

channel and microcontroller.

- Chapter 3, L64724 Registers, provides a summary of the registers in the L64724.

- Chapter 4, Channel Interfaces and Data Control, discusses the Input Channel and Output Channel interfaces and the circuitry that supports them.

Preface xi

- Chapter 5, Demodulator Module Functional Description, describes the operation of the Demodulator portion of the Satellite Receiver.

- Chapter 6, Decoding Pipeline Synchronization, discusses the mechanism for synchronizing the internal decoder modules to the incoming data stream.

- Chapter 7, The FEC Decoder Pipeline, describes the various logic modules that comprise the FEC decoding pipeline.

- Chapter 8, L64724 Specifications, describes the electrical and mechanical characteristics of the L64724.

- Appendix A, Programming the L64724 Using the Serial Bus Protocol, provides information on how to program the L64724 using its Serial Bus protocol.

- Appendix B, L64724 Application Notes, provides application information on connecting the L64724 in your circuit and programming it to meet your needs.

- Appendix C, Programming the Serializer, discusses the programming of the Serializer module.

- Appendix D, A/D Converters, discusses the Analog-to-Digital Converters used in the L64724 device.

- Appendix E, L64724 On-chip Microcontroller, summarizes the features of the L64724 on-chip microcontroller.

#### **Related Publications**

European Digital Video Broadcast Standard, DTVB 1110 Revision 7. This document is available from:

DVB Project Office European Broadcasting Union Ancienne Route, 17A Grand Saconnex Geneva, Switzerland

LSI Logic *L64002 MPEG-2 Audio/Video Decoder Technical Manual*, Document No. DB14-000004-00. Order No. I14011

LSI Logic *L64007 MPEG-2, DVB and TSAT Transport Demultiplexer Technical Manual,* Document No. DB14-000007-00.

#### **Conventions Used in This Manual**

The first time a word or phrase is defined in this manual, it is italicized.

The word *assert* means to drive a signal true or active. The word *deassert* means to drive a signal false or inactive.

Hexadecimal numbers are indicated by the prefix "0x" before the number—for example, 0x32CF. Binary numbers are indicated by the prefix "0b" before the number—for example, 0b0011.

Operations on registers are referred to using the binary numbers 0 and 1. Output signal levels are referred to by the designations HIGH and LOW. Example: Set the XCTR0 register bit to 1 to force the XCTR\_OUT0 pin HIGH.

Preface xiii

# Chapter 1 Introduction

This chapter introduces the L64724 Satellite Receiver from LSI Logic. The L64724 is designed specifically to meet the needs of satellite broadcast digital TV and is compliant with the European digital video broadcast (DVB-S) standard and the technical specifications for DSS systems.

The sections in this chapter are:

- Section 1.1, "General Description"

- Section 1.2, "Typical Application"

- Section 1.3, "Features Summary"

# 1.1 General Description

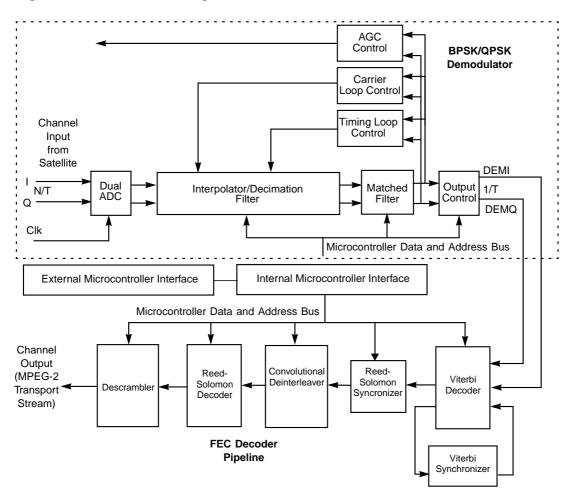

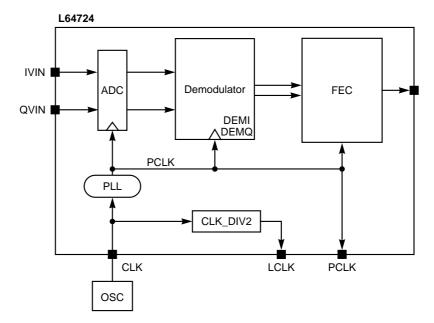

The L64724 Satellite Receiver contains two main blocks: a BPSK/QPSK Demodulator and a Concatenated FEC Decoder. The BPSK/QPSK module performs binary and quadrature phase-shift keying (BPSK/QPSK) demodulation, a method of extracting a digital signal from a phase-modulated analog signal.

The Concatenated FEC Decoder is a complete concatenated Forward Error Correction decoder that uses a Viterbi inner code and a Reed-Solomon outer code. The FEC decoding pipeline also contains all of the necessary synchronization, deinterleaving, and scrambling functions for a complete decoding solution. LSI Logic fabricates the L64724 using a 3.3-volt HCMOS process technology.

The L64724 provides maximum integration and flexibility for system designers at a minimum cost. It contains an on-chip dual 6-bit analog-to-digital converter (ADC) as well as an on-chip microcontroller. The microcontroller controls the tuner as well as acquisition and tracking,

which eliminates interaction from the main CPU, freeing up the CPU to perform other functions. The number of external components required to build a system is minimal because both clock and carrier loops are incorporated into the device. Figure 1.1 is a block diagram of the L64724.

Figure 1.1 L64724 Block Diagram

# 1.2 Typical Application

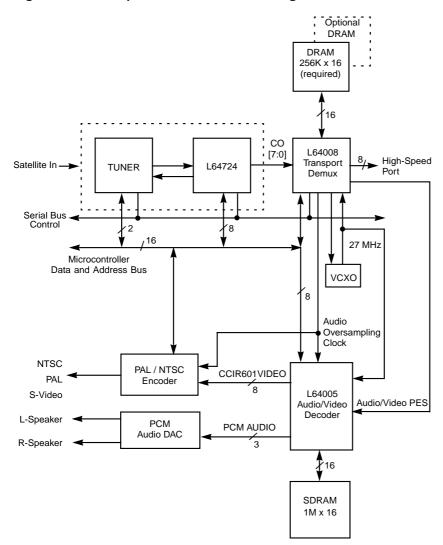

A typical application of the L64724 is satellite digital TV reception in accordance with the DVB 1110 Rev. 7 standard. Figure 1.2 shows the L64724 satellite receiver implemented in a typical satellite receiver settop decoder box. Also shown are two other LSI Logic products:

- L64008 MPEG-2 CPU Transport Demultiplexer

- L64005 MPEG-2 Audio/Video Decoder

Figure 1.2 Set-Top Decoder Box Block Diagram

# 1.3 Features Summary

This section summarizes the main features of the L64724. Subsequent chapters describe these features in more detail.

- On-chip self-tuning microcontroller acquisition and tracking, eliminating microprocessor interaction, and simplifying software development.

- Supports DVB and DSS system specifications.

- BPSK/QPSK demodulation rates from 1 to 45 Mbaud.

- Matched filter (square root raised cosine filter with roll-off factor of 20% or 35%).

- Antialiasing filters for operation from 1 to 45 MBaud without switching external SAW filters or the need for low-pass filters.

- On-chip digital clock synchronization.

- On-chip digital carrier synchronization, featuring a frequency sweep capability for signal acquisition.

- Auto-acquisition demodulator mode and tuner control through an on-chip microcontroller.

- Integrated phase-locked loop (PLL) for clock synthesis, allowing the use of a fundamental mode crystal.

- Dual ADC.

- Fast channel switching mode.

- Power estimation for AGC control.

- Programmable Viterbi decoder module for the following rates: 1/2, 2/3, 3/4, 5/6, 6/7, and 7/8.

- (204/188), (146/130) Reed-Solomon decoder.

- Auto-synchronization for the Viterbi decoder.

- Programmable synchronization for the deinterleaver, Reed-Solomon decoder, and descrambler.

- Bit error monitoring for channel performance measurements.

- Deinterleaver (DVB and DSS).

- Serial host interface compatible with the LSI Logic Serial Control bus interface.

- Power-down mode.

# Chapter 2 L64724 Signal Definitions

This chapter describes the L64724 signals and is divided into the following sections:

- Section 2.1, "Channel Interface"

- Section 2.2, "Channel Clock Interface"

- Section 2.3, "Phase-Locked Loop (PLL) Interface"

- Section 2.4, "Control Signals Interface"

- Section 2.5, "AGC/Clock Control Interface"

- Section 2.6, "Channel Data Output Interface"

- Section 2.7, "Analog-to-Digital Converter (ADC) Interface"

- Section 2.8, "Microcontroller Interface"

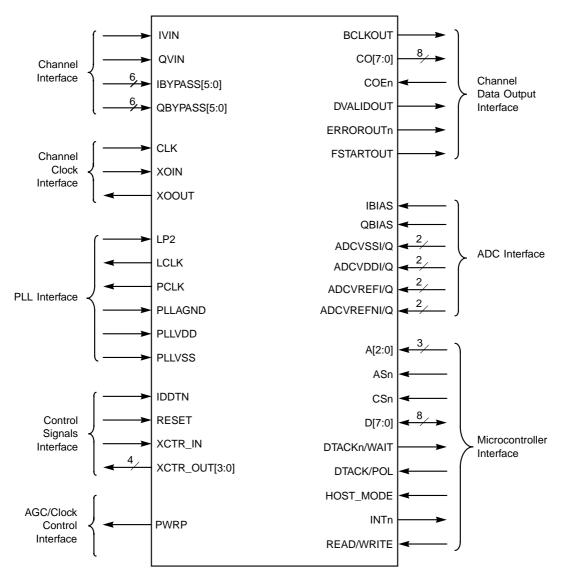

Figure 2.1 shows the logic symbol for the L64724.

Figure 2.1 L64724 Logic Symbol

- Channel

- Channel Clock

- PLL

- Control Signals

- AGC/Clock Control

- Channel Data Output

- ADC

- Microcontroller

The following signal descriptions are listed according to the major interface groups.

## 2.1 Channel Interface

The Channel interface is the input path to the L64724 satellite receiver. The two signals IVIN and QVIN are the I and Q streams from the satellite tuner circuit. The CLK signal strobes in the data signals.

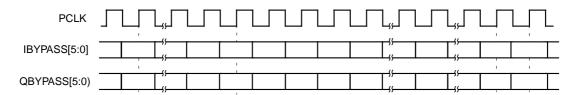

### IBYPASS[5:0] Channel Data

Input

The IBYPASS[5:0] signals form the Digital Received I Channel data input bus, which supplies the I Stream to the L64724 when the ADC is bypassed.

#### IVIN I Channel Data

Input

The IVIN signal is the Analog Received I Channel data input bus, which supplies the I Stream to the L64724.

#### QBYPASS[5:0]

#### **Q** Channel Data

Input

The QBYPASS[5:0] signals form the Digital Received Q Channel data input bus, which supplies the Q Stream to the L64724 when the ADC is bypassed.

#### QVIN Q Channel Data

Input

The QVIN signal is the Analog Received Q Channel data input bus, which supplies the Q Stream to the L64724.

Channel Interface 2-3

# 2.2 Channel Clock Interface

The Channel Clock interface consists of the clock and crystal oscillator signals.

CLK IVIN/QVIN Input Clock Input

CLK is a positive, edge-triggered clock that strobes input

data to the L64724.

XOIN Crystal Oscillator In Input

The XOIN pin is used for a crystal oscillator or external

reference clock input.

XOOUT Crystal Oscillator Out Output

The XOOUT pin is the crystal oscillator output pin.

# 2.3 Phase-Locked Loop (PLL) Interface

The PLL circuitry multiplies the external clock signal by 2, 3, or 4 times the symbol rate, based on the Viterbi code rate.

LCLK Decimated Clock Output Output

The L64724 internal clock generation module generates the LCLK signal. LCLK is derived from CLK by dividing by the value of the CLK\_DIV2 parameter (Group 4, APR

22 and 23).

LP2 Input to VCO Input

The LP2 signal is the input to the internal voltagecontrolled oscillator. It is normally connected to the output

of an external RC timing circuit.

PCLK PLL Clock Output Output

The L64724 internal PLL clock synthesis module generates the PCLK signal. The CLK signal drives the PLL. The PLL clock synthesis module can be configured to generate a PCLK rate that is appropriate for all data

rates.

PLLAGND PLL Analog Ground Input

PLLAGND is the analog ground pin for the PLL module and is normally connected to the system ground plane.

**PLLVDD PLL Power** Input

> PLLVDD is the power supply pin for the PLL module and is normally connected to the system power (V<sub>DD</sub>) plane.

**PLLVSS PLL Ground** Input

> PLLVSS is the ground pin for the PLL module and is normally connected to the system ground plane.

# 2.4 Control Signals Interface

The Control Signals Interface controls the operation of the L64724 and is not associated with any particular interface.

**IDDTN** Test Input

> The IDDTN pin is an LSI Logic internal test pin. Set the IDDTN pin LOW for normal operation.

RESET Reset Input

> RESET is an active-HIGH signal that, when asserted, resets all internal data paths. The RESET signal resets all of the Group 2 and Group 3 registers and some of the Group 5 register bits. Group 4 registers are unaffected. RESET timing is asynchronous to the device clocks. The RESET signal performs the same operation as the reset bits specified in the Group 4 APR 55 register. PCLK must be running for RESET to take effect.

XCTR IN **Control Input**  Input

The XCTR\_IN pin is an external input control pin. It is sensed by reading the XCTR\_IN bit (D6) in the Group 3, APR 6 register.

XCTR\_OUT[3] Control Output/Sync Status Flag Output

> The XCTR OUT[3] pin indicates the synchronization status for one of three synchronization modules in the L64724. The modules are the Viterbi Decoder, Reed-Solomon Deinterleaver (DI/RS), and Descrambler. For any of the three synchronization outputs, the XCTR\_OUT[3] signal, when asserted, indicates that synchronization has been achieved for the sync module chosen using the SSS[1:0] bits (Group 4, APR16). When deasserted, the signal indicates an out-of-synchronization condition.

#### XCTR\_OUT[2:0]

#### **Control Output**

Output

The XCTR\_OUT[2:0] pins are external output control pins. They are set by programming the corresponding bits in the Group 4, APR 55 register. XCTR\_OUT[1] can function as the Serial Clock (SCLK) signal, and XCTR\_OUT[0] can function as the Serial Data (SDATA) signal.

# 2.5 AGC/Clock Control Interface

#### PWRP Power Control

Output

The PWRP signal is the positive modulated output used for power control and can drive an external passive RC filter that feeds the tuner gain control stage.

# 2.6 Channel Data Output Interface

The Channel Data Output Interface is the output path from the L64724. It is typically connected to the input of the transport demultiplexer in a set-top decoder application.

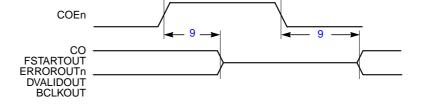

# **BCLKOUT** Byte Clock Out

Output

The BCLKOUT output signal is a strobe that indicates valid data bytes on the CO[7:0] bus when the L64724 is in Parallel Channel Output mode. The BCLKOUT signal cycles once every valid output data byte and is used by the transport demultiplexer to latch output data from the L64724 at the BCLKOUT rate. The BCLKOUT signal must be disregarded in Serial Channel Output mode.

## CO[7:0] Channel Data Out

Outpu

The CO[7:0] signals form the decoded output data port. When the OF bit is 1 (Group 4, APR17), the L64724 operates in the Parallel Channel Output mode. In this mode, the L64724 outputs the channel data as 8-bit wide parallel data on the CO[7:0] signals. In Serial Channel Output mode (OF = 0) the L64724 outputs the channel data as serial data on CO[0]. The data is latched on every bit clock cycle. The chronological ordering in Serial Channel output mode is MSB oldest, LSB newest.

#### COEn Channel Output Enable

Input

When asserted, the COEn signal enables the ERROROUTn, CO[7:0], DVALIDOUT, BCLKOUT, and FSTARTOUT pins. Operation of the receiver continues regardless of the state of the COEn signal.

#### **DVALIDOUT** Valid Data Out

Output

The DVALIDOUT signal indicates that the CO[7:0] signals contain the corrected channel data. New data is valid on the CO[7:0] signals when the DVALIDOUT signal is asserted. DVALIDOUT is not asserted during the propagated check and GAP bytes. The DVALIDOUT signal is deasserted after the FEC\_RST register bit (Group 4, APR 55) is set to a 1.

#### **ERROROUTn Error Detection Flag**

Output

The L64724 asserts the ERROROUTn pin (LOW) to flag uncorrectable errors. The L64724 asserts the ERROROUTn signal at the beginning of any frame that contains an uncorrectable error, and deasserts it at the end of the frame if the error condition is removed. The ERROROUTn signal is exactly aligned with the output data stream and is asserted after the FEC\_RST register bit (Group 4, APR 55) is set to a 1. The Errorout\_Invert bit (Group 4, APR 31), when set to 1, changes the active state of the ERROROUTn signal from active-LOW to active-HIGH.

#### **FSTARTOUT** Frame Start Output

Output

The L64724 asserts the FSTARTOUT signal during the first bit of every frame with valid data in Serial Channel Output mode and during the first byte in Parallel Channel Output mode. FSTARTOUT is valid only when the DVALIDOUT signal is asserted. The FSTARTOUT signal is deasserted after the FEC\_RST register bit (Group 4, APR 55) is set to a 1.

# 2.7 Analog-to-Digital Converter (ADC) Interface

The ADC module converts the incoming IVIN and QVIN signals into an internal 6-bit digital representation for processing. The following pins support the ADC module.

ADCVDDI/Q ADC Power Input

ADCVDDI/Q are the analog power supply pins for the ADC module and are normally connected to the system

power (V<sub>DD</sub>) plane.

ADCVREFI ADC I Reference Input

This pin supplies VDD to the internal reference generator.

ADCVREFNI ADC Negative I Reference Input

This pin supplies VREFN to the internal ADC cells.

ADCVREFQ ADC Q Reference Input

This pin is not used and should be left unconnected. Any other connection will cause unpredictable and unreliable

operation of the device.

ADCREFNQ ADC Negative Q Reference Input

This pin supplies the ground to the internal ADC cell.

ADCVSSI/Q ADC Analog Ground Input

ADCVSSI/Q are the analog ground pins for the ADC module and are normally connected to the system

ground plane.

IBIAS Current Bias I Input

The IBIAS pin supplies the current bias for the ADCs.

QBIAS Current Bias Q Input

This pin is used by LSI Logic for internal purposes, and should be connected as shown in Figure D.2. Any other connection will cause unpredictable and unreliable

operation of the device.

# 2.8 Microcontroller Interface

The Microcontroller Interface connects the L64724 to a microcontroller such as the 64008.

A[2:0] Address Input

The A[2:0] signals form the receiver address bus. The address bus is used in conjunction with an 8-bit data bus D[7:0], a read/write strobe (READ/WRITE), a chip select strobe (CS), and an address strobe (AS) to select, read, and write internal registers.

#### ASn Address Strobe

Address Strobe Input

The ASn signal is an active-LOW address strobe input.

The L64724 letches the address on the ASS signals on

The L64724 latches the address on the A[2:0] signals on the falling edge of the ASn signal.

#### CSn Chip Select

Input

The CSn signal is an active-LOW chip select strobe input. During a read cycle, the microcontroller must assert CSn (LOW) to access the on-chip data registers. The microcontroller must latch the data from the L64724 on the rising edge of CSn. During a write cycle, CSn must be asserted prior to data being valid from the microcontroller to the L64724. After the data has met the minimum setup time, the microcontroller deasserts CSn (HIGH) to strobe the data. There is a minimum write time to allow for internal synchronization. Setup and hold times are measured with respect to the falling edge of CSn.

#### D[7:0] Data

**Bidirectional**

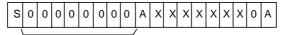

The D[7:0] signals form the bidirectional data bus, which is an input data bus when data is written to the L64724 chip and a data output bus when the L64724 chip is read in Parallel Host Interface mode<sup>1</sup> (HOST\_MODE pin HIGH). The data lines are 3-stated when not being read or written. When Serial Host Interface mode is selected (HOST\_MODE pin LOW), D[0] is used as the Serial Clock (SCLK) signal to synchronize the transfer of serial data on the Serial Data (SDATA) pin. In Serial Host interface mode, XCTR\_OUT[1] functions as SDATA, D[1] is used as the SDATA signal to transfer serial data, and D[3:2] are used as the two LSBs of the L64724 slave address.

#### DTACK/POL

#### Data Acknowledge/Wait Polarity

Input

The DTACK/POL signal determines the polarity of the Data Acknowledge/Wait Signal. When the DTACK/POL signal is LOW, DTACKn/WAIT is active-LOW. When the DTACK/POL signal is HIGH, the DTACKn/WAIT signal is active-HIGH.

Serial Mode is the recommended interface mode. LSI Logic does not recommend parallel mode for new designs.

#### DTACKn/WAIT

#### Data Acknowledge/Wait

**Output**

The DTACKn/WAIT signal is an output indicating that the transaction on the D[7:0] bus has been completed. It is active-LOW when DTACK/POL is LOW and active-HIGH when DTACK/POL is HIGH. Do not base the chip programming on this signal.

**HOST MODE** Serial or Parallel Host Interface Select

Input

When the HOST MODE signal is deasserted, it selects the Serial Host Interface mode. When it is asserted, it selects the Parallel Host Interface mode<sup>1</sup>.

#### **INT**n Interrupt

Output

The L64724 asserts the INTn signal (LOW) when an internal unmasked interrupt flag is set. The INTn signal remains asserted as long as the interrupt condition persists and the interrupt flag is not masked.

#### READ/WRITE Read/Write Strobe

Input

The microcontroller asserts the READ/WRITE signal (HIGH) to indicate that the current transaction is a read from the L64724, and deasserts it (LOW) to indicate that it is a write to the L64724.

<sup>1.</sup> Serial Mode is the recommended interface mode. LSI Logic does not recommend parallel mode for new designs.

# Chapter 3 L64724 Registers

This chapter discusses the L64724 internal registers. It also provides a description of the internal memory mapping and describes how to access the registers from the system interface. This chapter is intended primarily for system programmers who are developing software drivers and contains the following sections:

- Section 3.1, "L64724 Register Overview"

- Section 3.2, "Reset and How it Affects Registers"

- Section 3.3, "Groups 0 and 1: Address Pointer Register"

- Section 3.4, "Group 2: System Mode and System Status Registers"

- Section 3.5, "Group 3: Status Registers"

- Section 3.6, "Group 4: Configuration Registers"

- Section 3.7, "Group 5: Self-Tuning Microcontroller Registers"

- Section 3.8, "Group 6: Reserved (Internal Use Only)"

- Section 3.9, "Group 7: Arbiter Control Register"

- Section 3.10, "Reset Effect on Register Bits"

- Section 3.11, "Internal Data Path Reset Effects"

This chapter provides complete information on how to use these registers, but does not provide information on how to program the registers for a specific application. See Appendix B, "L64724 Application Notes," for some programming examples.

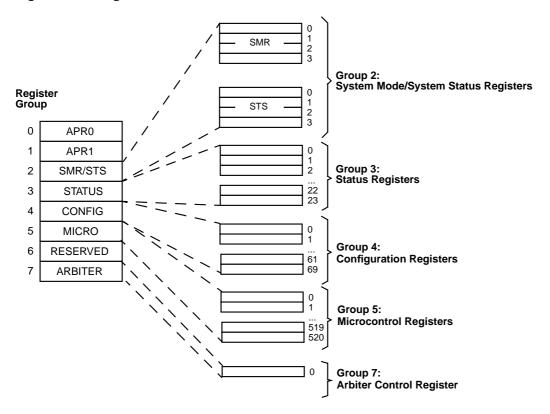

# 3.1 L64724 Register Overview

The L64724 registers and memory resources are divided into eight groups, Group 0 through Group 7.

- Groups 0 and 1 contain the Address Pointer Register. This pointer is used to address the registers in Groups 2, 3, and 4.

- Group 2 addresses the System Mode Register when written and the System Status Register when read.

- Group 3 contains the Status Registers.

- Group 4 contains the Configuration Registers.

- Group 5 contains the program space for the on-board microprocessor.

- Group 6 is reserved for internal use only.

- Group 7 is used for Arbiter control.

Table 3.1 shows the complete Register Map for the L64724 Satellite Receiver.

Table 3.1 Register Overview

| Group | Name     | Function                            | Page |

|-------|----------|-------------------------------------|------|

| 0     | APR0     | Address Pointer Register, LSB       | 3-8  |

| 1     | APR1     | Address Pointer Register, MSB       | 3-8  |

| 2     | SMR/STS  | System Mode/System Status Registers | 3-9  |

| 3     | STATUS   | Status Registers                    | 3-23 |

| 4     | CONFIG   | Configuration Registers             | 3-33 |

| 5     | MICRO    | Microcontrol Registers              | 3-77 |

| 6     | RESERVED | Reserved                            | 3-81 |

| 7     | ARBITER  | Arbiter Control Register            | 3-81 |

Figure 3.1 shows a simplified diagram of the L64724 register groups.

Figure 3.1 Register File Structure

To reduce the number of memory locations occupied by the L64724 in microprocessor memory, the L64724 uses a pair of Address Pointer Registers (APR0 and APR1). The Address Pointer Registers have an auto-increment feature that simplifies the initialization procedure and reduces the number of memory cycles needed to read or write the registers. The address pointer and auto-increment features are used whenever you access Groups 2, 3, and 4. The L64724 automatically points to the next register entry after you complete an access to one of the three groups. When writing or reading register groups 3 and 4, it is easier to initially set APR0 and APR1 to zero and let the auto-increment mechanism step through all the locations within the group.

For example, to access the PLL\_N configuration register 0 (Group 4, APR 0), first set APR0 and APR1 to 0x00 by writing a zero to addresses 0 and 1, then set A[2:0] to 0b100. The value of 0b100 for address A[2:0] selects Group 4.

The L64724 has an internal 8-bit architecture. Most registers are 8 bits wide, while some are either 16 or 24 bits wide. All registers are memory-mapped to the system with 8-bit resolution. When you are accessing a register that is wider than 8 bits, you must read or write two or three 8-bit sections. The sections are divided into the least-significant byte (LSB), the middle-significant byte (MB), and the most-significant byte (MSB). Each 8-bit section is assigned a specific address, and requires an individual memory cycle during programming.

# 3.1.1 Parallel Host Interface Mode<sup>1</sup>

The L64724 is addressable through either a serial or a parallel host interface. The interface used depends on the state of the HOST\_MODE input pin when the L64724 is reset. The interface is selected as follows:

- HOST MODE pin HIGH = Parallel Host Interface mode

- HOST\_MODE pin LOW = Serial Host Interface mode

The interface mode cannot be changed once the part is in operation. The following paragraphs show the steps required to read and write the L64724 registers when you are in Parallel Host Interface mode. Serial Host Interface mode is discussed in Section 3.1.2, "Serial Host Interface Mode," page 3-6, and Appendix A, "Programming the L64724 Using the Serial Bus Protocol,".

Figure 3.2 through Figure 3.5 demonstrate read and write operation through the parallel microprocessor interface.

Note: The PCLK signal must operate for the user to be able to access Groups 2 and 3. Group 4, however, can be programmed in the absence of PCLK.

To read and write registers using the parallel interface mode, follow these steps:

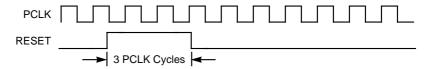

Issue a hard reset to the L64724 for three clock cycles, as shown in Figure 3.2. Wait for the wake-up time (t<sub>WK</sub>), which is 280 PCLK cycles, before continuing.

Serial Mode is the recommended interface mode. LSI Logic does not recommend parallel mode for new designs.

Figure 3.2 Issue a Hard Reset

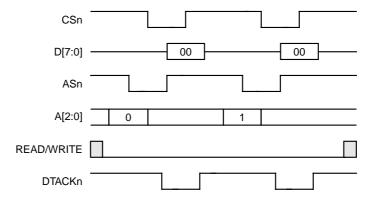

2. Set the APR0 and APR1 registers to zero by writing a zero to Groups 0 and 1. See Figure 3.3.

Figure 3.3 Initialize APR0 and APR1 to Zero

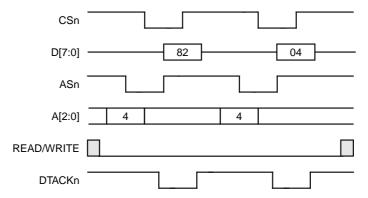

3. Write to the Configuration registers in Group 4.

Because the APRs were both initialized to zero, the first location written in Group 4 is location zero, the second location written is 1, and so on. As long as the address lines A[2:0] contain the value 4, the auto-increment mechanism advances to the next location in Group 4 with every low-to-high transition of CSn.

Figure 3.4 and Figure 3.5 show the first two writes to Group 4. The 0x82 and 0x04 values shown for D[7:0] are typical values for locations 0 and 1, respectively. See Section 3.6, "Group 4: Configuration Registers," page 3-33, for more details on the data values.

Figure 3.4 Write Locations 0 and 1 in Group 4

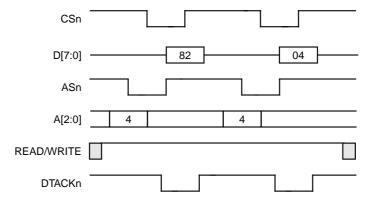

4. You can also choose to read back the Group 4 Configuration registers, as demonstrated in Figure 3.5. Just set APR0 and APR1 to zero (see Figure 3.3) and step through the configuration locations using a value of 4 for A[2:0]. The READ/WRITE signal is asserted, and the auto-increment mechanism selects location 0, then location 1, and so on.

Figure 3.5 Read Back Group 4

#### 3.1.2 Serial Host Interface Mode

Setting the HOST\_MODE pin LOW during reset places the L64724 in Serial Host Interface mode. When the L64724 is addressed using the serial interface, it must first be programmed with a 2-bit slave address before any other read or write cycles. Appendix A, "Programming the L64724 Using the Serial Bus Protocol," contains a detailed description of the protocol used when programming the L64724 in Serial Host Interface mode.

# 3.2 Reset and How it Affects Registers

There are three separate resets available on the L64724, as follows:

- The hardware RESET pin

- The DEMOD\_RST register bit (Group 4, APR 55, bit 1)

- The FEC RST register bit (Group 4, APR 55, bit 0).

Each reset affects the registers differently, as follows:

- Toggling the hardware RESET pin resets all of the Group 2 and Group 3 registers and some of the Group 4 registers. Registers in Group 4 are unaffected.

- Setting the DEMOD\_RST bit in the External Output Control bits and Reset Register (Group 4, APR 55, bit 1) affects only the bits in Group 3 registers that are directly concerned with the demodulator circuitry.

- Setting the FEC\_RST bit in the External Output Control bits and Reset Register (Group 4, APR 55, bit 0) resets the System Mode/Status registers (Group 2) and any bits in Group 3 registers that are directly concerned with the FEC circuitry.

Registers in Group 4 are unaffected by any of the reset operations. The contents of the Group 4 registers are random immediately after power-up, and retain their last known value after any of the three reset operations listed above.

The following steps should be followed when resetting the L64724:

- Issue an active-HIGH reset pulse to the RESET pin. The reset pulse width must be in accordance with the parameter t<sub>RWH</sub> (see Figure 8.4).

- 2. Program the Configuration (Group 4) registers to their proper values.

- 3. Issue a soft reset by setting the DEMOD\_RST bit and the FEC\_RST bits to a 1 (Group 4, APR 55). The bits are self-resetting, and do not have to be cleared.

- 4. After the RESET pin has been deasserted (LOW), wait the wake-up time amount specified by the parameter t<sub>WK</sub> (see Figure 8.4).

5. The L64724 is now in the acquisition mode. When data is applied at the L64724 input, it is ready to start demodulating and decoding.

For details on how reset affects the various register bits, see Section 3.10, "Reset Effect on Register Bits," page 3-82.

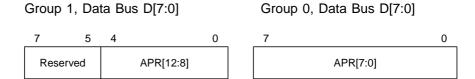

# 3.3 Groups 0 and 1: Address Pointer Register

The Address Pointer Register (APR) is a 13-bit R/W register that points to the registers in Groups 2, 3, and 4. It is accessed when A[2:0] = 0b000 and 0b001. Before accessing a register location from Group 2, 3, or 4, you must initialize the APR contents with the address of the first register entry that you are going to read or write. The APR automatically increments after reading or writing a byte within a Group 2 (A[2:0] = 0b010), Group 3 (A[2:0] = 0b011) Group 4 (A[2:0] = 0b100) or Group 5 (A[2:0] = 0b101) register.

Two consecutive writes are required to load the complete APR. The first write is to Group 0 to load the eight LSBs, the second to Group 1 to load the five MSBs. The APR can be read as well as written.

The reserved bits in these registers are for LSI internal test procedures and future expansion and should always be set to zero.

To access a Group 2, 3, or 4 register:

- Initialize the APR with the address of the first register you want to access within a particular register group. You should write both bytes of the APR.

- Read or write the first register within the register group you are accessing using the appropriate register group address. The addresses are:

Group 2-0b010

Group 3—0b011

Group 4—0b100

Group 5—0b101

If the register is a 16-bit register, just perform another read or write to the group register address to access the second byte. The APR increments automatically.

When you are through, the APR automatically points to the next register in the group.

# 3.4 Group 2: System Mode and System Status Registers

Group 2 contains two 32-bit registers, the System Mode Register (SMR) and the System Status Register (STS). The System Mode Register is accessed by writing the Group 2 address, and the System Status Register is accessed by reading the Group 2 address. Because the L64724 has an 8-bit architecture, each 32-bit register is accessed as four 8-bit registers.

The microprocessor accesses these registers by setting A[2:0] = 0b010. It can access these registers at any point during Satellite Receiver operation without interrupting the internal processing unit.

Note: The phase-locked loop must be locked (PCLK running) for the status signals to be valid.

# 3.4.1 System Mode Register (SMR)

The 32-bit System Mode Register (SMR) is a write-only register that allows the external microprocessor to control the L64724. Table 3.2 shows the SMR map.

Table 3.2 Group 2 System Mode Register Map (Write-Only)

| APR | D7                              | D6             | D5       | D4            | D3      | D2       | D1              | D0              |

|-----|---------------------------------|----------------|----------|---------------|---------|----------|-----------------|-----------------|

| 0   |                                 | SMR[7:0]       |          |               |         |          |                 |                 |

|     | VBER_IE                         | S3_LS_IE       | S3_S_IE  | S2_LS_IE      | S2_S_IE | S1_LS_IE | S1_S_IE         | Reserved        |

| 1   | SMR[15:8]                       |                |          |               |         |          |                 |                 |

|     | CLK_LK_<br>IE                   | CLK_LLK_<br>IE | CP_LK_IE | CP_LLK_<br>IE | Reserv  | /ed = 0  | CL_FS_LL_<br>IE | CL_FS_UL_<br>IE |

| 2   |                                 | SMR[23:16]     |          |               |         |          |                 |                 |

|     | Reserved TL_FS_LL_ IE TL_FS_UL_ |                |          |               |         |          |                 |                 |

| 3   | SMR[31:24]                      |                |          |               |         |          |                 |                 |

|     | uC_IE7                          | uC_IE6         | uC_IE5   | uC_IE4        | uC_IE3  | uC_IE2   | uC_IE1          | uC_IE0          |

The bits in the register are allocated as follows:

- SMR[7:0] enable FEC module interrupts.

- SMR[23:8] enable the Demodulator interrupts.

- SMR[31:24] enable interrupts for the on-chip microcontroller.

Because the SMR is arranged as four 8-bit registers, the microprocessor must perform four consecutive writes to the register address. The lower eight bits of the APR must be set to 0x00 in order to access bits SMR[7:0]. The eight LSBs of the SMR are accessed first. The auto-increment mechanism toggles the Address Pointer Register after the first access so that the next write goes to the SMR[15:8] bits.

If you want to access the SMR starting with bytes 1, 2, or 3, set the APR equal to 0b01, 0b10, or 0b11, respectively.

The following register diagram shows the bit organization of SMR[7:0]. Descriptions of the bits follow the register diagram. The L64724 clears all bits in the SMR to zero after a software or hardware reset.

| APR | D7      | D6       | D5      | D4       | D3      | D2       | D1      | D0       |

|-----|---------|----------|---------|----------|---------|----------|---------|----------|

| 0   |         |          |         | SMR[     | 7:0]    |          |         |          |

| U   | VBER_IE | S3_LS_IE | S3_S_IE | S2_LS_IE | S2_S_IE | S1_LS_IE | S1_S_IE | Reserved |

#### VBER\_IE Viterbi Bit Error Rate Monitor Interrupt Enable

The microprocessor sets the VBER\_IE bit to enable an interrupt when the Viterbi decoder reaches the period specified by VMDC2 (the period over which the Viterbi bit errors are counted). The L64724 always sets the VBER bit in the STS register when this condition occurs.

| VBER_IE |   | Definition                              |

|---------|---|-----------------------------------------|

|         | 0 | Disable Interrupt for Viterbi BER count |

|         | 1 | Enable Interrupt for Viterbi BER count  |

# S3\_LS\_IE Stage 3 Loss of Synchronization Interrupt Enable 6

The microprocessor sets the S3\_LS\_IE bit to enable an interrupt when Descrambler synchronization is lost. S3 LS IE is not used in DSS mode.

| S3_LS_IE | Definition                                            |

|----------|-------------------------------------------------------|

| 0        | Disable Interrupt for Stage 3 Loss of Synchronization |

| 1        | Enable Interrupt for Stage 3 Loss of Synchronization  |

## S3 S IE Stage 3 Synchronization Interrupt Enable

The microprocessor sets the S3\_S\_IE bit to enable an interrupt when Descrambler synchronization is established. S3\_S\_IE is not used in DSS mode.

| S3_S_IE | Definition                                    |

|---------|-----------------------------------------------|

| 0       | Disable Interrupt for Stage 3 Synchronization |

| 1       | Enable Interrupt for Stage 3 Synchronization  |

5

#### S2 LS IE Stage 2 Loss of Synchronization Interrupt Enable 4

The microprocessor sets the S2 LS IE bit to enable an interrupt when Deinterleaver/Reed-Solomon Decoder synchronization is lost.

| S2_LS_IE | Definition                                            |

|----------|-------------------------------------------------------|

| 0        | Disable Interrupt for Stage 2 Loss of Synchronization |

| 1        | Enable Interrupt for Stage 2 Loss of Synchronization  |

#### S2 S IE Stage 2 Synchronization Interrupt Enable

The microprocessor sets the S2\_S\_IE bit to enable an interrupt when Deinterleaver/Reed-Solomon Decoder synchronization is established.

| S2_S_IE | Definition                                |

|---------|-------------------------------------------|

| 0       | Disable Stage 2 Synchronization Interrupt |

| 1       | Enable Stage 2 Synchronization Interrupt  |

#### S1 LS IE Stage 1 Loss of Synchronization Interrupt Enable 2

The microprocessor sets the S1 LS IE bit to enable an interrupt when Viterbi Decoder synchronization is lost.

| S1_LS_IE | Definition                                          |

|----------|-----------------------------------------------------|

| 0        | Disable Stage 1 Loss of Synchronization Interrupt   |

| 1        | Enable Stage 1 Loss of Synchronization<br>Interrupt |

#### S1\_S\_IE Stage 1 Synchronization Interrupt Enable

The microprocessor sets S1 S IE to enable an interrupt when Viterbi Decoder synchronization is established.

| S1_S_IE | Definition                                |

|---------|-------------------------------------------|

| 0       | Disable Stage 1 Synchronization Interrupt |

| 1       | Enable Stage 1 Synchronization Interrupt  |

#### Reserved Reserved

The Reserved bit is for LSI Logic internal use only and should always be cleared to 0.

The following register diagram shows the bit organization of SMR[15:8]. Descriptions of the bits follow the register diagram. The L64724 sets all the bits in SMR[15:8] to 0 after a software or a hardware reset.

| APR | D7        | D6         | D5       | D4        | D3       | D2    | D1          | D0          |

|-----|-----------|------------|----------|-----------|----------|-------|-------------|-------------|

| 4   |           |            |          | SMR[      | 15:8]    |       |             |             |

| 1   | CLK_LK_IE | CLK_LLK_IE | CP_LK_IE | CP_LLK_IE | Reserved | I = 0 | CL_FS_LL_IE | CL_FS_UL_IE |

#### CLK LK IE **Timing Lock Detect Interrupt Enable**

15 The microcontroller sets the CLK LK IE bit to enable an interrupt when timing lock is detected. The L64724 always sets the CLK LK bit in the STS register when this condition occurs.

| CLK_LK_IE | Definition                               |

|-----------|------------------------------------------|

| 0         | Disable Interrupt for Timing Lock Detect |

| 1         | Enable Interrupt for Timing Lock Detect  |

#### CLK\_LLK\_IE Timing Lock Lost Detect Interrupt Enable

The microcontroller sets the CLK LLK IE bit to enable an interrupt when timing lock loss is detected. The L64724 always sets the CLK\_LLK bit in the STS register when this condition occurs.

| CLK_LLK_IE | Definition                                    |

|------------|-----------------------------------------------|

| 0          | Disable Interrupt for Timing Lock Lost Detect |

| 1          | Enable Interrupt for Timing Lock Lost Detect  |

#### CP LK IE **Carrier Phase Lock Detect Interrupt Enable**

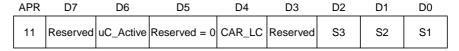

The microprocessor sets the CP\_LK\_IE bit to enable an interrupt when Carrier Phase Lock is detected (CAR LC = 1 in Group 3, APR11). The L64724 always sets the CP LK bit in the STS register when this condition occurs.

| CP_LK_IE | Definition                                      |

|----------|-------------------------------------------------|

| 0        | Disable Interrupt for Carrier Phase Lock Detect |

| 1        | Enable Interrupt for Carrier Phase Lock Detect  |

#### CP LLK IE **Carrier Phase Lock Lost Detect Interrupt Enable**

The microprocessor sets the CP\_LLK\_IE bit to enable an interrupt when Carrier Phase Lock Loss is detected

14

13

(CAR\_LC = 0 in Group 3, APR11). The L64724 always sets the CP\_LLK bit in the STS register when this condition occurs.

| CP_LLK_IE | Definition                                              |

|-----------|---------------------------------------------------------|

| 0         | Disable Interrupt for Carrier Phase Lock<br>Loss Detect |

| 1         | Enable Interrupt for Carrier Phase Lock Loss Detect     |

#### Reserved

#### Reserved

[11:10]

The Reserved bits are for LSI Logic internal use only and must always be cleared to 0.

#### CL\_FS\_LL\_IE

# Frequency Sweep Lower Limit Reached Interrupt Enable

9

The microprocessor sets the CL\_FS\_LL\_IE bit to enable an interrupt when the Carrier Loop Frequency Sweep has reached its lower limit. The L64724 always sets the CL\_FS\_LL bit in the STS register when this condition occurs.

| CL_FS_LL_IE | Definition                                                       |

|-------------|------------------------------------------------------------------|

| 0           | Disable Interrupt for Frequency Sweep Lower Limit Reached Detect |

| 1           | Enable Interrupt for Frequency Sweep Lower Limit Reached Detect  |

#### CL\_FS\_UL\_IE

# Frequency Sweep Upper Limit Reached Interrupt Enable

8

The microprocessor sets the CL\_FS\_UL\_IE bit to enable an interrupt when the Carrier Loop Frequency Sweep has reached its upper limit. The L64724 always sets the CL\_FS\_UL bit in the STS register when this condition occurs.

| CL_FS_UL_IE | Definition                                                      |

|-------------|-----------------------------------------------------------------|

| 0           | Disable Interrupt for Frequency Sweep Upper Limit Reached       |

| 1           | Enable Interrupt for Frequency Sweep Upper Limit Reached Detect |

The following register diagram shows the bit organization of SMR[23:16]. Descriptions of the fields follow the register diagram. The L64724 sets all the bits in SMR[23:16] to 0 after a software or a hardware reset.

| _ | APR | D7 | D6 | D5    | D4  | D3        | D2 | D1          | D0          |

|---|-----|----|----|-------|-----|-----------|----|-------------|-------------|

|   |     |    |    |       | SM  | IR[23:16] |    |             |             |

|   | 2   |    |    | Reser | ved |           |    | TL_FS_LL_IE | TL_FS_UL_IE |

#### Reserved Reserved

[23:18]

The Reserved bits are for LSI Logic internal use only and must always be cleared to 0.

# TL\_FS\_LL\_IE Frequency Sweep Lower Limit Reached Interrupt Enable

17

The microprocessor sets the TL\_FS\_LL\_IE bit to enable an interrupt when the Timing Loop Frequency Sweep has reached its lower limit. The L64724 always sets the TL\_FS\_LL bit in the STS register when this condition occurs.

#### TL FS LL IE Definition

| 0 | Disable Interrupt for Frequency Sweep Lower Limit Reached Detect |

|---|------------------------------------------------------------------|

| 1 | Enable Interrupt for Frequency Sweep Lower Limit Reached Detect  |

# TL\_FS\_UL\_IE Frequency Sweep Upper Limit Reached Interrupt Enable 16

The microprocessor sets the TL\_FS\_UL\_IE bit to enable an interrupt when the Frequency Sweep has reached its upper limit. The L64724 always sets the TL\_FS\_UL bit in the STS register when this condition occurs.

#### TL\_FS\_UL\_IE Definition

| 0 | Disable Interrupt for Frequency Sweep<br>Upper Limit Reached       |

|---|--------------------------------------------------------------------|

| 1 | Enable Interrupt for Frequency Sweep<br>Upper Limit Reached Detect |

The following register diagram shows the bit organization of SMR[31:24]. Descriptions of the bits follow the register diagram. The L64724 clears all the bits in SMR[31:24] to 0 after a software or a hardware reset.

| APR | D7         | D6     | D5     | D4     | D3     | D2     | D1     | D0     |  |

|-----|------------|--------|--------|--------|--------|--------|--------|--------|--|

| 3   | SMR[31:24] |        |        |        |        |        |        |        |  |

| 3   | uC_IE7     | uC_IE6 | uC_IE5 | uC_IE4 | uC_IE3 | uC_IE2 | uC_IE1 | uC_IE0 |  |

#### uC IE7 uC Interrupt 7 Enable

31

The microprocessor sets the uC\_IE7 bit to enable interrupt 7 from the on-chip microcontroller. The microcode can define the meaning of interrupt 7; therefore this is a user-programmable interrupt.

#### uC\_IE6 uC Interrupt 6 Enable

30

The microprocessor sets the uC\_IE6 bit to enable interrupt 6 from the on-chip microcontroller. The microcode can define the meaning of interrupt 6; therefore, this is a user-programmable interrupt.

#### uC IE5 uC Interrupt 5 Enable

29

The microprocessor sets the uC\_IE5 bit to enable interrupt 5 from the on-chip microcontroller. The microcode can define the meaning of interrupt 5; therefore, this is a user-programmable interrupt.

# uC\_IE4 uC Interrupt 4 Enable

28

The microprocessor sets the uC\_IE4 bit to enable interrupt 4 from the on-chip microcontroller. The microcode can define the meaning of interrupt 4; therefore, this is a user-programmable interrupt.

# uC\_IE3 uC Interrupt 3 Enable

27

The microprocessor sets the uC\_IE3 bit to enable interrupt 3 from the on-chip microcontroller. The microcode can define the meaning of interrupt 3; therefore, this is a user-programmable interrupt.

#### uC\_IE2 uC Interrupt 2 Enable

26

The microprocessor sets the uC\_IE2 bit to enable interrupt 2 from the on-chip microcontroller. The microcode can define the meaning of interrupt 2; therefore, this is a user-programmable interrupt.

#### uC\_IE1 uC Interrupt 1 Enable

The microprocessor sets the uC\_IE1 bit to enable interrupt 1 from the on-chip microcontroller. The microcode can define the meaning of interrupt 1; therefore, this is a user-programmable interrupt.

#### uC\_IE0 uC Interrupt 0 Enable

24

25

The microprocessor sets the uC\_IE0 bit to enable interrupt 0 from the on-chip microcontroller. The microcode can define the meaning of interrupt 0; therefore, this is a user-programmable interrupt.

# 3.4.2 System Status Register (STS)

The STS Register is a read-only register that provides the external microprocessor access to L64724 status information. Table 3.3 shows the STS map.

Table 3.3 Group 2 System Status Register Map (Read-Only)

| APR | D7         | D6      | D5    | D4              | D3              | D2    | D1       | D0       |

|-----|------------|---------|-------|-----------------|-----------------|-------|----------|----------|

| 0   |            |         |       |                 | STS[7:0]        |       |          |          |

|     | VBER       | S3_LS   | S3_S  | S2_LS           | S2_S            | S1_LS | S1_S     | Reserved |

| 1   |            |         |       | S               | TS[15:8]        |       |          |          |

| '   | CLK_LK     | CLK_LLK | CP_LK | CP_LLK          | Set to 0        |       | CL_FS_LL | CL_FS_UL |

|     | STS[23:16] |         |       |                 |                 |       |          |          |

| 2   |            |         |       | TL_CL_FS_<br>LL | TL_CL_FS_<br>UL |       |          |          |

| 3   |            |         |       | S               | TS[31:24]       |       |          |          |

|     | uC_I7      | uC_l6   | uC_I5 | uC_I4           | uC_l3           | uC_l2 | uC_I1    | uC_I0    |

The STS register bits indicate the event that generated an internal interrupt condition. The interrupt status bits are set regardless of the enable interrupt bits in the SMR Register. The internal status is updated every L64724 CLK. When the microprocessor reads the status, the current information is buffered in a special-purpose 32-bit STS buffer that locks the STS value until the end of the microprocessor read operation.

Four consecutive read operations must be done to the same Group 2 address (A[2:0] = 0b010) to access all four bytes of the status registers.

The STS register bits are cleared to 0 after a hardware reset. They are also cleared each time a register byte is read—when you read the eight LSBs, the eight LSB interrupts are cleared, and when you read the eight MSBs, the eight MSB interrupts are cleared.

The following register diagram shows the bit organization of STS[7:0]. Descriptions of the bits follow the register diagram.

| APR | D7       | D6    | D5   | D4    | D3   | D2    | D1   | D0       |  |

|-----|----------|-------|------|-------|------|-------|------|----------|--|

| 0   | STS[7:0] |       |      |       |      |       |      |          |  |

| U   | VBER     | S3_LS | S3_S | S2_LS | S2_S | S1_LS | S1_S | Reserved |  |

## VBER Viterbi Bit Error Rate Flag

The L64724 sets the VBER bit when the period specified by VMDC2 (Group 4—APR 5, 6, and 7) is reached. The L64724 also generates an interrupt if the VBER\_IE bit in the SMR is set. The L64724 clears the VBER bit to 0 after a reset or a Group 2 (STS) read.

| <br>VBER | Definition               |

|----------|--------------------------|

| 0        | VMDC2 period not reached |

| 1        | VMDC2 period reached     |

# S3\_LS Stage 3 Loss of Synchronization Flag

The L64724 sets the S3\_LS bit when the Descrambler synchronization module determines that synchronization is lost. It also generates an interrupt if the S3\_LS\_IE bit is set in the SMR. The L64724 clears the S3\_LS bit to 0 after a reset or a Group 2 (STS) read.

| S3_LS | Definition                               |

|-------|------------------------------------------|

| 0     | Stage 3 Synchronization status unchanged |

| 1     | Loss of Stage 3 Synchronization detected |

# S3\_S Stage 3 Synchronization Flag

The L64724 sets the S3\_S bit when the Descrambler synchronization module acquires synchronization. The L64724 also generates an interrupt if the S3\_S\_IE bit is

5

set in the SMR. The L64724 clears the S3\_S bit to 0 after a reset or a Group 2 (STS) read.

| S3_S | Definition                               |

|------|------------------------------------------|

| 0    | Stage 3 Synchronization status unchanged |

| 1    | Stage 3 Synchronization acquired         |

## S2\_LS Stage 2 Loss of Synchronization Flag

The L64724 sets the S2\_LS bit when the Deinterleaver/Reed-Solomon Decoder synchronization module determines that synchronization is lost. The L64724 also generates an interrupt if the S2\_LS\_IE bit is set in the SMR. The L64724 clears the S2\_LS bit to 0 after a reset or a Group 2 (STS) read.

| S2_LS | Definition                               |

|-------|------------------------------------------|

| 0     | Stage 2 Synchronization status unchanged |

| 1     | Loss of Stage 2 Synchronization detected |

#### S2\_S Stage 2 Synchronization Flag

The L64724 sets the S2\_S bit when the Deinterleaver/Reed-Solomon Decoder synchronization module acquires synchronization. The L64724 also generates an interrupt if the S2\_S\_IE bit is set in the SMR. The L64724 clears the S2\_S bit to 0 after a reset or a Group 2 (STS) read.

| S2_S | Definition                               |

|------|------------------------------------------|

| 0    | Stage 2 Synchronization status unchanged |

| 1    | Stage 2 Synchronization acquired         |

# S1\_LS Stage 1 Loss of Synchronization Flag

The L64724 sets the S1\_LS bit when the Viterbi Decoder synchronization module determines that synchronization is lost. The L64724 also generates an interrupt if the S1\_LS\_IE bit is set in the SMR. The L64724 clears S1\_LS to 0 after a reset or a Group 2 (STS) read.

| S1_LS | Definition                               |

|-------|------------------------------------------|

| 0     | Stage 1 Synchronization status unchanged |

| 1     | Loss of Stage 1 Synchronization detected |

3

#### S1\_S Stage 1 Synchronization Flag

The L64724 sets the S1\_S bit when the Viterbi Decoder synchronization module has acquired synchronization. The L64724 also generates an interrupt if the S1\_S\_IE bit is set in the SMR. The L64724 clears S1\_S to 0 after a reset or a Group 2 (STS) read.

| S1_S | Definition                               |

|------|------------------------------------------|

| 0    | Stage 1 Synchronization status unchanged |

| 1    | Stage 1 Synchronization acquired         |

#### Reserved

#### Reserved

0

This bit is reserved for LSI Logic internal use only. Reading this bit will give unpredictable results.

The following register diagram shows the bit organization of STS[15:8]. Descriptions of the bits follow the register diagram.

| APR | D7     | D6      | D5    | D4     | D3      | D2    | D1       | D0       |

|-----|--------|---------|-------|--------|---------|-------|----------|----------|

| 4   |        |         |       | STS[1  | 5:8]    |       |          |          |

| ' [ | CLK_LK | CLK_LLK | CP_LK | CP_LLK | Reserve | d = 0 | CL_FS_LL | CL_FS_UL |

#### CLK LK

# **Timing Lock Established**

15

The L64724 sets the CLK\_LK bit when Timing Lock is established.

| CLK_LK | Definition                   |

|--------|------------------------------|

| 0      | Timing Lock Status Unchanged |

| 1      | Timing Lock Established      |

#### **CLK LLK**

## **Timing Lock Lost**

14

The L64724 sets the CLK\_LLK bit when Timing Lock is lost.

| CLK_LLK | Definition                   |

|---------|------------------------------|

| 0       | Timing Lock Status Unchanged |

| 1       | Timing Lock Lost             |

#### CP LK Carrier Phase Lock Established

The L64724 sets the CP\_LK bit when Carrier Phase Lock is established.

| CP_LK | Definition                          |

|-------|-------------------------------------|

| 0     | Carrier Phase Lock Status Unchanged |

| 1     | Carrier Phase Lock Established      |

#### CP LLK Carrier Phase Lock Lost

12

13

The L64724 sets the CP\_LLK bit when Carrier Phase Lock is lost.

| CP_LLK | Definition                          |

|--------|-------------------------------------|

| 0      | Carrier Phase Lock Status Unchanged |

| 1      | Carrier Phase Lock Lost             |

#### Reserved Reserved

[11:10]

The Reserved bits are for LSI Logic internal use only and must always be cleared to 0.

#### CL\_FS\_LL Frequency Sweep Lower Limit Reached

9

The L64724 sets the CL\_FS\_LL bit when the lower limit of the Carrier Loop Frequency Sweep is reached.

| FS_LL | Definition                          |

|-------|-------------------------------------|

| 0     | Frequency Sweep Status Unchanged    |

| 1     | Frequency Sweep Lower Limit Reached |

# CL FS UL Frequency Sweep Upper Limit Reached

8

The L64724 sets the CL\_FS\_UL bit when the upper limit of the Carrier Loop Frequency Sweep is reached.

| FS_UL | Definition                          |

|-------|-------------------------------------|

| 0     | Frequency Sweep Status Unchanged    |

| 1     | Frequency Sweep Upper Limit Reached |

The following register diagram shows the bit organization of STS[23:16]. Descriptions of the fields follow the register diagram.

| APR | D7 | D6 | D5    | D4  | D3        | D2 | D1          | D0          |

|-----|----|----|-------|-----|-----------|----|-------------|-------------|

|     |    |    |       | S   | TS[23:16] |    |             |             |

| 2   |    |    | Reser | ved |           |    | TL_CL_FS_LL | TL_CL_FS_UL |

#### Reserved Reserved

[23:18]

These bits are reserved for LSI Logic internal use only. The bits, when read, return a value of zero.

#### TL\_CL\_FS\_LL

#### Frequency Sweep Lower Limit Reached

17

The L64724 sets the TL\_CL\_FS\_LL bit when the lower limit of the Timing Loop Frequency Sweep is reached.

#### TL\_CL\_FS\_LL Definition

| 0 | Frequency Sweep Status Unchanged    |

|---|-------------------------------------|

| 1 | Frequency Sweep Lower Limit Reached |

#### TL\_CL\_FS\_UL

#### Frequency Sweep Upper Limit Reached

16

The L64724 sets the TL\_CL\_FS\_UL bit when the upper limit of the Timing Loop Frequency Sweep is reached.

#### TL\_CL\_FS\_UL Definition

| 0 | Frequency Sweep Status Unchanged    |

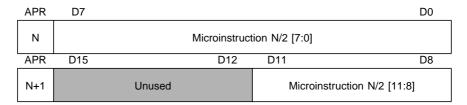

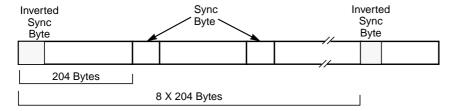

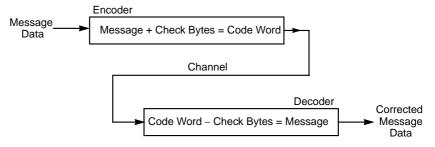

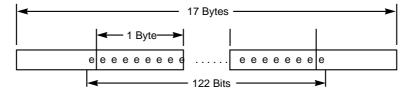

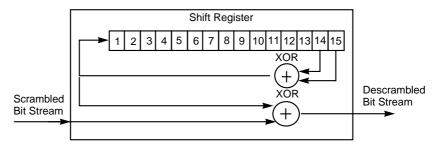

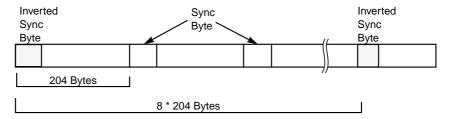

|---|-------------------------------------|