16G040

T-75-11-29

# High Speed Clock & Data Recovery Circuit 2.0 Gbit/s NRZ Data Rate

### **FEATURES**

- Clock recovery and data retiming and regeneration subsystem on a chip

- 2.0 Gbit/s performance with ext. clock source;

1.0 Gbit/s performance with on-chip VCO

- · Patented, self-acquiring PLL GaAs IC design

- On-chip VCO powered separately to allow use of optional external clock source

- Interfaces to 10G041A Time Division DEMUX easily

- Loop bandwidth externally controllable for fast acquisition time

- Available in C-leaded or leadless chip carriers, or as unpackaged die

- Demo Board Available 90GCDR (-DX)

### **FUNCTIONAL DESCRIPTION**

The 16G040 contains the high speed analog and digital circuitry needed to implement a phase locked loop (PLL) for both clock extraction from high speed digital data streams, as well as data retiming and regeneration. All PLL components are on-chip excluding the loop filter. Using the on-chip VCO as a clock source, the 16G040 can be operated from >50 Mbit/s to 1.0 Gbit/s. Performance with an external clock source extends to >2.0 Gbit/s. The 16G040 is available in four forms:

- 1. The 16G040-2C and 16G040-2L are packaged in GigaBit's standard 40 I/O C-leaded and leadless ceramic chip carrier packages, respectively.

- 2. Unpackaged dice (16G040-2X).

- As a demonstration board: part number 90GCRB.

Available in standard frequencies: 100, 250, 565, 622, and 800 Mbit/s. Custom frequences available upon request.

- 4. As in "3" but with a 10G041A-4 1:8 DEMUX incorporated on the board: part number 90GCRB-DX. See the 90GCRB datasheet for more details.

Unlike SAW-filter clock and data recovery approaches which first filter the clock component from incoming data and then retimes it using the extracted clock, the PLL-based 16G040 is capable of synchronizing an on-chip VCO or external clock source directly to an incoming digital data stream, while simultaneously retiming and regenerating the data stream. In addition, the on-chip VCO of the 16G041 or the external clock source will generate a clock output even in the absence of data. This might be critical if the recovered clock drives a state machine or any other logic circuitry that might go into a metastable state in the absence of a clock. In operation, the 16G040-based PLL is capable of unaided frequency acquisition, eliminating the need for special circuits to "pull" the loop into lock when the

### **APPLICATION**

High speed fiber optic and microwave receivers and repeaters

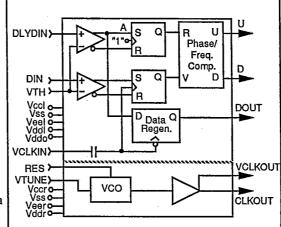

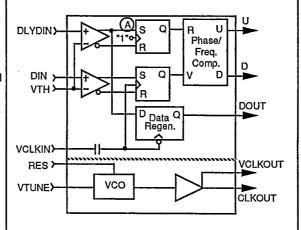

#### 16G040 BLOCK DIAGRAM

### **ORDERING INFORMATION**

| Package or                          | Part No.                                                                        |

|-------------------------------------|---------------------------------------------------------------------------------|

| Product                             | (Min. Data Rate @ 25°C)                                                         |

| C-leaded CC                         | 16G040-2C (≤1.0 Gbit/s)                                                         |

| Leadless CC                         | 16G040-2L (≤1.0 Gbit/s)                                                         |

| Dice                                | 16G040-2X (≤2.0 Gbit/s)                                                         |

| Demo Board<br>Demo Board<br>w/DEMUX | 90GCRB (100-800 Mbit/s; 0°C to 70°C)<br>90GCRB-DX (100-800 Mbit/s; 0°C to 70°C) |

7-75-11-29 16G040

Because the device is implemented as a PLL, the center frequency can be tuned over a wide range and if an external loop filter and clock source are used, their parameters can be chosen to realize extremely fast acquisition time loops. All power supplies to the on-chip VCO are separate so that it can be powered down to decrease power dissipation when the 16G040 is used with an external clock source.

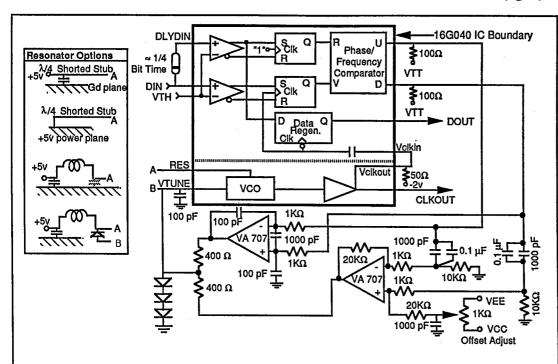

The 16G040 requires an external resonator when the on-chip VCO is used. This resonator can be a 1/4 wavelength tunable microstrip stub or an LC resonator. The 16G040 also requires a fixed external delay (non-critical, between 1/4 and 1/2 bit period) between inputs DIN (Data In) and DLYDIN (Delayed Data In). GigaBit Application Note 7, titled "Application of the 16G040 Clock and Data Recovery Circuit" provides necessary background material and should be carefully reviewed.

A key subcircuit included in the 16G040 is the phase/frequency comparator. This component is also available as a stand-alone product, the 16G044, with a detailed datasheet which supplements the information contained in this datasheet.

The 16G040 is a member of GigaBit's family of components for high speed fiber optic and microwave communications which include the 10G040A time division multiplexer, the 10G041A time division demultiplexer and the 16G044 phase/frequency comparator. The 16G040 utilizes GigaBit's production proven GaAs MESFET process technology.

### 16G040 PLL OPERATION

When interconnected to form a phase locked loop as shown in the Typical PLL Circuit diagram (Fig. 2), two modes of operation are possible: 1) the VCO frequency is equal to the input data rate; that is, the loop is in frequency lock but is not phase locked; 2) the initial VCO frequency is unequal to the input data rate but the data rate is within the loop capture range.

### PHASE OFFSET OPERATION

When the loop is in frequency but not phase locked, the outputs of the phase/frequency comparator (PFC) will produce pulses which, when low pass filtered and subtracted, provide an error signal that is applied to the Vtune input of the VCO to correct the phase offset. With reference to the 16G040 block diagram (Fig. 1), the signal on the PFC "V" input leads the signal on the "R" input when the

rising edge of the clock applied to the clocked S-R latch leads the rising edge of the delayed data input applied to the transparent S-R latch ("A" in the block diagram). "V" lags" R" when the rising edge of the clock input lags the signal at A.

Figure 1: 16G040 BLOCK DIAGRAM

### **PIN DESCRIPTIONS**

| I | DUM       | 10.6                                          |

|---|-----------|-----------------------------------------------|

| l | DIN       | High speed, serial data input.                |

|   | DLYDIN    | Delayed data input.                           |

| I | VTH       | The threshold bias control to the input       |

| ı |           | comparators1.3V≤Vcm≤0V.                       |

| ı | VCLKIN    |                                               |

| ļ | VCLKIN    | AC-coupled clock input, typically driven from |

| Ì |           | the VCLKOUT pin.                              |

| ł | RES       | 1/4 wavelength stub or LC resonator           |

| 1 |           | connection.                                   |

|   | VTUNE     |                                               |

|   | VIOINE    | DC tuning voltage input to the VCO. Nom.      |

|   |           | tuning voltage range is -2.5V to +2.5V.       |

| 1 | U, D      | Phase error outputs of the phase/freq.        |

| 1 |           | comparator.                                   |

|   | VCLKOUT,  | The VCO output pins. These pins are           |

|   | CLKOUT    | interchangeable.                              |

|   |           |                                               |

|   | DOUT      | Reclocked, regenerated data output.           |

|   | Vccl,Vccr | +5.0V power supply connections.               |

|   | Vss       | -3.4V power supply.                           |

| ĺ | Veel,Veer | -5.2V power supply pins.                      |

| Į | Vddl,Vddr | Ground connections.                           |

| ı | •         |                                               |

|   | Vddo      | Output driver ground connection for data      |

| i |           | regenerator and phase/freq. comparator.       |

| Į |           | •                                             |

16G040 T-75-11-29

Figure 2: Typical Clock Recovery PLL Implementation

The relative phase of "V" with respect to "R" is sensed by a phase/frequency comparator. The phase/ frequency comparator is an edge-triggered digital device which produces pulses in "U" when "R" leads "V" and in "D" when "R" lags "V". The width of these pulses is equal to the amount by which "R" leads or lags "V". Only one output is active at a time. The difference between the "U" and "D" outputs is fed back to the VCO through an appropriate loop filter, which then "servos" the VCO in the direction necessary to correct this phase offset. When the loop is in lock, the rising edges of "A" are exactly lined up with the rising edges in "CLK". This ensures that the falling edge-triggered D- type flip-flop, which is used as a "decision circuit" to detect the digital data, is clocking precisely in the middle of the data bit, and thus has maximum timing margin to prevent jitter-induced bit

When the loop is phase locked, then both the PFC "U" and "D" outputs are low, resulting in a zero error voltage being applied to the loop filter.

Therefore, the tendency is for the loop to hold its frequency once it is locked. This condition also occurs in the absence of any rising edges (often called "missed transitions") in the input data.

When the loop is locked, missing transitions will not cause loss of lock as long as the frequency of transitions exceeds 10 times the loop filter cutoff frequency, as a rule of thumb. However, during acquisition, long strings of "1's" and "0's" will cause an increase in loop acquisition time since these strings of constant data present no phase information to the loop. In this case, the effective phase detector gain factor (Kd) is reduced, according to: Kd effective = Ptr X Kd where Ptr is given by (number of transitions) + (number of bits).

This factor can be called the "probability of transitions", or more accurately, the "transitions ratio" and is a measure of the spectral richness at the clock frequency of a digital data stream. A lower Kd (all other factors constant) lowers the closed loop gain of the PLL, resulting in a longer acquisition time.

4

*7-75-11-29* 16G040

### **DEFINITION OF TERMS**

### LOOP ACQUISITION TIME

The total time taken by the PLL to establish lock is called the acquisition time. Acquisition time depends on the initial frequency and phase differences between the two signals as well as on the overall loop gain and the low pass filter bandwidth.

### LOOP CAPTURE RANGE

The frequency range centered about the initial VCO free-running frequency over which the loop can acquire lock with the input signal. The capture range is a measure of how close the input signal frequency must be to that of the VCO to acquire lock assuming an initial condition of no incoming data. The "capture range" can assume any value within the lock range and depends primarily upon the band edge of the low pass filter together with the closed loop gain of the system.

### LOOP LOCK RANGE

The frequency range centered about the initial VCO free-running frequency over which the loop can track the input signal once lock has been achieved. The lock range is limited by the range of error voltage that can be generated by the loop filter and the corresponding VCO frequency deviation produced. The lock range is essentially a dc parameter and is not affected by the band edge of the low pass filter.

### FREQUENCY ACQUISITION

When the initial VCO frequency is unequal to the input data rate, the phase/frequency comparator produces "beat notes" which drive the VCO in the direction which will correct the frequency error. This acquisition process is highly complex and does not lend itself to simple mathematical analysis. The capture range of the loop is a function of the standard PLL parameters such as the phase detector gain, loop filter bandwidth, VCO control gain and the delay between the DIN and DLYDIN pins.

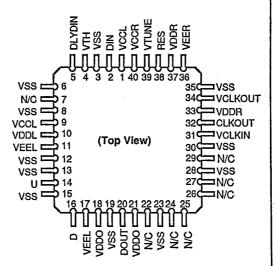

### PIN FUNCTIONS - PACKAGE TYPES "L" AND "C"

### 40 I/O LEADLESS CHIP CARRIER

#### DLYDIN VTH VSS DIN VCCL VCCR VTUNE RES VDDR 2 1 40 39 38 3736 35¢ VSS VSS 34¢ VCLKOUT N/C 33√ VDDR VSS 32 CLKOUT VCCL 31 VOLKIN 10 VDDL (Top View) VEEL 11 vss 29 N/C 12 VSS 5 12 13 VSS VSS N/C U VSS

### NOTES:

Pin 1 is marked for orientation. N/C = no connection.

### 40 I/O C-LEADED CHIP CARRIER

#### NOTES:

Pin 1 is marked for orientation. N/C = no connection.

# **GBL**) GigaBit Logic

|                                                       | 16G040 ABSOLUT  (Beyond which useful life ma                                                                                                                                                                                                                                                                                                                                                         | E MAXIMUM RATINGS by be impaired) (Notes 1, 4)                                                                                                                                                                      |       |

|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| SYMBOL                                                | PARAMETER                                                                                                                                                                                                                                                                                                                                                                                            | ABSOLUTE MAXIMUM RATINGS                                                                                                                                                                                            | NOTES |

| TSTOR TJ TC VDDO VCC VSS VEE VIN IIN VOUT IOUT PD VTT | Storage Temperature Junction Temperature Case Temperature Under Bias Output Driver Supply Voltage Supply Voltage Supply Voltage Supply Voltage Supply Voltage Voltage Applied to Any Input; Continuous VSS = -3.4 V, VEE = -5.2 V Current Into Any Input; Continuous Voltage Applied to Any Output Current From Any Output Current From Any Output POUT = (VDDO-VOUT) x IOUT Load Termination Supply | -65°C to + 150°C -55°C to + 150°C -55°C to + 125°C VSS to + 1.0 V +1.0 V to +7.0 V -4.0 V to +0.5 V -7.0 V to VSS + 0.5 V -4.0 V to +0.5 V  -0.5 mA to 1.0 mA -4.0V to +7.0 V -100 mA 100 mW -6.0 V to VDDO + 6.0 V | 2     |

- 1. All voltages specified with VDDL= VDDR = Gnd. Positive current is defined as current into the device.

- 2. TC is measured at case top.

- 3. Subject to IOUT and power dissipation limitations.

- 4. Power supply sequencing is not necessary, but since the VEE supply is used to bias off the normally-on depletion mode transistors, sustained (>5 secs.) application of VSS in the absence of VEE may result in excessive power dissipation and damage to the device.

### 16G040 RECOMMENDED OPERATING CONDITIONS

| SYMBOL                                                  | PARAMETER                                                                                                                                                                                     | MIN                            | NOM                                       | MAX                                 | UNITS                                   | NOTES |  |

|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-------------------------------------------|-------------------------------------|-----------------------------------------|-------|--|

| TC<br>VDDL,R<br>VDDO<br>VCCL,R<br>VSS<br>VEEL,R,<br>VTT | Case Operating Temperature<br>Ground Connections<br>Output Driver Supply Voltage<br>Supply Voltage<br>Supply Voltage(common in L,C pkgs)<br>Supply Voltage<br>Load Termination Supply Voltage | -0.8<br>4.75<br>- 3.5<br>- 5.5 | 25<br>Gnd<br>Gnd<br>5.0<br>- 3.4<br>- 5.2 | 85<br>1.0<br>5.25<br>- 3.3<br>- 5.1 | © V V V V V V V V V V V V V V V V V V V | 1     |  |

| RLOAD                                                   | Output Termination Load Resistance                                                                                                                                                            | VSS<br>25                      | - 2.0<br>50                               | - 2.0<br>100                        | Ω                                       | 2     |  |

### Notes:

- Tcase measured at case top. HEATSINKING IS REQUIRED.

See GigaBit Application Note 3, "Thermal Management of PicoLogic and NanoRam GaAs Digital IC Families" for a complete discussion of all aspects of device thermal management. Heatsinks are available from GigaBit. See page 8, notes 6 and 7.

- 2. The RLOAD and VTT combination used is subject to maximum output current and power restrictions.

4

7-75-7/-29 16G040

# (GBL) GigaBit Logic

| Symbol    | <del></del>                     |              | · <del></del> | · · ·        | ATIONS   |                                   |

|-----------|---------------------------------|--------------|---------------|--------------|----------|-----------------------------------|

|           | Parameter                       | Min          | Тур           | Max          | Units    | Test Conditions                   |

| Data Inp  | outs                            |              |               |              |          |                                   |

| VIH       | Input high voltage              | -1.0         |               | 0.0          | V        | Vth = -1.3V                       |

| VIL       | Input low voltage               | -2.0         |               | -1.6         |          | Vth = -1.3V                       |

| CMR       | Common mode range               | -1.6<br>-300 |               | -1.0<br>300  | V<br>μA  | Vin = VIH max to VIL min          |

| Clock In  | Input current                   | -300         |               | 300          | μΑ ]     | VIII = VIII IIIAX (O VIL IIIIII   |

| Vckdc     | DC voltage bias                 | -1.3         |               | 0            | l v l    |                                   |

| Pck       | Input power                     | 0            |               | 13           | dBm      |                                   |

|           | requency Comparator Output      | L            |               |              | 1        |                                   |

| Kd        | Large signal gain constant      | 250/π        | 300/π         |              | mV/rad   | Alternating 1,0 pattern           |

| kd        | Small signal gain constant      | 125/π        | 150/π         |              | mV/rad   | Alternating 1,0 pattern           |

| VOH       | Output peak voltage             | -0.8         | -0.5          | -0.3         | V        | $100\Omega$ to Vtt = -2.0V term.  |

| VOL       | Output low level voltage        | VTT          | -1.8          | -1.6         | V        | $100\Omega$ to Vtt = -2.0V term.  |

| Data an   | nd Clock Outputs                | •            | ·             | •            |          |                                   |

| VOH       | Output high level voltage       | -0.8         | -0.5          | -0.3         | V        | $50\Omega$ to Vtt = -2.0V term.   |

| VOL       | Output low level voltage        | Vtt          | -1.8          | -1.7         | l v l    | $50\Omega$ to Vtt = -2.0V term.   |

| tdD       | Clock output falling edge to    |              | TBD           | 1            | ps       |                                   |

|           | data output delay               | <u> </u>     | <u> </u>      |              |          |                                   |

|           | aracteristics                   |              |               |              |          |                                   |

| Kv        | VCO gain constant               |              | 4             |              | MHz/V    | @600 MHz, $1/4 \lambda$ stub res. |

| Δfv       | VCO freq. drift vs. temp.       | -30          |               | -60          | KHz/°C   | @400 MHz inclu, resonator         |

| Vin       | Vtune input voltage             | -5.0         |               | 2.5          | V        | Badaaa aa ta allaa da             |

| Cres      | Resonator input capacitance     | <del></del>  | 1.5           | <u> </u>     | pf       | Package cap. to adjacent leads    |

| ICCL      | upply Currents                  |              | 1 60          | 1            | 1        | T                                 |

| IEEL.     | Loop components supply currents | İ            | 63<br>-128    | 1            | mA<br>mA |                                   |

| ICCR      | Resonator & VCO supply          |              | 14            |              | mA       |                                   |

| IEER      | currents                        | •            | -30           |              | mA       |                                   |

|           | Common VSS supply current       |              | -121          | <del> </del> | mA       | <del>i</del>                      |

|           | Power Dissipation               |              | 1.6           |              | W W      | 1                                 |

| ISS<br>PD |                                 |              |               |              |          |                                   |

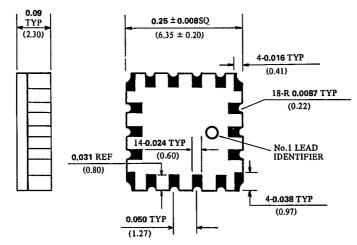

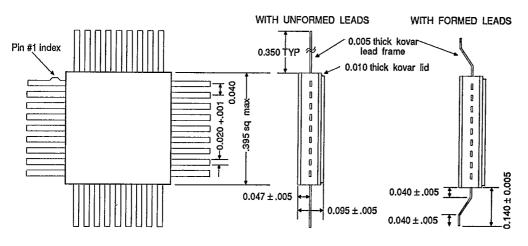

### 24 PIN HYBRID **18 PIN PACKAGE**

T-90-20

### 24 PIN HYBRID PACKAGE

### 18 PIN LEADLESS CHIP CARRIER TYPE L1

All dimensions shown in inches and (millimeters)

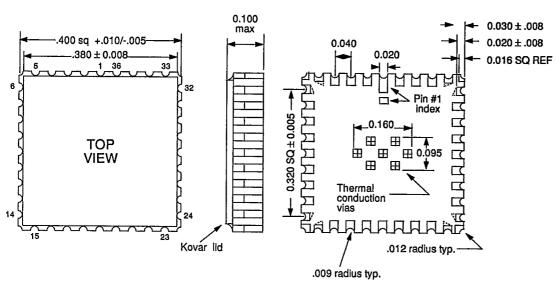

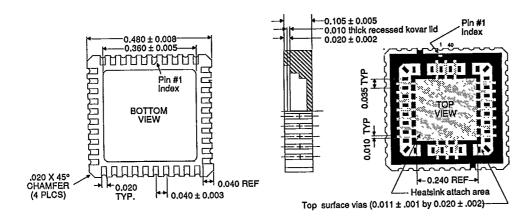

## T-90-20 36 PIN PACKAGES

### 36 PIN LEADLESS CHIP CARRIER TYPE L36

### NOTES:

- The package bottom thermal vias, top lid surface and 4 metallized corner castellations (when present) are all at Vss potential.

- 2) All dimensions in inches.

- 3) Plin #1 identifier may be an elongated pad or small, square gray marker.

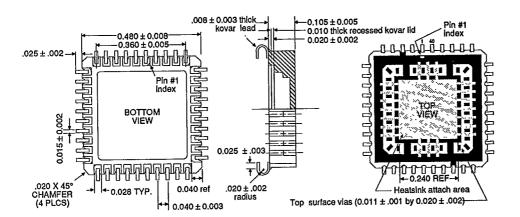

# 36 I/O LEAD FLATPACK TYPE F

11

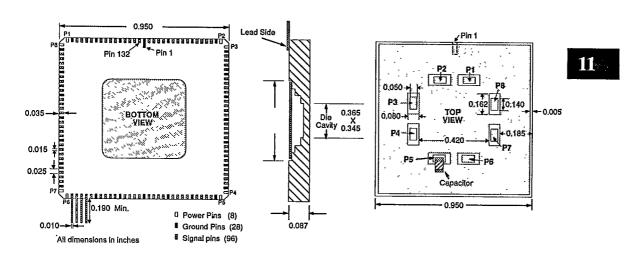

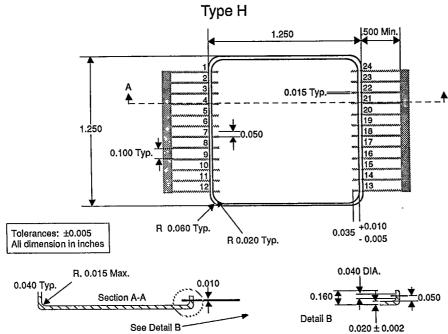

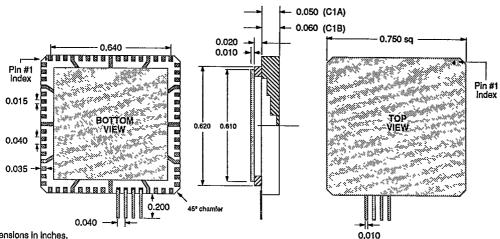

### T-90-20 **40 PIN PACKAGES**

### **40 PIN LEADLESS CHIP CARRIER** TYPE L

### **40 PIN LEADED CHIP CARRIER** TYPE C

### NOTES:

- (1) Footprint is JEDEO standard outline.

(2) Top surface vias (for terminating resistors and decoupling capacitions) are not available on prins 3,417,18, 23,24,37 and 38.

(3) Top surface metal (not including vias) and prins 3 and 23 are litted at VTT pote of Recommended top surface chip resistors are 0,040 long by 0,030 wide by 0,010 thick typ, 100 mm min. normal power rating (Mint Systems MSC 200 wide by 0,010 thick typ, 25 of the chip of the ch

- or equivalent)

(8) L40 and C40 packages are dimensionally identical except for contact finger width

68 & 132 PIN PACKAGES T-90-20

## 68 PIN LEADED CHIP CARRIER TYPE C1

(1) All dimensions in inches.

(2) a. C1A: Package lid, top, and pins 4, 9, 14, 21, 26, 31, 38, 43, 48, 55, 60, 65 are at common potential (system ground).

b. C1B: Package lid and pins 4, 9, 14, 21, 26, 31, 38, 43, 48, 55, 60, 65 are at common potential (system ground).

## 132 PIN LEADED CHIP CARRIER TYPE C3