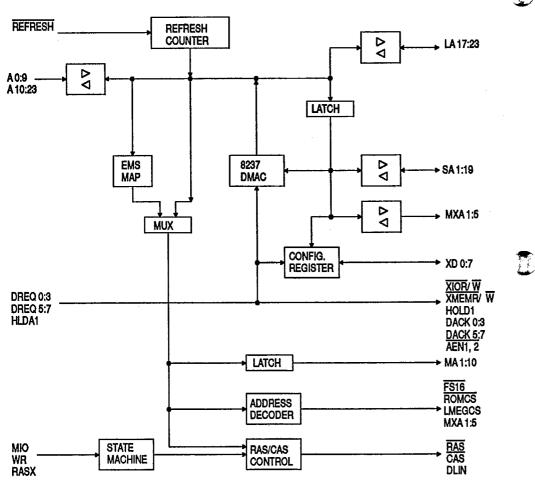

T-52-33-03 GS62C102 MEMORY/ADDRESS CONTROLLER

#### **1. FEATURES**

- Address buffer and latch circuits.

- The I/O address decoder circuit.

- 10 separate hardware or software configurable memory configurations for a flexible memory system design.

- LIM 4.0 EMS controller circuit register circuit.

- DRAM page mode controller circuit.

- Gold mode memory controller circuit. (non-page mode RAM).

- 8237 memory address refresh counter circuit.

- Early RAS and CAS signal generation.

- DMA page mapper circuit.

- 8237 DMA controller (X2).

- Low power CMOS VLSI implementation.

- 160 pins QFP package.

#### 2. DESCRIPTION

#### Memory Subsystem

The SUNTAC GS62CS102 chip supports both a conventional 0 wait state memory subsystem and a 4-bank 4-way page interleaved memory subsystem. It supports up to 8MB of on-board memory with combinations of 256Kbit and 1Mbit DRAMs. For example, one bank of 1Mbit DRAM plus two banks of 256Kbit DRAM can be used to provide a total of 3MB memory for running the DOS compatible function of OS/2. Special design is incorporated in the memory controller to allow a 10 to 15 percent enhancement in DRAM efficiency. Hidden refresh and minimized precharge time are several features which enhances the memory performance. The processor can run at

20Mhz and 16Mhz with 0.3 wait state using 100ns and 120ns, respectively. In addition, GS62C102 can be configured to run at 16 MHz using conventional DRAM mode. The page mode performance can be further enhanced by using fast page mode DRAMs. The page-interleave feature of the memory subsystem takes the advantages of both the page mode RAM and memory bank interleave. The fast page mode RAM allows for fast 0WS on page accesses during high speed CPU operation. The four page interleaved banks www.Datasheethu.com acts as four separate segments of one page size. This feature ideally matches the four segment process model of the

T-52-33-03

**1**

.

Intel IAPX<sup>®</sup> architecture for enhanced performance for both protected and real mode.

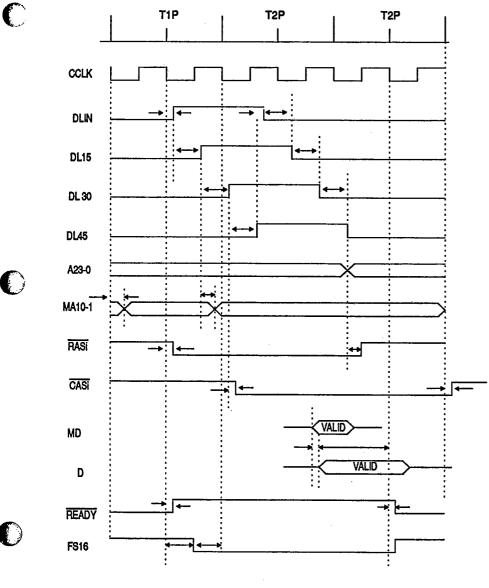

#### MEMORY CONTROL

GS62C102 converts the address to MA for local memory for both EMS enabled and EMS disabled. In addition, this chip provides the bank select, RAS and CAS signals to control the DRAM. When the ROM is being accessed, the MXA is also used with the MA to address the content of the ROM. Several delay lines are connected with DLIN as output and DL15, DL30 and DL45 as input. These signals provide the necessary signals to generate the memory control signals.

#### **ADDRESS CONTROL**

GS62C102 provides the address buffering from CPU to MA, LA, SA and XA in CPU cycle, and SA to XA, MA in MASTER cycle. In DMA cycle, the ad-

#### Shadow RAM/EMS/Extended Memory

The LIM EMS version 4.0 is fully supported by the EMS registers built into the chip set. Either 640KB or 512KB can be used as the base memory and the remaining DRAMs can be used as extended memory, EMS memory, BIOS shadow RAM or video shadow RAM. For example, when 1MB memory is available with 640KB base memory, 64KB can be used as BIOS shadow RAM and video shadow RAM. The remaining 320 KByte can be configured as conventional extended memory or 20 pages of EMS memory, or as 96 KBytes extended memory plus 14 pages of EMS memory. Each individual EMS page can be disabled or enabled by dress is generated from internal DMA controller. The bus master accesses are not mapped by the EMS circuit.

writing to the configuration registers. GS62CS0102 chip supports EMS without any speed penalty.

The SUNTAC GS62CS102 chip supports both 8- and 16-bit PROM. The 8-bit mode operation not only reduces the board space but also reduces cost and inventory. With the optional BIOS shadow RAM enabled, the 8-bit mode operation is faster than the 16-bit mode operation (without shadow RAM). The chip set also supports single ROM for both system and video BIOS. This further reduces the board space and component cost for all-in-one motherboard designs.

21E D 🔳 3775612 0000124 6 🔳

T-52-33-03

Features of the GS62C102 include:

- Optional shadow RAM for system and video BIOS ROM.

- Fully support EMS 4.0 with 64 EMS registers.

- Two shadow RAM map: window size programmable.

- Two alternate sets of 6 EMS registers. The 6 registers are grouped into 4 contiguous 16KB blocks (total 64K, EMS-3.2) and 2 contiguous 16KB blocks (total 32K, EMS-4.0).

- Extended memory is left over while the space between BASE 0FFFFF is not programed as EMS or SHADOW RAM.

#### **CONFIGURATION REGISTER**

The default configuration index port I/O address is defined at 98H after power up. One can program the configuration registers by first writing the correct index register number to the I/O address 98H (Index Address Register) and then, the new data for the index register to the I/O address 99H (Index Data Register). In case of the I/O address conflict with some other I/O devices, one can program the Index Address Register and the Index Data Register by writting to the new location to the Index register location 00H. In addition, to the above software programmable configuration, the initial power on setup can be read in using the DIP switches. These DIP switch setting is documented in a table at the end of this section.

•

induced and the second second

.

,

G S TECHNOLOGY

.

# 21E D 🔳 3775612 0000127 1 🔳

a a ser a

T-52-33-03

Caral and and

•

# **PIN DESCRIPTION**

- · ·

| Pin Name      | Pin Number         | Туре | Description                                                                                                                                                                                                                |  |  |  |

|---------------|--------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| CPU Interface |                    |      |                                                                                                                                                                                                                            |  |  |  |

| M/IO          | 91                 | I    | Memory/IO status from the CPU.                                                                                                                                                                                             |  |  |  |

| W/R           | 55                 | 1    | W/R status pin from the CPU.                                                                                                                                                                                               |  |  |  |

| BHE           | 158                | I/O  | CPU byte-high-enable pin, CD8-CD15 to be valid. This pin is logical complement of the A0 pin.                                                                                                                              |  |  |  |

| A0:9          | 128-137            | I    | CPU address line A0 to A9.                                                                                                                                                                                                 |  |  |  |

| A10:23        | 138-139<br>146-157 | 1    | CPU address line A10 to A23.                                                                                                                                                                                               |  |  |  |

| READY         | 45 I/O             |      | Connects to CPU's "READY" pin. READY<br>signal to CPU when cycle other than loca<br>memory access is done. This pin serves as<br>output during local memory cycle. For al<br>other cycles, this pin serves as an input pin |  |  |  |

| HLDA          | 92 I               |      | Connects to CPU's "HOLDA" pin. Hold ac<br>knowledge from CPU. This pin indicates<br>that AT Bus has been acquired by another<br>bus master.                                                                                |  |  |  |

| GS62C101 I    | nterface           |      |                                                                                                                                                                                                                            |  |  |  |

| RASX          | 54                 | 1    | The synchronized version of address strobe.                                                                                                                                                                                |  |  |  |

| RSTX          | 104                | I    | Reset pin from GS62C101. Resets the G62C102 from either power on or key board.                                                                                                                                             |  |  |  |

.

21E D 🔳 3775612 0000128 3 📟

.

T-52-33-03

1

| Pin Name | Pin Number            | Туре | Description                                                                                                                                                                                                           |

|----------|-----------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CCLK     | 105                   | I .  | CPU clock input from the clock generato<br>on board of the GS62C101. This pin is also<br>connected to the clock input of the CPU<br>During the Low Power and Sleep Mode<br>this clock frequency is reduced or stopped |

| SYSCLK   | 106                   | I    | System clock from the GS62C101 is used<br>for the 8237 DMA controller. It is derived by<br>dividing the AT clock by two. This pin is used<br>to generate the DMA clock.                                               |

| FS16     | 111                   | 0    | Asserted when local memory is accessed<br>Active low indicates a 16 bits local memory<br>access.                                                                                                                      |

| ALE      | 89                    | l    | Address-latch-enable from the GS62C101 indicating valid address on SA bus.                                                                                                                                            |

| LMEGCS   | 112                   | 0    | Low mega memory operation. This pin in dicates a memory access under 1MB.                                                                                                                                             |

| MXA1:5   | 87-88,<br>125-<br>127 | I/O  | X address bus to on-board peripheral and<br>ROM. Also used to address configuration<br>registers. These pins are also used to read<br>in default dip switch setting during powe<br>on.                                |

| XD0:7    | 9-12,<br>115-<br>118  | 1/0  | X data bus. These pins carry the data<br>needed for programming the DMA and the<br>configuration registers. These pins are also<br>used to read in default dip switch setting<br>during power on.                     |

| XIOR     | 85                    | 1/0  | XIO read command. This command is ac<br>tive when one wants to read from an I/C<br>device on the X bus.                                                                                                               |

| VOIX     | 86                    | I/O  | XIO write command. This command is ac<br>tive when a write is performed on an X bus<br>I/O device.                                                                                                                    |

| XMEMR    | 69                    | 1/0  | Memory read command that indicates a local memory read operation.                                                                                                                                                     |

## 21E D 🔳 3775612 0000129 5 🔳

. . . . . . . . . . . . .

5-

# T-52-33-03

**3**

.

| Pin Name  | Pin Number              | Туре | Description                                                                                                                                                  |

|-----------|-------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XMEMW     | 68                      | VO   | Memory write command that indicates a local memory write operation.                                                                                          |

| HOLD37    | 58                      | 0    | Hold request generated by the internal DMA controller (8237).                                                                                                |

| HLDA37    | 59                      | 1    | Hold acknowledge from the hold circuit on<br>GS62C101 indicating that the CPU has<br>been put on hold, and the DMA controller<br>has the control of the bus. |

| AEN1,2    | 62-63                   | 0    | AEN1 and AEN2 from the built-in DMA controller. The signal indicates either a 16-bits or 8-bits DMA accesses.                                                |

| REFRESH   | 64                      |      | Refresh cycle. Generate by the refresh timer or external master to commence refresh operation.                                                               |

| MEMORY In | lerface                 |      | · · · · · · · · · · · · · · · · · · ·                                                                                                                        |

| ROMCS     | 53                      | 0    | ROM chip select. This pin indicates a ROM access cycle to the GS62C101. This pin also enable the ROM.                                                        |

| MA1:10    | 21-26, 38-<br>39, 42-43 | 0    | Memory address bus. These pins are con-<br>nected to the address input of the DRAM<br>and ROM chips.                                                         |

| DLIN      | 70                      | 0    | Delay line input. These lines are used to generate address strobe to local memory.                                                                           |

| DL15      | 71                      | l    | Delay line 1st input indicating a delay signal is generated by delaying the DLIN signal 15 ns.                                                               |

| DL30      | 72                      | 1    | Delay line 2nd input indicating a delay sig-<br>nal is generated by delaying the DLIN sig-<br>nal 30 ns.                                                     |

| DL45      | 73                      | I    | Delay line 3rd input indicating a delay signal is generated by delaying the DLIN signal 45 ns.                                                               |

21E D 🗰 3775612 0000130 1 🖿

.

T-52-33-03 =

en de companya en companya

.

| Pin Name      | Pin Number                                                                                  | Туре | Description                                                                                                           |

|---------------|---------------------------------------------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------|

| RAS0:3        | 5, 19,<br>34, 37                                                                            | 0    | Row address control for the 4 banks o memory.                                                                         |

| CAS0:3L       | 4, 18,<br>33, 36                                                                            | 0    | Column address control for low bytes.                                                                                 |

| CAS0:3H       | 3, 17,<br>32, 35                                                                            | 0    | Column address control for high bytes.                                                                                |

| BUS Interface | )                                                                                           |      |                                                                                                                       |

| SA1:19        | 7-8, 15-<br>16, 29-30,<br>56-57, 65-<br>66, 82-83,<br>95-96,<br>109-110,<br>122-123,<br>142 | I/O  | System address line from the A1 to A19<br>These signals are latched by ALE signal.                                    |

| LA17:23       | 31, 44, 67,<br>20, 124,<br>143-144                                                          | I/O  | System LA bus. These lines are no latched, and they come directly from the CPU address bus.                           |

| MASTER        | 113                                                                                         | I    | MASTER cycle. Indicates a bus master has<br>taken control of the ISA Bus. This signa<br>comes from the ISA Bus slots. |

| DREQ0:3       | 46-49                                                                                       | I    | DMA request inputs from the ISA Bus.                                                                                  |

| DREQ5:7       | 50-52                                                                                       | I    | DMA request inputs from the ISA Bus.                                                                                  |

| DAK0:3        | 97-100                                                                                      | 0    | DMA acknowledge outputs to the devices<br>on the ISA Bus requesting a DMA transfer                                    |

21E D 🔳 3775612 0000131 3 🔳

-

a set as a la

T-52-33-03

NULL PRESS

.

| Pin Name     | Pin Number | Туре | Description                                                                                                                                                                                                                                                                 |

|--------------|------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DAK5:7       | 101-103    | 0    | DMA acknowledge outputs to the devices on the ISA Bus requesting a DMA transfer.                                                                                                                                                                                            |

| T/C          | 145        | 0    | Terminal count from DMA controller. This<br>pin is used to indicate the count of byte<br>being transferred.                                                                                                                                                                 |

| IOCHRDY      | 74         | I    | IO channel ready. This signal is used by a slow device on the ISA Bus that requires an access time longer than the 4 wait state normally allocated for the I/O transfers.                                                                                                   |

| SYSTEM Inte  | erface     |      |                                                                                                                                                                                                                                                                             |

| AS146818     | 75         | 1/0  | 146818 AS. Real Time Clock interface. This<br>pin is connected to the 146818's AS pir<br>which function as address strobe for read-<br>ing the time and the configuration informa-<br>tion. This pin is also used to read in defaul-<br>dip switch setting during power on. |

| DS146818     | 76         | 1/0  | 146818 DS. RTC interface. This pin is con-<br>nected to the 146818's DS pin which func-<br>tions as the data strobe for setting time and<br>writing configuration. This pin is also used<br>to read in the default dip switch setting<br>during power on.                   |

| RW146818     | 77         | 0    | 146818 R/W. RTC interface. This pin con<br>nects to the R/W pin of the 146818, indicat<br>ing the read or write command to the RAM                                                                                                                                          |

| KYCS         | 114        | I/O  | Key board controller (8742) chip select<br>This pin is also used to read in the defaul<br>dip switch setting during power on.                                                                                                                                               |

| A20G         | 90         | 1    | A20GATE signal from keyboard controller<br>This signal cause a fast reset that allows<br>one to switch from protected mode to rea<br>mode. It is an optimization for the OS 2.                                                                                              |

| TST1<br>TST2 | 84<br>6    |      | Enable test mode for GS62C102. Always pull high.                                                                                                                                                                                                                            |

## 21E D 🖬 3775612 0000132 5 💼

T-52-33-03 ·

~.\*

5

.

# **CONFIGURATION DESCRIPTION**

#### MEMORY CONFIGURATION

## Table I: Memory configuration

## ■ 4 banks up to 8M byte.

| Mode |      | Total memory |      |      |                                       |

|------|------|--------------|------|------|---------------------------------------|

|      | 0    | 1            | 3    | 4    | · · · · · · · · · · · · · · · · · · · |

| 1    | 256K |              |      |      | 512K                                  |

| 2    | 256K | 256K         |      |      | 1M                                    |

| 3    | 1M   |              |      |      | 2M                                    |

| 4    | 256K | 1M           |      |      | 2.5M                                  |

| 5    | 256K | 256K         | 256K | 256K | 2M                                    |

| 6    | 256K | 256K         | 1M   |      | 3M                                    |

| 7    | 1M   | 1M           |      |      | 4M                                    |

| 8    | 256K | 256K         | 1M   | 1M   | 5M                                    |

| 9    | 1M   | 1M           | 1M   |      | 6M                                    |

| 10   | 1M   | 1M           | 1M   | 1M   | 8M                                    |

#### Table II: DRAM WAIT STATE

| Mode                                                                           | Wait state   |     |     | Corresponding DRAM (Mhz/ns)           |  |

|--------------------------------------------------------------------------------|--------------|-----|-----|---------------------------------------|--|

| NON-PAGE                                                                       |              | 0   |     | 16/60                                 |  |

| (GOLD MODE)                                                                    |              | 0.5 |     | 16/60                                 |  |

|                                                                                | 1            |     |     | 16/80                                 |  |

|                                                                                |              | 1.5 |     | 16/100                                |  |

| PAGE MODE                                                                      | START ON OFF |     | OFF | · · · · · · · · · · · · · · · · · · · |  |

| REG-PAGE:                                                                      | 2 0 3        |     | 3   | 16/120, 20/100, 25/80                 |  |

| FAST-PAGE:                                                                     | 1.5 0 2.5    |     | 2.5 | 16/100, 20/80, 25/60                  |  |

| SUPER-PAGE:                                                                    | 1 0 2        |     | 2   | 16/80, 25/60                          |  |

| Each read after write cycle will have 1 wait state.<br>ROM: 1 or 3 wait state. |              |     |     |                                       |  |

## 21E D 🔳 3775612 0000133 7 🔳

· · •

- . . .

T-52-33-03

,

## Table 3: System Configuration Register

| Index Regis                                                          | iter #0                                                                                                                                                                                                                                                                                                                                        | and the second se |

|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| index data r                                                         | r contains the I/O address of the index address register and the<br>egister. The default I/O address for index address register is 98H,<br>ault index data register is 99H. (See below for the index registers<br>n)                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Index Regis                                                          | ster #30                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| bit 0<br>bit 1<br>bit 2<br>bit 3<br>bit 4<br>bit 5<br>bit 6<br>bit 7 | Reserved. Always pull low.<br>0=8-bits ROM 1=16-bits ROM<br>AT Bus clock select: 0=ATCLK, 1=CLK2/2<br>Rom Accesses Wait State: 0=3WS, 1=1WS<br>0=Page Interleave Mode, 1=Gold Mode<br>0=Fast Page Mode, 1=Normal Page Mode<br>Gold Mode Wait State: 0=0WS, 1=1WS<br>Enable Setup ROM: 0=disabled(use FFFFF0),<br>1=enabled(remap to setup ROM) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Index Regis                                                          | ster #31                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| bit 0,1,2,3<br>bit 4,5                                               | Memory Bank Configuration (see TABLE 1)<br>00=disable EMS, disable shadow RAM.<br>01=enable shadow RAM only.<br>10=enable EMS and shadow RAM.<br>11=reserved.                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Index Regis                                                          | ster #32                                                                                                                                                                                                                                                                                                                                       | <u> </u> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| bit 0                                                                | RAS time out: 0=disable 1=enable                                                                                                                                                                                                                                                                                                               | ]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Index Regis                                                          | ster #33                                                                                                                                                                                                                                                                                                                                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| bit 0                                                                | Video BIOS relocate to allow for single ROM for all BIOS:<br>0=disable, 1=enable                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Index Regis                                                          | ster #38:                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| bit 0<br>bit 1                                                       | base memory ceiliing: 0=640K, 1=512K<br>enable EMS alternate set (0=A 1=B)                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

# 21E D 🖿 3775612 0000134 9 (

T-52-33-03

,

## Table 3: System Configuration Register Continued

| 4 | 8  | - <b>F</b> |

|---|----|------------|

| 4 |    |            |

| 1 | Ê. |            |

- Sierela

| Index Regis                                                                                               | Index Register #39: extended memory ceiling |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------|---------------------------------------------|--|--|--|--|--|

| bit 0                                                                                                     | memory address bit 23                       |  |  |  |  |  |

| bit 1                                                                                                     | memory address bit 22                       |  |  |  |  |  |

| bit 2                                                                                                     | memory address bit 21                       |  |  |  |  |  |

| bit 3                                                                                                     | memory address bit 20                       |  |  |  |  |  |

| bit 4                                                                                                     | memory address bit 19                       |  |  |  |  |  |

| bit 5                                                                                                     | memory address bit 18                       |  |  |  |  |  |

| Index Regis                                                                                               | Index Register #3A                          |  |  |  |  |  |

| bit 0                                                                                                     | read enable the shadow RAM                  |  |  |  |  |  |

| Index Regis                                                                                               | ter #3B                                     |  |  |  |  |  |

| bit 0                                                                                                     | write enable the shadow RAM                 |  |  |  |  |  |

| Index Register #3C-3F:                                                                                    |                                             |  |  |  |  |  |

| Enable/disable bit pattern for individual EMS pages.                                                      |                                             |  |  |  |  |  |

| Each bit corresponds to each of the currently enabled 32 EMS registers.                                   |                                             |  |  |  |  |  |

| Index Register #40-7F:                                                                                    |                                             |  |  |  |  |  |

| EMS Look up table content each of the 64 index registers contains the 9 bits address mapping information. |                                             |  |  |  |  |  |

#### SIE D **3775612 0000135 0**

T-52-33-03

<u>ر</u> ا

.

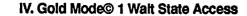

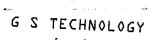

## MEMORY CYCLE TIMING DIAGRAM

. . .

#### I. Start Cycle of the Page Mode Operation

----

21E D 🔳 3775612 0000136 2

5

.

T-52-33-03

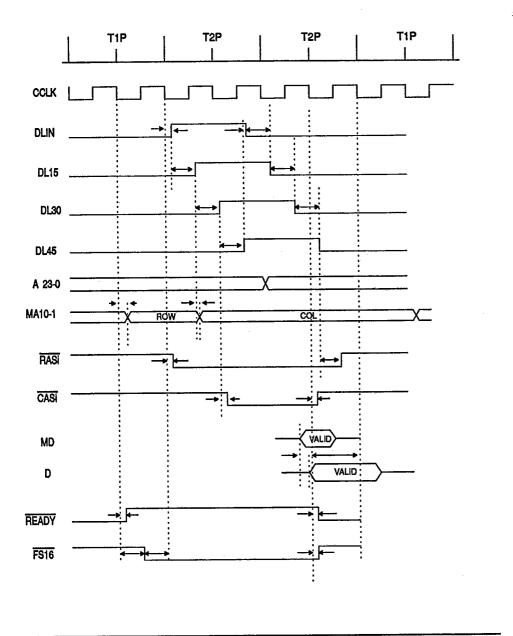

II. Off Page Access Cycle

21E D 🔳 3775612 0000137 4 🔜

T-52-33-03

.

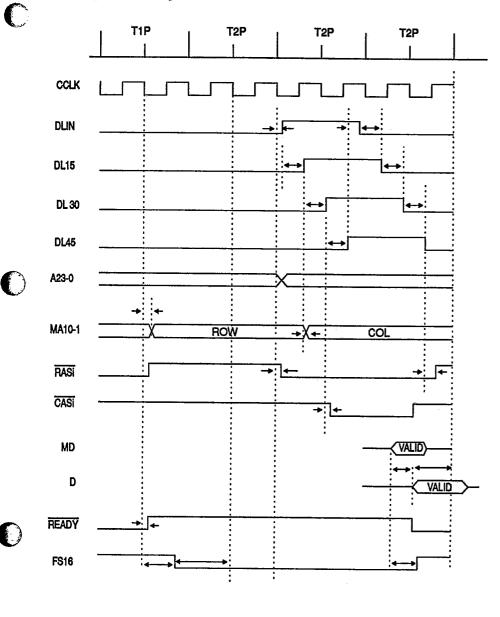

#### III. On Page Accesses

....

21E D 🔳 3775612 0000138 6 🛛

T-52-33-03

: 5

•