# **OKI** Semiconductor

This version: Nov. 1997 Previous version: Jul. 1996

## MSC7170-xx

5×7 Dot Character × 16-Digit × 2-Line Display Controller/Driver with Keyscan Function

#### **GENERAL DESCRIPTION**

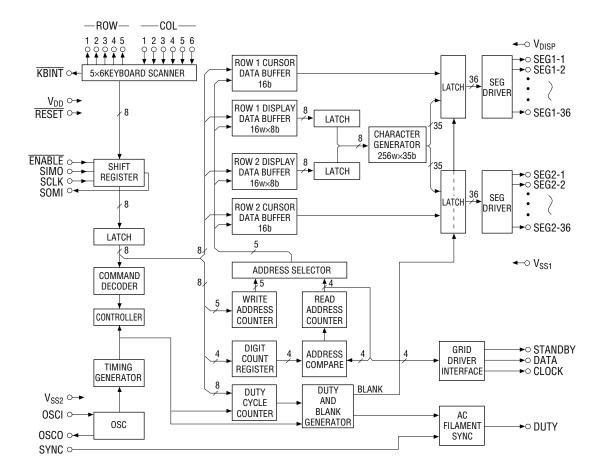

The MSC7170 is a display controller/segment driver containing a  $5 \times 6$  keyscan circuit, designed for a  $5 \times 7$  dot matrix type vacuum fluorescent (VF) display tube.

Use of the MSC1164/1165 grid driver allows a maximum of 16-digit pair to be displayed, or use of the MSC7171 grid driver allows a maximum of 12 digit pairs to be displayed.

#### **FEATURES**

- Able to display  $5 \times 7$  dot matrix type characters of a maximum of 16 digits  $\times$  2 lines (when MSC1164/1165 is used)

- The number of display digits selectable in a range of 1 digit  $\times$  2 lines to 16 digits  $\times$  2 lines

- Standby function

Combination of the MSC7171 grid driver and the MSC7170 decreases grid driver current during the standby mode of the driver.

- Display intensity selectable by 10-bit digital dimming

- Display characters selectable from among 256 types by internal PLA User programmable, mask option

- 8-bit synchronous serial data transfer SPI interface

- 5 × 6 keyscan circuit

- Driver output current (I<sub>OH)</sub> : 1 mA (SEG1 to SEG35) : –15 mA (SEG36)

- Supply voltage:  $V_{DD} = 5 V \pm 10\%$ :  $V_{DISP} = 60 V (max.)$

- Package:

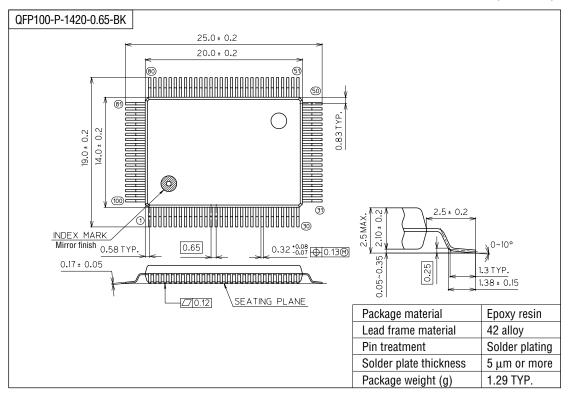

100-pin plastic QFP (QFP100-P-1420-0.65-BK) (Product name: MSC7170-xxGS-BK) xx indicates the code number.

#### **BLOCK DIAGRAM**

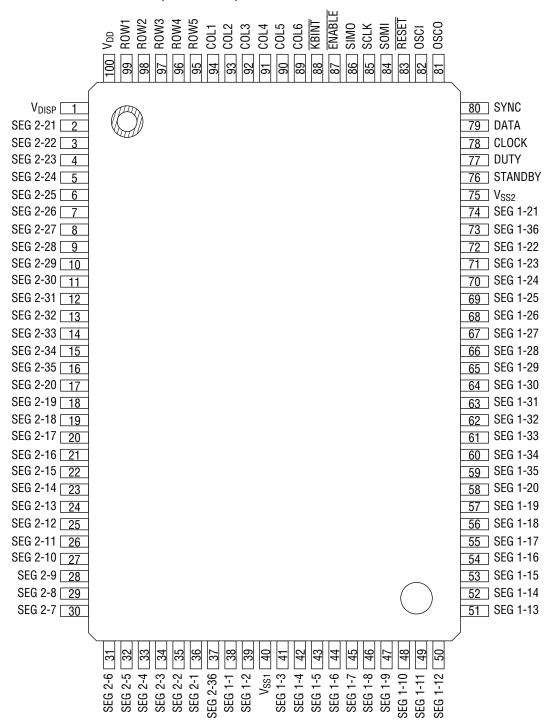

## PIN CONFIGURATION (TOP VIEW)

#### 100-Pin Plastic QFP

Note: SEGn-x sequence depends on ROM code content and may be altered by changing segment number x relationship to ROM bit number. See Correspondence between Segment Output and VF Display Tube Dots.

## **PIN DESCRIPTIONS**

| Pin   | Symbol               |                                                        | Description                                                                                                                                                                                                     |

|-------|----------------------|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | V <sub>DISP</sub>    | High voltage power suppl                               | у                                                                                                                                                                                                               |

| 2-36  | SEG2-1 to<br>SEG2-35 | VF tube 5×7 dot anode dr<br>the VF tube.               | iver outputs. These pins may be connected directly to                                                                                                                                                           |

| 37    | SEG2-36              | VF tube cursor driver out                              | put.                                                                                                                                                                                                            |

| 38-39 | SEG1-1<br>SEG1-2     | VF tube 5×7 dot anode dr<br>the VF tube.               | iver outputs. These pins may be connected directly to                                                                                                                                                           |

| 40    | V <sub>SS1</sub>     | High voltage ground                                    |                                                                                                                                                                                                                 |

| 41-72 | SEG1-3 to<br>SEG1-35 | VF tube 5×7 dot anode dr<br>the VF tube.               | iver outputs. These pins may be connected directly to                                                                                                                                                           |

| 73    | SEG1-36              | VF tube cursor driver out                              | put.                                                                                                                                                                                                            |

| 74    | SEG1-21              | VF tube 5×7 dot anode dr<br>the VF tube.               | iver output. This pin may be connected directly to                                                                                                                                                              |

| 75    | V <sub>SS2</sub>     | Logic supply ground.                                   |                                                                                                                                                                                                                 |

| 76    | STANDBY              | Grid driver standby outpu<br>driver (MSC7171) into a l | nt pin. A logic high level on this output forces the grid ow power standby mode.                                                                                                                                |

| 77    | DUTY                 | Duty cycle output pin.                                 |                                                                                                                                                                                                                 |

| 78    | CLOCK                | Grid driver clock output p                             | in.                                                                                                                                                                                                             |

| 79    | DATA                 | Grid driver data output pi                             | n.                                                                                                                                                                                                              |

| 80    | SYNC                 | AC filament synchronizati                              | on input pin.                                                                                                                                                                                                   |

| 81    | 0SC0                 | Oscillator output pin.                                 | Connects to crystal (or ceramic resonator) oscillator and                                                                                                                                                       |

| 82    | OSCI                 | Oscillator input pin.                                  | capacitor. These pins have internal feedback resistors.                                                                                                                                                         |

| 83    | RESET                | Reset input pin.                                       |                                                                                                                                                                                                                 |

| 84    | SOMI                 | SPI data output pin. Keys                              | can data is shifted out on the falling edge of SCLK.                                                                                                                                                            |

| 85    | SCLK                 | SPI clock input pin. Data                              | is shifted in on the SIMO pin on the rising edge of SCLK.                                                                                                                                                       |

| 86    | SIMO                 | SPI data input pin. Comm                               | nand data is shifted in on the rising edge of SCLK.                                                                                                                                                             |

| 87    | ENABLE               | logic low level is applied t                           | rface to the microprocessor is possible only when a to this pin. The SOMI output pin is tri-stated when level so that multiple devices may use the SPI network.                                                 |

| 88    | KBINT                | Keyscanning is started whof one cycle, KBINT goes      | o the microprocessor for keyscan data read out. hen any key is depressed or released. After completion to a logic low level to indicate new keyscan data is low until execution of Keyscan Data Output command. |

| 89-94 | COL6-1               |                                                        | om key switch matrix. A pull-up resistor is built in so that a state except when a key is depressed and a logic low                                                                                             |

| Pin   | Symbol   | Description                                                                                                                                                                                                                                                    |

|-------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 95-99 | ROW5-1   | Row 1-5 scanning signal output pins to key switch matrix. When any key is depressed or released, keyscanning is started and is continued until Keyscan Data Output command is executed. All Row 1-5 outputs go to logic low level when keyscanning is stopped. |

| 100   | $V_{DD}$ | Logic voltage supply.                                                                                                                                                                                                                                          |

### **ABSOLUTE MAXIMUM RATINGS**

| Parameter                  | Symbol            | Condition             | Rating                          | Unit |

|----------------------------|-------------------|-----------------------|---------------------------------|------|

| Logic Supply Voltage       | V <sub>DD</sub>   | _                     | -0.3 to 6.0 *1                  | V    |

| Driver Supply Voltage      | V <sub>DISP</sub> | _                     | -0.3 to 65 *1, 2                | V    |

| Input Voltage              | V <sub>IN</sub>   | Applies to all inputs | -0.3 to V <sub>DD</sub> +0.3 *1 | V    |

| Power Dissipation          | PD                | Ta≤25                 | 663                             | mW   |

| Package Thermal Resistance | R <sub>j-a</sub>  | \                     | 98 *3                           | °C/W |

|                            |                   | SEG1-1 to SEG1-35     | -2                              | mA   |

| Driver Output Current      | _                 | SEG2-1 to SEG2-35     | -2                              | mA   |

|                            |                   | SEG1-36, SEG2-36      | -15                             | mA   |

| Storage Temperature        | T <sub>STG</sub>  | _                     | -65 to 150                      | °C   |

- Notes: \*1 Voltage that can be applied to GND

- \*2 Stresses beyond the rating may cause permanent damage to the device.

- \*3 Package thermal resistance between junction and atomsphere. Junction temperature T<sub>i</sub> in the following expression must not exceed 150°C:  $T_j = P \times R_{j-a} + Ta$  (P: maximum IC power consumption)

#### RECOMMENDED OPERATING CONDITIONS

| Parameter                    | Symbol            | Condition                             | Range      | Unit |

|------------------------------|-------------------|---------------------------------------|------------|------|

| Logic Circuit Supply Voltage | $V_{DD}$          | Usable only for logic power terminal  | 4.5 to 5.5 | V    |

| Driver Supply Voltage        | V <sub>DISP</sub> | Usable only for driver power terminal | 7 to 60    | V    |

| Operating Temperature        | Top               | _                                     | -40 to 85  | °C   |

## **ELECTRICAL CHARACTERISTICS**

### **DC Characteristics**

(Ta=-40 to 85°C,  $V_{DD}$ =4.5 to 5.5 V,  $V_{DISP}$ =7 to 60 V)

| Parameter          | Symbol             | Condition                                                                                       | Min.                 | Max.                 | Unit | Applied Pin                                          |

|--------------------|--------------------|-------------------------------------------------------------------------------------------------|----------------------|----------------------|------|------------------------------------------------------|

| "H" Input Voltage  | V <sub>IH</sub>    | _                                                                                               | 0.7 V <sub>DD</sub>  | _                    | ٧    | All inputs                                           |

| "L" Input Voltage  | V <sub>IL</sub>    | _                                                                                               | _                    | 0.3 V <sub>DD</sub>  | ٧    | All inputs                                           |

| "H" Input Current  | I <sub>IH1</sub>   | V <sub>DD</sub> =5.5 V<br>V <sub>IN</sub> =V <sub>DD</sub>                                      | -1                   | 1                    | μА   | SIMO, SCLK, ENABLE,<br>RESET                         |

|                    | I <sub>IH2</sub>   | ין א ואיי א                                                                                     | -30                  | 30                   | μА   | COL1-6, SYNC                                         |

| "L" Input Current  | I <sub>IL1</sub>   | V <sub>DD</sub> =5.5 V<br>V <sub>IN</sub> =0.5 V                                                | -1                   | 1                    | μА   | SIMO, SCLK, ENABLE, RESET                            |

|                    | I <sub>IL2</sub>   | V   N = 0.5 V                                                                                   | -15                  | -160                 | μΑ   | COL1-6, SYNC                                         |

|                    | V <sub>OH1</sub>   | Ι <sub>ΟΗ</sub> =–500 μΑ                                                                        | V <sub>DD</sub> -0.6 | _                    | V    | 0SC0                                                 |

|                    | V <sub>OH2</sub>   | I <sub>OH</sub> =-1 mA                                                                          | V <sub>DISP</sub> -3 | _                    | V    | SEGn-1 to n-35, n=1, 2                               |

| "H" Output Voltage | V <sub>OH3</sub>   | I <sub>OH</sub> =–15 mA                                                                         | V <sub>DISP</sub> -4 | _                    | V    | SEG1-36, SEG2-36                                     |

|                    | V <sub>OH4</sub>   | I <sub>0H</sub> =–200 μA                                                                        | 4                    | _                    | V    | DUTY, SOMI, KBINT<br>DATA, CLOCK, STANDBY            |

|                    | V <sub>OL1</sub>   | I <sub>0L</sub> =500 μA                                                                         | _                    | V <sub>SS</sub> +0.6 | ٧    | 0SC0                                                 |

|                    | V <sub>OL2</sub>   | I <sub>0L</sub> =100 μA                                                                         | _                    | 2.5                  | V    | SEGn-1 to n-35, n=1, 2                               |

| "L" Output Voltage | V <sub>0L3</sub>   | I <sub>OL</sub> =3 mA                                                                           | _                    | 3                    | V    | SEG1-36, SEG2-36                                     |

| 2 output voltage   | V <sub>OL4</sub>   | I <sub>OL</sub> =200 μA                                                                         | _                    | 0.5                  | V    | ROW1-5, DUTY,<br>SOMI, KBINT,DATA,<br>CLOCK, STANDBY |

|                    | I <sub>DD1</sub>   | All SEGs on,<br>16-digit display,<br>maximum brightness,<br>no load,<br>f <sub>osc</sub> =4 MHz | _                    | 10                   | mA   | V <sub>DD</sub> -V <sub>SS</sub>                     |

| Power              | I <sub>DD2</sub>   | All SEGs off                                                                                    | _                    | 10                   | mA   |                                                      |

| Supply             | I <sub>DD3</sub>   | Low power mode                                                                                  | _                    | 25                   | μΑ   |                                                      |

|                    | I <sub>DISP1</sub> | All SEGs on,<br>16-digit display,<br>maximum brightness,<br>no load,<br>f <sub>osc</sub> =4 MHz | _                    | 15                   | mA   | V <sub>DISP</sub> -V <sub>SS</sub>                   |

|                    | I <sub>DISP2</sub> | All SEGs off                                                                                    | _                    | 1                    | μΑ   |                                                      |

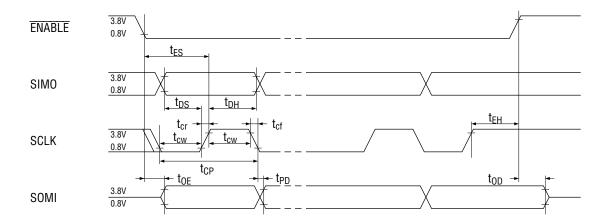

## AC Characteristics (1/2)

(Ta=-40 to 85°C,  $V_{DD}$ =4.5 to 5.5V,  $V_{DISP}$ =7 to 60 V,  $f_{OSC}$ =4 MHz, 12-digit display)

| Parameter             | Symbol                           | Condition                                                                                                           | Min.      | Тур. | Max. | Unit |

|-----------------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------|-----------|------|------|------|

| ENABLE Setup Time     | t <sub>ES</sub>                  | See Fig. 1 (Data Transfer Timing)                                                                                   | 50        | _    | _    | ns   |

| ENABLE Hold Time      | t <sub>EH</sub>                  | See Fig. 1 (Data Transfer Timing)                                                                                   | 4         | _    | _    | μS   |

| SCLK Frequency        | t <sub>CP</sub>                  | See Fig. 1 (Data Transfer Timing)                                                                                   | _         | 0.5  | 2    | MHz  |

| SCLK Pulse Width      | t <sub>cw</sub>                  | See Fig. 1 (Data Transfer Timing)                                                                                   | 250       | _    | _    | ns   |

| SCLK Rise/Fall Time   | t <sub>cr</sub> /t <sub>cf</sub> | See Fig. 1 (Data Transfer Timing)                                                                                   | _         | _    | 500  | ns   |

| SIMO Setup Time       | t <sub>DS</sub>                  | See Fig. 1 (Data Transfer Timing)                                                                                   | 50        | _    | _    | ns   |

| SIMO Hold Time        | t <sub>DH</sub>                  | See Fig. 1 (Data Transfer Timing)                                                                                   | 120       | _    | _    | ns   |

| SOMI Output Enable    | t <sub>OE</sub>                  | Enable to SOMI valid                                                                                                | _         | _    | 200  | ns   |

| SOMI Output Disable   | t <sub>OD</sub>                  | Enable to SOMI tri-state                                                                                            | _         | _    | 200  | ns   |

| SCLK to SOMI Delay    | t <sub>PD</sub>                  | See Fig. 1 (Data Transfer Timing)                                                                                   | _         | _    | 100  | ns   |

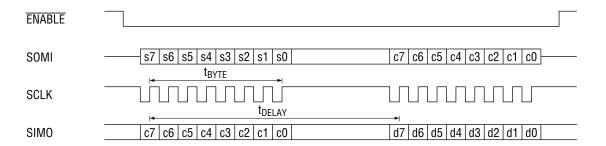

| Byte Length           | t <sub>BYTE</sub>                | MSB to LSB<br>See Fig. 2 (Example of Data Transfer)                                                                 | 3.5       | _    | _    | μS   |

| Byte Delay            | t <sub>DELAY</sub>               | MSB to LSB<br>See Fig. 2 (Example of Data Transfer)                                                                 | _         | _    | 20   | μS   |

| SYNC Frequency        | t <sub>SYNC</sub>                | Duty cycle=50%, f <sub>OSC</sub> -4 MHz<br>12-digit display                                                         | *1<br>0.4 | _    | 250  | kHz  |

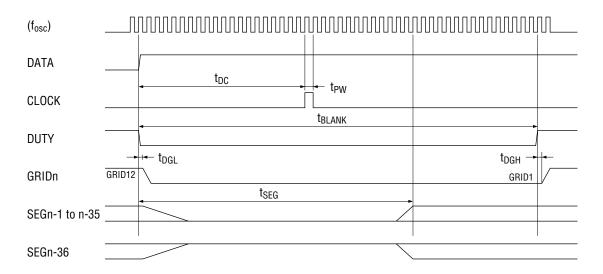

| SEGn Pulse Width      | t <sub>SEG</sub>                 | f <sub>OSC</sub> =4 MHz<br>See Fig. 5 (Duty Cycle Timing)<br>C <sub>I</sub> =20pF                                   | _         | 10   | _    | μs   |

| Operating Frequency   | tosc                             | Self-oscillation                                                                                                    | 1.5       | 4    | 4.5  | MHz  |

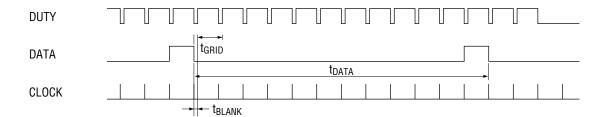

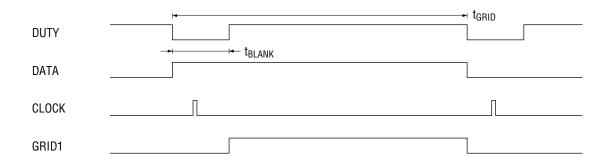

| DUTY Period           | t <sub>GRID</sub>                | f <sub>OSC</sub> =4 MHz,<br>See Fig. 3 (12-digit Display Cycle<br>Timing)                                           | _         | 256  | _    | μS   |

| Blank Interval (min.) | t <sub>BLANK</sub>               | f <sub>OSC</sub> =4 MHz<br>See Fig. 3 (12-digit Display Cycle<br>Timing)<br>t <sub>BLANK</sub> =48/f <sub>OSC</sub> | _         | 12   | _    | μs   |

| DATA Pulse Width High | t <sub>DW</sub>                  | f <sub>OSC</sub> =4 MHz<br>See Fig. 5 (Duty Cycle Timing)                                                           | _         | 256  | _    | μS   |

| DATA Period           | t <sub>DATA</sub>                | f <sub>OSC</sub> =4 MHz<br>See Fig. 3 (12-digit Display Cycle<br>Timing)                                            | _         | 3072 | _    | μS   |

| DATA to CLOCK Delay   | t <sub>DC</sub>                  | f <sub>OSC</sub> =4 MHz<br>See Fig. 5 (Duty Cycle Timing)                                                           | _         | 5    | _    | μS   |

| CLOCK Pulse Width     | t <sub>PW</sub>                  | f <sub>OSC</sub> =4 MHz<br>See Fig. 5 (Duty Cycle Timing)                                                           | _         | 250  | _    | μS   |

| CLOCK Cycle           | t <sub>CLOCK</sub>               | f <sub>OSC</sub> =4 MHz<br>See Fig. 5 (Duty Cycle Timing)                                                           | _         | 256  | _    | μS   |

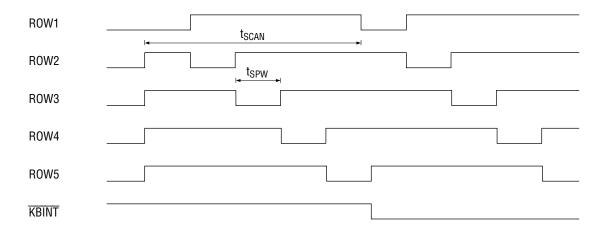

| Keyscan Cycle Time    | t <sub>SCAN</sub>                | f <sub>OSC</sub> =4 MHz<br>See Fig. 6 (Keyscan Timing)                                                              | _         | 40   | _    | μS   |

#### AC Characteristics (2/2)

(Ta=-40 to 85°C,  $V_{DD}$ =4.5 to 5.5 V,  $V_{DISP}$ =7 to 60 V,  $f_{OSC}$ =4 MHz, 12-digit display)

| Parameter                      | Symbol                         | Cond                                                                                                | lition                 | Min. | Тур. | Мах. | Unit |

|--------------------------------|--------------------------------|-----------------------------------------------------------------------------------------------------|------------------------|------|------|------|------|

| Keyscan Pulse Width            | t <sub>SPW</sub>               | f <sub>OSC</sub> =4 MHz,<br>See Fig. 6 (Keyscan Timing)                                             |                        |      | 8    | _    | μS   |

| Waka un Tima                   | t                              | Keypress to<br>KBINT at "L" level                                                                   | Ceramic resonator      | _    | _    | 5    |      |

| Wake-up Time                   | twake                          | f <sub>OSC</sub> =4 MHz                                                                             | Crystal                | _    | _    | 10   | ms   |

| Claur Data (CECn 1 to CECn 25) | t <sub>r</sub>                 | $C_L$ =20 pF, $V_{DISP}$ =60 V, $V_{OL}$ =6 V, $V_{OH}$ =50 V                                       |                        |      | 1.3  | 5    | μs   |

| Slew Rate (SEGn-1 to SEGn-35)  | t <sub>f</sub>                 |                                                                                                     |                        |      | 3.4  | 5    | μs   |

| Class Data (CEC = OC)          | t <sub>r</sub>                 | C <sub>L</sub> =20 pF, V                                                                            | <sub>DISP</sub> =60 V, | 0.2  | _    | 5    | μs   |

| Slew Rate (SEGn-36)            | t <sub>f</sub>                 | $V_{OL}=6$ V, $V_{OH}=50$ V                                                                         |                        |      | _    | 5    | μs   |

| Slew Rate (DUTY, DATA, CLOCK)  | t <sub>r</sub> /t <sub>f</sub> | V <sub>OL</sub> =0.1 V <sub>DD</sub> , V <sub>OH</sub> =0.9 V <sub>DD</sub> , C <sub>L</sub> =10 pF |                        |      | 20   | 200  | ns   |

| Input Capacitance              | Cı                             | all p                                                                                               | ins                    |      | 6    | _    | pF   |

<sup>\*1)</sup> For the minimum value when digits other than 12 digits are displayed, refer to the following expression.

$t_{SYNC (Min)} > \frac{f_{OSC}}{1024 \times (digit display number)}$

#### **TIMING DIAGRAM**

Figure 1. Data Transfer Timing

Figure 2. Data Transfer Example

Figure 3. 12-Digit (n=12) Display Cycle Timing

Figure 4. GRID1 Interval Timing

Note:  $(f_{OSC})$  is internal to the MSC7170 and not visible externally. GRIDn are outputs of, and  $t_{DGL}$  and  $t_{DGH}$  are timig parameters of, the MSC7171 (grid driver).

Figure 5. Duty Cycle Timing

Figure 6. Keyscan Timing

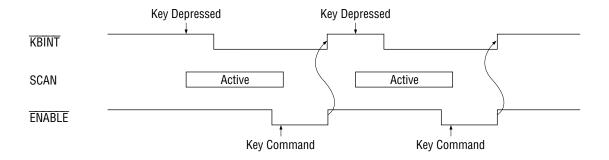

Figure 7-1. Single Keypress/Single Read

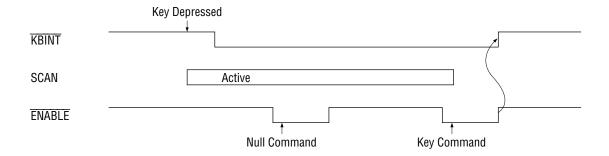

Figure 7-2. Single Keypress/Multiple Read

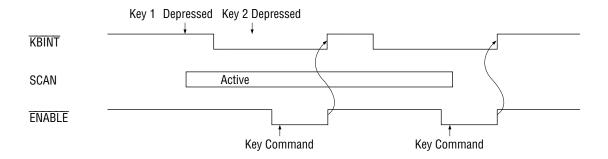

Figure 7-3. Multiple Keypress/Multiple Interrupt

Figure 7. Typical Cases of Keyscan Operation

#### **FUNCTIONAL DESCRIPTION**

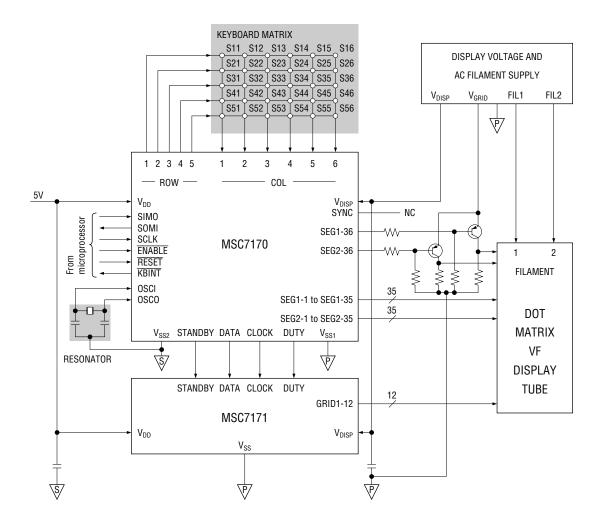

The MSC7170 (Dot Matrix VF Segment Driver) in conjunction with the MSC7171 (Dot Matrix VF Grid Driver) is capable of controlling a variety of dot matrix VF displays and keyboards. The MSC7170 is designed to drive the anodes of up to 32 dot matrix digits in two lines. Each digit is a  $5 \times 7$  matrix of anodes, or dots, which requires a total of 70 segment driver outputs. There are two extra segment outputs for supplying drive to dedicated annunciators. The grid drivers of the MSC7171 are controlled by the MSC7170 through a two-line serial interface and a duty cycle control line, DUTY (see APPLICATION CIRCUIT). Additionally, the MSC7170 provides 10-bit digital dimming of all display data, a  $5 \times 6$  keyscan function allowing control of up to 30 key pads and a low-power standby mode. The MSC7170 is controlled through a standard SPI interface.

All MSC7170 internal timings are generated through an external 4 MHz (typ) ceramic oscillator. One display cycle is defined as up to 16384 periods of the 4 MHz (250 ns) reference in increments of 1024 periods, one for each pair of digits displayed. Display intensity is determined by the duty cycle of the DUTY output within one display increment divided by the total number of increments, or character pairs, displayed (see Display Duty Cycle Set and Number of Display Digit Pairs Set commands below). The maximum duty cycle is defined as 976 out of 1024 increments or 95.3 percent.

The MSC7170 is capable of synchronizing the DUTY signal with an AC filament to avoid visible flicker during dimming conditions. This is required in VF tubes of greater than 100 mm, equivalent to 14 digits, in length. Synchronization is accomplished by alternately initiating display cycles coincident with rising and falling edges of the filament voltage. Upon completion of a rising/falling edge display cycle, the MSC7170 will wait for a falling/rising edge before initiating the next display cycle. The MSC7170 detects rising and falling edges of a CMOS-compatible SYNC input derived directly from the filament voltage. The amount of hold time between display cycles varies between no delay as a minimum and the period of the filament voltage as maximum. The amount of delay should be consistent for all display cycles assuming that the filament frequency is well defined.

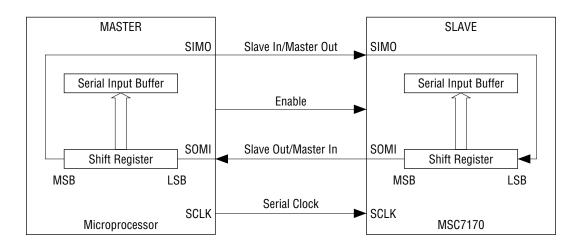

The MSC7170 is controlled through a Serial Peripheral Interface (SPI) compatible communications port. The SPI is a high-speed synchronous serial I/O port that shifts a serial bit stream of eight data bits into or out of a device at a bit transfer rate programmed in a controlling device. The figure below shows a typical connection of the SPI for communications between a master (radio microprocessor) and slave (MSC7170). Three I/O pins are associated with the SPI interface — SPI slave-in master-out (SIMO), SPI slave-out master-in (SOMI), and SPI serial clock (SCLK). Additionally, a separate input pin is used to enable the MSC7170 to communicate with the microprocessor through this interface.

**SPI Master/Slave Connection**

The microprocessor provides the serial clock (500 kHz typ.) to all devices on the SPI network with a CLOCK POLARITY of 1 (inactive level is high). Data is transferred from the master (microprocessor) to the salve (MSC7170) over the SIMO line, while data is transferred from the slave to the master over the SOMI line. Data is clocked out of the transmitting device on the falling edge of SCLK and latched into the receiving device with the rising edge of SCLK. ALL data transmissions are made MSB (b7) first.

A typical data transfer cycle between the microprocessor and the MSC7170 is initiated by first bringing the  $\overline{ENABLE}$  line low. The first byte transmitted defines the command or operation to be executed. All remaining bytes received, prior to  $\overline{ENABLE}$  being returned high, are treated as data bytes for that operation. Each command or operation executed requires a separate  $\overline{ENABLE}$  transfer cycle.

The maximum waiting period between byte transfers, measured from MSB to LSB, is 20 msec. All activity on the SCLK and SIMO pins while  $\overline{\text{ENABLE}}$  is high is ignored. Additionally, the SOMI pin shall be in a tri-state condition when  $\overline{\text{ENABLE}}$  is high so that other SPI devices on the network may drive the line without contention.

The MSC7170 controls up to 30 key pads via a 5 controls up to 30 key pads via a  $5\times6$  key scan circuit. COL1 to 6 (inputs) and ROW1 to 5 (outputs) are connected to an external switch matrix with an impedance of  $500\Omega$  max. The ROW1 to 5 outputs start scanning only when a depression or release of any key is detected. Upon completion of the first keyscan cycle, see Figure 6, the keyboard interrupt,  $\overline{KBINT}$ , output is pulled low to indicate availability of new keyscan data. The keyscan circuit continues to scan and  $\overline{KBINT}$  remains low until the keyscan data has been read using the Keyscan Data Output Command. In the event of a multiple key depression, a second interrupt will be generated following the clearing of the first interrupt. A stuck key switch will not generate multiple interrupts since only state transitions are detected by the keyscan circuitry.

Keyscan data may be read without stopping the keyscan by using the Null Command. The keyscan data is transmitted to the microprocessor by rows as shown in the Output Data Bytes section. The output of keyscan data wraps around to the first byte for SPI transactions of more than six bytes. After completion of the last keyscan cycle all ROW outputs go to low level.

Key switch data is latched internally for transfer to the microprocessor via the SPI port. The microprocessor may use KBINT as an interrupt request or for polling the MSC7170 to determine when new keyscan information is available. As an alternative for polling, the MSC7170 continuously outputs a status byte during any SPI transaction, with the exceptions of the Null Command and the Keyscan Data Output Command. An all zeros (00h) byte indicates the presence of new keyscan information while all ones (FFh) indicate no new keyscan information. For the Null and Keyscan Data Output commands, the first byte output is still the status byte followed by five bytes containing the data from the five keyscan rows as described above and in the Output Data Bytes section. The status byte is reset upon completion of a Keyscan Data Output command in the same fashion as KBINT.

The MSC7170 can also be commanded into a low power or "standby" mode (see Mode Set command). In this mode all operation, including the internal oscillator, of the MSC7170 ceases. The only exception is the key scan detection circuitry which, on any key pad activity (depress or release), will cause the MSC7170 to return to normal operation. The MSC7170 will be fully operational within 10 msec (max) after return to normal operation. The wake-up cycle includes a full scan of the key matrix.  $\overline{\text{KBINT}}$  will be pulled low to indicate full wake-up. Normal operation is also resumed when the  $\overline{\text{ENABLE}}$  line is taken low. In this case, a scan of the key matrix is not executed, nor is the  $\overline{\text{KBINT}}$  line pulled low to indicate full wake-up.

The RESET and ENABLE lines shall be maintained at logic high levels during standby operation. All segment outputs go to a high impedance state while in standby mode. The SPI interface lines (SLCK, SIMO, and SOMI) will not interfere with the operation of the SPI network when the standby mode is properly selected. To ensure correct operation of the SPI network, the standby mode of the MSC7170 should always be selected before the logic supply is switched off.

The following sequence of events should be followed to enter standby mode:

- 1) Set duty cycle to zero percent

- 2) Turn off high voltage  $(V_{DISP})$

- 3) Send low power (standby) "on" command

Following wake-up, the high voltage should be turned on prior to setting a duty cycle greater than zero percent.

The MSC7170 may be commanded into Blank and Lamp Test modes. For Blank mode, the DUTY and SEGn-1 to SEGn-35 outputs remain at a continuous low level while the SEGn36 outputs assume a high level. The outputs remain at this level until the command is deselected. For Lamp Test mode, the DUTY output assumes a maximum duty cycle condition and the SEGn outputs are all forced to the on condition regardless of input data.

The MSC7170 accepts a reset signal from the microprocessor or other controller. There shall be no internal pull-up resistor on this signal. The state of the MSC7170 following a reset is as follows:

- a) All segment driver outputs are low

- b) The number of display digits is  $16 \times 2$ .

- c) The display duty cycle is set to 0

- d) Display Data Buffers are not cleared

- e) SPI registers are reset

- f) Keyscan registers are reset

The MSC7170 is protected against thermal overload or other failure caused by extreme display configurations (e.g. Lamp Test) or due to output short circuits to high voltage supply, ground, or another output. These shall be no performance degradation once the short circuit is removed.

## **Commands Description**

| No. | Instruction              | Byte | с7    | с6    | с5    | c4    | сЗ    | c2    | с1   | с0   |

|-----|--------------------------|------|-------|-------|-------|-------|-------|-------|------|------|

| 0   | Address Setup            | 1    | 1     | 0     | 0     | 0     | Χ     | Χ     | Χ    | Х    |

|     | Address Setup            | 2    | Χ     | Χ     | Χ     | a4    | a3    | a2    | a1   | a0   |

| 1   | Character Code Setup     | 1    | 1     | 0     | 0     | 1     | Χ     | Χ     | Χ    | Χ    |

| ı   | Character Code Setup     | 2    | b7    | b6    | b5    | b4    | b3    | b2    | b1   | b0   |

| 2   | Dienlay Duty Cycle Setup | 1    | 1     | 0     | 1     | 0     | Χ     | Χ     | DC9  | DC8  |

|     | Display Duty Cycle Setup | 2    | DC7   | DC6   | DC5   | DC4   | DC3   | DC2   | DC1  | DC0  |

| 3   | Display Digits Setup     | 1    | 1     | 0     | 1     | 1     | n3    | n2    | n1   | n0   |

| 4   | Mode Setup               | 1    | 1     | 1     | 0     | 0     | Χ     | m2    | m1   | m0   |

|     |                          | 1    | 1     | 1     | 0     | 1     | Χ     | Χ     | Χ    | Χ    |

|     |                          | 2    | C1-7  | C1-6  | C1-5  | C1-4  | C1-3  | C1-2  | C1-1 | C1-0 |

| 5   | Cursor Setup             | 3    | C1-15 | C1-14 | C1-13 | C1-12 | C1-11 | C1-10 | C1-9 | C1-8 |

|     |                          | 4    | C2-7  | C2-6  | C2-5  | C2-4  | C2-3  | C2-2  | C2-1 | C2-0 |

|     |                          | 5    | C2-15 | C2-14 | C2-13 | C2-12 | C2-11 | C2-10 | C2-9 | C2-8 |

| 6   | Keyscan Data Output      | 1    | 1     | 1     | 1     | 0     | Χ     | Χ     | Χ    | Χ    |

| 7   | Null                     | 1    | 0     | 0     | 0     | 0     | 0     | 0     | 0    | 0    |

#### **Address Setup Command**

This command is used to setup a start position of display character code writing and must be executed before the desired character code is sent. In applications using less than the full 16-digit pair capability, only the first 2n memory locations are used. For example, if n=12-digit pair is selected, only addresses 0 through 23 are used. Row 1 display data (SEG1 outputs) is stored in addresses 0 through 11 while Row 2 display data (SEG2 outputs) is stored in addresses 12 through 23. All bytes following Bytes 1 and 2 are treated as character code data bytes. Address 0 is set after reset.

|      |   | с7 | с6 | с5 | с4 | сЗ | c2 | c1 | c0 |

|------|---|----|----|----|----|----|----|----|----|

| Byte | 1 | 1  | 0  | 0  | 0  | Χ  | Χ  | Χ  | Χ  |

|        | d7 | d6 | d5 | d4 | d3 | d2 | d1 | d0 |

|--------|----|----|----|----|----|----|----|----|

| Byte 2 | Χ  | Χ  | Χ  | a4 | a3 | a2 | a1 | a0 |

a4 to a0 : 00000=00h=0 : 11111=1Fh=31

#### **Character Code Setup Command**

This command is used to specify the character to be displayed in the display location previously specified by the Address Setup command. A built-in automatic address increment function simplifies writing more than one display character code. All bytes transmitted after Byte 2 are treated as character code data for successive locations. The internal address counter will be automatically incremented from the address set using the Address Set command through address 31 (or character 32), while executing valid write cycles, regardless of the number of digit pairs as defined using the Number of Display Digits Setup command. In the event that additional data is input to the MSC7170 following a valid write to address 31, the address counter will wraparound and continue to increment (to address 0 etc.) with write cycles disabled. This prevents overwriting of the memory.

|        | с7 |   |   |   |   |   |   |   |

|--------|----|---|---|---|---|---|---|---|

| Byte 1 | 1  | 0 | 0 | 1 | Χ | Χ | Χ | Χ |

|        |    |   |   |   |   |   |   |   |

|        |    |   |   |   |   |   |   |   |

|        | d7 | d6 | d5 | d4 | d3 | d2 | d1 | d0 |

|--------|----|----|----|----|----|----|----|----|

| Byte 2 | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

b4 to b0 : 8-bit character code — Select one of 256 codes

#### **Display Duty Cycle Setup Command**

This command is used to set the duty cycle of the display. The time allocated to a 1-digit display is 1024T, where T is the period of the internal oscillator ( $f_{OSC}$ ). The display time for each digit may be specified as 0 to 976T in increment of T. Entries greater than 976 default to 976. The display duty cycle is calculated by dividing the input duty cycle value, DC, by 1024 times the number of digits, n, commanded to display. Note that the percent duty cycle depends on how many digits (characters) are displayed.

|        | с7 | с6 | с5 | с4 | сЗ | c2 | c1  | с0  |

|--------|----|----|----|----|----|----|-----|-----|

| Byte 1 | 1  | 0  | 1  | 0  | Χ  | Χ  | DC9 | DC8 |

|        | d7  | d6  | d5  | d4  | d3  | d2  | d1  | d0  |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|

| Byte 2 | DC7 | DC6 | DC5 | DC4 | DC3 | DC2 | DC1 | DC0 |

#### **Number of Display Digits Setup Command**

This command is used to set the number of digits to be displayed. The number of digits selectable ranges from 1 to 16.

|        | с7 | с6 | с5 | с4 | сЗ | c2 | с1 | 00 |

|--------|----|----|----|----|----|----|----|----|

| Byte 1 | 1  | 0  | 1  | 1  | n3 | n2 | n1 | n0 |

n3 to n0 : 0000=0h=16-digit pair

: 0001=1h=1-digit pair

:

: 1111=Fh=15-digit pair

#### **Mode Setup Command**

This command is used to select an operation mode for the MSC7170. Lamp Test and Blank modes turns all 36 segments of each displayable digit (as set by the Number of Display Digits Setup command) to the ON and OFF states respectively. The contents of the display buffer are not affected by either of these modes. The normal operation mode returns after reset. Low Power mode is described earlier.

|        | с7 | с6 | с5 | с4 | сЗ | c2 | c1 | c0 |

|--------|----|----|----|----|----|----|----|----|

| Byte 1 | 1  | 1  | 0  | 0  | Χ  | m2 | m1 | m0 |

| <u>m2</u> | <u>m1</u> | <u>m0</u> | Mode                       |

|-----------|-----------|-----------|----------------------------|

| 0         | 0         | 0         | Normal operation           |

| 0         | 0         | 1         | Lamp test (All display ON) |

| 0         | 1         | 0         | Low power                  |

| 0         | 1         | 1         | Normal operation           |

| 1         | 0         | 0         | Blank (All display OFF)    |

| 1         | 0         | 1         | Normal operation           |

| 1         | 1         | 0         | Normal operation           |

| 1         | 1         | 1         | Normal operation           |

#### **Cursor Setup Command**

This command is used to specify the on/off state of cursor segments (SEGn-36) in the display. The cursor outputs are issued inversely to allow an external PNP transistor to be used in applications requiring high current drive capability. Therefore, a logic high, l, in a given bit position will turn on the associated cursor. In applications requiring low current (less than 15 mA) drive capability, the cursor outputs may drive the VF display tube directly. In these applications, setting to "0" turns on the cursor.

|        | с7 | с6 | с5 | с4 | сЗ | c2 | с1 | с0 |

|--------|----|----|----|----|----|----|----|----|

| Byte 1 | 1  | 1  | 0  | 1  | Χ  | Χ  | Χ  | Χ  |

|        | d7    | d6    | d5    | d4    | d3    | d2    | d1   | d0   |

|--------|-------|-------|-------|-------|-------|-------|------|------|

| Byte 2 | C1-7  | C1-6  | C1-5  | C1-4  | C1-3  | C1-2  | C1-1 | C1-0 |

| Byte 3 | C1-15 | C1-14 | C1-13 | C1-12 | C1-11 | C1-10 | C1-9 | C1-8 |

| Byte 4 | C2-7  | C2-6  | C2-5  | C2-4  | C2-3  | C2-2  | C2-1 | C2-0 |

| Byte 5 | C2-15 | C2-14 | C2-13 | C2-12 | C2-11 | C2-10 | C2-9 | C2-8 |

#### **Keyscan Data Output Command**

This command is used to read keyscan data via the SPI interface and has no effect on the operation or state of the display portion of the MSC7170. Upon completion of this command the  $\overline{\text{KBINT}}$  output is reset to its non-active state and the keyscan function is stopped. All bytes after Byte 1 are ignored.

|        | с7 | с6 | с5 | с4 | сЗ | c2 | с1 | с0 |

|--------|----|----|----|----|----|----|----|----|

| Byte 1 | 1  | 1  | 1  | 0  | Χ  | Χ  | Χ  | Χ  |

#### **NULL Command**

This command has the same function as the Keyscan Data Output command with the exception that KBINT is not reset and the keyscan function continues to scan the key matrix. The keyscan may stop momentarily to prevent changing data while data output is in progress. All bytes after Byte 1 are ignored.

|        | с7 | с6 | с5 | с4 | сЗ | c2 | с1 | с0 |

|--------|----|----|----|----|----|----|----|----|

| Byte 1 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

#### **Output Data Byte Description**

#### Status output

The following byte is output from the MSC7170 during execution of every SPI command with the exceptions of the Keyscan Data Output and Null commands. The status byte is issued for each byte of the input command sequence.

|        | d7 | d6 | d5 | d4 | d3 | d2 | d1 | d0 |        |

|--------|----|----|----|----|----|----|----|----|--------|

| Byte 1 | s7 | s6 | s5 | s4 | s3 | s2 | s1 | s0 | Status |

s7 to s0: indicates change status from last SPI transaction 00h = change, FFh = no change

#### • Keyscan data output

The following bytes are output from the MSC7170 during execution of the Keyscan Data Output and Null commands. The output of keyscan data wraps around to byte 1 for transactions of more than six bytes.

|        | d7 | d6 | d5  | d4  | d3  | d2  | d1  | d0  |

|--------|----|----|-----|-----|-----|-----|-----|-----|

| Byte 1 | Х  | Х  | s16 | s15 | s14 | s13 | s12 | s11 |

| Byte 2 | Χ  | Χ  | s26 | s25 | s24 | s23 | s22 | s21 |

| Byte 3 | Χ  | Χ  | s36 | s35 | s34 | s33 | s32 | s31 |

| Byte 4 | Х  | Χ  | s46 | s45 | s44 | s43 | s42 | s41 |

| Byte 5 | Χ  | Χ  | s56 | s55 | s54 | s53 | s52 | s51 |

Row 1 Row 2 Row 3 Row 4 Row 5

sij : i=ROW1 to 5, j =Col1 to 6

sij=1: Switch on sij=0: Switch off

## **Character Codes and Character Patterns (for ROM Code 01: Standard)**

|           |   | MSB: | D7 - D      | 4            |          |    | T    |          |             | ı         | T     | T    | ı   |   | T    |          | ı          |

|-----------|---|------|-------------|--------------|----------|----|------|----------|-------------|-----------|-------|------|-----|---|------|----------|------------|

|           |   | 0    | 1           | 2            | 3        | 4  | 5    | 6        | 7           | 8         | 9     | Α    | В   | С | D    | E        | F          |

| : D3 - D0 | 0 | H    |             |              |          |    |      |          | <b> </b>    | ::::.     | ::::  |      |     |   |      | ==       | <b></b>    |

| LSB:      | 1 |      |             | :            |          |    |      |          | <u></u>     | •.<br>••. | ====  | -::: |     |   |      |          |            |

|           | 2 |      |             |              |          |    |      |          | <b>!-"</b>  |           |       |      |     |   |      |          | <b>!-"</b> |

|           | 3 |      |             |              |          |    | ==== | :        | -:::        |           |       |      |     |   | ==== | <b>:</b> |            |

|           | 4 |      | .· <b>·</b> | <b>:</b> ::: |          |    |      |          | •           |           | ::    |      |     |   |      |          | #          |

|           | 5 |      |             |              |          |    |      |          |             | •-        |       | ."   |     |   |      |          |            |

|           | 6 |      |             |              |          |    |      |          | <b>!!</b>   | :         | <br>  | -    |     |   |      |          | <b>.</b>   |

|           | 7 |      |             | <b>:</b>     |          |    |      |          |             | :::::     | ::    |      |     |   |      |          |            |

|           | 8 |      |             | <b>!</b>     |          |    |      | <b>!</b> | <u>;:::</u> |           |       |      |     |   |      |          |            |

|           | 9 |      |             |              |          |    | ==   |          | •           | •.<br>••  | <br>  |      | :   |   | ==   |          |            |

|           | Α |      |             |              | ##<br>## | ·i |      |          |             | <br>      |       |      |     | ! |      |          |            |

|           | В | -==  |             |              | ::       |    |      |          | •           |           | ===== |      | === |   |      |          | •          |

|           | С |      |             | ij.          | •        |    | •••• |          |             |           | -:::- | -=   |     |   |      |          |            |

|           | D |      |             |              |          |    |      |          | •           |           |       |      |     |   |      |          |            |

|           | E |      |             | ##           | •        |    |      | <br>!    |             | -         | ::    |      | :-  |   | .**. |          |            |

|           | F |      |             |              | •***     |    |      |          |             |           |       |      |     |   | :    |          |            |

Note: These character patterns are user programmable and can be selected by mask option.

## **Correspondence between Segment Outputs and VF Display Tube Dots**

| VF Dot: | 1-1     | 2-1     | 3-1     | 4-1     | 5-1     |

|---------|---------|---------|---------|---------|---------|

| IC Pin: | SEGn-1  | SEGn-2  | SEGn-3  | SEGn-4  | SEGn-5  |

| VF Dot: | 1-2     | 2-2     | 3-2     | 4-2     | 5-2     |

| IC Pin: | SEGn-6  | SEGn-7  | SEGn-8  | SEGn-9  | SEGn-10 |

| VF Dot: | 1-3     | 2-3     | 3-3     | 4-3     | 5-3     |

| IC Pin: | SEGn-11 | SEGn-12 | SEGn-13 | SEGn-14 | SEGn-15 |

| VF Dot: | 1-4     | 2-4     | 3-4     | 4-4     | 5-4     |

|         | SEGn-16 | SEGn-17 | SEGn-18 | SEGn-19 | SEGn-20 |

| VF Dot: | 1-5     | 2-5     | 3-5     | 4-5     | 5-5     |

|         | SEGn-21 | SEGn-22 | SEGn-23 | SEGn-24 | SEGn-25 |

| VF Dot: | 1-6     | 2-6     | 3-6     | 4-6     | 5-6     |

|         | SEGn-26 | SEGn-27 | SEGn-28 | SEGn-29 | SEGn-30 |

| VF Dot: | 1-7     | 2-7     | 3-7     | 4-7     | 5-7     |

|         | SEGn-31 | SEGn-32 | SEGn-33 | SEGn-34 | SEGn-35 |

### **APPLICATION CIRCUIT**

### **PACKAGE DIMENSIONS**

(Unit: mm)

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, SOJ, QFJ (PLCC), SHP and BGA are surface mount type packages, which are very susceptible to heat in reflow mounting and humidity absorbed in storage.

Therefore, before you perform reflow mounting, contact Oki's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).