# 75 $\Omega$ Digital Attenuator, 6-Bit, Serial / Parallel Control 31.5 dB, 0.005 - 1.0 GHz

Rev.V1

#### **Features**

- 75 Ω Impedance

- Integrated TTL/CMOS Compatible Driver

- Parallel & Serial (P/S) Control with power-up state selection

- 0.5-dB Attenuation Steps to 31.5 dB

- Low DC Power Consumption

- Lead-Free 4mm PQFN-24LD Plastic Package

- Halogen-Free "Green" Mold Compound

- RoHS\* Compliant and 260°C Re-flow Compatible

#### Description

The MAAD-008866 is a 6-bit, 0.5-dB step GaAs digital attenuator in a lead-free 4mm PQFN-24LD surface mount plastic package. The MAAD-008866 is ideally suited for use where high accuracy, very low power consumption and low intermodulation products are required. This part can be used in all 75  $\Omega$  systems operating up to 1 GHz.

### Ordering Information <sup>1,2</sup>

| Part Number        | Package         |

|--------------------|-----------------|

| MAAD-008866-TR3000 | 3000 piece reel |

| MAAD-008866-001SMB | Sample Board    |

- 1. Reference Application Note M513 for reel size information.

- 2. All sample boards include 5 loose parts.

# **Absolute Maximum Ratings** <sup>3,4</sup>

| Parameter                         | Absolute Maximum                                    |

|-----------------------------------|-----------------------------------------------------|

| Input Power<br>50 MHz<br>1000 MHz | +15 dBm<br>+27 dBm                                  |

| Operating Voltage                 | +8.5 V                                              |

| Control Voltage                   | -0.5 V <u>&lt;</u> V <sub>C</sub> <u>&lt;</u> 5.5 V |

| Operating Temperature             | -40°C to +85°C                                      |

| Storage Temperature               | -65°C to +150°C                                     |

- 3. Exceeding any one or combination of these limits may cause permanent damage to this device.

- 4. M/A-COM Technology Solutions does not recommend sustained operation near these survivability limits.

# Functional Schematic 5

5. Blocking capacitors are required on all RF ports

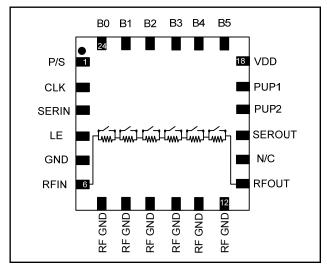

## **Pin Configuration**

| <b>-</b> |                             |                     |                  |

|----------|-----------------------------|---------------------|------------------|

| Pin No.  | Function                    | Pin No.             | Function         |

| 1        | Parallel / Serial<br>Select | 13                  | RF Output        |

| 2        | Clock                       | 14                  | No Connect       |

| 3        | Serial Data In              | 15                  | Serial Data Out  |

| 4        | Latch Enable                | 16                  | Power Up State 2 |

| 5        | GND                         | 17                  | Power Up State 1 |

| 6        | RF Input                    | 18                  | Bias Voltage     |

| 7        | RF GND                      | 19                  | B5               |

| 8        | RF GND                      | 20                  | B4               |

| 9        | RF GND                      | 21                  | В3               |

| 10       | RF GND                      | ) 22 B2             |                  |

| 11       | RF GND                      | 23 B1               |                  |

| 12       | RF GND                      | 24                  | B0               |

| 25       |                             | Paddle <sup>6</sup> |                  |

<sup>6.</sup> The exposed pad centered on the package bottom must be connected to the RF and DC ground.

<sup>\*</sup> Restrictions on Hazardous Substances, European Union Directive 2002/95/EC.

North America Tel: 800.366.2266 • Europe Tel: +353.21.244.6400 India Tel: +91.80.43537383 • China Tel: +86.21.2407.1588

India Tel: +91.80.43537383

China Tel: +86.21.2407.1588

Visit www.macomtech.com for additional data sheets and product information.

# 75 Ω Digital Attenuator, 6-Bit, Serial / Parallel Control 31.5 dB, 0.005 - 1.0 GHz

Rev.V1

# Electrical Specifications $^{7,8}$ : T<sub>A</sub> = 25°C, Z<sub>0</sub> = 75 $\Omega$ , V<sub>DD</sub> = 5 V, V<sub>C</sub> = 5 V

| Parameter                    | Test Conditions                                          | Units     | Min.             | Тур.                      | Max.            |

|------------------------------|----------------------------------------------------------|-----------|------------------|---------------------------|-----------------|

| Reference Insertion Loss     | 5 MHz<br>50 MHz<br>500 MHz<br>1000 MHz                   | dB        | _<br>_<br>_<br>_ | 1.3<br>1.35<br>1.6<br>1.8 | <br><br><br>2.3 |

| Attenuation Accuracy         | Any Bit or combination<br>5 - 1000 MHz                   | ± (0.15 d | B + 4% of a      | ttenuation se             | etting in dB)   |

| Return Loss                  | 5 - 1000 MHz                                             | dB        | _                | 18                        | _               |

| Trise, Tfall                 | 10% to 90% RF, 90% to 10% RF                             | ns        | _                | 320                       | _               |

| Ton, Toff                    | 50% Control to 90 / 10% RF                               | ns        | _                | 340                       | _               |

| Transients                   | In Band                                                  | mV        | _                | 88                        | _               |

| Input P1dB                   | 50 MHz<br>1000 MHz                                       | dBm       | _                | 12<br>25.6                |                 |

| IIP3                         | 0 dBm/tone at Input, 6 MHz Spacing<br>50 MHz<br>1000 MHz | dBm       | _                | 33<br>43                  | _               |

| IIP2                         | 0 dBm/tone at Input, 6 MHz Spacing<br>50 MHz<br>1000 MHz | dBm       | _                | 51<br>74                  | _               |

| Composite Triple Beat, CTB   | 132 channels, +30 dBmV/channel at the input              | dBc       | _                | 88                        | _               |

| Composite Second Order, CSO  | 132 channels, +30 dBmV/channel at the input              | dBc       | _                | 69                        | _               |

| Steady State I <sub>DD</sub> | V <sub>DD</sub> = +5 V                                   | μΑ        | _                | 4                         | _               |

<sup>7.</sup> External DC blocking capacitors are required on all RF ports. Loss varies at 0.003 dB/°C.

## Truth Table 9

| B5 | B4 | В3 | B2 | B1 | В0 | Attenuation (dB) |

|----|----|----|----|----|----|------------------|

| 1  | 1  | 1  | 1  | 1  | 1  | Reference IL     |

| 1  | 1  | 1  | 1  | 1  | 0  | 0.5              |

| 1  | 1  | 1  | 1  | 0  | 1  | 1                |

| 1  | 1  | 1  | 0  | 1  | 1  | 2                |

| 1  | 1  | 0  | 1  | 1  | 1  | 4                |

| 1  | 0  | 1  | 1  | 1  | 1  | 8                |

| 0  | 1  | 1  | 1  | 1  | 1  | 16               |

| 0  | 0  | 0  | 0  | 0  | 0  | 31.5             |

9. 0 = 0 to 0.8V, 1 = 2 to 5V.

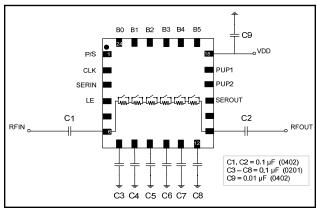

# Application <sup>10</sup>

10. Capacitors C3 - C8 should be as close to package pins as possible.

Solutions has under development. Performance is based on engineering tests. Specifications are typical. Mechanical outline has been fixed. Engineering samples and/or test data may be available. Commitment to produce in volume is not guaranteed.

<sup>8.</sup> Low frequency is determined by DC block and RF GND capacitor value.

# 75 $\Omega$ Digital Attenuator, 6-Bit, Serial / Parallel Control 31.5 dB, 0.005 - 1.0 GHz

Rev.V1

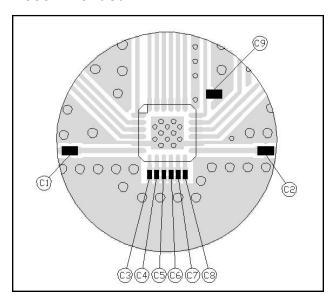

#### Recommended PCB

### **Off-Chip Component Values**

| Component | Value   | Package |

|-----------|---------|---------|

| C1 & C2   | 0.1 μF  | 0402    |

| C3 - C8   | 0.1 μF  | 0201    |

| C9        | 0.01 µF | 0402    |

#### **Handling Procedures**

Please observe the following precautions to avoid damage:

#### **Static Sensitivity**

Gallium Arsenide Integrated Circuits are sensitive to electrostatic discharge (ESD) and can be damaged by static electricity. Proper ESD control techniques should be used when handling these devices. An external protection circuit using an inexpensive anti-parallel diode pair can be used to protect the IC.

Please reference application note AN3028 on http://www.macomtech.com for further detail.

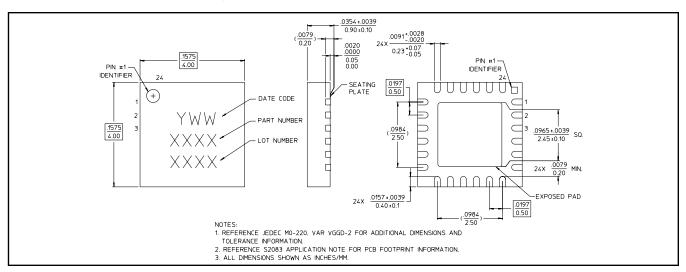

#### Lead Free 4 mm 24-Lead PQFN †

<sup>&</sup>lt;sup>†</sup> Reference Application Note M538 for lead-free solder reflow recommendations. Meets JEDEC moisture sensitivity level 1 requirements. Plating is 100% matte tin over copper.

3

India Tel: +91.80.43537383

China Tel: +86.21.2407.1588

Visit www.macomtech.com for additional data sheets and product information.

# MAAD-008866

# 75 $\Omega$ Digital Attenuator, 6-Bit, Serial / Parallel Control 31.5 dB, 0.005 - 1.0 GHz

Rev.V1

## **Typical Performance Curves**

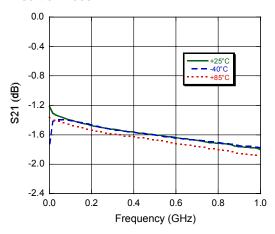

#### Insertion Loss

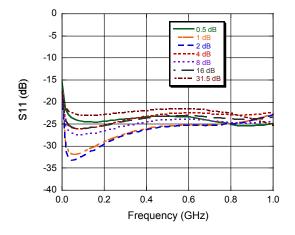

#### Input Return Loss, across all attenuation states

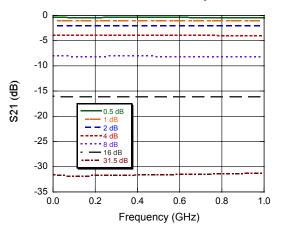

#### Relative Attenuation across all major states

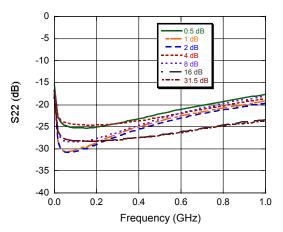

#### Output Return Loss, across all attenuation states

Europe Tel: +353.21.244.6400

China Tel: +86.21.2407.1588

# MAAD-008866

# 75 **Ω** Digital Attenuator, 6-Bit, Serial / Parallel Control 31.5 dB, 0.005 - 1.0 GHz

Rev.V1

# Typical Performance Curves @ 5 Volts

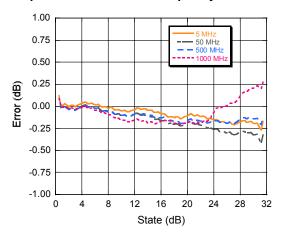

#### Step Error vs. State over Frequency

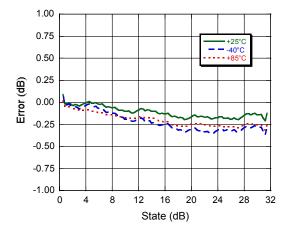

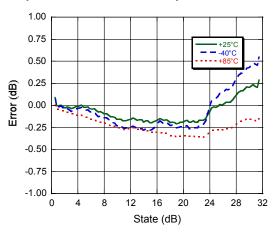

#### Step Error vs. State over Temp @ 500 MHz

#### Step Error vs. State over Temp @ 5 MHz

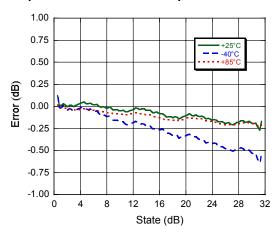

#### Step Error vs. State over Temp @ 1000 MHz

Visit www.macomtech.com for additional data sheets and product information.

# MAAD-008866

# 75 Ω Digital Attenuator, 6-Bit, Serial / Parallel Control 31.5 dB, 0.005 - 1.0 GHz

Rev.V1

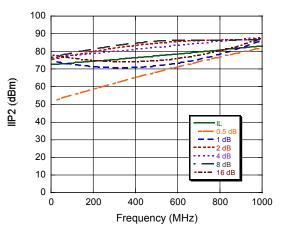

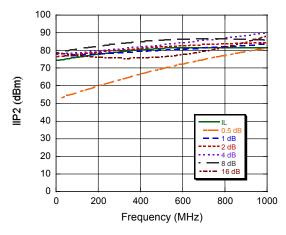

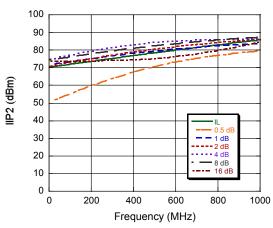

# Typical Performance Curves @ 5 Volts

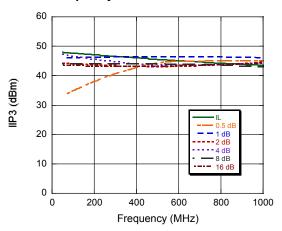

#### IIP3 vs. Frequency @ 25°C

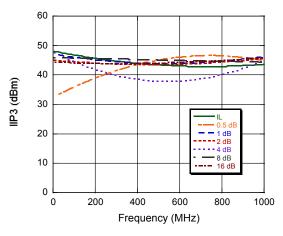

#### IIP3 vs. Frequency @ -40°C

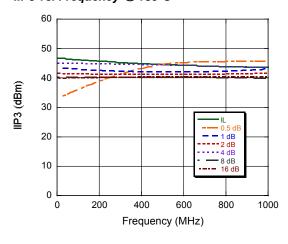

#### IIP3 vs. Frequency @ +85°C

Commitment to produce in volume is not guaranteed.

#### IIP2 vs. Frequency @ 25°C

#### IIP2 vs. Frequency @ -40°C

#### IIP2 vs. Frequency @ +85°C

India Tel: +91.80.43537383

North America Tel: 800.366.2266 • Europe Tel: +353.21.244.6400 • China Tel: +86.21.2407.1588

Visit www.macomtech.com for additional data sheets and product information.

<sup>6</sup>

75 Ω Digital Attenuator, 6-Bit, Serial / Parallel Control 31.5 dB, 0.005 - 1.0 GHz

Rev.V1

# **Functionality** Modes of Operation: Serial, Direct Parallel, and Latched Parallel

#### **Mode Truth Table**

| P/S | LE            | Mode             |

|-----|---------------|------------------|

| 1   | X             | Serial           |

| 0   | Constant High | Direct Parallel  |

| 0   | Pulsed        | Latched Parallel |

#### Serial Mode

The serial control interface (SERIN, CLK, LE, SEROUT) is compatible with the SPI protocol. SPI mode is activated when P/S is kept high. The 6-bit serial word must be loaded with MSB first. After shifting in the 6 bit word, bringing LE high will set the attenuator to the desired state. While LE is high the CLK is masked to protect the data while implementing the change . SEROUT is the SERIN delayed by 6 clock cycles.

When P/S is low, the serial control interface is disabled and the serial input register is loaded asynchronously with parallel digital inputs.

### Direct Parallel Mode

The parallel mode is enabled when P/S is set to low. In the direct parallel mode, the attenuator is controlled by the parallel control inputs directly. The LE must be at logic high to control the attenuator in this mode.

#### Latched Parallel Mode

Commitment to produce in volume is not guaranteed.

In the latched parallel mode, the parallel control inputs will be buffered by registers, and loaded to the outputs when LE is high. The outputs shall not change states when LE is low.

#### **Power-up States**

The power-up (PUP) states will work in both serial and parallel modes, and initiate the attenuator according to the PUP truth table. During power up, the digital inputs shall be held constant for at least 1 µs after V<sub>CC</sub> reaches 90% of final value. For serial mode, the PUP states will only work when LE is held low. The PUP state shall be locked out after the first LE pulse.

typical. Mechanical outline has been fixed. Engineering samples and/or test data may be available.

75 Ω Digital Attenuator, 6-Bit, Serial / Parallel Control 31.5 dB, 0.005 - 1.0 GHz

Rev.V1

# **Functionality** Modes of Operation: Serial, Direct Parallel, and Latched Parallel

#### **PUP Truth Table**

|    | Inp | puts |      |                                  | Notes         |

|----|-----|------|------|----------------------------------|---------------|

| PS | LE  | PUP2 | PUP1 | Gain Relative to Max. Gain       | Notes         |

| 0  | 0   | 0    | 0    | -31.5 dB                         |               |

| 0  | 0   | 0    | 1    | -24 dB                           |               |

| 0  | 0   | 1    | 0    | -16 dB                           | Parallel Mode |

| 0  | 0   | 1    | 1    | Insertion Loss                   |               |

| 0  | 1   | Х    | Х    | 0 to -31.5 dB (Set VC0.5 - VC16) |               |

| 1  | 0   | Х    | Х    | 0 to –31.5 dB (Set VC0.5 - VC16) |               |

| 1  | 1   | Х    | Х    | No Definition                    | Serial Mode   |

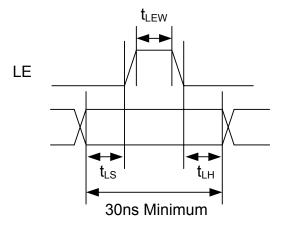

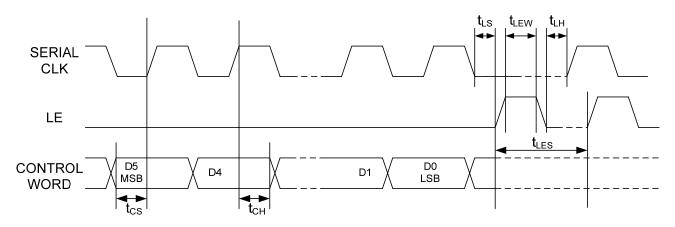

# **Serial Interface Timing Characteristics**

| Symbol           | Parameter -                         | Ту    | Heite |       |       |

|------------------|-------------------------------------|-------|-------|-------|-------|

|                  |                                     | -40°C | 25°C  | +85°C | Units |

| t <sub>sck</sub> | Min. Serial Clock Period            | 100   | 100   | 100   | ns    |

| t <sub>CS</sub>  | Min. Control Set-up Time            | 20    | 20    | 20    | ns    |

| t <sub>CH</sub>  | Min. Control Hold Time              | 20    | 20    | 20    | ns    |

| t <sub>LS</sub>  | Min. LE Set-up Time                 | 10    | 10    | 10    | ns    |

| t <sub>LEW</sub> | Min. LE Pulse Width                 | 10    | 10    | 10    | ns    |

| t <sub>LH</sub>  | Min. Serial Clock Hold Time from LE | 10    | 10    | 10    | ns    |

| t <sub>LES</sub> | Min. LE Pulse Spacing               | 630   | 630   | 630   | ns    |

75  $\Omega$  Digital Attenuator, 6-Bit, Serial / Parallel Control 31.5 dB, 0.005 - 1.0 GHz

Rev.V1

# Functionality Modes of Operation: Serial, Direct Parallel, and Latched Parallel

### **Serial Input Interface Timing Diagram**

### **Parallel Control Word**