# DIGITAL ECHO CANCELLER

- SIMPLIFIED INTERFACE CIRCUITRY FOR FLEXIBLE ADAPTION TO A WIDE RANGE OF V.32 CONFIGURATIONS

- DOVETAILED HARDWARE AND FIRMWARE CONNECTION WITH TS68950/1/2 MODEM ANALOG FRONT-END CHIP SET

- KEY COMPONENT IN THE ADVANCED TS7532 V.32 MODEM

- 16 msec OF ECHO PATH IMPULSE RESPONSE IN THE NEAR END AND IN THE FAR-END CANCELLERS

- 1.14 SEC OF CHANNEL DELAY (two satellite hops) IN FAR-END ECHO CANCELLER.

- 10Hz OF FREQUENCY OFFSET IN FAR-END ECHO PATH

- MEETS OR EXCEEDS THE REQUIREMENTS OF CCITT RECOMMENDATION V.32

#### DESCRIPTION

The TS75320 is a high performance voiceband data modem echo canceller implemented on a single chip using advanced digital signal processing technology. Using sophisticated adaptive algorithms, the TS75320 realizes the high precision cancellation of near-end and far-end echoes, even in the presence of frequency offset in the far end echo.

The residual cancellation levels and convergence rates of the TS75320 meet or exceed the demanding requirements of high performance V.32 modems.

The TS75320 is ideally suited for high performance low-cost integrated V.32 solutions.

August 1988

1/12

367

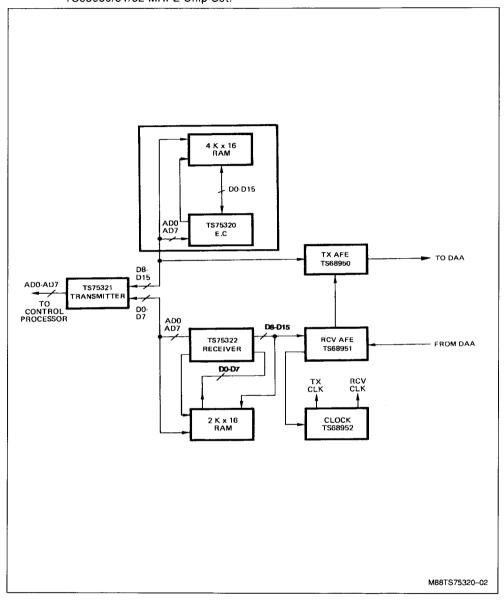

#### **BLOCK DIAGRAM**

Figure 1: Shows a Configuration for a V.32 Modem utilizing the TS75320 with the TS68950/51/52 MAFE Chip Set.

2/12

SGS-THOMSON MICROELECTROMICS

368

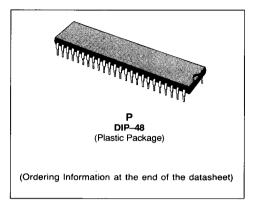

## **PIN DESCRIPTION**

## LOCAL INTERFACE

| Pin<br>Name | Pin<br>N°     | Туре | Function        | Description                                                                      |  |

|-------------|---------------|------|-----------------|----------------------------------------------------------------------------------|--|

| D (0:15)    | 45-48<br>1-11 | 1/0  | Data<br>Bus     | D(0:15) Data Bus                                                                 |  |

| A (8:11)    | 35.37.39      | 0    | Address<br>Bus  | High Order Addresses for Local Interface                                         |  |

| RD          | 17            | 0    | Read            | Transfer Data Read                                                               |  |

| WR          | 18            | 0    | Write           | Transfer Data Write                                                              |  |

| CLKOUT      | 16            | 0    | Cłock<br>Output | The frequency of CLKOUT is one half the frequency of the input clock or crystal. |  |

## SYSTEM INTERFACE

| Pin<br>Name | Pin<br>N° | Type | Function                                                       | Description                                                                                                                                                   |

|-------------|-----------|------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD (0:7)    | 27-34     | 1/0  | System Data Bus<br>or Local Address<br>Bus                     | The data exchanges between the processor and a maste via a mailbox is the function of this bus. It is also used to generate the addresses of an external RAM. |

| CS          | 21        | I    | Chip Select                                                    | Used by a Master to Gain Access to the Mailbox and System Bus                                                                                                 |

| RS          | 22        | l    | Register Select                                                | Used by a Master to Gain Access to the Mailbox and System Bus                                                                                                 |

| SDS         | 20        | 1    | System Data Synchronizes the Transfer on the System Bus Strobe |                                                                                                                                                               |

| SR/W        | 19        | I    | System<br>Read/Write                                           | Indicates the Current System Bus Cycle State                                                                                                                  |

| DTACK       | 25        | 0    | Data Transfer<br>Acknowledge                                   | Indicates that the processor has recognized it is being accessed.                                                                                             |

| BA          | 26        | 0    | Bus Available                                                  | Indicates Availability of System Bus to Master                                                                                                                |

| ĪRQ         | 24        | 0    | Interrupt Request                                              | Handshake signal sent to the master gain access to the mailbox.                                                                                               |

## OTHER PINS

| Pin<br>Name | Pin<br>N° | Туре | Function        | Description                                                                    |

|-------------|-----------|------|-----------------|--------------------------------------------------------------------------------|

| EXTAL       | 15        | 1    | Clock           | Crystal Input Pin for Internal Oscillator or Input Pin for External Oscillator |

| XTAL        | 14        | !    | Clock           | Together with EXTAL it is used for the external 25 MHz crystal.                |

| VCC         | 38        | I    | Power<br>Supply |                                                                                |

| VSS         | 13        |      | Ground          |                                                                                |

| RESET       | 23        | 1    | Reset           | -                                                                              |

#### **FUNCTIONAL DESCRIPTION**

#### PERFORMANCE SUMMARY

The TS75320 performance figures below are obtained with analog front-end D/A converters with integral linearity of 12 bits or better, such as the TS68950

- Near-end echo cancellation : > 55 dB

- With a near-end echo level of 10 dBm at the receiver input, in the absence of a far-end signal and of a far-end echo, the residual echo level is below 65 dBm

- Combined near-end and far-end echo cancellers:

For a typical receive level of –20 dBm and far-end echo smaller than –28 dBm the received signal to residual echo ratio is better than 24 dB even in the presence of up to 10 Hz of frequency offset in the far-end echo.

- The signal to residual echo ratio is better than 21 dB even for receive levels as small as -40 dBm, provided that the far-end echo is 8 dB below the received far-end signal.

- The far-end echo channel delay can be as large as 1.14 s.

- Convergence Time: meets or exceeds CCITT V.32 handshake requirements.

#### ECHO CANCELLER OPERATION

The principal task of the echo canceller is the determination by means of adaptive algorithms, of the coefficients of digital filters and phasing processors that will generate a modem receiver input free of near-end or far-end echoes. The signals processed by the echo canceller are the cancellation error at the receiver input and the V.32 date sequence being transmitted. These signals will normally be available in the appropriate format in a digitally realized modem.

The echo canceller hardware and firmware have been designed for ease of interface with a general purpose DSP or microprocessor and require minimal interaction with the modem. In this section we describe the hardware and software interfaces to the TS75320.

#### HARDWARE INTERFACE

The TS75320 echo canceller is configured as an essentially self-contained digital peripheral interfaced to a host microcontroller or to a host digital signal processor through an 8-bit system bus. The bus interface dovetails with the control bus of the TS68930 digital signal processor. Straightforward interconnection to other processors or to peripheral circuits is realized by wirtue of an asynchronous mailbox that is readily controlled by means of a flexible handshake protocol.

The system bus is also used for addressing the echo canceller external RAM, during which time it is not available to the host controller. Data transfer to the echo canceller's RAM is effected through the 16-bit data bus.

The timing of all communications with the host is determined by the echo canceller.

Data for transmission to the host is loaded into the TS75320 three-byte wide ROUT shift register. The communication process is effected by means of the mailbox transfer protocol. Data for transmission from the host is stored in the TS75320 RIN register, which is also three bytes wide.

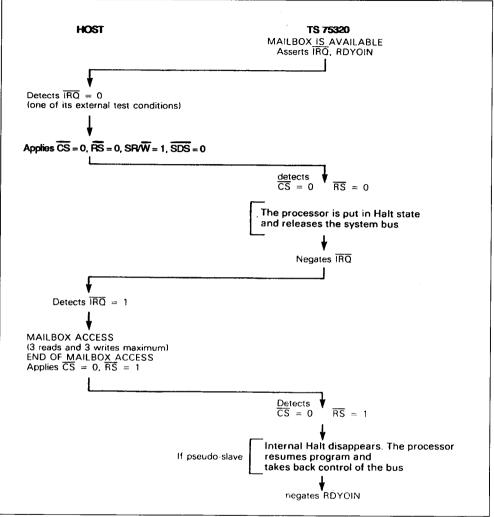

The operation of the mailbox transfer protocol is described schematically in the flow chart in Figure 2.

Figure 2: Mailbox Handshake Protocol.

While the mailbox protocol is in <u>progress</u> only, the host may deselect the TS75320 (CS = 1) to use the system bus to communicate with other peripherals.

At all other times, the system bus is under the control of the TS75320 and it is therefore essential that the connection of the bus to the host be tri-state at those times.

#### FIRMWARE INTERFACE

The echo canceller firmware is designed in the first instance for V.32 modem applications, and therefore operates at a Baud rate of 2400 symbols per second. The sampling rate is 7200 per second, i.e. three samples per Baud interval.

In the period of one Baud interval, the echo canceller generates three echo estimates, one for each of the three receiver samples, and it requires the input of the three corresponding echo cancellation errors. The echo estimates and the cancellation errors are both 16 bit quantities. The echo canceller requires also the input of the complex-valued V.32 format current symbol from the transmitter, this is the reference signal for the computation of the echo estimates. By virtue of the V.32 constellation requirements, three bits are sufficient for the representation of the real and imaginary parts, respectively. Hence, the transfer of this signal is effected with a single byte (the four MSBs for the real part, the four LSBs for the imaginary part).

Three mailbox exchanges are required per Baud interval to transfer the data. Once an echo estimate has been computed, it is stored in the TS75320 ROUT register (3-byte wide). The LSB and MSB are stored in the first and second bytes, respectively.

The TS75320 then initiates a mailbox transfer during which the host reads the echo estimate (LSBs followed by MSBs) and stores the two bytes for the transmitted symbol. The mailbox transfer operation is identical for the second and third echo estimates

and for the cancellation errors except that there is no need for the transmitted symbol to be transferred more than once per baud interval.

Particular care must be taken, however, to ensure that the modem does not hold the echo canceller during the mailbox transfer for more than the time required for the data transfer. Otherwise problems relating to cycle duration may arise.

#### INITIALIZATION

The echo canceller is initialized by first asserting the reset signal (RESET = 0) for at least 640 ns. The TS75320 will then automatically clear its internal status and filter coefficients. It will then wait for a mailbox transfer consisting of the following three hexadecimal bytes: AA AA 00. This will indicate the beginning of echo canceller configuration.

The first mailbox transfer after the configuration bytes must contain the far-end echo round trip delay expressed in number of Baud periods. This number must be smaller than 3000 (1.25 seconds). The echo canceller will interpret the first two bytes in its RIN register as the round trip delay, LSBs followed by MSBs, right justified. If the third byte is 0, the farend echo canceller is disabled. If it is 1, the far-end canceller is enabled.

The near-end echo canceller convergence is enabled by the following 3 bytes in the RIN register of the TS75320: AA AA 01. If the far-end echo canceller is enabled it will start adapting automatically once the near-end echo canceller has converged.

### **ABSOLUTE MAXIMUM RATINGS**

| Symbol            | Parameter                   | Value        | Unit |

|-------------------|-----------------------------|--------------|------|

| V <sub>cc</sub> * | Supply Voltage              | - 0.3 to 7.0 | V    |

| V <sub>in</sub> * | Input Voltage               | - 0.3 to 7.0 | V    |

| TA                | Operating Temperature Range | 0 to 70      | .c   |

| T <sub>stq</sub>  | Storage Temperature Range   | - 55 to 150  | °C   |

With respect to Vss.

Stresses above those hereby listed may cause permanent damage to the device. The ratings are stress ones only and functional operation of the device at these or any conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability. Standard MOS circuits handling procedure should be used to avoid possible damage to the device.

## DC ELECTRICAL OPERATING - CHARACTERISTICS

$V_{CC} = 5.0 \text{ V} \pm 5 \text{ %}, V_{SS} = 0, T_{amb} = 0 \text{ to} + 70 \text{ }^{\circ}\text{C} \text{ (unless otherwise specified)}$

| Symbol          | Parameter                                         | Min.  | Тур. | Max. | Unit |

|-----------------|---------------------------------------------------|-------|------|------|------|

| Vcc             | Supply Voltage                                    | 4.75  | 5    | 5.25 | V    |

| V <sub>IL</sub> | Input Low Voltage                                 | - 0.3 | _    | 0.8  | V    |

| V <sub>IH</sub> | Input High Voltage                                | 2.4   | _    | Vcc  | V    |

| lin             | Input Leakage Current Except EXTAL                | - 10  | _    | 10   | μА   |

| $I_i$           | Input EXTAL Current                               | - 50  | -    | 50   | μА   |

| V <sub>OH</sub> | Output High Voltage (I <sub>load</sub> = -300 μA) | 2.7   | _    | _    | ٧    |

| V <sub>OL</sub> | Output Low Voltage (I <sub>load</sub> = 3.2 mA)   |       | _    | 0.5  | ٧    |

| PD              | Power Dissipation                                 | _     | 1.5  | _    | W    |

| Cin             | Input Capacitance                                 | _     | 10   |      | pF   |

| ITSI            | Three State (off state) Input Current             | - 20  | _    | 20   | μА   |

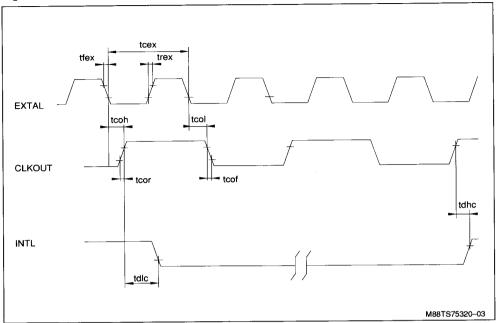

# AC ELECTRICAL SPECIFICATIONS - CLOCK AND CONTROL PINS TIMING

$(VCC = 5.0V \pm 5\%, Tamb = 0^{\circ} to +70^{\circ}C$ ; see figure 3)

Output load = 50 pF + DC characteristics load

Reference levels :

$V_{IL}: 0.45 \; V \qquad V_{IH}: 2.4 \; V$

V<sub>OL</sub>: 0.45 V V<sub>OH</sub>: 2.4 V

tr, tf  $\leq$  5 ns for input signals

| Symbol           | Parameter                                                     | Min. | Тур. | Max. | Unit |

|------------------|---------------------------------------------------------------|------|------|------|------|

| t <sub>cex</sub> | External Clock Cycle Time                                     | 40   |      | 160  | ns   |

| t <sub>fex</sub> | External Clock Fall Time                                      |      |      | 5    | ns   |

| t <sub>rex</sub> | External Clock Rise Time                                      |      |      | 5    | ns   |

| tcon             | EXTAL to CLKOUT High Delay                                    |      | 25   |      | ns   |

| t <sub>col</sub> | EXTAL to CLKOUT Low Delay                                     |      | 25   |      | ns   |

| trco             | CLKOUT Rise Time                                              |      |      | 10   | ns   |

| t <sub>fco</sub> | CLKOUT Fall Time                                              |      |      | 10   | ns   |

| t <sub>dsl</sub> | CLKOUT to DS, RD, WR Low                                      |      | 5    |      | ns   |

| tdsh             | CLKOUT to DS, RD, WR High                                     |      | 5    |      | ns   |

| tsc              | Control Inputs Set-up Time<br>(BS0 BS2, BE3 BE6, Reset, Halt) | 20   |      | -    | ns   |

| thc              | Control Inputs Hold Time<br>(BS0 BS2, BE3 BE6, Reset, Hait)   | 10   |      |      | ns   |

| tdic             | CLKOUT to Control Output Low (IRQ, BA)                        |      |      | 50   | ns   |

| t <sub>dhc</sub> | CLKOUT to Control Output High (BA, IRQ)                       |      |      | 50   | ns   |

Figure 3: Clock and Control Pins Timing.

Note 1: t<sub>c</sub> = Instruction cycle time = 4 t<sub>cex</sub>.

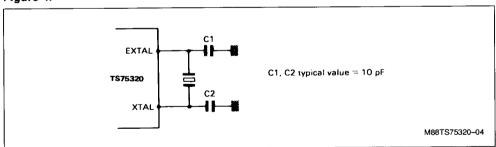

## INTERNAL CLOCK OPTION

A crystal oscillator can be connected across XTAL and EXTAL. The frequency of CLKOUT: tc/2 is half the crystal fundamental frequency.

Figure 4.

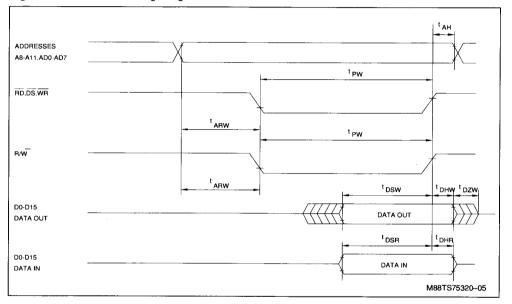

#### **ELECTRICAL CHARACTERISTICS - LOCAL BUS TIMING**

$(V_{CC} = 5.0 \text{ V} \pm 5 \%, T_{amb} = 0 \% \text{ to } + 70 \% \text{ ; see figure 5})$

| Symbol           | Parameter                                    | Min.        | Max.   | Unit |

|------------------|----------------------------------------------|-------------|--------|------|

| tpw              | RD, WR, SDS, Pulse Width                     | 1/5 tc - 15 | 1/2 tc | ns   |

| t <sub>AH</sub>  | Address Hold Time                            | 10          | _      | ns   |

| t <sub>DSW</sub> | Data Set-up Time, Write Cycle                | 25          | _      | ns   |

| t <sub>DHW</sub> | Data Hold Time, Write Cycle                  | 10          | _      | ns   |

| t <sub>DZW</sub> | SDS High to Data High Impedance, Write Cycle | _           | 40     | ns   |

| t <sub>DSR</sub> | Data Set-up Time, Read Cycle                 | 20          | _      | ns   |

| tohr             | Data Hold Time, Read Cycle                   | 5           | _      | ns   |

| tanw             | Address Valid to WR, SDS, RD Low             | 1/2 tc - 40 | _      | ns   |

Figure 5: Local Bus Timing Diagram.

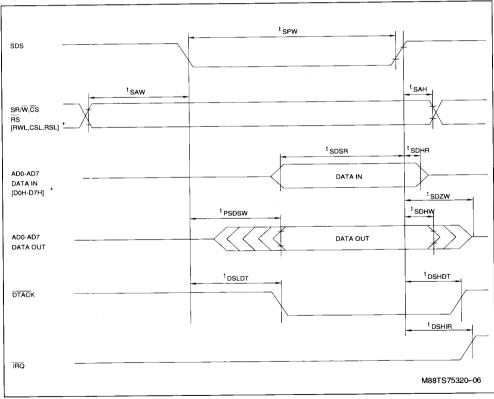

# AC ELECTRICAL SPECIFICATIONS. SYSTEM BUS TIMING

$(V_{CC} = 5.0 \text{ V} \pm 5 \%, T_{amb} = 0 \% \text{ to} + 70 \% \text{ ; see figure 6})$

| Symbol             | Parameter                                    | Min. | Max. | Unit |

|--------------------|----------------------------------------------|------|------|------|

| tspw               | SDS Pulse Width                              | 60   |      | ns   |

| tsaw               | SR/W, CS, RS Set-up Time                     | 20   |      | ns   |

| tsah               | SR/W, CS, RS Hold after SDS High             | 5    |      | ns   |

| tspsa              | Data Set-up Time, Read Cycle                 | 20   |      | ns   |

| tsphr              | Data Hold Time, Read Cycle                   | 5    |      | ns   |

| tspsw              | Data Set-up Time, Write Cycle                |      | 35   | ns   |

| t <sub>SDHW</sub>  | Data Hold Time, Write Cycle                  | 10   | 50   | ns   |

| toslot             | SDS Low to DTACK Low                         | -    | 50   | ns   |

| t <sub>DSHDT</sub> | SDS High to DTACK High *                     | -    | 50   | ns   |

| toshir             | SDS High to IRQ High                         | _    | 50   | ns   |

| tspzw              | SDS High to Data High Impedance, Write Cycle |      | 40   | ns   |

<sup>\*</sup>  $\overline{\text{DTACK}}$  is an open drain output test load include R<sub>L</sub> = 890 $\Omega$  at V<sub>cc</sub>.

Figure 6: System Bus Timing Diagram.

10/12

SGS-THOMSON MICROELECTRONICS

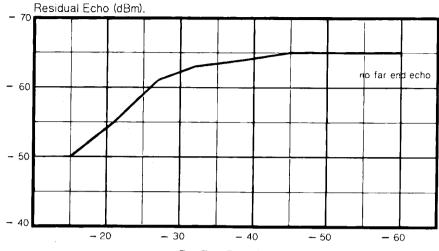

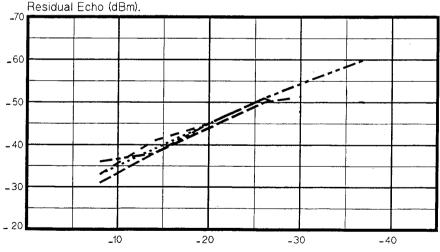

#### TYPICAL PERFORMANCE

TS75320: Residual Echo without Far-end Signal.

Far End Echo (dBm).

M88TS75320-07

TS75320 : Residual Echo versus Far End Signal (with far-end echo level 8dB below far-end signal).

Far End Signal (dBm).

M88TS75320-08

SGS-THOMSON

11/12

377

#### ORDERING INFORMATION

| Part Number | Temperature RAnge | Package            |  |

|-------------|-------------------|--------------------|--|

| TS75320CP   | 0 °C to + 70 °C   | 48 Pin Plastic Dil |  |

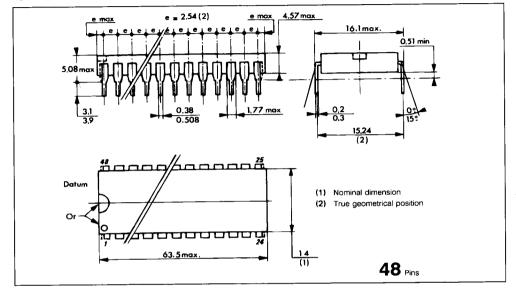

## PACKAGE MECHANICAL DATA

48 PINS - PLASTIC DIP