# Designing A High-Frequency, Higher-Power Buck/Boost Converter for Multi-Cell Input Configurations Using Si9168

Nitin Kalje

#### INTRODUCTION

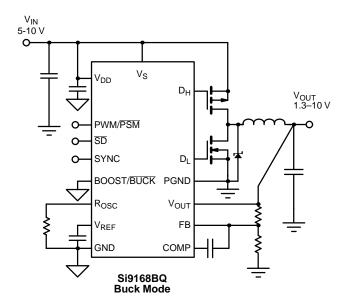

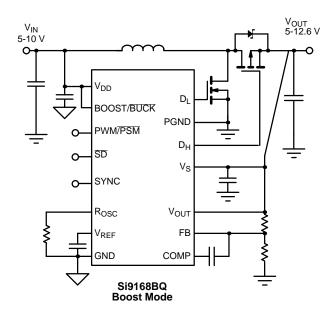

The Si9168 is a high-frequency synchronous dc-to-dc controller designed for higher-power buck or boost conversion applications in end products running off 2-cell Lithium Ion or 6-cell NiCd or NiMH battery packs. Like the lower-power Si9167, the Si9168 is capable of operating at up to 2 MHz while offering the flexibility to choose the optimum drivers for higher current handling. Its high-frequency operation, strong totem pole drivers, selectable PWM/PSM operation modes, integrated under-voltage lockout, and soft-start features make

the Si9168 suitable for 1-A to 10-A conversion applications. A synchronization feature allows designers to use multiple Si9168s for a complete power management system, where size and cost are a prime importance. The Si9168 is designed to promote efficient use of battery energy and to allow the use of smaller form factors, thanks to better heat dissipation and thereby lower operating junction temperature of power management components.

#### **DESIGN GUIDELINES**

The features and functions of the Si9168 are described in detail in the product data sheet. The following section provides design guidelines for the creation of buck and boost dc-to-dc converters using the Si9168.

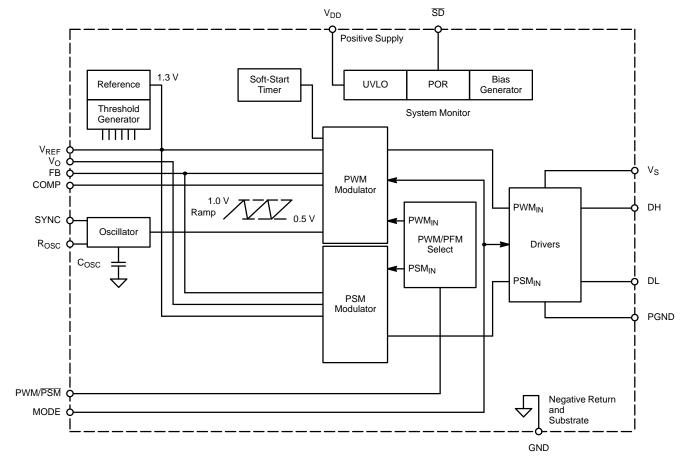

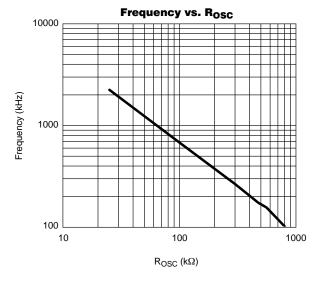

#### Oscillator Frequency—Choosing Rosc

The oscillator function is implemented with an RS flip-flop, an inverter, an internal capacitor, a temperature-compensated

current source, and an external resistor. The oscillator ramp is generated by charging the internal capacitor with a constant current source. This current is mirrored from the current in ROSC. The capacitor is charged from 0.5 V to a 1-V threshold, where it is discharged at a faster rate and the flip-flop is reset for the next cycle. The lower the value of Rosc, the higher the charging current and the higher the oscillator frequency. The oscillator is guaranteed to operate within  $\pm 20\%$  with a 1% RoSC for the 200-kHz to 2-MHz frequency range. Refer to Figure 2 to set the oscillator frequency.

#### **APPLICATION SCHEMATIC**

FIGURE 1.

FIGURE 2. Frequency Setting

#### **Synchronization**

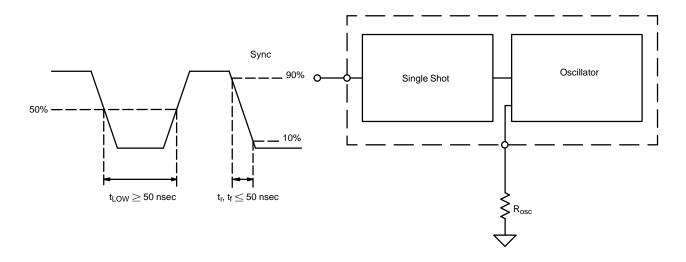

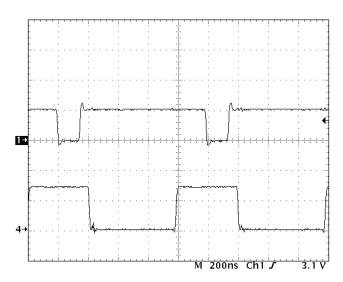

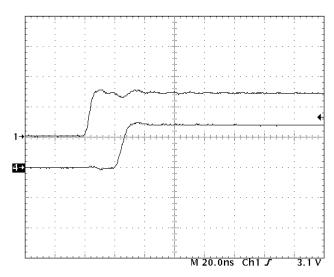

The internal single-shot circuit resets the flip-flop at the low-going edge of the external synchronization pulse. The external clock driving the synchronization pin does not get loaded because of the low input capacitance seen at the synchronous pin. At every cycle, the low-going external clock pulse would end the positive ramp and start the next cycle. Obviously, the external clock frequency needs to be at least 20% higher than the internal oscillator frequency for reliable synchronization. In addition, the minimum low pulse width must be 50 nS, while the fall time should not exceed 50 nS (refer to Figure 3). Figure 4 shows the synchronization achieved with the external clock running at 1.2 times the internal oscillator frequency.

FIGURE 3. Synch Pulse Width

Ch1 – External Clock (5 V/div)

Ch4 – Drive Output (5 V/div)

F<sub>OSC</sub> (Internal) – 825 kHz

F<sub>CLOCK</sub> (External) – 1 MHz

FIGURE 4. Synchronization

#### **Duty Cycle**

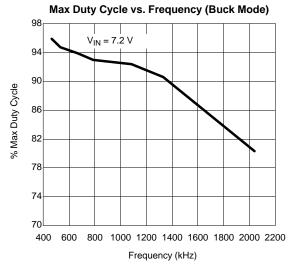

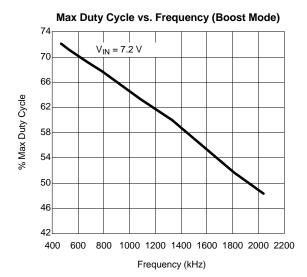

In PWM mode, the controller operates at a fixed frequency determined by  $R_{OSC}$ . The duty cycle in buck or boost mode is a function of the difference in the input and output voltage levels, with the maximum duty ratio at a minimum input line.

At 2 MHz, the duty cycle in buck mode increases gradually up to a typical level of 80% before jumping instantaneously to 100%. At this time, the upper switch is continuously in the on state and the converter functions as a low dropout regulator. The difference between the input and output voltages is equal to the resistive drop in the upper MOSFET switch, the inductor, and the printed circuit board (pcb) traces. Since the fixed break-before-make (BBM) time causes this sudden jump, the maximum duty cycle the converter can attain before going into LDO mode will increase at lower switching frequencies.

In boost mode, the same phenomenon is observed when the duty cycle needs to be reduced down to 0%. The decrease will be gradual from 75% to 5% and abrupt from 5% to 0%. The maximum duty cycle in boost mode is limited in order to provide a fixed off-state time for an inductor to discharge before the next cycle. Obviously, the maximum achievable duty cycle is inversely proportional to the switching frequency of the converter. Refer to Figure 5 and Figure 6 for typical maximum duty cycles at selected operating frequencies.

Before selecting the operating frequency, ensure that the maximum duty cycle required at the minimum input and maximum output voltages and loads is less than or equal to the maximum provided by the Si9168. Refer equations 1 and 2 to calculate the maximum operating duty cycle at the rated load.

$$D_{MAX-BUCK} = \frac{V_{OUT\_MAX} + V_{ESR} + V_{TRACE}}{V_{IN\_MIN} - r_{DS\_p} \times I_{OUT}}$$

(1)

$$\begin{split} &D_{MAX-BOOST} = \\ &\frac{V_{OUT\_MAX} + V_{ESR} + V_{TRACE} + r_{DS\_p} \times I_{IN} - V_{IN\_MIN}}{V_{OUT\_MAX} + I_{IN} \left(r_{DS\_p} - r_{DS\_n}\right)} \end{split} \tag{2}$$

Where,

V<sub>ESR</sub>, V<sub>TRACE</sub> = dc voltage drop across inductor ESR, PCB traces (V)

$r_{DS_p}$ ,  $r_{DS_n}$  = on-resistance of p- or n- channel MOSFET at an operating junction temperature ( $\Omega$ )

V<sub>IN\_MIN</sub>, V<sub>OUT\_MAX</sub> = extreme minimum input and maximum output voltage (V)

$I_{IN}$ ,  $I_{OUT}$  = input supply and output load currents (A)

FIGURE 5.

#### **MOSFET Selection**

Synchronous rectification is used to achieve the best possible efficiency at moderate to high load currents. A moderate to high load can be defined as the value at which the total voltage drop across the synch switch is less than the forward voltage drop of the Schottky rectifier, which otherwise is used in asynchronous dc-dc converter. At lower loads, the switching losses of the synchronous switch can outweigh the dc losses. Under such circumstances, the Si9168 operates in pulse skipping mode, where it shuts off the synchronous switch driver and allows the parallel Schottky diode to conduct. Selection criteria for the power MOSFET include on-resistance  $(r_{DS(on)})$ , total gate charge( $Q_{\alpha}$ ), rise/fall time  $(t_r/t_f)$  and gate threshold  $(V_{GS(th)})$ .

MOSFET on-resistance is inversely proportional to the number of cells or the channel width, while the gate capacitance increases with the channel width. The product of the gate charge and on-resistance is thus a figure of merit, with a lower number signifying better performance. Vishay offers a wide range of PWM-optimized MOSFETs using Trench technology to provide the lowest product of on-resistance times gate charge. Lower gate charge is needed to reduce CV<sup>2</sup> as well as cross conduction losses by reducing the rise and fall times for a given peak gate current drive. This is critical especially when operating at a higher input voltages. It is also recommended to use a high gate threshold (4.5-V) MOSFET to reduce the CV<sup>2</sup> losses further. One good approach to selecting the appropriate level of on-resistance is to calculate the dc and total switching power losses at a load level where the converter will be operating most of the time and then choose a MOSFET with dc losses equal to or less than 40% of the total dc and switching losses combined. Refer to equations 3 through 10 to estimate the MOSFET dc (Pdc) and switching (P<sub>sw</sub>) power losses in buck and boost converters at a nominal line and load.

FIGURE 6.

#### **Buck Converter**

$$P_{sw-n} = Q_{gn} \times V_{in} \times F_{sw}$$

(3)

$$P_{dc-n} = 1.4 \times I_{rms-n} \times r_{DS(on) n}$$

(4)

$$P_{sw-P} = Q_{gp} \times V_{in} \times F_{sw} + \frac{V_{in} \times I_{pk} \times (t_r + t_f) f_{sw}}{2}$$

(5)

$$P_{dc-p} = 1.4 \times I_{rms-p} \times r_{DS(on) p}$$

(6)

#### **Boost Converter**

$$P_{sw-n} = Q_{gn} \times V_o \times f_{sw} + \frac{V_o \times I_{in} \times (t_r + t_f)}{2}$$

(7)

$$P_{dc-n} = 1.4 \times I_{rms-n} \times r_{DS(on) n}$$

(8)

$$P_{sw-P} = Q_{gp} \times V_{in} \times f_{sw}$$

(9)

$$P_{dc-p} = 1.4 \times I_{rms-p} \times r_{DS(on)_p}$$

(10)

Where,

$r_{DS(on)_p}$ ,  $r_{DS(on)_n}$  = on-resistance of the p- or n-channel MOSFET at 25°C junction temperature ( $\Omega$ )

$Q_{gn},\ Q_{gp}$  = specified total gate charge for n-, p-channel switches at  $V_{IN}$  (C)

$t_r$ ,  $t_f = rise/fall$  time of respective switches (sec)

$I_{rms-n}$ ,  $I_{rms-p}$  = RMS currents in n-/p-channel switches (A) (see Appendix)

## **Vishay Siliconix**

Once the dc and switching losses are determined, make sure that the MOSFET package can handle the power dissipation without the junction temperature going above 125°C in worst-case line/load and ambient temperature conditions.

#### **Diode Selection**

In PSM operation, the synchronous switch (n-channel in buck configurations and p-channel in boost configurations) is switched off to reduce switching losses. The circuit works as a non-synchronous buck or boost converter, where the diode freewheels during the off cycle. The operating frequency in PSM is kept relatively low to reduce switching losses, which means that dc losses can become significant if the parasitic body diode is used as a free wheeling diode. The use of a low forward drop Schottky diode is thus recommended to achieve good efficiency results in PSM operation.

The other reason the parasitic body diode cannot be used as a freewheeling diode is its dynamic behavior, the effect of which becomes more significant during high frequency PWM operation. Break before make is internally set at about 40 nS, to avoid any possible shoot-through during the transition time. The MOSFET internal body diode, being a silicon p-n junction diode, can experience a significant reverse recovery minority carrier charge if used to conduct in the forward direction during the BBM period. The result is almost the same as shoot-through without BBM and the losses are proportional to the operating frequency. At the operating frequencies above 1 MHz, these could reduce efficiency significantly.

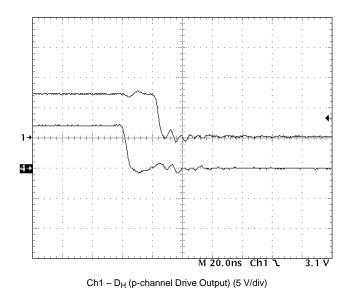

The Schottky should be chosen such that at a maximum peak inductor current, the forward drop is less than the forward breakdown of internal body diode. Figure 7 and 8 shows the practical waveforms explaining the BBM.

Ch1 – D<sub>H</sub> (p-channel Drive Output) (5 V/div) Ch4 – D<sub>L</sub> (n-channel Drive Output) (5 V/div)

FIGURE 7. Break Before Make (N-channel turn on)

FIGURE 8. Break Before Make (P-channel turn on)

Ch4 - D<sub>L</sub> (n-channel Drive Output) (5 V/div)

#### **Inductor and Capacitor**

Proper inductor and capacitor values should be chosen to achieve the specified input/output ripple, for a selected operating frequency. For a converter, operating at near one-megahertz switching frequency, the low ESR ceramic capacitors with values as low as 10  $\mu F$  are good enough to achieve 10-mV\_p-p ripple/noise at the output. The inductor value determines the ripple current( $\Delta I$ ) in the inductor and output capacitor, for given input/output voltages and switching frequency. The total peak-to-peak output ripple is contributed by the  $\Delta V_{\rm ESR}$ , caused by the ESR of the output capacitor and the  $\Delta V_{\rm C}$ , caused by the loss of charges from the output capacitor. Equal contribution of ripple voltage from the ESR and capacitance can be assumed for high frequency converters using the low ESR ceramic capacitors.

#### **Buck**

Refer to equation 11 in appendix to calculate the inductance value for a  $\Delta I = 0.2 \ I_{OUT}$ . The capacitor value and ESR for output capacitor are estimated using the following equation:

$$\begin{split} \text{ESR} &= \frac{\Delta V_{\text{ESR}}}{\Delta I} \\ C_{\text{OUT}} &= \frac{1}{\Delta V_{\text{C}}} \times \frac{1}{2} \times \left[ \frac{1}{2 F_{\text{sw}}} \times \frac{\Delta I}{2} \right] \\ \text{Output Ripple } \Delta V_{\text{P-P}} &= \Delta V_{\text{ESR}} + \Delta V_{\text{C}} \end{split}$$

#### **Boost**

Refer to Application Note AN715 to determine the required inductance for a continuous conduction mode boost conversion.

$$L_{MIN} \; = \; \frac{V_{IN}^2 \times D \times \eta}{2 \times F_{sw} \times V_{OUT} \times I_{OUT \; MIN}} \label{eq:LMIN}$$

In a boost converter, entire load current is supplied by the output capacitor when the main switch is ON. Obviously, the output capacitance required to support the load is quite high, especially at a higher duty cycle. Moreover, the output capacitor ESR needs to be low enough for minimum voltage drop across it, while supporting the load. Use the following equation to calculate the output capacitor, for a specified ripple performance.

$$\begin{split} \text{ESR} &= \frac{\Delta V_{\text{ESR}}}{\Delta I} \\ \text{C}_{\text{OUT}} &= \frac{I_{\text{OUT}} \times D_{\text{MAX}}}{\Delta V_{\text{C}} \times F_{\text{sw}}}. \\ \text{Output Ripple } \Delta V_{\text{P-P}} &= \Delta V_{\text{ESR}} + \Delta V_{\text{C}} \end{split}$$

Where,

$L_{MIN}$  = inductance required to remain in continuous conduction mode operation (H)

D<sub>MAX</sub> = maximum duty cycle at minimum V<sub>IN</sub>

$\eta$  = converter efficiency

$I_{OUT\_MIN}$  = minimum output current for continuous conduction mode (A)

#### **APPENDIX**

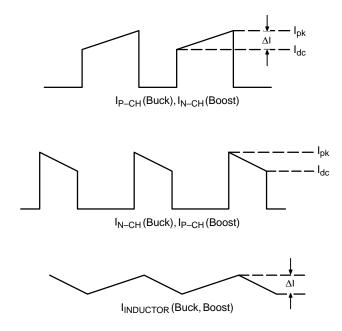

Use the following equations to calculate dc, peak, and rms values of currents in the n- and p-channel switches in buck or boost converter designs.

FIGURE 9. Current Waveform (Buck, Boost)

#### **Buck Converter**

# $\Delta I = \frac{\left(V_{in} - V_{O}\right) \times D}{L \times f_{sw}}$ $D = \frac{1.05 V_{O}}{V_{in}}$ $I_{dc} = I_{o} - \frac{\Delta I}{2}$ (2)

$$\begin{split} I_{pk} &= I_{o} + \frac{\Delta I}{2} \\ I_{rms-p} &= \sqrt{\left(I^{2}_{dc} + I^{2}_{pk} + I_{dc} \times I_{pk}\right) \frac{D}{3}} \end{split} \tag{3}$$

$$I_{rms-n} &= \sqrt{\left(I^{2}_{dc} + I^{2}_{pk} + I_{dc} \times I_{pk}\right) \frac{I-D}{3}} \end{split}$$

#### **Boost Converter**

$$\begin{split} \Delta I &= \frac{V_{in} \times D}{f_{sw} \times L} \\ D &= \frac{1.1 \left( V_o - V_{in} \right)}{V_o} \\ I_{dc} &= I_{in} - \frac{\Delta I}{2} \\ I_{pk} &= I_{in} - \frac{\Delta I}{2} \\ I_{rms\_p} &= \sqrt{\left( I^2_{dc} + I^2_{pk} + I_{dc} \times I_{pk} \right) \frac{1-D}{3}} \\ I_{rms\_n} &= \sqrt{\left( I^2_{dc} + I^2_{pk} + I_{dc} \times I_{pk} \right) \frac{D}{3}} \end{split}$$

Where,

$\begin{array}{l} \Delta I = Peak-to-Peak \ ripple \ current \ (A) \\ D = Converter \ Duty \ Cycle \\ I_{dc}, \ I_{pk} = Refer \ to \ Figure \ 9 \\ I_{L} = Inductor \ Current \ (A) \\ I_{rms-P}, \ I_{rms-n} = RMS \ current \ thru \ P, \ N-channel \ switch \ (A) \\ f_{sw} = Converter \ switching \ frequency \ (Hz) \end{array}$

(4)

#### **ADDITIONAL WAVEFORMS AND PERFORMANCE DATA**

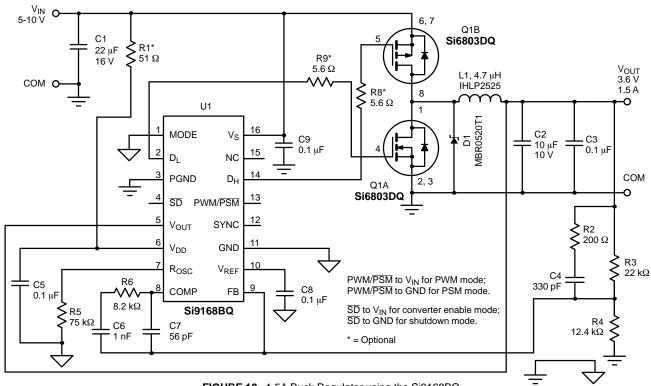

FIGURE 10. 1.5A Buck Regulator using the Si9168BQ

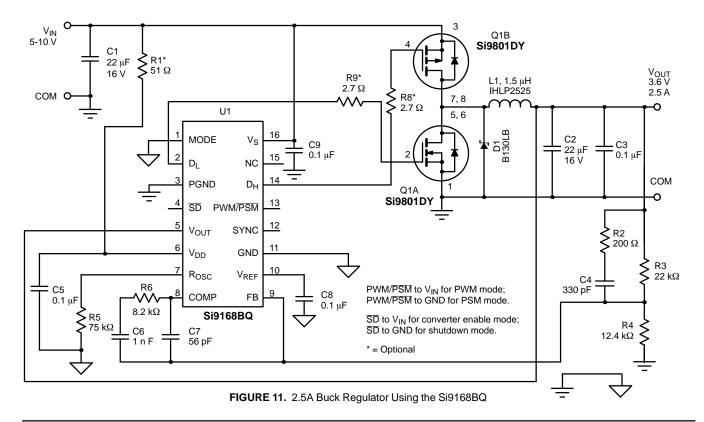

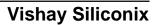

FIGURE 12. 7.2-V<sub>O</sub>/2.5-A Boost Regulator Application

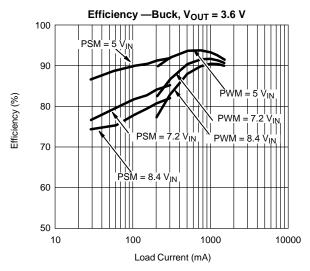

FIGURE 13. Efficiency—1.5-A Buck Converter

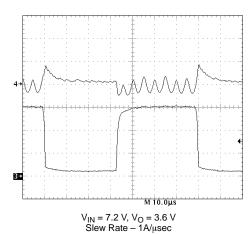

Ch4 – Output (200 mV/div)

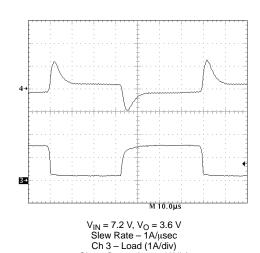

FIGURE 15. Dynamic Load Response Buck Converter – PWM

Ch4 – Output (200 mV/div)

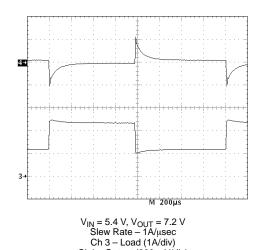

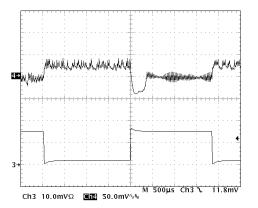

FIGURE 17. Dynamic Load Response Boost Converter – PWM

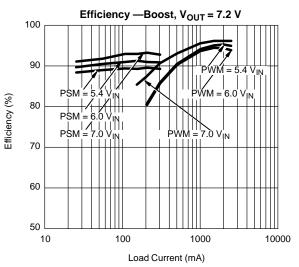

FIGURE 14. Efficiency—Boost Converter

Ch 3 – Load (100 mA/div) Ch4 – Output (100 mV/div)

FIGURE 16. Dynamic Load Response Buck Converter - PSM

$$\begin{split} &V_{\text{IN}} = 5.4 \text{ V, } V_{\text{OUT}} = 7.2 \text{ V} \\ &\text{Slew Rate} - 1 \text{A/} \mu \text{sec} \\ &\text{Ch 3} - \text{Load (200 mA/div)} \\ &\text{Ch4} - \text{Output (50 mV/div)} \end{split}$$

FIGURE 18. Dynamic Load Response Boost Converter - PSM