## **ASYNCHRONOUS COMMUNICATIONS ELEMENT WITH FIFO**

#### **FEATURES**

- PC/AT-compatible

- · Enhanced bidirectional line printer port

- · 16-byte FIFO reduces CPU interrupts

- Independent control of transmit, receive, line status and data set interrupts on each channel

- Individual modem control signals for each channel

- Programmable serial interface characteristics for each channel:

- -5-, 6-, 7- or 8-bit characters

- Even-, odd- or no-parity bit generation and detection

- 1, 1 1/2 or 2 stop bit generation

- Three-state TTL drive for the data and control bus on each channel

Hardware and software compatible with VL16C451 and VL16C451B

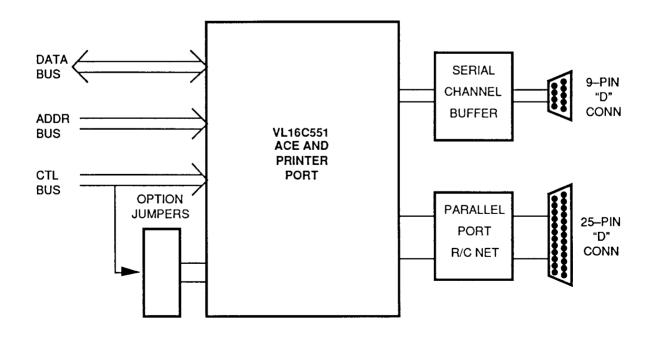

### **DESCRIPTION**

The VL16C551 is an enhanced version of the popular VL16C550 asynchronous communications element (ACE). The device serves as a serial input/output interface in microcomputer- or microprocessor-based systems. It performs serial-to-parallel conversion on data characters received from peripheral devices or modems, and parallel-to-serial conversion on data characters transmitted by the CPU. The complete status of the ACE can be read at any time during functional operation by the CPU. The information obtained includes the type and condition of the transfer

operations being performed, and error conditions.

In addition to its communications interface capabilities, the VL16C551 provides the user with a fully bidirectional parallel data port that fully supports the parallel Centronics-type printer. The parallel port, together with the two serial ports, provide PC/AT-compatible computers with a single device to serve the three system ports.

A programmable baud rate generator is included that can divide the timing reference clock input by a divisor between 1 and (2<sup>16</sup> –1).

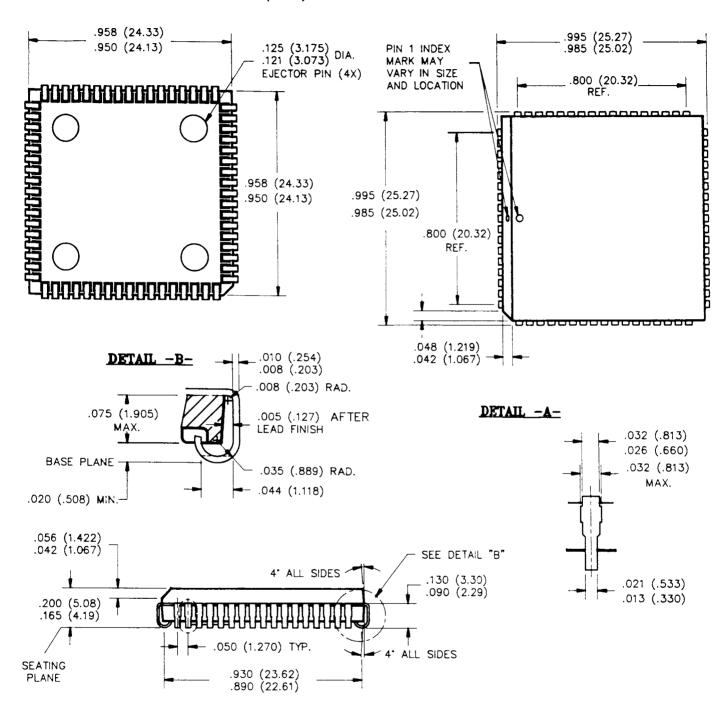

The VL16C551 is housed in a 68-pin plastic leaded chip carrier.

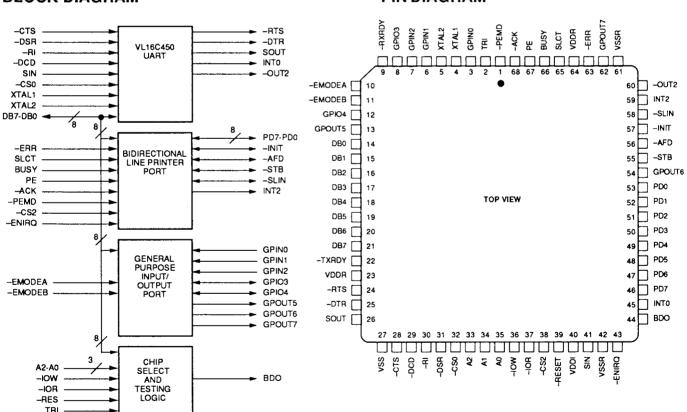

### **BLOCK DIAGRAM**

### **PIN DIAGRAM**

#### ORDER INFORMATION

| Part Maximum Number Clock Frequency |       | Package                            |  |  |

|-------------------------------------|-------|------------------------------------|--|--|

| VL16C551-QC                         | 8 MHz | Plastic Leaded Chip Carrier (PLCC) |  |  |

Note: Operating temperature range is 0°C to +70°C.

## **SIGNAL DESCRIPTIONS**

| Signal<br>Name | Pin<br>Number | Signal<br>Type | Signal<br>Description                                                                                                                                                                                                                                                                                                                                    |

|----------------|---------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

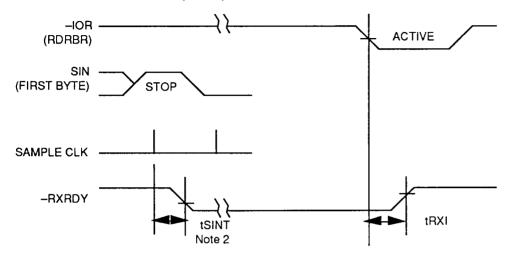

| -RXRDY         | 9             | 07             | Receiver Ready (active low) - Two types of DMA signalling are available when operating with the FIFO's enabled (bit 0 of the FCR = 1). The mode select is controlled by the status of bit 3 of the FCR.                                                                                                                                                  |

|                |               |                | Mode 0 - The -RXRDY signal will be active when in FIFO Mode 0 (bit 0 of the FCR = 1, bit 3 of the FCR = 0) and the RCVR FIFO or RCVR holding register contain at least one character. When there are no more characters in the FIFO or holding register, the -RXRDY pin will go inactive. This mode is typically used when single transfer DMA occurs.   |

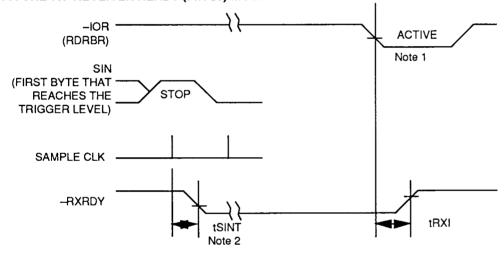

|                |               |                | Mode 1 - The –RXRDY pin will go low in the FIFO Mode (bit 0 of the FCR = 1) when bit 3 of the FCR is high and the time-out or trigger levels have been reached. It will go inactive when the FIFO or holding register is empty.                                                                                                                          |

|                |               |                | Mode 1 - The -RXRDY pin will go active in FIFO Mode 1 (bit 0 of the FCR = 1, bit 3 of the FCR = 1) when the time-out or trigger levels have been reached. It will go inactive when the FIFO or holding register is empty. This mode is typically used when continual multiple transfers that fill the FIFO are made.                                     |

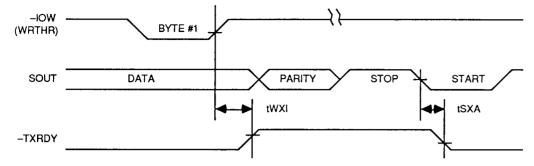

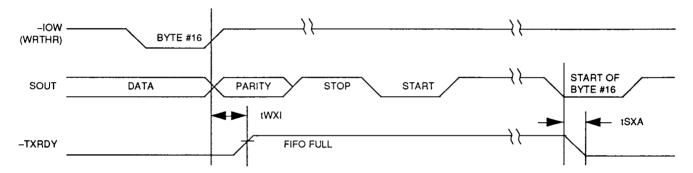

| -TXRDY         | 22            | 07             | Transmit Ready (active low) - Two types of DMA signalling are available when operating with the FIFO's enabled (bit 0 of the FCR = 1). The mode select is controlled by the status of bit 3 of the FCR.                                                                                                                                                  |

|                |               |                | Mode 0 - The -TXRDY signal will be active when in FIFO Mode 0 (bit 0 of the FCR = 1, bit 3 of the FCR = 0) and the XMIT FIFO or XMIT holding register contain no characters. When the first character is loaded into the holding register of the XMIT FIFO, -TXRDY will go inactive (high). This mode is typically used when single transfer DMA occurs. |

|                |               |                | Mode 1 - The -TXRDY pin will go active in FIFO Mode 1 (bit 0 of the FCR = 1, bit 3 of the FCR = 1) when there are no characters in the XMIT FIFO. When the XMIT FIFO is completely full, -TXRDY will go inactive. This mode is typically used when continual multiple transfers that fill the FIFO are made.                                             |

|                |               |                | Note: When the FIFO's are disabled, the VL16C551 is in VL16C450 mode. In this mode, the UARTs mimic FIFO Mode 0, which allows for single DMA transfers only.                                                                                                                                                                                             |

| -RTS           | 24            | O7             | Request To Send output (three-state, active low) - This signal is asserted to indicate the UART is ready to transmit data to an external modem. In half duplex applications, the –RTS line is used to control the transmission direction. The signal is negated on reset.                                                                                |

| -DTR           | 25            | 07             | Data Terminal Ready output (three-state, active low) - This signal is asserted to indicate the UART is ready to receive data. The signal is negated on reset.                                                                                                                                                                                            |

| SOUT           | 26            | 07             | Serial Output (three-state, active high) - SOUT is the data output of the UART. This signal is negated whenever the transmitter is disabled, —RES is active, the Transmitter Register is empty, or the UART is in Loop Mode.                                                                                                                             |

| -CTS           | 28            | l1             | Clear To Send input (active low) - This signal is a status line from the external modem to indicate that it is ready to transmit data. A change in status of this line sets the Delta CTS bit in the Modem Status Register.                                                                                                                              |

| -DSR           | 31            | I1             | Data Set Ready input (active low)DSR is a status line indicating that the external modem is ready to transfer data to/from the UART. A change in status of this line sets the Delta DSR bit in the Modem Status Register.                                                                                                                                |

SIGNAL DESCRIPTIONS (Cont.)

| Signal<br>Name | Pin<br>Number                     | Signal<br>Type | Signal<br>Description                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------|-----------------------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -DCD           | 29                                | 11             | Data Carrier Detect input (active low) - This signal is used to indicate that the external modem has detected a carrier. A change in this line sets the Delta DCD bit in the Modem Status Register.                                                                                                                                                                                                            |

| –RI            | 30                                | l1             | Ring Indicator input (active low) - This signal is used to indicate that the telephone ring signal has been detected by an external modem. The modem status register TERI bit is used to indicate that a trailing edge of the Ring Indicator has been detected.                                                                                                                                                |

| SIN            | 41                                | l1             | Serial Input (active high) - This is the data input to the UART. This input is ignored when Loop Mode is enabled.                                                                                                                                                                                                                                                                                              |

| INTO           | 45                                | O5             | Gated Interrupt Request (three-state, active high output) - This signal is asserted whenever the UART attempts to generate an interrupt. This signal is negated upon an interrupt being serviced. This signal is enabled/three-stated by setting the Interrupt Enable (bit 3) signal in the Modem Control Register. This signal is suitable for directly driving the SIRQ signal on the slot-bus of the PC/AT. |

| -CS0           | 32                                | <b>I</b> 1     | Chip Select input (active low) - $-$ CS0 is used to indicate that an access is being made to the UART registers.                                                                                                                                                                                                                                                                                               |

| –OUT2          | 60                                | O4             | Output - User defined output for modem control logic that can be set to an active low by programming bit 3 of the Modem Control Register to a high level. This signal is cleared (high) by writing a logic 0 to the –OUT2 bit of the (MCR or whenever a reset occurs. In PC/AT or PS/2® applications, this signal normally indicates that the SIO interrupts have been enabled for system level interrupts.    |

| PARALLEL P     | RINTER PORT:                      |                |                                                                                                                                                                                                                                                                                                                                                                                                                |

| PD7-PD0        | 46, 47, 48, 49,<br>50, 51, 52, 53 | IO5            | Printer Data port bit 0 - These signals, PD7-PD0 provide a bidirectional eight-bit I/O port usually connected to a printer. These lines are driven when the -PEMD signal is negated (low) or when -PEMD is asserted and the direction control bit is set to 0 (write).                                                                                                                                         |

| -INIT          | 57                                | O4             | Printer command Initialize - This signal follows bit 2 of the LPT Port Contro Register. When bit 2 of the LPTPC = 0, -INIT is low. When bit 2 if the LPTPC = 1, -INIT is high.                                                                                                                                                                                                                                 |

| –AFD           | 56                                | O4             | Printer command Autofeed - This signal is the inversion of bit 1 of the LPTP or Control Register. When bit 1 of the LPTPC = 0, -AFD is high. When bit 1 of the LPTPC = 1, -AFD is low.                                                                                                                                                                                                                         |

| -STB           | 55                                | O4             | Printer command Data Strobe - This signal is the inversion of bit 0 of the LPT Port Control Register. When bit 0 of the LPTPC = 0, -STB is high. When bit 0 of the LPTPC = 1, -STB is low.                                                                                                                                                                                                                     |

| -SLIN          | 58                                | O4             | Printer command Select - This signal is the inversion of bit 3 of the LPT Por Control Register. When bit 3 of the LPTPC = 0, -SLIN is high. When bit 3 of the LPTPC = 1, -SLIN is low.                                                                                                                                                                                                                         |

| -ERR           | 63                                | 13             | Printer status Error - The status of this signal can be determined by reading bit 3 of the LPT Port Status Register. This bit signal follows the state of the -ERR pin.                                                                                                                                                                                                                                        |

| SLCT           | 65                                | 13             | Printer status Select - The status of this signal can be determined by reading bit 4 of the LPT Port Status Register. This bit signal follows the state of the SLCT pin.                                                                                                                                                                                                                                       |

| SIGNAL DESCRIPTIONS (Cont.) |

|-----------------------------|

|-----------------------------|

| Signal<br>Name | Pin<br>Number                     | Signal<br>Type | Signal<br>Description                                                                                                                                                                                                                                                                                                                                |

|----------------|-----------------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BUSY           | 66                                | 13             | Printer status Busy - The status of this signal can be determined by reading bit 7 of the LPT Port Status Register. This signal is the inversion of the BUSY pin.                                                                                                                                                                                    |

| PE             | 67                                | 13             | Printer status Paper Empty - The status of this signal can be determined by reading bit 5 of the LPT Port Status Register. This signal follows the state of the PE pin.                                                                                                                                                                              |

| -ACK           | 68                                | 13             | Printer status Acknowledge - The status of this signal can be determined by reading bit 6 of the LPT Port Status Register. If bit 4 of the LPT Port Control Register is a 1, a low-to-high transition of -ACK will generate an interrupt.                                                                                                            |

| INT2           | 59                                | O5             | Printer Port Interrupt - This signal is an active high, three-state output, generated by the positive transition of –ACK. It is enabled by bit 4 of the Write Control Register. Upon a reset, the interrupt output will be in the high impedance state.                                                                                              |

| PEMD           | 1                                 | I1             | Printer Enhancement Mode - When asserted (high), this signal enables the bidirectional printer port capabilities. When negated (low), the printer port is output only (PC/AT-compatible).                                                                                                                                                            |

| -CS2           | 38                                | I1             | Parallel Port Select inputCS2 is used to indicate that an access is being directed to the printer port registers.                                                                                                                                                                                                                                    |

| -ENIRQ         | 43                                | l1             | Parallel Port Interrupt Source Mode Selection - When negated (low), the AT® mode of interrupts is selected. In this mode, the –ACK input is internally connected to the INT2 output. If the –ENIRQ input is tied high, the interrupt source will be held in a latched state until the Status Register is read which will then reset the INT2 output. |

| COMMON CO      | ONTROL SIGNALS                    | :              |                                                                                                                                                                                                                                                                                                                                                      |

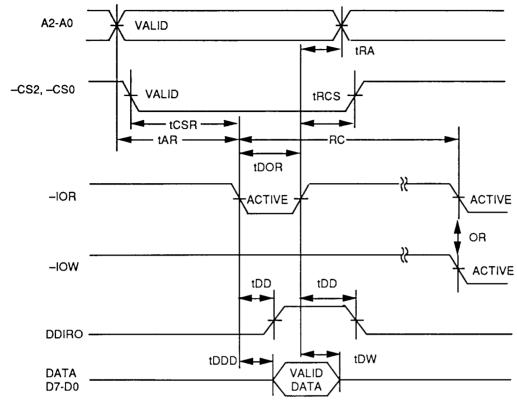

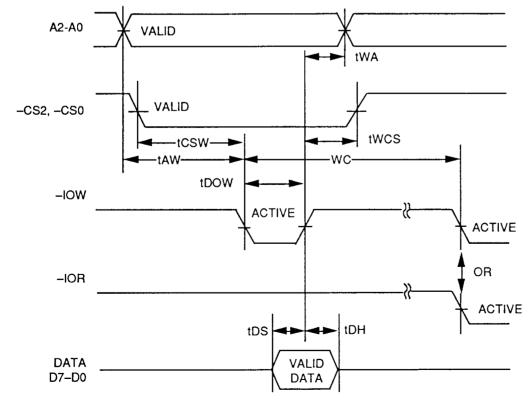

| –IOR           | 37                                | l1             | I/O Read Strobe input (active-low) - Used to drive data from the VL16C551 to the data bus (DB7-DB0). The output data depends on the register selected by the address inputs A2-A0 and the Chip Selects (CS0 for the UART, and CS2 for the printer port).                                                                                             |

| -low           | 36                                | l1             | I/O Write Strobe input (active low) - This signal is used to latch data into the VL16C551 from the data bus (DB7-DB0). The input data depends on the register selected by the address inputs A0, A1, A2 and the Chip Selects (CS0 for the UART, and CS2 for the printer port).                                                                       |

| DB7-DB0        | 21, 20, 19, 18,<br>17, 16, 15, 14 | 106            | Data I/O Bits 7-0 (three-state, active high) - These are lines used to interface to the slot bus. These signals are normally high impedance except during read cycles. Data bit 0 is the least significant bit (LSB) and data bit 7 is the most significant bit (MSB).                                                                               |

| A2-A0          | 33, 34, 35                        | 11             | Address line inputs - A2-A0 are used to decode which register is selected during CPU accesses to the VL16C551.                                                                                                                                                                                                                                       |

| XTAL1          | 4                                 | l1             | Crystal Input 1 or External Clock input - This is used for the UART baud rate generator.                                                                                                                                                                                                                                                             |

| XTAL2          | 5                                 | l1             | Crystal Input 2 - XTAL2 may be tied to VDD, VSS or left open if an external clock source is tied to XTAL1.                                                                                                                                                                                                                                           |

| -RES           | 39                                | l1             | Reset input (active low) - This signal is used to force the VL16C551 into an idle state with all serial transfers suspended. The Modem Control Register and Line Status Register are both initialized.                                                                                                                                               |

| Signal<br>Name             | Pin<br>Number       | Signal<br>Type    | Signal<br>Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                          |                          |                          |                              |                                                                          |                                |

|----------------------------|---------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------|--------------------------|------------------------------|--------------------------------------------------------------------------|--------------------------------|

| BDO                        | 44                  | O7                | Bus Drive Output (three-state, active high) - BDO is used to indicate to external octal transceivers that the VL16C551 is driving the data pins. I can be directly connected to the direction pin of a 74LS245.                                                                                                                                                                                                                                                                                                                                                                                                                                 |                          |                          |                          |                              |                                                                          |                                |

| -EMODEA                    | 10                  | 13                | -EMC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | DEB                      |                          | onfigure the             | General P                    | is used in conj<br>urpose I/O por                                        |                                |

|                            |                     |                   | EMOI<br>A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | DE<br>B                  | GPIN0-<br>GPIN2          | GPIO3                    | GPIO4                        | GPOUT5-<br>GPOUT7                                                        |                                |

|                            |                     |                   | Н                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Н                        | NC                       | NC                       | NC                           | NC                                                                       |                                |

|                            |                     |                   | Н                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | L                        | IN                       | IN                       | OUT                          | OUT                                                                      |                                |

|                            |                     |                   | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Н                        | IN                       | OUT                      | OUT                          | OUT                                                                      |                                |

|                            |                     |                   | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | L                        | IN                       | IN                       | IN                           | OUT                                                                      |                                |

| -EMODEB                    | 11                  | 13                | Enhar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | nced .                   | Mode Selec               | at B input.              |                              |                                                                          |                                |

| <b>GENERAL PU</b><br>GPINO | JRPOSE I/O POP<br>3 | R <b>T:</b><br>I3 | via the of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | e –EN<br>Gene<br>or left | MODEA and<br>eral Purpos | I -EMODEI<br>e I/O (GPIC | 3 configurat<br>)) Port Regi | s signal if enab<br>ion inputs can<br>ster. It can be<br>at high with no | be read at bit<br>tied to VSS, |

| GPIN1                      | 6                   | 13                | General Purpose Input Port Bit 1 - Read at bit 1 GPIO Port Register if enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                          |                          |                          |                              |                                                                          |                                |

| GPIN2                      | 7                   | 13                | General Purpose Input Port Bit 2 - Read at bit 2 GPIO Port Register if enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                          |                          |                          |                              |                                                                          |                                |

| GPIO3                      | 8                   | IO5               | General Purpose Input/Output Port Bit 3 - This signal can be configured to be an input or an output control bit via the –EMODEA and –EMODEB configuration inputs. If the signal is configured as an output it is initially reset to a 0 (low) state when –RES is asserted. It can be set high by programming bit 3 of the GPIO Port Register to a 1. It will be set low by programming bit 3 to a 0. If configured as an input, it can be read at bit 3 of the GPIO Port. If the bit is changed from an output port to an input port and then subsequently back to an output port, its initial state will always be reset to a logical 0 (low). |                          |                          |                          |                              |                                                                          |                                |

| GPIO4                      | 12                  | 105               | General Purpose Input/Output Port Bit 4 - Set or read at bit 4 of the GPIO Port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          |                          |                          |                              |                                                                          |                                |

| GPOUT5                     | 13                  | 04                | General Purpose Output Port Bit 5 - This signal is configured as an output control bit via the -EMODEA and -EMODEB configuration inputs. If the signal is configured as an output it is initially reset to a 0 (low) state when -RES is asserted. It can be set high by programming bit 5 of the GPIO Port Register to a 1. It will be set low by programming bit 5 to a 0.                                                                                                                                                                                                                                                                     |                          |                          |                          |                              |                                                                          |                                |

| GPOUT6                     | 54                  | O4                | Gener                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | al Pu                    |                          | ut Port Bit 6            |                              | s set or cleare                                                          |                                |

### SIGNAL DESCRIPTIONS (Cont.)

| Signal | Pin    | Signal | Signal                                                                                                           |

|--------|--------|--------|------------------------------------------------------------------------------------------------------------------|

| Name   | Number | Type   | Description                                                                                                      |

| GPOUT7 | 62     | O4     | General Purpose Output Port Bit 7 (MSB) - This bit is set or cleared by writing bit 7 of the GPIO Port Register. |

#### POWER BUSSING:

The power connections to the VL16C551 are split into an internal supply for the logic, and a ring supply for the I/O drivers. Each supply should be individually bypassed with decoupling capacitors.

| VDDR | 23, 64 | Ring Power Supply - +5 V     |

|------|--------|------------------------------|

| VDDI | 40     | Internal Power Supply - +5 V |

| VSSR | 42, 61 | Ring Ground                  |

| VSS  | 27     | Internal Ground              |

#### **TEST MODE PINS:**

The three test modes which are supported by the VL16C551 are:

In-Circuit The In-circuit Test Mode is selected when -IOW and -IOR are simultaneously taken low when DB1 is low, DB0 is high and TRI is high. This mode is normally used to confirm that the VL16C551B has been physically at-

tached to the printed circuit board.

Three-State The Three-state Test Mode is entered when the TRI input is taken high. This mode is used to control the three-state control of all I/O and output pins. When this mode is selected, all I/O and outputs become high impedance,

allowing board level testers to drive the outputs without overdriving internal buffers.

Each of these test modes are selected by driving a combination of pins into the desired mode.

TRI 2 I4 This pin is used to control the three-state control of all I/O and output pins.

When this pin is asserted, all I/O and outputs become high impedance, allowing board level testers to drive the outputs without overdriving internal buffers. This pin is level sensitive. This pin is pulled down with an internal

resistor that is approximately 5  $k\Omega,$  and is a CMOS input.

### SIGNAL LEGEND

| mA | Туре                               | Comments                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10 | ΠL                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 24 | TTL                                |                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 10 | TTL-OD                             | Open Drain Collector                                                                                                                                                                                                                                                                                                                                                                                                               |

| 12 | TTL-ODP                            | Open Drain with 3 kΩ Pull-up                                                                                                                                                                                                                                                                                                                                                                                                       |

| 10 | TTL-TS                             | Three-state                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 24 | TTL-TS                             | Three-state                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2  | TTL-TS                             | Three-state                                                                                                                                                                                                                                                                                                                                                                                                                        |

| -  | TTL                                |                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| -  | CMOS                               |                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| -  | TTL                                | With 20 kΩ Pull-up Resistor                                                                                                                                                                                                                                                                                                                                                                                                        |

| -  | CMOS                               | With 1-5kΩ Pull-down Resistor                                                                                                                                                                                                                                                                                                                                                                                                      |

| 10 | TTL-TS                             | Bidirectional, Three-state                                                                                                                                                                                                                                                                                                                                                                                                         |

| 24 | TTL-TS                             | Bidirectional, Three-state                                                                                                                                                                                                                                                                                                                                                                                                         |

| 10 | TTL-OD                             | Bidirectional, Open drain                                                                                                                                                                                                                                                                                                                                                                                                          |

| 24 | TTL-OD                             | Bidirectional, Open drain                                                                                                                                                                                                                                                                                                                                                                                                          |

| 12 | TTL-TSP                            | Bidirectional, Three-state                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4  | TTL-TS                             | Bidirectional, Three-state                                                                                                                                                                                                                                                                                                                                                                                                         |

|    | 10 24 10 12 10 24 2 10 24 10 24 10 | 10         TTL           24         TTL           10         TTL-OD           12         TTL-ODP           10         TTL-TS           24         TTL-TS           2         TTL-TS           -         TTL           -         CMOS           -         TTL           -         CMOS           10         TTL-TS           10         TTL-TS           10         TTL-OD           24         TTL-OD           12         TTL-TSP |

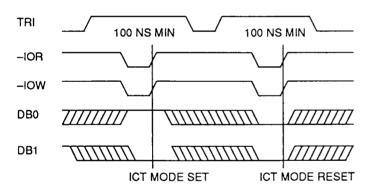

### **IN-CIRCUIT-TEST DESCRIPTION:**

During In-circuit-test (ICT) all of the inputs except TRI and –RES can toggle one or more outputs. This allows for a board level tester to test the solder connections for each signal pin.

The sequence for enabling ICT is as follows:

- 1. Tester drives TRI signal to 1.

- 2. Tester drives DB0=1 and DB1=0.

- 3. Tester pulses -IOR and -IOW low for 100 ns (minimum).

- 4. Tester drives TRI signal to 0 (outputs now enabled).

- 5. VL16C551 is now in ICT mode.

The sequence for disabling ICT is either assertion of the –RES signal or the sequence as follows:

- 1. Tester drives TRI signal to 1.

- 2. Tester drives both DB0 and DB1 to 1 or both to 0.

- 3. Tester pulses -IOR and -IOW low for 100 ns (minimum).

- 4. Tester drives TRI signal to 0 (outputs now enabled).

- 5. VL16C551 is now out of ICT mode.

Functionally ICT can be entered and exited as shown in the ICT Test Timing diagram.

## TABLE 1. PIN MAPPING FROM INPUT TO OUTPUT

| INPUT |         |      | OUTPUT   |            |            |

|-------|---------|------|----------|------------|------------|

| Pin   | Signal  | Туре | Pin      | Signal     | Туре       |

|       | -PEMD   | I    | 8        | GPIO3      | 1/0        |

| 3     | GPIN0   |      | 12       | GPIO4      | 1/0        |

| 6     | GPIN1   | -    | 13       | GPOUT5     | 0          |

| 7     | GPIN2   | 1    | 24       | -RTS       | 0          |

| 10    | -EMODEA | 1    | 25       | -DTR       | 0          |

| 11    | -EMODEB | 1    | 26       | SOUT       | 0          |

| 38    | -CS2    | _    | 54       | GPOUT6     | 0          |

| 28    | -CTS    | ı    | 44       | BD0        | 0          |

| 29    | -DCD    | 1    | 45       | iNT0       | 0          |

| 30    | -RI     | I    | 21<br>46 | DB7<br>PD7 | I/O<br>I/O |

| 31    | -DSR    | ı    | 20<br>47 | DB6<br>PD6 | 1/O<br>1/O |

| 32    | -CS0    | 1    | 19<br>48 | DB5<br>PD5 | I/O<br>I/O |

| 33    | A2      | I    | 18<br>49 | DB4<br>PD4 | I/O<br>I/O |

| 34    | A1      | l    | 17<br>50 | DB3<br>PD3 | 1/O<br>1/O |

| 35    | Ao      | 1    | 16<br>51 | DB2<br>PD2 | I/O<br>I/O |

| 36    | -IOW    | I    | 15<br>52 | DB1<br>PD1 | I/O<br>I/O |

| 37    | -IOR    | l    | 14<br>53 | DB0<br>PD0 | I/O<br>I/O |

| 41    | SIN     | ı    | 55       | -STB       | 0          |

| 43    | -ENIRQ  | 1    | 56       | –AFD       | 0          |

| 63    | –ERR    | 1    | 57       | -INIT      | 0          |

| 65    | SLCT    | I    | 58       | -SLIN      | 0          |

| 66    | BUSY    | I    | 59       | INT2       | 0          |

| 67    | PE      | ı    | 60       | –OUT2      | 0          |

| 68    | -ACK    | ı    | 62       | GPOUT7     | 0          |

# TABLE 2. PINS NOT MAPPED

| Pin | Signal | Type |

|-----|--------|------|

| 2   | TRI    |      |

| 9   | GNDI   | GND  |

| 22  | GNDR   | GND  |

| 23  | VDDR   | PWR  |

| 27  | GNDI   | GND  |

| 39  | -RES   | 1    |

| 40  | VDDI   | PWR  |

| 42  | GNDR   | GND  |

| 61  | GNDR   | GND  |

| 64  | VDDR   | PWR  |

### **REGISTERS**

Three types of internal registers are used in the ACE (Control, Status and Data). The control registers are the Bit Rate Select Register DLL (Divisor Latch LSB) and DLM (Divisor Latch MSB), Line Control Register, Interrupt Enable Register, FIFO Control Register and the Modem Control Register. The status registers are the Line Status Registers and the Modem Status

Register. The data registers are the Receiver Buffer Register and the Transmitter Holding Register. The Address, Read, and Write inputs are used in conjunction with the Divisor Latch Access Bit in bit 7 of the Line Control Register to select the register to be written or read (see Table 3). The Transmitter Buffer Register and Receiver Buffer Register are data registers that hold from five to eight bits

of data. If less than eight data bits are transmitted, data is right justified to the LSB. Bit 0 of a data word is always the first serial data bit received and transmitted. The ACE data registers are double-buffered so that read and write operations may be performed when the ACE is performing the parallel-to-serial or serial-to-parallel conversion.

### **TABLE 3. SERIAL CHANNEL INTERNAL REGISTERS**

| DLAB | A2 | <b>A</b> 1 | A0 | Mnemonic                               | Register                                      |

|------|----|------------|----|----------------------------------------|-----------------------------------------------|

| 0    | 0  | 0          | 0  | RBR                                    | Receiver Buffer Register (read-only)          |

| 0    | 0  | 0          | 0  | THR                                    | Transmitter Holding Register (write-only)     |

| 0    | 0  | 0          | 1  | IER                                    | Interrupt Enable Register                     |

| X    | 0  | 1          | 0  | IIR                                    | Interrupt Identification Register (read-only) |

| X    | 0  | 1          | 0  | FCR FIFO Control Register (write-only) |                                               |

| X    | 0  | 1          | 1  | LCR Line Control Register              |                                               |

| X    | 1  | 0          | 0  | MCR Modem Control Register             |                                               |

| X    | 1  | 0          | 1  | LSR                                    | Line Status Register                          |

| X    | 1  | 1          | 0  | MSR                                    | Modem Status Register                         |

| Χ    | 1  | 1          | 1  | SCR Scratch Register                   |                                               |

| 1    | 0  | 0          | 0  | DLL Divisor Latch (LSB)                |                                               |

| 1    | 0  | 0          | 1  | DLM                                    | Divisor Latch (MSB)                           |

X = "Don't Care"

0 = Logic Low

1 = Logic High

Note: The serial channel is accessed when CS0 is low.

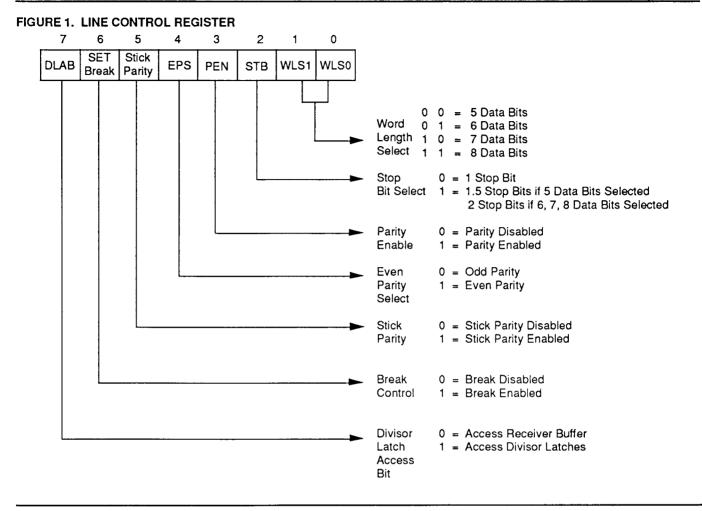

### LINE CONTROL REGISTER

The format of the data character is controlled by the Line Control Register. The LCR may be read. Its contents are described below and shown in Figure 1.

Bits 1 and 2 - Word Length Select bit 1. The number of bits in each serial character is programmed as shown in Figure 2.

Bit 2 - Stop Bit Select. This bit specifies the number of stop bits in each transmitted character. The receiver always checks for one stop bit.

Bit 3 - Parity Enable. When bit 3 of the LCR is high, a parity bit between the last data word bit and stop bit is generated and checked.

Bit 4 - Even Parity Select. When enabled a one selects even parity.

Bit 5 - Stick Parity. When parity is enabled (bit 3 of the LCR = 1), bit 5 of the LCR = 1 causes the transmission

and reception of a parity bit to be in the opposite state from the value of bit 4 of the LCR. This forces parity to a known state and allows the receiver to check the parity bit in a known state.

Bit 6 - Break Control. When bit 6 of the LCR is set to a logic 1, the serial output (SOUT) is forced to the spacing (logic 0) state. The Break Control bit acts only on SOUT and does not effect the transmitter logic. If the following sequence is used, no invalid characters will be transmitted because of the break.

- Load all "0"s pad character in response to THRE.

- 2. Set the break in response to the next THRF.

- Wait for the transmitter to be idle (TEMT = 1), then clear the break when the normal transmission has to be restored.

Bit 7 - Divisor Latch Access Bit (DLAB). This bit must be set high (logic 1) to access the Divisor Latches DLL and DLM of the Baud Rate Generator during a read or write operation. Bit 7 of the LCR must be input low (logic 0) to access the Receiver Buffer, the Transmitter Holding, or the Interrupt Enable Registers.

#### LINE STATUS REGISTER

The Line Status Register (LSR) is a single register that provides status indications.

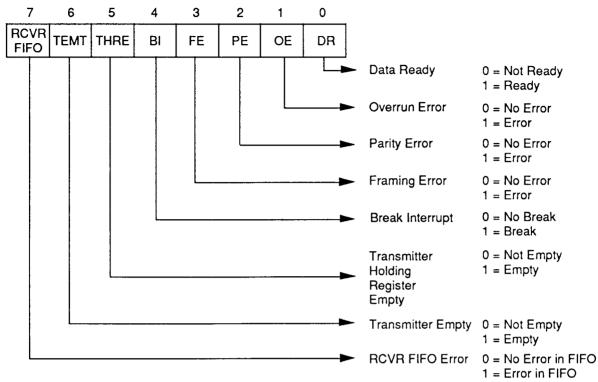

The Line Status Register shown in Figure 2 is described below:

Bit 0 - Data Ready (DR). Data Ready indicates that the RBR, or FIFO, has been loaded with a received character (including Break) and that the CPU may access this data. This bit is set low by a read of the RBR when in VL16C450 Mode or FIFO Mode 0. When in FIFO

#### FIGURE 2. LINE STATUS REGISTER

Mode 1, this bit is not set low until the last byte is read (read RBR) from the FIFO.

Bit 1 - Overrun Error (OE). Overrun Error indicates that data in the Receiver Buffer Register was not read by the CPU before the next character was transferred into the Receiver Buffer Register, overwriting the previous character. The OE indicator is reset whenever the CPU reads the contents of the Line Status Register.

An overrun error will occur in the FIFO Mode after the FIFO is full and the next character is completely received. The overrun error is detected by the CPU on the first LSR read after it happens. The character in the shift register is not transferred to the FIFO but it is overwritten.

Bit 2 - Parity Error (PE). Parity Error indicates that the received data character does not have the correct parity, as selected by bits 3 and 4 of the LCR. The PE bit is set high upon detection of a parity error, and is reset low when the CPU reads the contents of the LSR.

In the FIFO Mode, the Parity Error is associated with a particular character in the FIFO. Bit 2 of the LSR reflects the

error when the character is at the top of the FIFO.

Bit 3 - Framing Error (FE). Framing Error indicates that the received character did not have a valid stop bit. This bit is set high when the stop bit following the last data bit or parity bit is detected as a zero bit (spacing level). The FE indicator is reset low when the CPU reads the contents of the LSR. In the FIFO Mode, the Framing Error is associated with a particular character in the FIFO. Bit 3 of the LSR reflects the error when the character is at the top of the FIFO.

Bit 4 - Break Interrupt (BI). Break Interrupt is set high when the received data input is held in the spacing (logic 0) state for a full word transmission time (start bit + data bits + parity + stop bits). The BI indicator is reset when the CPU reads the contents of the Line Status Register.

In the FIFO Mode this is associated with a particular character in the FIFO. Bit 4 of the LSR reflects the BI when the break character is at the top of the FIFO. The error is detected by the CPU when its associated character is at the top of the FIFO during the first LSR

read. Only one zero character is loaded into the FIFO when BI occurs.

Bits 1 through 4 are the error conditions that produce a Receiver Line Status interrupt [priority 1 interrupt in the Interrupt Identification Register (IIR)] when any of the conditions are detected. This interrupt is enabled by setting bit 2 of the IER = 1 in the Interrupt Enable Register.

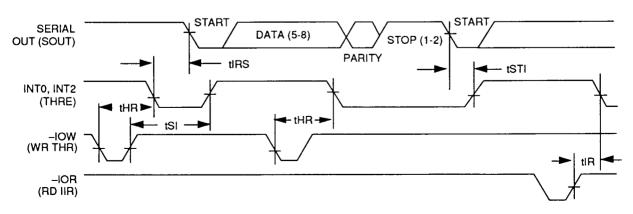

Bit 5 - Transmitter Holding Register Empty (THRE). THRE indicates that the ACE is ready to accept a new character for transmission. The THRE bit is set high when a character is transferred from the Transmitter Holding Register into the Transmitter Shift Register. Bit 5 is reset low by the loading of the Transmitter Holding Register by the CPU. Bit 5 is not reset by a CPU read of the LSR. In the FIFO Mode when the XMIT FIFO is empty this bit is set. It is cleared when one byte is written to the XMIT FIFO.

When the THRE interrupt is enabled IER(1), THRE causes a priority 3 interrupt in the IIR. If THRE is the interrupt source indicated in IIR, INTRPT is cleared by a read of the IIR.

Bit 6 - Transmitter Empty (TEMT). TEMT is set high when the Transmitter Holding Register (THR) and the Transmitter Shift Register (TSR) are both empty. Bit 6 of the LSR is reset low when a character is loaded into the THR and remains low until the character is transferred out of SOUT. TEMT is not reset low by a CPU read of the LSR. In the FIFO Mode, when both the transmitter FIFO and shift register are empty this bit is set to one.

Bit 7 - This bit is always 0 in the VL16C450 Mode. In FIFO Mode, it is set when at least one of the following data errors is in the FIFO: Parity Error, Framing Error or Break Interrupt indication.

Note: The Line Status Register may be written. However, this function is intended only for factory test. It should be considered READ ONLY by applications software.

### FIFO CONTROL REGISTER

This write only register is at the same location as the IIR. It is used to enable and clear the FIFOs, set the trigger level of the RCVR FIFO, and select the type of DMA signaling.

Bit 0 - FIFO Enable. Enables both the XMIT and RCVR FIFOs. Programming of other FCR bits is enabled by setting bit 0 of the FCR = 1. The FIFO's operate in VL16C450 mode when bit 0 of the FCR = 0. All bytes in both FIFOs can be cleared automatically from the FIFOs when changing from FIFO Mode,bit 0 of FCR = 1, to VL16C450 Mode and vice versa.

Bit 1 - RCVR FIFO Reset. This bit clears all bytes in the RCVR FIFO and resets the counter logic to 0 when it is set to a one. It does not clear the receive shift register.

Bit 2 - XMIT FIFO Reset. This bit clears all bytes in the XMIT FIFO and resets the counter logic to 0 when it is set to a one. This does not clear the transmit shift register.

Bit 3 - DMA Mode Select. This bit controls the method of DMA signalling that will be used. If bit 3 of the FCR is a one, the part will operate in Mode 1. It will be in Mode 0 if bit 3 of the FCR is 0. These modes are only valid if bit 0 of the FCR is a one, and it directly affects the operation of the -RXRDY and -TXRDY pins.

Bits 4 and 5 - These two bits are reserved for future use

Bits 6 and 7 - These two bits are used for setting the trigger level for the RCVR FIFO interrupt.

| 7 | 6 | RCVR FIFO<br>Trigger Level (Bytes) |

|---|---|------------------------------------|

| 0 | 0 | 01                                 |

| 0 | 1 | 04                                 |

| 1 | 0 | 08                                 |

| 1 | 1 | 14                                 |

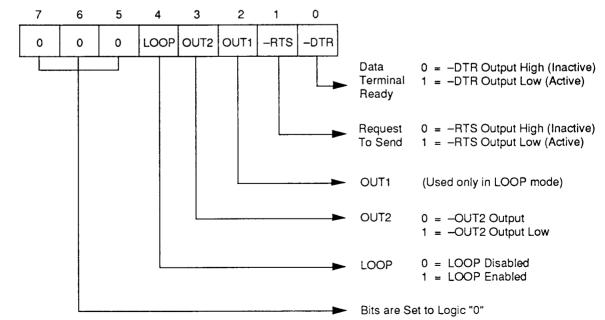

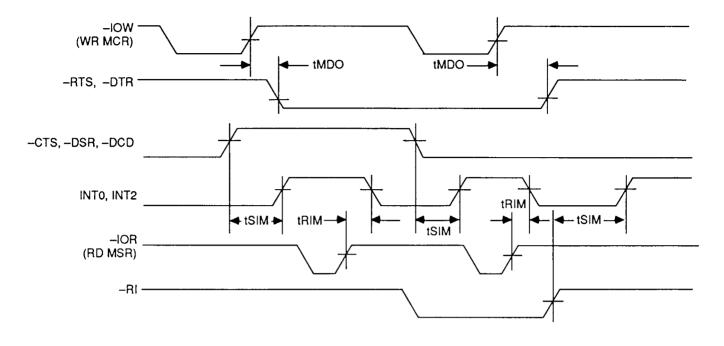

#### MODEM CONTROL REGISTER

The Modem Control Register (MCR) controls the interface with the modem or data set as described in Figure 3. MCR can be written and read. The –RTS and –DTR outputs are directly controlled by their control bits in this register. A high input asserts a low (true) at the output pins.

Bit 0 - When bit 0 of the MCR is set high, the -DTR output is forced low. When bit 0 of the MCR is reset low, the -DTR output is forced high. The -DTR output of the serial channel may be input into an inverting line driver in order to obtain the proper polarity input at the modem or data set.

Bit 1 - When bit 1 of the MCR is set high, the –RTS output is forced low. When bit 1 of the MCR is reset low, the –RTS output is forced high. The –RTS

#### FIGURE 3. MODEM CONTROL REGISTER

#### FIGURE 4. MODEM STATUS REGISTER

output of the serial channel may be input into an inverting line driver in order to obtain the proper polarity input at the modem or data set.

Bit 2 - Not used in normal operation. It is only seen in Loop-Back mode.

Bit 3 - When bit 3 of the MCR is set high, the -OUT2 output is forced low.

Bit 4 - Bit 4 of the MCR provides a local loopback feature for diagnostic testing of the channel. When bit 4 is set high, Serial Output (SOUT) is set to the marking (logic 1) state, and the receiver data input Serial Input (SIN) is disconnected. The output of the Transmitter Shift Register is looped back into the Receiver Shift Register input. The four modem control inputs (-CTS, -DSR, -DCD, and -RI) are disconnected. The four MCR bits (DTR, RTS, OUT1, and OUT2) are internally connected (in order) to bits 4 through 7 of the MSR. The modem control output pins are forced to their inactive state (high) on the VL16C552.

In the Diagnostic Mode, data transmitted is immediately received. This allows the processor to verify the transmit and receive data paths of the selected serial channel.

Interrupt control is fully operational. However, interrupts are generated by controlling the lower four MCR bits internally. Interrupts are not generated by activity on the external pins represented by those four bits.

Bits 7 through 5 are permanently set to logic 0.

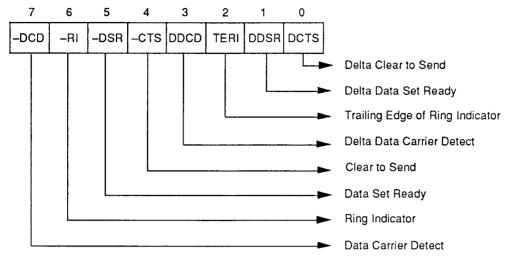

#### **MODEM STATUS REGISTER**

The Modem Status Register (MSR) provides the CPU with status of the modem input lines from the modem or peripheral devices. The MSR allows the CPU to read the serial channel modem signal inputs by accessing the data bus interface of the ACE in addition to the current status information, four bits of the MSR indicate whether the modem inputs have changed since the last reading of the MSR. The delta status bits are set high when a control input from the modem changes state, and reset low when the CPU reads the MSR.

The modem input lines are -CTS, -DSR, -RI, and -DCD. Bits 7 through 4 of the MSR are status indications of these lines. A status bit = 1 indicates the input is a low. A status bit = 0 indicates the input is high. If the modem status interrupt in the Interrupt Enable Register is enabled, bit 3 of the IER, an interrupt is generated whenever bits 3 through 0 of the MSR are set to a one. The MSR is a priority 4 interrupt. The contents of the Modem Status Register are described in Figure 4.

Bit 0 - Delta Clear to Send (DCTS). DCTS displays that the -CTS input to the serial channel has changed state since it was last read by the CPU.

Bit 1 - Delta Data Set Ready (DDSR). DDSR indicates that the –DSR input to the serial channel has changed state since the last time it was read by the CPU.

Bit 2 - Trailing Edge of Ring Indicator (TERI). TERI indicates that the -RI input to the serial channel has changed state from low to high since the last time it was read by the CPU. High to low transitions on -RI do not activate TERI.

Bit 3 - Delta Data Carrier Detect (DDCD). DDCD indicates that the –DCD input to the serial channel has changed state since the last time it was read by the CPU.

Bit 4 - Clear to Send (CTS). CTS is the complement of the –CTS input from the modem indicating to the serial channel that the modem is ready to receive data from the serial channel's transmitter output (SOUT). If the serial channel is in Loop Mode (bit 4 of the MCR = 1), bit 4 of the MSR reflects the value of RTS in the MCR.

Bit 5 - Data Set Ready (DSR). DSR is the complement of the –DSR input from the modem to the serial channel which indicates that the modem is ready to provide received data to the serial channel receiver circuitry. If the channel is in the Loop Mode (bit 4 of the MCR = 1), bit 5 of the MSR reflects the value of DTR in the MCR.

Bit 6 - Ring Indicator (RI). RI is the complement of the -RI input (pin 39). If the channel is in the Loop Mode (bit 4 of

the MCR = 1), bit 6 of the MSR reflects the value of -OUT1 in the MCR.

Bit 7 - Data Carrier Detect (DCD). Data Carrier Detect indicates the status of the Data Carrier Detect (–DCD) input. If the channel is in the Loop Mode (bit 4 of the MCR = 1), bit 7 of the MSR reflects the value of –OUT2 in the MCR.

Reading the MSR register will clear the delta modem status indications but has no effect on the other status bits.

For LSR and MSR, the setting of status bits is inhibited during status register read operations. If a status condition is generated during a read –IOR operation, the status bit is not set until the trailing edge of the read.

If a status bit is set during a read operation, and the same status condition occurs, that status bit will be cleared at the trailing edge of the read instead of being set again.

Note: In Loop Back Mode, when Modem Status interrupts are enabled, the -CTS, -DSR, -RI and -DCD input pins are ignored. However, a Modem Status interrupt may still be generated by writing to bits 7 through 4 of the MSR. This is considered a test mode only. Applications software should not write to the MSR.

#### **DIVISOR LATCHES**

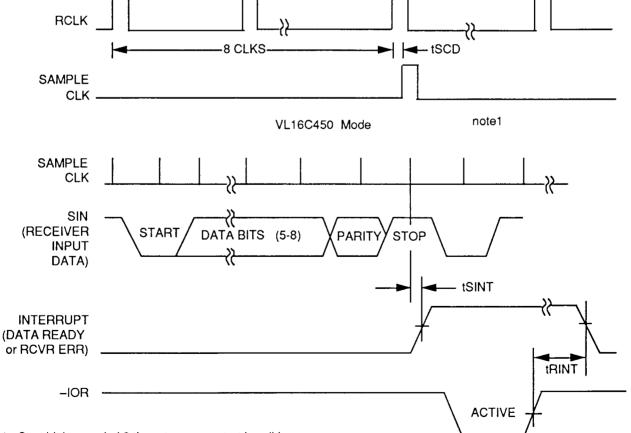

The ACE serial channel contains a programmable Baud Rate Generator (BRG) that divides the clock (DC to 8 MHz) by any divisor from 1 to 216-1 (see also BRG description). The output of the BRG is referred to as RCLK. The frequency of RCLK is 16x the data rate. The desired divisor number is reached through use of the following equation: [divisor # = clock + (baud rate x 16) = clock + data rate]. Two 8-bit divisor latch registers store the divisor in a 16bit binary format. These Divisor Latch registers must be loaded during initialization. Upon loading either of the Divisor Latches, a 16-bit baud counter is immediately loaded. This prevents long counts on initial load.

The BRG can use any of three different popular frequencies to provide standard baud rates. These frequencies are 1.8432 MHz, 3.072 MHz, and 8 MHz. With these frequencies, standard bit rates from 50 to 512K bps are available. Tables 5, 6, and 7 illustrate the divisors needed to obtain standard rates using

these three frequencies.

#### SCRATCHPAD REGISTER

Scratchpad Register is an 8-bit Read/ Write register that has no effect on either channel in the ACE. It is intended to be used by the programmer to hold data temporarily.

# INTERRUPT IDENTIFICATION REGISTER

In order to minimize software overhead during data character transfers, the serial channel prioritizes interrupts into four levels. The four levels of interrupt conditions are as follows:

- 1. Receiver Line Status (priority 1)

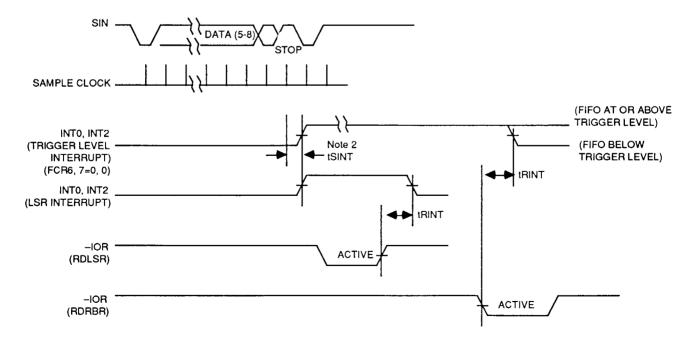

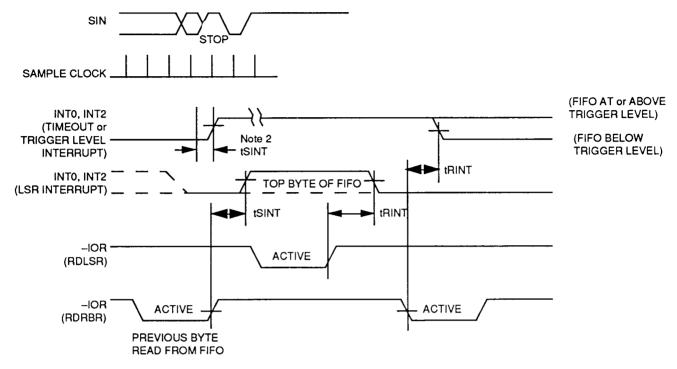

- Received Data Ready (priority 2) or character time-out

- Transmitter Holding Register Empty (priority 3)

- 4. Modem Status (priority 4)

Information indicating that a prioritized interrupt is pending and the type of interrupt is stored in the Interrupt Identification Register (IIR). The IIR indicates the highest priority interrupt pending. The contents of the IIR are indicated in Table 4 and are described as follows:

TABLE 4. INTERRUPT IDENTIFICATION REGISTER

| FIFO<br>Mode<br>Only | lde   | nterrupt<br>ntificatio<br>legister | on    |                   | Inte                               | rrupt Set and Reset Functions                                                                                                                                                                                     | d Reset Functions                                 |  |  |  |

|----------------------|-------|------------------------------------|-------|-------------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|--|--|--|

| Bit 3                | Bit 2 | Bit 1                              | Bit 0 | Priority<br>Level |                                    |                                                                                                                                                                                                                   | Interrupt Reset Control                           |  |  |  |

| 0                    | 0     | 0                                  | 1     | -                 | None                               | None                                                                                                                                                                                                              | _                                                 |  |  |  |

| 0                    | 1     | 1                                  | 0     | First             | Receiver Line Status               | OE, PE, FE or BI                                                                                                                                                                                                  | LSR Read                                          |  |  |  |

| 0                    | 1     | 0                                  | 0     | Second            | Received Data Available            | Receiver Data Available for 450 or 550 mode, or Trigger Level Reached for FIFO mode.                                                                                                                              | RBR Read or FIFO Drops<br>Below the Trigger Level |  |  |  |

| 1                    | 1     | 0                                  | 0     | Second            | Trigger Change Level<br>Indication | Minimum of One Character in the RCVR FIFO and No Character Input or Removed During a Time Period Depending on How Many Characters are in FIFO and What the Trigger Level is Set at (3.5 to 4.5 character times*.) | RBR Read                                          |  |  |  |

|                      |       |                                    |       |                   |                                    | * The exact time will be [(word length) x 7 - 2] x 8 + [(trigger level - number of characters) x 8 +1] RCLKS.                                                                                                     |                                                   |  |  |  |

| 0                    | 0     | 1                                  | 0     | Third             | THRE                               | THRE                                                                                                                                                                                                              | Read of IIR or THR Write                          |  |  |  |

| 0                    | 0     | 0                                  | 0     | Fourth            | Modem Status                       | -CTS, -DSR, -RI or -DCD                                                                                                                                                                                           | MSR Read                                          |  |  |  |

Bit 0 - Used to indicate whether an interrupt is pending. When bot 0 of the IIR is low, an interrupt is pending.

Bits 1 and 2 - Used to identify the highest priority interrupt pending as indicated in Table 4.

Bit 3 - This bit is always logic 0 when in the VL16C450 Mode. This bit is set along with bit 2 when in the FIFO Mode and a trigger change level interrupt is pending.

Bits 4 and 5 - These two bits are always logic 0.

Bits 6 and 7 - Bit 0 of the FCR = 1 sets these two bits.

#### **INTERRUPT ENABLE REGISTER**

The Interrupt Enable Register (IER) is used to independently enable the four serial channel interrupt sources which activate the interrupt (INT) output. All interrupts are disabled by resetting bits 3 through 0 of the IER. Interrupts are enabled by setting the appropriate bits of the IER high. Disabling the interrupt system inhibits the Interrupt Identification Register and the active (high) INT output. All other system functions operate in their normal manner, including the setting of the Line Status and Modem Status Registers. The contents of the IIER is described in Table 9 and following:

Bit 0 - When set to one, bit 0 of the IER enables the Received Data Available interrupt and the timeout interrupts in the FIFO Mode.

Bit 1 - When set to one, bit 1 of the IER enables the Transmitter Holding Register Empty interrupt.

Bit 2 - When set to one, bit 2 of the IER enables the Receiver Line Status interrupt.

Bit 3 - When set to one, bit 3 of the IER enables the Modern Status Interrupt.

Bits 4 through 7 - These four bits of the IER are logic 0.

### **MASTER RESET**

After power up, the ACE –RES input should be held low for five microseconds to reset the ACE circuits to an idle mode until initialization. A low on –RES causes the following:

- Initializes the transmitter and receiver internal clock counters.

- Clears the Line Status Register (LSR), except for Transmitter Shift Register Empty (TEMT) and Transmit Holding Register Empty (THRE), which are set. The Modem Control Register (MCR) is also cleared. All of the discrete lines, memory elements and miscellane-