# **CCD 133A 1024-Element High Speed** Linear Image Sensor

## **FEATURES**

- 1024 x 1 photosite array

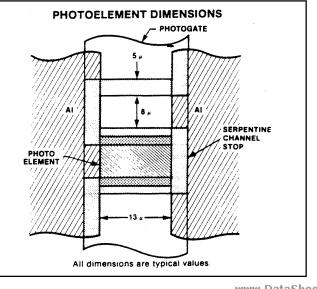

- 13 µm x 13 µm photosites on 13µm pitch

- High speed: up to 20 MHz data rate

- **Enhanced spectral response**

- Low dark signal

- **High responsivity**

- **On-chip clock drivers**

- Dynamic range typical: 7500:1

- Over 1 V peak-to-peak outputs

- Special selections available consult factory

## **GENERAL DESCRIPTION**

The CCD133A is a 1024-photoelement linear image sensor utilizing charge-coupled device technology. It is designed for visible and very-near-IR imaging applications such as page scanning, facsimile, optical character recognition, earth-resources-satellite telescopes, and other applications which require high resolution, high responsivity, high data rates, and high dynamic range.

The CCD133A has been improved and is pin-for-pin compatible with the CCD133 except for the deletion of the end-of-Scan Waveform (EOSout). The CCD133A has several new features which may be implemented

at the user's option by supplying input voltages and wave forms different than those required for standard CCD133-type operation.

Photoelement size is 13 µm (0.51mils) x 13 µm (0.51 mils) on 13  $\mu$ m (0.51 mils) centers. The devices are manufactured using Fairchild Imaging's advanced second-generation n-channel Isoplanar buried-channel technology.

www.DataSheet4U.com

DataShe

#### FUNCTIONAL DESCRIPTION

et4U.com

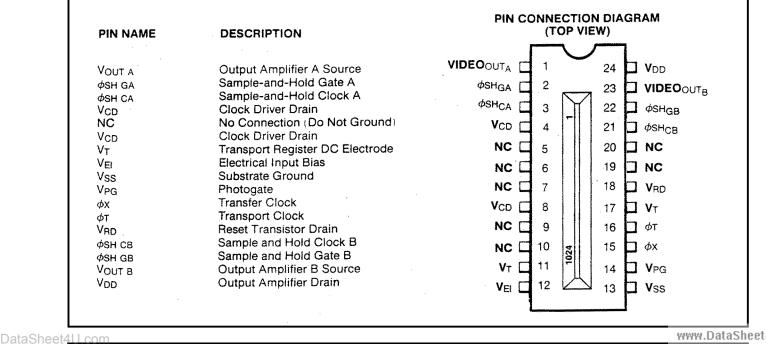

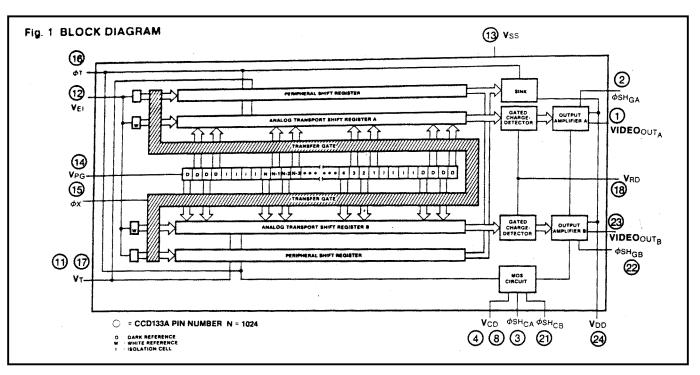

The CCD133A consists of the following functional elements illustrated in the Block Diagram and Circuit Diagram (Fig1.).

**Photosites:** A row of 1024 image sensor elements separated by a diffused channel stop and covered by a silicon dioxide surface passivation layer. Image photons pass through the transparent silicon creating hole-electron pairs. The photon generated electrons are accumulated in the photosites. The amount of charge accumulated in each photosite is a linear function of the incident illumination intensity and the integration period. The output signal will vary in an analog manner from a thermally generated background level at zero illumination to a maximum at saturation under bright illumination.

**Photogate:** The photogate structure, located at the edge of the photosites, provides a bias voltage for the photosites.

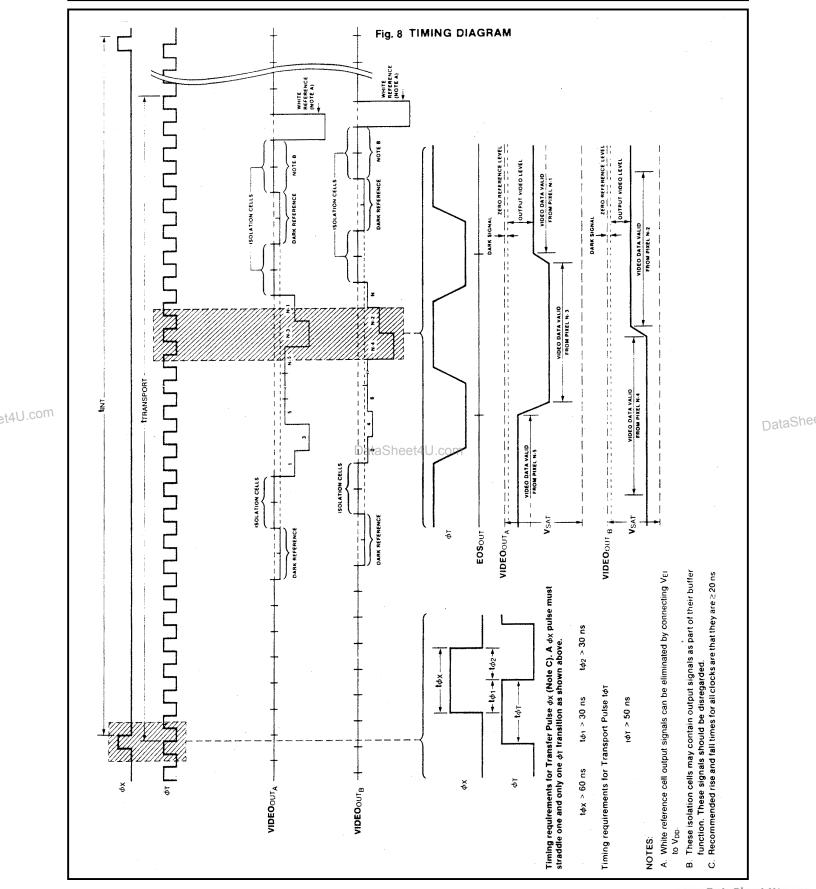

**Transfer Gate:** The transfer gate structure separates the outer edge of the photogates from the analog shift registers. Charge-packets generated and accumulated in the photosites are transferred into the transport analog shift registers whenever the transfer gate voltage goes "High". All odd-numbered charge packets are transferred into the "A" transport analog shift register: all even-numbered charge packets are transferred into the "B" transport analog shift register. The transfer gate also controls the input of charge from VEI into the white reference cells (described below). The time interval between successive transfer pulses determines the integration time.

**Analog Shift Registers:** Four 529-element analog shift registers transport charge towards the output end of the chip. the two inner registers, the transport registers, move the image generated charge packets serially to the two gated charge detectors and amplifiers. The two outer shift registers, the peripheral registers, accumulate charge generated at the chip periphery (by photons passing through unavoidable gaps in the light shield layer, etc.) and transport it to charge sinks. The primary shift register clock is  $\phi \tau$ . The complementary phase relationship of the secondary shift register clocks  $\overline{\phi \tau}$  and  $\overline{\phi \tau}$ , generated on-chip, provide alternate delivery of

charge packets from "A" and "B" shift registers to their amplifiers so that the original serial sequential string of video information may be easily demutiplexed off-chip.

#### Gated Charge Detectors & Reset Gates: Each transport ana-

log shift register delivers charge packets to a precharged diode. The change in diode potential is linearly proportional to the amount of charge delivered in the charge packet. This potential is applied to the input gate of a MOS transistor amplifier (see below), which linearly amplifies the input potential. The diode is reset to the reset drain bias voltage (VRD) by the reset gate structure. Reset occurs when both the internal reset clocks ( $\overline{\phi \tau}$  on the "A: side,  $\overline{\phi \tau}$  on the "B" side) are "High." Each side is reset just before the next charge packet is delivered from its respective transport analog shift register.

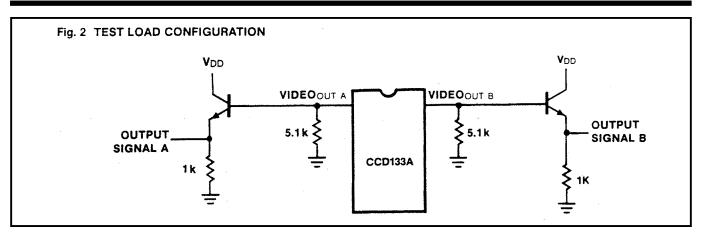

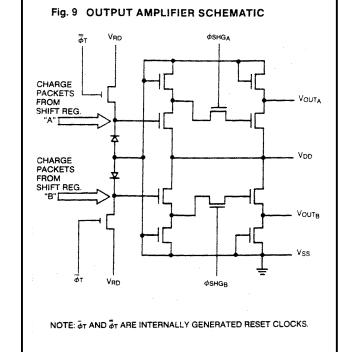

**Output Amplifiers and Sample-and Hold Gates:** Each sides' gated charge integrator drives the input of a two-stage linear MOStransistor amplifier. A schematic diagram of this circuit is shown in Figure 9 below. The two stages of each amplifier are separated by sample-and-hold gates. The output of the first stage is connected to the input of the second stage whenever the sample-and-hold gates is "High". The output of the second stage is connected to the VIDEOour pin. The sample-and-hold gates are switching MOS transistors: clocking these gates results in a sampled-and-held output, thus eliminating the reset clock feedthrough. When on-chip sample-and-hold is used, pin 2 is to be tied to pin 3 and pin 21 is to be tied to pin 22. Offchip sample-and-hold operation can be disabled by tying pins 2 and 22. The sample-and-hold operation can be disabled by tying pins 3 and 21 should be left unconnected.

**Clock Driver Circuits:** Two MOSFET clock-driver circuits onchip allow sample-and-held operation of the CCD133A with only two externally-supplied clocks: the square-wave primary shift register transport clock  $\phi T$ , which determines the output data rate, and the transfer clock  $\phi X$ , which determines the integration time.

Dark Reference Circuitry: Four additional sensing elements at

DataSheet4

2

DataShe

both ends of the 1024-photosite array are covered by opaque metallization. These "Dark Reference Cells" provide four charge packets (two on each side) at each end of the serial video output which indicate the typical dark (non-illuminated) signal level. These cells may be used as inputs to external DC restoration.

#### **DEFINITION OF TERM**

**Charge-Coupled Device** — A Charge-coupled device is a semiconductor device in which finite isolated charge-packets are transported from one position in the semiconductor to an adjacent position by sequential clocking of an array of gates. The charge-packets are minority carriers with respect to the semiconductor substrate.

et4U.com

**Transfer Clock**  $\phi x$  — The transfer clock is the voltage waveform applied to the transfer gate to move the accumulated charge from the image sensor elements to the CCD transport shift registers to Sheet 4 Udetails of definition.)

**Transport Clock**  $\phi T$  — The transport clock is the clock applied to the gates of the CCD transport shift registers to move the charge-packets received from the image sensor elements to the gate charge-detector/amplifiers.

**Sample-and-Hold Clock** ( $\phi$ SHCA,  $\phi$ SHCB) — The voltage waveform applied to the sample-and-hold gates in the output amplifiers to create a continuous sampled video signal at the output. The sample-and-hold feature may be defeated by connecting  $\phi$ SHGA and  $\phi$ SHGA to VDD.

**Isolation Cell** — A site on-chip producing an element in the video output that serves as a buffer between valid video data and dark reference signals. The output from an isolation cell contains no valid information and should be ignored.

**Dynamic Range** — The saturation exposure divided by the rms temporal noise equivalent exposure. Dynamic range is sometimes defined in terms of peak-to-peak noise. To compare the two definitions a factor of four to six is generally appropriate in that peak-to-peak noise is approximately equal to four to six times rms noise.

**RMS Noise Equivalent Exposure** — The exposure level that gives an output signal to the rms noise level at the output in the dark.

**Saturation Exposure** — The minimum exposure level that will provide a saturation output signal. Exposure is equal to the light intensity times the photosites integration time.

**Charge Transfer Efficiency** — Percentage of valid charge information that is transferred between each successive stage of the transport registers.

**Responsivity** — The output signal voltage per unit exposure for a specified spectral type of radiation. Responsivity equals output voltage divided by exposure.

**Total Photoresponse Non-uniformity** — The difference of the response levels of the most and the least sensitive element under uniform illumination. Measurement of PRNU excludes first and last elements.

**Dark Signal** — The output signal in the dark caused by thermally generated electrons that is a linear function of the integration time and highly sensitive to temperature. (See accompanying photos for details of definition.)

**Saturation Output Voltage** — The maximum usable signal output voltage. Charge transfer efficiency decreases sharply when the saturation output voltage is exceeded.

**Integration Time** — The time interval between the falling edge of any two successive transfer pulses ( $\phi x$ ). The integration is the time allowed for the photosites to collect charge.

**Pixel -** A picture element (photosite).

DataSheet4

www.DataSheet4U.com

Fairchild Imaging, Inc., 1801 McCarthy Blvd., Milpitas, CA 95035 • (800)325-6975 • (408) 433-2500

З

ABSOLUTE MAXIMUM RATINGS Above which useful life may be impaired Storage Temperature Operating Temperature See Curves CCD133A Pins 2, 3, 4, 8, 11, 12, 14, 15, 16, 17, 18, 21, 22, 24 Pin 13 Pins 5, 6, 7, 9, 10, 19, 20 Pins 1, 23

-25°C to +125°C -25°C to +70°C -0.3V to +18V 0V NC See Caution Note

CAUTION NOTE: These devices have limited built-in gate protection. It is recommended that static discharge be controlled and minimized. Care must be taken to avoid shorting pins Vout A&B to Vss or Vpb during operation of these devices. Shorting these pins temporarily to Vss or Vpb may destroy the output amplifiers.

| SYMBOL | CHARACTERISTIC                        | RANGE                                 |      |      |       |            |

|--------|---------------------------------------|---------------------------------------|------|------|-------|------------|

|        |                                       | MIN                                   | TYP  | MAX  | UNITS | CONDITIONS |

| Vcd    | Clock Driver Drain Supply Voltage     | 13.5                                  | 14   | 15.5 | v     | Note 3     |

| lco    | Clock Driver Drain Supply Current     |                                       | 7.0  | 15   | mA    |            |

| VDD    | Output Amplifier Drain Supply Voltage | 13.5                                  | 14   | 15.5 | V     | Note 3     |

| ICD    | Output Amplifier Drain Supply Current |                                       | 15   | 25   | mA    |            |

| Vpg    | Photogate Bias Voltage                | 8.5                                   | 9.0  | 9.5  | V     |            |

| VT     | DC Electrode Bias Voltage             | 5.5                                   | 6.0  | 6.5  | V     | Note 4     |

| VEI    | Electrical Input Bias Voltage         | Anti                                  | 14.0 |      | v     | Note 5     |

| Vss    | Substrate (Ground)                    | an bhrainne, bri e , chan — bhlia ter | 0.0  |      | V     | Note 6     |

| VRD    | Reset Drain Supply                    | 12                                    | 13   | 15.5 | V     | Note 18    |

| CLOCK CHA | RACTERISTICS: TP = 25° C (Note 1 T) | Typical values should be used for optimum performance |       |  |       |            |  |  |

|-----------|-------------------------------------|-------------------------------------------------------|-------|--|-------|------------|--|--|

|           |                                     |                                                       | RANGE |  | 1     |            |  |  |

| SYMBOL    | CHARACTERISTIC                      |                                                       | TVD   |  | UNITS | CONDITIONS |  |  |

| SYMBOL        | CHARACTERISTIC                  | MIN | TYP  | MAX | UNITS | CONDITIONS |

|---------------|---------------------------------|-----|------|-----|-------|------------|

| νφχί.<br>νφτί | Transfer & Transport Clock LOW  | 0.0 | 0.3  | 0.7 | V.    | Notes 6, 7 |

| Vфхн.<br>Vфт, | Transfer & Transport Clock HIGH | 11  | 11.5 | 12  | V     | Note 7     |

| fdata max     | Maximum Output Data Rate        | 12  | 20   |     | MHz   | Notes 8, 9 |

NOTES:

1. Tp is defined as the package temperature, measured on a copper block in good thermal contact with the entire backside of the package.

2. ALL Vss PINS MUST BE GROUNDED. All NC pins must be left unconnected.

3. VDD pins may be connected to  $V_{\text{CD}}$  and/or  $V_{\text{RD}}$  pins.

4. V<sub>T</sub> = 0.55 φx HIGH = 0.55 φT HIGH

5. White reference signal can be enabled by connecting  $V_{EI}$  to a voltage less than  $V_{DD}$ .  $V_{EI} = 6_V$  will typically produce a white reference signal of 80 ± 20% of the saturation output voltage.

6. Negative transients on any clock pin going below 0.0 volts may cause charge injection, which results in an increase in apparent DS,

7. C  $\phi_T$  = 360 pF; C  $\phi_X$  = 80 pF.

All clock rise and fall times should be > 30ns.

8. The minimum clock frequency is limited by increases in dark signal.

9.  $f_{DATA} = 2 (f \phi_T)$

OCLI WBHM = Optical Coating Laboratory, Inc. Wide Band Hot Mirror.

CTE is the measurement for a one stage transfer, measured with sample & hold disabled.

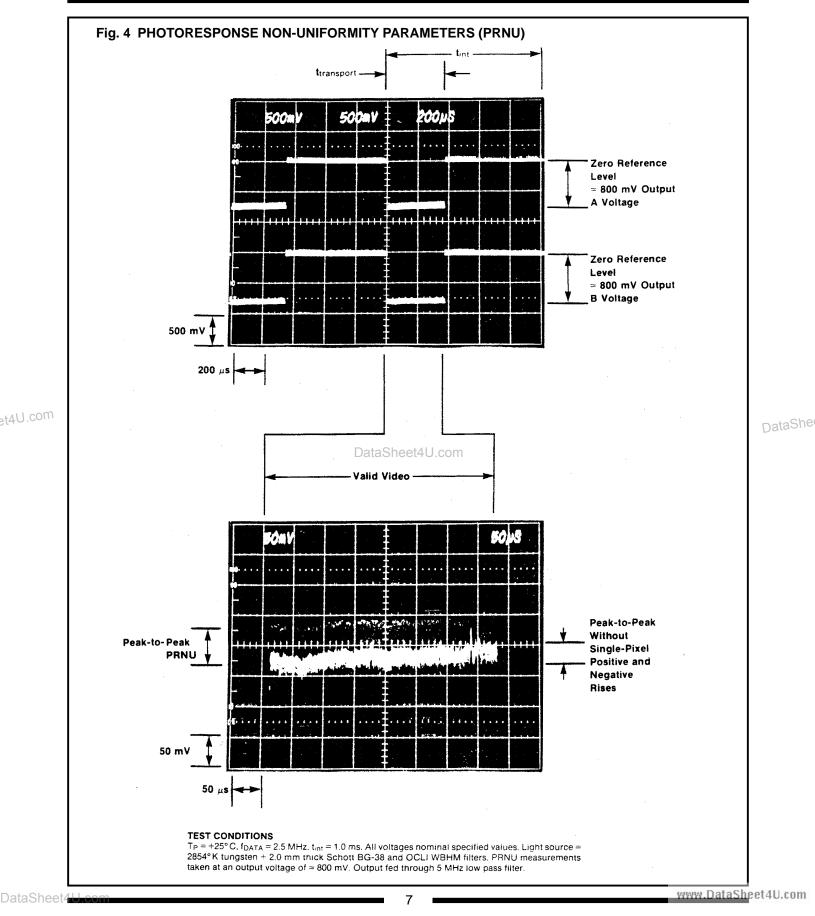

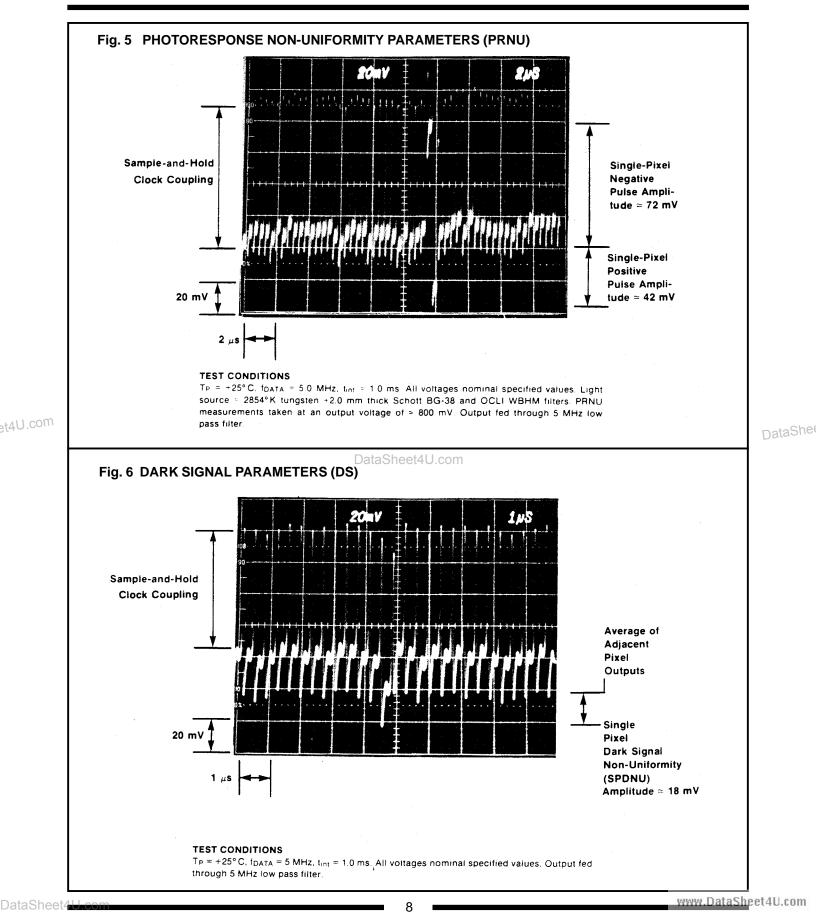

12. See photographs for PRNU definitions.

13. Video mismatch is the difference in ac amplitudes between V<sub>OUT A</sub> and V<sub>OUT B</sub> under uniform illumination. It can be eliminated by attenuation/amplification of one of the video outputs.

14. DC mismatch is the difference in dc output level  $V_{\rm O}$  between  $V_{\rm OUT \ A}$  and  $V_{\rm OUT \ B}$

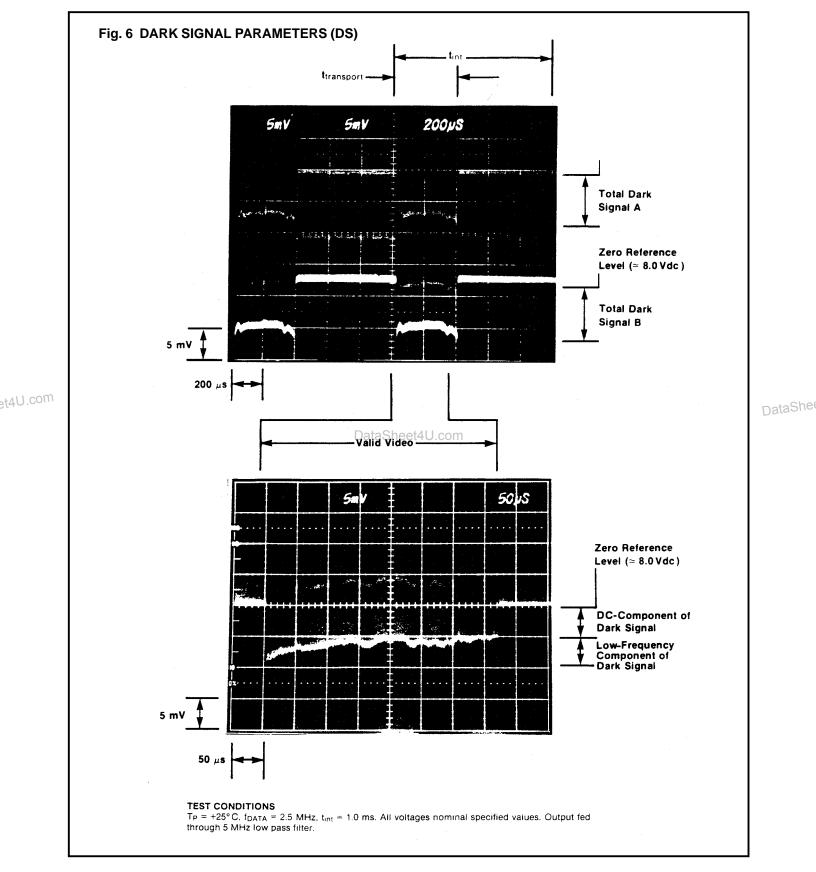

15. See photographs for dark signal definitions.

16. Dark signal component approximately doubles for every 5-10 °C in Tp.

17. Each SPDSNU is measured from the DS level adjacent to the base of the SPDSNU. The SPDSNU approximately doubles for every 5-15 °C in Tp.

18. VRD voltages in the lower range improves amplifier linearity.

DataSheet4U.com

www.DataSheet4U.com

DataShe

## AC CHARACTERISTICS: (Note 1

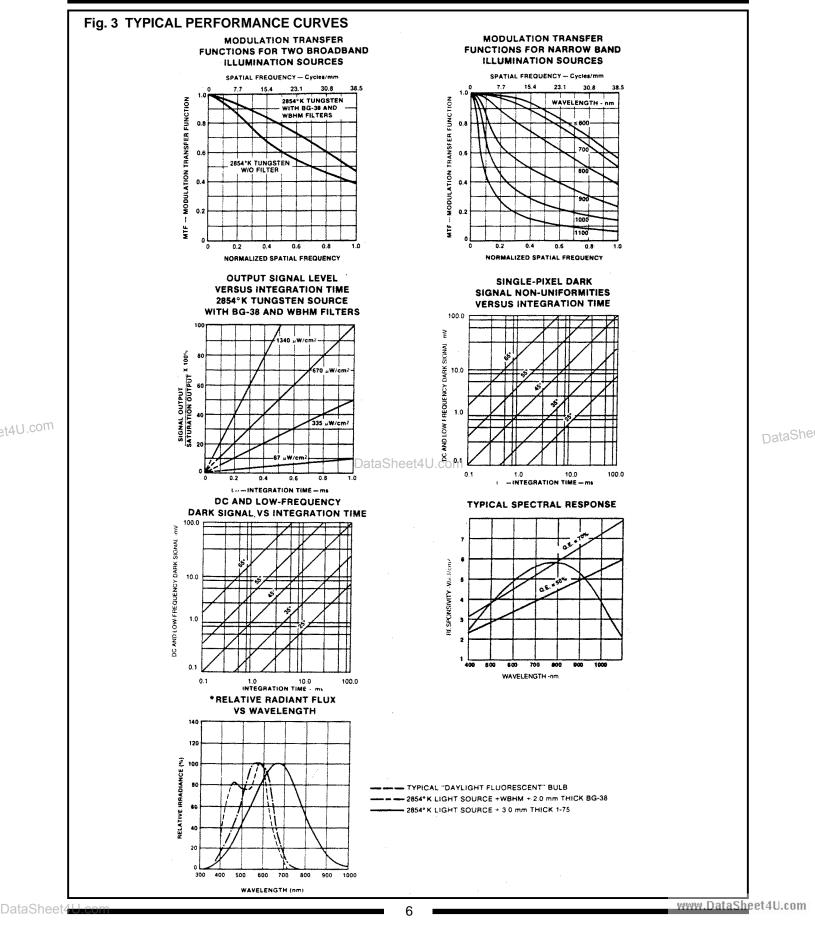

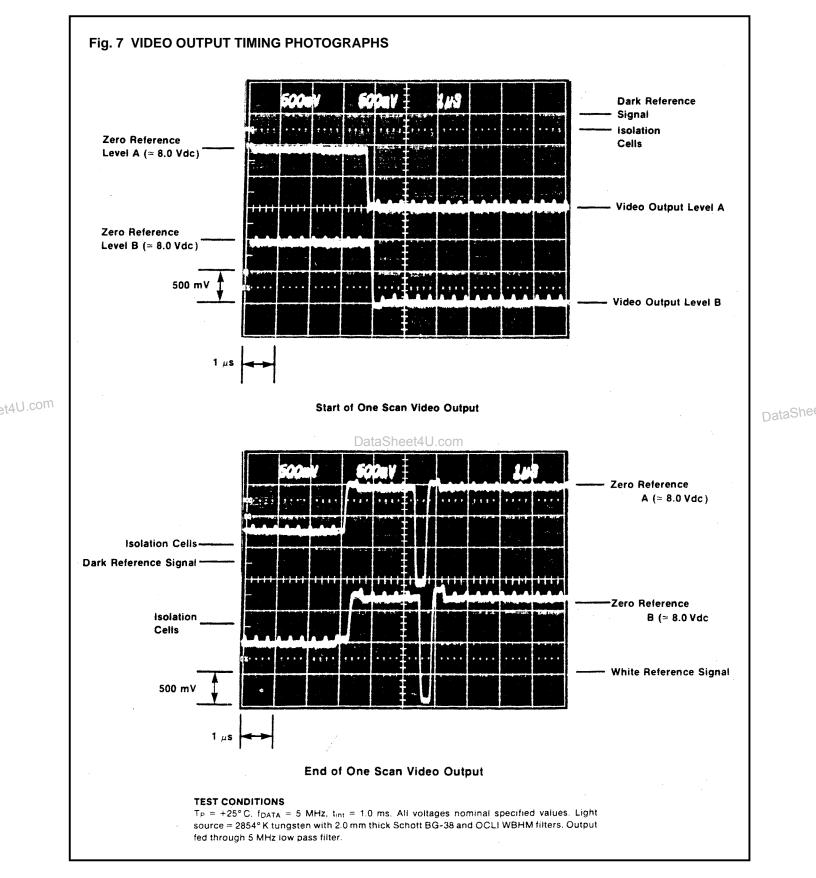

$T_P = 25^{\circ}$  C,  $f_{DATA} = 5.0$  MHz,  $t_{int} = 1.0$  ms, Light Source<sup>\*</sup> = 2854° K - 2.0 mm thick Schott BG-38 and OCLI WBHM filters All tests done using "Test Load Configuration."

All operating voltages nominal specified values

| SYMBOL | CHARACTERISTIC                                           | RANGE   |            |            |          |            |

|--------|----------------------------------------------------------|---------|------------|------------|----------|------------|

|        |                                                          | MIN     | ТҮР        | MAX        | UNITS    | CONDITIONS |

| DR     | Dynamic Range (relative to                               |         | 1500:1     |            |          |            |

|        | peak-to-peak noise                                       |         | 7500:1     | -          |          |            |

| NEE    | RMS Noise Equivalent Exposure                            |         | 0.00007    |            | μJ/cm²   |            |

| SE     | Saturation Exposure                                      |         | 0.50       |            | μJ/cm²   |            |

| CTE    | Charge Transfer Efficiency                               | 0.99995 | 0.999999   |            |          | Note 11    |

| Vo     | Output DC Level                                          | 4.0     | 8.0        | 11.0       | V        | 1          |

| Z      | Output Impedance                                         |         | 0.75       | 1.5        | kΩ       |            |

| Ρ      | On-Chip Power Dissipation<br>Clock Drivers<br>Amplifiers |         | 100<br>170 | 215<br>325 | mW<br>mW |            |

| N      | Peak-to-Peak Temporal Noise                              |         | 1.0        |            | mV       |            |

## PERFORMANCE CHARACTERISTICS: (Note 1)

$T_P = 25^{\circ}$  C,  $f_{DATA} = 5.0$  MHz,  $t_{int} = 1.0$  ms, Light Source<sup>\*</sup> = 2854° K + 2.0 mm thick Schott BG-38 and OCLI WBHM filters

All operating voltages nominal specified values

| SYMBOL | CHARACTERISTIC Da                                                  |                | RANGE |     |          |             |

|--------|--------------------------------------------------------------------|----------------|-------|-----|----------|-------------|

|        |                                                                    | DataSheet4U.co | ТҮР   | MAX | UNITS    | CONDITION   |

| PRNU   | Photoresponse Non-<br>Uniformity:                                  |                |       |     |          | Note 12     |

|        | Peak-to-Peak                                                       |                | 60    | 160 | mV       |             |

|        | Peak-to-Peak Without<br>Single-Pixel Positive &<br>Negative Pulses |                | 40    |     | mV       |             |

|        | Single-Pixel Positive Pulses                                       |                | 10    |     | mV       |             |

|        | Single-Pixel Negative Pulses                                       |                | 20    |     | mV       |             |

| MVIDEO | Video Mismatch                                                     |                | 10    | 100 | mV       | Note 13     |

| Mpc    | DC Mismatch                                                        |                | 0.5   | 2.0 | V        | Note 14     |

| DS     | Dark Signal:                                                       |                |       |     |          | Note 15, 16 |

|        | DC Component                                                       |                | 1.0   | 2.0 | mV       |             |

|        | Low Frequency Component                                            |                | 1.0   | 2.0 | mV       |             |

| SPDSNU | Single-Pixel DS Non-Uniformity                                     |                | 1.0   | 2.0 | mV       | Note 17     |

| R      | Responsivity                                                       | 2.5            | 3.0   | 7.5 | V/µJ/cm² |             |

| VSAT   | Saturation Output Voltage                                          | 1.0            | 1.5   | 2.5 | V        |             |

Laboratory, Inc. Wide Band Hot Mirro

\*\* PRNU measurements include both register outputs but exclude the outputs from the first and last elements of the array. Also excluded from the measurement are video and dc mismatch.

All PRNU measurements taken at 800 mV output level using an f/5.0 lens.

The "f" number is defined as the distance from the lens to the array divided by the diameter of the lens aperture. As the "f" number increases, the resulting more highly collimated light causes the package window imperfections to dominate and increase PRNU. A lower "f" number results in less collimated light causing device photosite blemishes to dominate the PRNU.

DataSheet4

www.DataSheet4U.com

DataShe

5 Fairchild Imaging, Inc., 1801 McCarthy Blvd., Milpitas, CA 95035 • (800)325-6975 • (408) 433-2500

et4U.com

DataSheet4U.com

9

www.DataSheet4U.com

DataSheet4U.com

10

www.DataSheet4U.com

DataSheet4U.com

www.DataSheet4U.com

Fairchild Imaging, Inc., 1801 McCarthy Blvd., Milpitas, CA 95035 • (800)325-6975 • (408) 433-2500

## CCD133A

### **DEVICE CARE AND OPERATION**

Glass may be cleaned by saturating a cotton swab in alcohol and lightly wiping the surface. Rinse off the alcohol with deionized water. Allow the glass to dry, preferably by blowing with filtered dry N<sub>2</sub> or air.

It is important to note in design and applications considerations that the devices are very sensitive to thermal conditions. The dark signal dc and low frequency components approximately double for every 5° C temperature increase and single-pixel dark signal non-uniformities approximately double for every 8° C temperature increase. The devices may be cooled to achieve very long integration times and very low light level capability.

#### **ORDER INFORMATION**

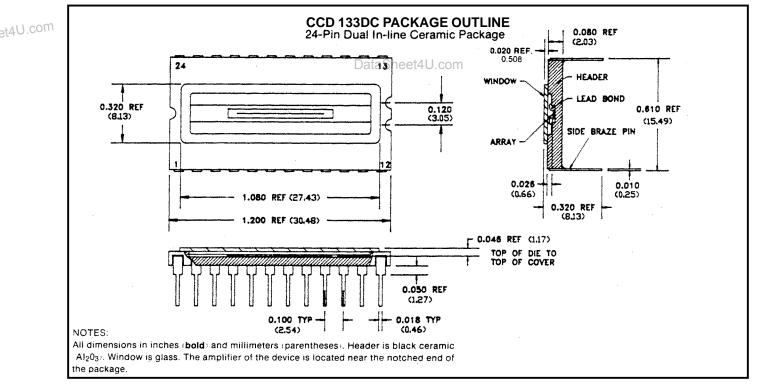

Order CCD133ADC where "D" stands for a ceramic package and "C" for commercial temperature range.

Also available are printed circuit boards that include all the necessary clocks, logic drivers and video amplifiers to operate the CCD133A. The boards are fully assembled and tested and require only one power supply for operation (+20V). The printed circuit board order codes are CCD133DB. The CCD143A and CCD133A can be operated in the same printed circuit board. The 24 pin CCD133A can be placed at the center of the 28 pin socket on the circuit board. (Note: the series resistors between the clock drivers and the CCD  $\phi_X$  and  $\phi_T$  pins have to be adjusted for each device type.)

### WARRANTY

Within twelve months of delivery to the end customer, Fairchild Imaging will repair or replace, at our option, any Fairchild Imaging camera product if any part is found to be defective ion materials or workmanship. Contact factory for assignment of warranty return number and shipping instructions to ensure prompt repair or replacement.

### CERTIFICATION

Fairchild Imaging certifies that all products are carefully inspected and tested at the factory prior to shipment and will meet all requirements of the specification under which it is furnished.

DataSheet4U.com

12

www.DataSheet4U.com