# High current PROFET<sup>TM</sup> BTS50060-1TEA

Smart High-Side Power Switch One Channel

# Datasheet

Rev. 1.1, 2011-04-13

Automotive

| 1                                                                                                                                                                    | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 3                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| 2                                                                                                                                                                    | Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 4                                                                        |

| 3<br>3.1<br>3.2<br>3.3                                                                                                                                               | Pin Configuration Pin Assignment Pin Definitions and Functions Definition of Terms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 5<br>. 5                                                                 |

| <b>4</b> 4.1 4.2 4.3                                                                                                                                                 | General Product Characteristics  Absolute Maximum Ratings  Functional Range  Thermal Resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 6<br>. 9                                                                 |

| 5<br>5.1<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.2<br>5.3<br>5.3.1<br>5.3.2<br>5.3.3<br>5.3.4<br>5.3.5<br>5.3.6<br>5.3.7<br>5.4<br>5.4.1<br>5.4.2<br>5.4.3<br>5.5.4 | Functional Description  Power Stage  Switching a Resisitve Load  Switching an Inductive Load - Infineon® SMART CLAMPING  Switching a Capacitive Load  Inverse Load Current Operation  Input Circuit  Protection Functions  Protection by Over Current Shutdown  Protection by Over Temperature Shutdown  Infineon® INTELLIGENT LATCH  Reverse Polarity Protection  Protection during Loss of Ground  Protection during Loss of Load or Loss of V <sub>S</sub> Condition  Protection during ESD or Over Voltage Condition  Diagnosis Functions  Sense Output  Enhancing Accuracy of the Sense Output by End of Line Calibration  Short-to-Battery detection / Open Load Detection in OFF state  Undervoltage Shutdown & Restart | 12<br>12<br>13<br>13<br>14<br>15<br>16<br>16<br>17<br>17<br>18<br>19<br>21 |

| 6<br>6.1<br>6.2<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4                                                                                                                  | Electrical Characteristics BTS50060-1TEA  Electrical Characteristics Table  Parameter Dependencies  Power Stage  Input Circuit  Protection Functions  Diagnosis Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 23<br>27<br>27<br>30<br>31                                                 |

| <b>7</b><br>7.1                                                                                                                                                      | Application Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                            |

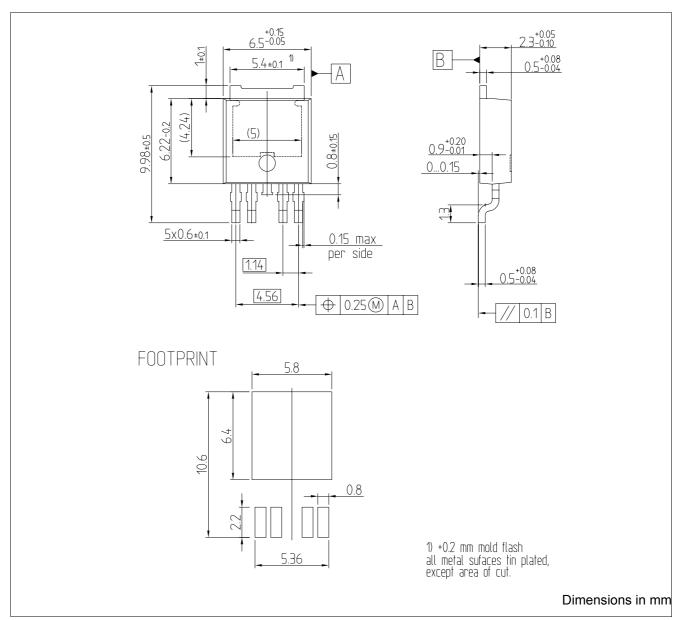

| 8                                                                                                                                                                    | Package Outlines and Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 37                                                                         |

| 9                                                                                                                                                                    | Revision History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 38                                                                         |

# Smart High-Side Power Switch One Channel

BTS50060-1TEA

#### 1 Overview

#### **Application**

- All types of resistive, inductive and capacitive loads

- Most suitable for driving loads with PWM frequency from 0 Hz (DC operation) up to 1kHz and above

- · Drives loads with high inrush current, e.g. PTC heaters

- Replaces electromechanical relays, fuses and discrete circuits

#### **Features**

- Reduced switching losses

- · Optimized for EMC low emission, high immunity

- Optimized for PWM frequencies of approx. 100Hz

- 3.3V and 5V compatible logic inputs

- Advanced analog load current sense signal supporting easy calibration for very high accuracy

- Embedded diagnosis features (e.g. open load detection at ON and OFF)

- Embedded protection functions (e.g. over current shutdown, over temperature shutdown)

- Infineon<sup>®</sup> INTELLIGENT LATCH

- · Green Product (RoHS compliant)

- AEC Qualified

#### **Description**

Embedded in a PG-TO252-5-311 package, the BTS50060-1TEA is a  $6m\Omega$  single channel Smart High-Side Power Switch. It is based on Smart power chip on chip technology with a P-channel vertical power MOSFET, providing protective and diagnostic functions. It is specially designed to drive loads in the harsh automotive environment.

Table 1 Product Summary

| Parameter                                        | Symbol                  | Values     |  |

|--------------------------------------------------|-------------------------|------------|--|

| Range of typical PWM frequencies                 | $f_{PWM}$               | 0 Hz 1 kHz |  |

| Maximum On-state Resistance at $T_j$ = 150 °C    | R <sub>DS(ON)_150</sub> | 12 mΩ      |  |

| Nominal Supply Voltage Range for Operation       | $V_{S(NOM)}$            | 6 V 19 V   |  |

| Nominal Load Current (DC operation)              | $I_{L(NOM)}$            | 16.5 A     |  |

| Typical Load Current at 100Hz                    | $I_{L(100 Hz)}$         | 13.5 A     |  |

| Typical Stand-by Current at $T_j$ = 25 °C        | $I_{S(OFF)}$            | 5 μΑ       |  |

| Minimum short circuit current shutdown threshold | $I_{L(SC)}$             | 60 A       |  |

| Maximum reverse battery voltage                  | $-V_{\mathrm{S(REV)}}$  | 16 V       |  |

| Туре          | Package        | Marking |

|---------------|----------------|---------|

| BTS50060-1TEA | PG-TO252-5-311 | S50060A |

PG-TO252-5-311

**Block Diagram**

#### **Embedded Protection functions**

- Infineon<sup>®</sup> INTELLIGENT LATCH resettable latch resulting from protective switch OFF

- Over current protection by short-circuit shutdown

- Overload protection by over-temperature shutdown

- Infineon® SMART CLAMPING

#### **Embedded Diagnosis functions**

- Advanced analog load current sense signal with defined positive offset current; enabling load diagnosis, e.g. open load at ON, overload

- Providing defined fault signal

- · Open Load at OFF detection

- · Short-to-battery detection

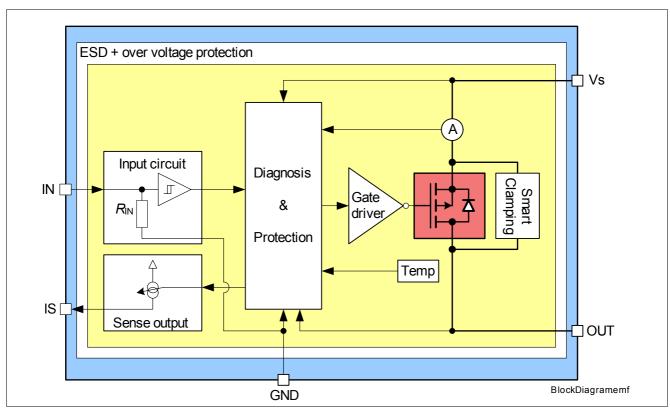

# 2 Block Diagram

Figure 1 Block Diagram of BTS50060-1TEA

For a Diagram of Diagnosis & Protection block, please see Figure 14.

**Pin Configuration**

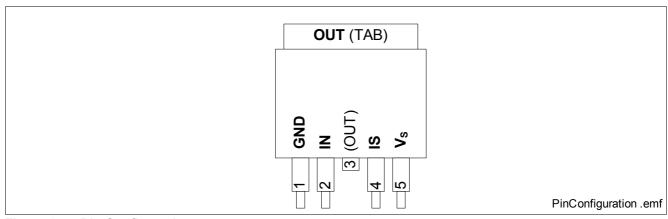

# 3 Pin Configuration

## 3.1 Pin Assignment

Figure 2 Pin Configuration

#### 3.2 Pin Definitions and Functions

| Pin                  | Symbol | Function                                                                                                                                                      |

|----------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                    | GND    | Ground; Ground connection for control chip.                                                                                                                   |

| 2                    | IN     | <b>Input</b> ; Digital 3.3 V and 5 V compatible logic input; activates power switch if set to HIGH level; Includes internal pull-down resistor $R_{\rm IN}$ . |

| Tab; 3 <sup>1)</sup> | OUT    | Output; Protected high side power output                                                                                                                      |

| 4                    | IS     | Sense; Provides analog sense current signal and defined fault signal.                                                                                         |

| 5                    | Vs     | Supply Voltage; Positive supply voltage for Logic and Power Stage <sup>2)</sup>                                                                               |

- 1) Tab and pin 3 are internally connected. Pin 3 is cut.

- 2) PCB traces have to be designed to withstand maximum current occuring in the application.

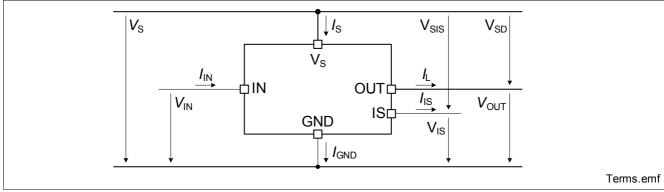

#### 3.3 Definition of Terms

Figure 3 shows all terms used for currents and voltages in this data sheet, with associated convention for positive values.

Figure 3 Definition of currents and voltages

# 4 General Product Characteristics

# 4.1 Absolute Maximum Ratings

Table 2 Absolute Maximum Ratings 1)

| Parameter                                                                         | Symbol                   | Va           | lues              | Unit | Note /                                                                                                                                         | Number |

|-----------------------------------------------------------------------------------|--------------------------|--------------|-------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------|--------|

|                                                                                   |                          | Min.         | Max.              |      | <b>Test Condition</b>                                                                                                                          |        |

| Supply voltages                                                                   |                          | +            | *                 | *    |                                                                                                                                                | •      |

| Supply Voltage                                                                    | $V_{S}$                  | -0.3         | 28                | V    | _                                                                                                                                              | P_4.1  |

| Reverse Polarity Voltage on pin GND, IS                                           | $ -V_{\mathrm{S(REV)}} $ | 0            | 16                | V    | 2), 3)                                                                                                                                         | P_4.2  |

| Supply voltage for short circuit protection                                       | $V_{\mathrm{BAT(SC)}}$   | 0            | 28                | V    | $R_{\rm ECU} = 20 {\rm m}\Omega,$ $R_{\rm Cable} = 6 {\rm m}\Omega/{\rm m},$ $L_{\rm Cable} = 1 {\rm \mu H/m},$ $l=0$ or 5m, see Chapter 5.3.1 | P_4.3  |

| Supply voltage for load dump protection                                           | $V_{S(LD)}$              | -            | 45                | V    | $R_{\rm l} = 2 \Omega^{5)}$ ,<br>$R_{\rm L} = 1.0 \Omega$ ,<br>$t_{\rm d} = 400 {\rm ms}$                                                      | P_4.4  |

| Short circuit capability                                                          |                          |              |                   |      |                                                                                                                                                |        |

| Short circuit cycle capability                                                    | $n_{RSC1}$               | _            | 1 E6<br>(Grade A) | _    | 4)6)                                                                                                                                           | P_4.21 |

| IN + IS + GND pin                                                                 |                          |              |                   |      |                                                                                                                                                |        |

| Voltage at IN pin                                                                 | $V_{IN}$                 | -0.3         | 6                 | V    | _                                                                                                                                              | P_4.5  |

| Current through IN pin                                                            | $I_{IN}$                 | -2           | 2                 | mA   | t < 2min                                                                                                                                       | P_4.6  |

| Voltage at IS pin                                                                 | $V_{IS}$                 | -0.3         | $V_{S}$           | V    | _                                                                                                                                              | P_4.7  |

| Current through IS pin                                                            | $I_{IS}$                 | -2           | 10                | mA   | _                                                                                                                                              | P_4.8  |

| Current through GND pin                                                           | $I_{GND}$                | -2           | 10                | mA   | _                                                                                                                                              | P_4.9  |

| Power stage                                                                       | 1                        |              | -11               |      |                                                                                                                                                | •      |

| Load current                                                                      | $I_{L}$                  | $-I_{L(SC)}$ | $I_{L(SC)}$       | Α    | _                                                                                                                                              | P_4.10 |

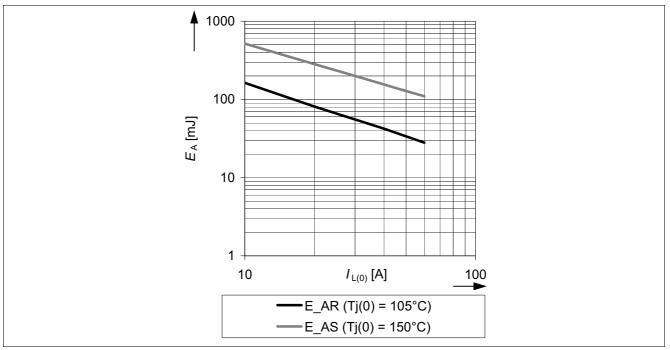

| Maximum energy dissipation for switching OFF an inductive load - single pulse     | $E_{AS}$                 | _            | 280               | mJ   | $V_{\rm S}$ = 13.5V<br>$I_{\rm L(0)}$ = 20A<br>$T_{\rm j(0)}$ = 150°C<br>See Figure 4 and<br>Chapter 5.1.2                                     | P_4.11 |

| Maximum energy dissipation for switching OFF an inductive load - repetitive pulse | $E_{AR}$                 | -            | 82                | mJ   | $V_{\rm S}$ = 13.5V<br>$I_{\rm L(0)}$ = 20A<br>$T_{\rm j(0)}$ = 105°C<br>See Figure 4 and<br>Chapter 5.1.2                                     | P_4.13 |

| Temperatures                                                                      | •                        |              |                   |      |                                                                                                                                                |        |

| Junction Temperature                                                              | $T_{j}$                  | -40          | 150               | °С   | _                                                                                                                                              | P_4.14 |

#### Table 2 Absolute Maximum Ratings (cont'd)<sup>1)</sup>

$T_j$  = -40°C to 150°C; all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                                                             | Symbol            | Val  | ues  | Unit | Note /<br>Test Condition | Number |

|---------------------------------------------------------------------------------------|-------------------|------|------|------|--------------------------|--------|

|                                                                                       |                   | Min. | Max. |      |                          |        |

| Dynamic temperature increase while switching                                          | $\Delta T_{ m j}$ | -    | 60   | K    | _                        | P_4.15 |

| Storage Temperature                                                                   | $T_{stg}$         | -55  | 150  | °C   | _                        | P_4.16 |

| ESD Susceptibility                                                                    |                   |      |      |      |                          |        |

| ESD Resistivity HBM all Pins to GND                                                   | $V_{ESD1}$        | -2   | 2    | kV   | HBM <sup>7)</sup>        | P_4.17 |

| ESD Resistivity HBM<br>V <sub>S</sub> vs. GND, V <sub>S</sub> vs. OUT,<br>OUT vs. GND | $V_{ESD2}$        | -4   | 4    | kV   | HBM <sup>7)</sup>        | P_4.18 |

| ESD Resistivity CDM all pins to GND                                                   | $V_{ESD3}$        | -500 | 500  | V    | CDM <sup>8)</sup>        | P_4.19 |

| ESD Resistivity CDM corner pins                                                       | $V_{ESD4}$        | -750 | 750  | V    | CDM <sup>8)</sup>        | P_4.20 |

- 1) Not subject to production test, specified by design.

- 2) In case of reverse polarity voltage on pin IN,  $I_{\rm IN}$  needs to be limited (see P\_4.6) by external resistor  $R_{\rm INPUT}$ , see Figure 53.

- 3) In case of reverse polarity voltage, current through the OUT pin needs to be limited by external circuitry to prevent over heating (see P\_4.14). Power dissipation during reverse polarity voltage can be calculated by **Equation (3)**. Please note, build-in protection functions are not available during reverse polarity condition.

- 4) In accordance to AEC Q100-012 and AEC Q101-006.

- 5)  $V_{\rm S(LD)}$  is setup without the DUT connected to the generator per ISO 7637-1.

- 6) Test aborted after 1 E6 cycles.

- 7) ESD susceptibility, HBM according to EIA/JESD 22-A114B

- 8) ESD susceptibility, Charged Device Model "CDM" EIA/JESD22-C101 or ESDA STM5.3.1

Figure 4 Maximum energy dissipation for switching OFF an inductive load  $E_{\rm A}$  vs. load current

#### **Notes**

- 1. Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- 2. Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

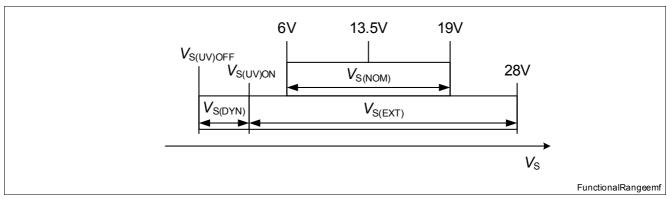

# 4.2 Functional Range

Table 3 Functional Range

| Parameter                                                                 | Symbol       | Val               | ues              | Unit | Note /<br>Test Condition | Number |

|---------------------------------------------------------------------------|--------------|-------------------|------------------|------|--------------------------|--------|

|                                                                           |              | Min.              | Max.             |      |                          |        |

| Nominal Supply Voltage<br>Range for Operation                             | $V_{S(NOM)}$ | 6                 | 19               | V    | -                        | P_4.23 |

| Extended Supply Voltage Range for Operation                               | $V_{S(EXT)}$ | $V_{ m S(UV)ON}$  | 28               | V    | 1)2)                     | P_4.24 |

| Extended Supply Voltage<br>Range for short dynamic<br>undervoltage swings | $V_{S(DYN)}$ | $V_{ m S(UV)OFF}$ | $V_{ m S(UV)ON}$ | V    | 1)2)3)                   | P_4.25 |

| Junction Temperature                                                      | $T_{\rm j}$  | -40               | 150              | °C   | _                        | P_4.26 |

- 1) see Chapter 5.5, Undervoltage turn ON voltage and Undervoltage turn OFF voltage

- 2) In extended supply voltage range, the device is functional but electrical parameters are not specified.

- 3) Operation only if supply voltage was in range of  $V_{\mathrm{S(EXT)}}$  before undervoltage swing. Otherwise, device will stay OFF.

Figure 5 Overview of functional ranges

Note: Within the functional or operating range, the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the Electrical Characteristics table.

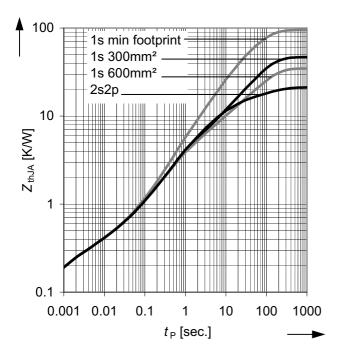

#### 4.3 Thermal Resistance

Note: This thermal data was generated in accordance with JEDEC JESD51 standards. For more information, go to www.jedec.org.

Table 4 Thermal Resistance

| Parameter                                          | Symbol                       | Values |      |      | Unit | Note /         | Number |

|----------------------------------------------------|------------------------------|--------|------|------|------|----------------|--------|

|                                                    |                              | Min.   | Тур. | Max. |      | Test Condition |        |

| Thermal Resistance -<br>Junction to Case           | $R_{\rm thJC}^{-1)}$         | _      | 1    | 1.1  | K/W  | _              | P_4.27 |

| Thermal Resistance -<br>Junction to Ambient - 2s2p | $R_{\text{thJA}\_2s2p}^{1)}$ | -      | 22   | _    | K/W  | 2)             | P_4.29 |

<sup>1)</sup> Not subject to production test, specified by design.

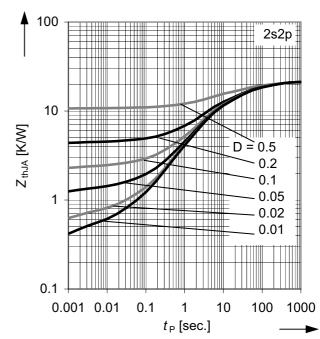

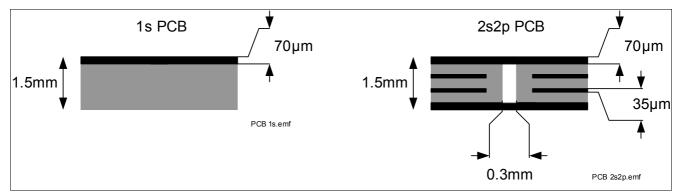

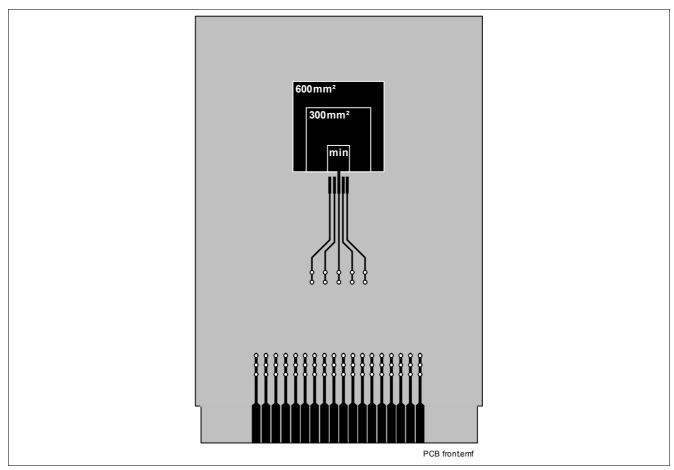

**Figure 6** and **Figure 7** are showing the typical thermal impedance of BTS50060-1TEA mounted according to Jedec JESD51-2,-5,-7 at natural convection on FR4 1s and 2s2p board. The product (chip + package) was simulated on a 76.4 x 114.3 x 1.5 mm board with 2 inner copper layers (2x 70μm Cu, 2 x 35μm Cu). Where applicable, a thermal via array under the exposed pad contacted the first inner copper layer. The PCB layer structure is shown in **Figure 8**. The PCB layout is shown in **Figure 9**.

Figure 6 Typical transient thermal impedance  $Z_{th(JA)} = f(t_P)$  for different cooling areas

Typical transient thermal impedance  $Z_{th(JA)} = f(t_P)$  for PWM operation with duty cycles D =  $t/t_{period}$  on a 2s2p PCB

Figure 7

<sup>2)</sup> Specified  $R_{\text{thJA}}$  value is according to Jedec JESD51-2,-5,-7 at natural convection on FR4 2s2p board; The Product (Chip+Package) was simulated on a 76.2  $\times$  114.3  $\times$  1.5 mm board with 2 inner copper layers (2  $\times$  70 mm Cu, 2  $\times$  35 mm Cu). Where applicable a thermal via array under the exposed pad contacted the first inner copper layer.

Figure 8 Cross section of 1s and 2s2p PCB used for  $Z_{\mathrm{thJA}}$  simulation

Figure 9 Front view of PCB layout used for  $Z_{\rm thJA}$  simulation

# 5 Functional Description

#### 5.1 Power Stage

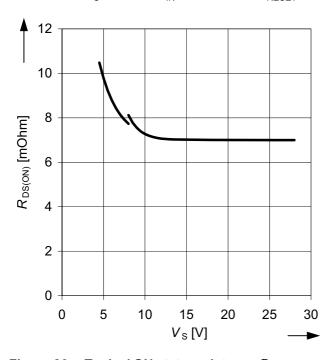

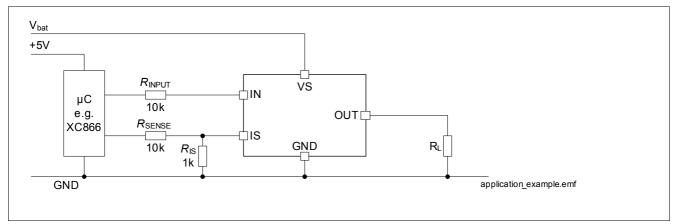

The power stage is built by a P-channel vertical power MOSFET (DMOS). The ON-state resistance  $R_{\rm DS(ON)}$  depends on the supply voltage  $V_{\rm S}$  as well as the junction temperature  $T_{\rm j}$ . Figure 25 shows the dependencies for the typical ON-state resistance. The behavior in reverse polarity is described in Chapter 5.3.4. A HIGH signal at the input pin (see Chapter 5.2) causes the power DMOS to switch ON. A LOW signal at the input pin causes the power DMOS to switch OFF.

#### 5.1.1 Switching a Resisitve Load

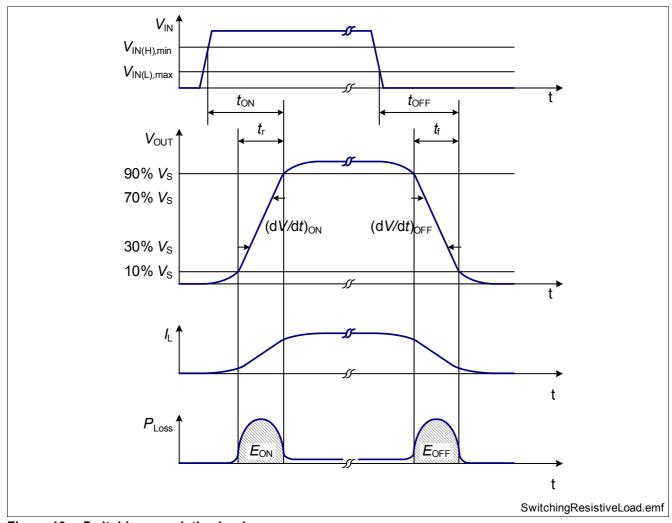

Defined slew rates for turn ON and OFF as well as edge shaping support PWM'ing of the load while achieving lowest EMC emission at minimum switching losses. Figure 10 shows the typical timing when switching a resistive load.

Figure 10 Switching a resistive load

# 5.1.2 Switching an Inductive Load - Infineon® SMART CLAMPING

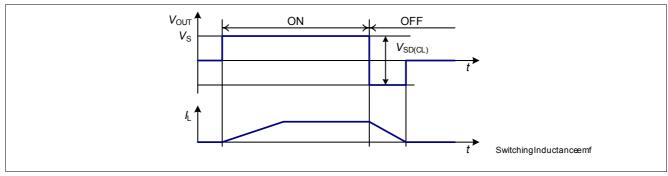

When switching OFF inductive loads, the output voltage  $V_{\rm OUT}$  drops below ground potential due to the involved inductance (  $-di_{\rm L}/dt = -v_{\rm L}/L$ ;  $-V_{\rm OUT} \cong -V_{\rm L}$ ). To prevent the destruction of the device due to high voltages, there is a

voltage clamp mechanism implemented that keeps the negative output voltage at a certain level (- $V_{\text{OUT}} = V_{\text{S}}$  -  $V_{\text{SD(CL)}}$ ). Please refer to **Figure 1** and **Figure 11** for details.

Figure 11 Switching an inductance

Nevertheless, the energy capability of the device is limited because the energy is converted into heat. That's why the maximum allowed load inductance is limited as well. Please see **Figure 4** for limitations of energy and load inductance

For calculating the demagnization energy, **Equation (1)** may be used:

$$E_{\rm A} = V_{\rm SD(CL)} \times \frac{L}{R_{\rm L}} \times \left[ \frac{V_{\rm S} - V_{\rm SD(CL)}}{R_{\rm L}} \times \ln\left(1 + \frac{R_{\rm L} \times I_{\rm L}}{V_{\rm SD(CL)} - V_{\rm S}}\right) + I_{\rm L} \right]$$

(1)

The equation can be simplified under the assumption of  $R_1 = 0 \Omega$  to:

$$E_{\rm A} = \frac{1}{2} \times L \times I_{\rm L}^2 \times \frac{V_{\rm SD(CL)}}{V_{\rm SD(CL)} - V_{\rm S}} \tag{2}$$

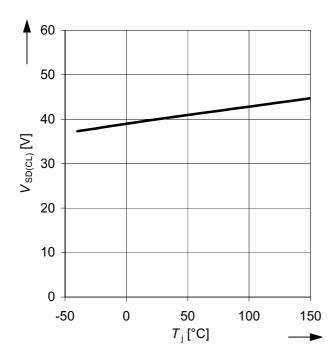

The BTS50060-1TEA provides Infineon SMART CLAMPING functionality. To optimize the energy capability for single and parallel operation, the clamp voltage  $V_{\rm SD(CL)}$  increases over the junction temperature  $T_{\rm j}$  and load current  $I_{\rm L}$ . Figure 36 shows the dependency from  $T_{\rm j}$  for the typical  $V_{\rm SD(CL)}$ . Please refer also to Figure 14.

#### 5.1.3 Switching a Capacitive Load

A capacitive load's dominant characteristic is it's inrush current. The BTS50060-1TEA can support inrush currents up to  $I_{L(SC)}$ . If the inrush current reaches  $I_{L(SC)}$ , the device may detect a short circuit and switch OFF. For a description of the short circuit protection mechanism, please refer to **Chapter 5.3.1**.

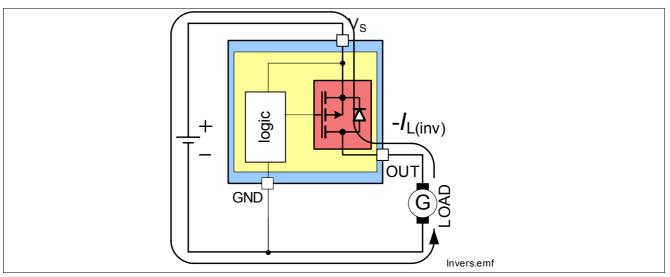

#### 5.1.4 Inverse Load Current Operation

In case of a negative load current, e.g. caused by a load operating as a generator, the device can not block the current flowing through the intrinsic body diode. See **Figure 12**. The power stage of the device can be switched ON or stays ON as long as  $V_{\rm IN}$  = HIGH, reaching the same  $R_{\rm DS(ON)}$  as for positive load currents, if no fault condition is detected. In case of fault condition, the logic of the device will switch OFF the power stage and supply a fault signal  $I_{\rm IS(fault)}$ . Since the device can not block negative load currents (even under fault conditions), it can not protect itself from overload condition. In the application, overload conditions, e.g. over temperature, must not occur during inverse load current operation.

Figure 12 Inverse load current operation

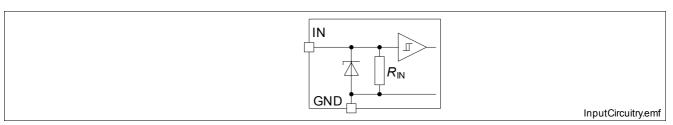

#### 5.2 Input Circuit

The input circuitry is compatible with 3.3 and 5V micro controllers. If  $V_{\rm IN}$  is set to  $V_{\rm IN} = V_{\rm IN(H)}$  ( $V_{\rm IN} = {\rm HIGH}$ ), the device will turn ON. See **Figure 10** for the timings. If  $V_{\rm IN}$  is set to  $V_{\rm IN} = V_{\rm IN(L)}$  ( $V_{\rm IN} = {\rm LOW}$ ), the power stage of the device will be turned OFF. The input circuitry has a hysteresis  $\Delta V_{\rm IN}$ . The input circuitry is compatible with PWM applications. **Figure 13** shows the electrical equivalent input circuitry. The logic of the BTS50060-1TEA stays active for a delay time  $t_{\rm RESET}$  after the switch OFF signal.

Figure 13 Input pin circuitry

Applying an input voltage of  $V_{\rm IN}$  > 20V (absolute maximum ratings exceeded!) may force the BTS50060-1TEA to deactivate parts of the logic circuitry. This includes the undervoltage shutdown, the undervoltage restart delay, and the analog sense function. In this case, also the short circuit shutdown threshold  $I_{\rm L(SC)}$  is set to typically 50A, and the latch reset time  $t_{\rm RESET}$  is reduced to typically 200µs. To reset this behavior, set input voltage to  $V_{\rm IN}$  = LOW for t>300µs.

#### 5.3 Protection Functions

The BTS50060-1TEA provides embedded protective functions. Integrated protection functions are designed to prevent the destruction of the IC from fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are designed for neither continuous nor repetitive operation.

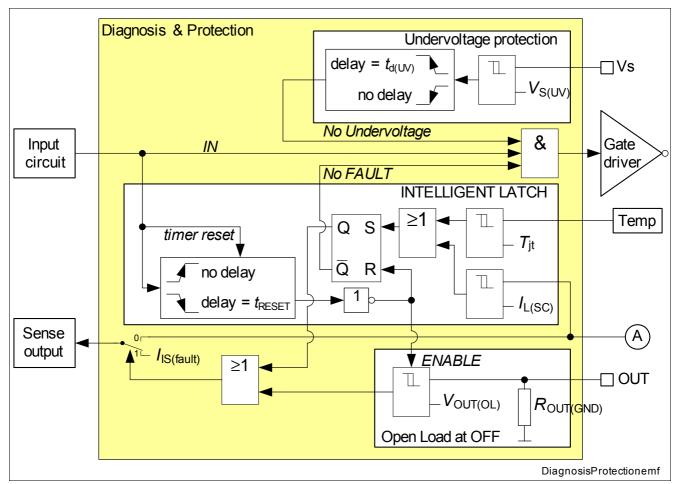

In case of overload, high inrush currents, or short circuit to ground, the BTS50060-1TEA offers several protection mechanisms. **Figure 14** describes the functionality of the diagnosis and protection block.

Figure 14 Diagram of Diagnosis & Protection block

#### 5.3.1 Protection by Over Current Shutdown

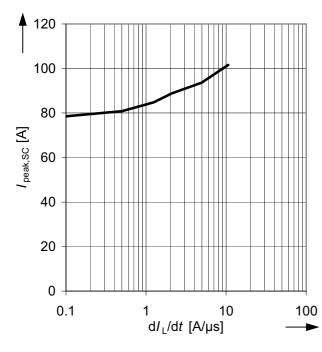

The internal logic permanently monitors the load current  $I_{\rm L}$ . In the event of a load current exceeding the short circuit shutdown threshold ( $I_{\rm L}>I_{\rm L(SC)}$ ), the output will switch OFF with a latching behavior. During an over current shutdown, an overshooting  $I_{\rm L(SC)peak}$  may occur, depending on the short circuit impedances. For the case the device is in ON state while short circuit appears, the typical overshooting  $I_{\rm L(SC)peak}$  as a function of the steepness of the short circuit current  $dI_{\rm SC}/dt$ , see Chapter 6.2.3.

For a detailed description of the latching behavior, please see Chapter 5.3.3.

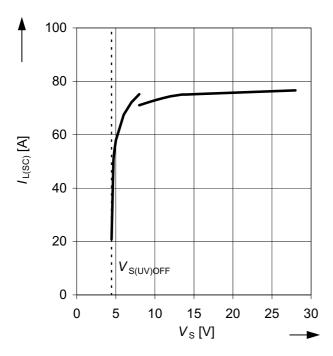

At lower supply voltages the current tripping level  $I_{L(SC)}$  will decrease depending on the supply voltage. At  $V_S$  = 4.7V, the current tripping level will be reduced to  $I_{L(SC)LV}$ . Please refer to **Figure 38** for typical current tripping level  $I_{L(SC)}$  as a function of the supply voltage  $V_S$ .

### 5.3.2 Protection by Over Temperature Shutdown

The internal logic permanently monitors the junction temperature of the output stage. In the event of an over temperature ( $T_{\rm j} > T_{\rm jt}$ ) the output will immediately switch OFF with a latching behavior, see **Chapter 5.3.3** for details.

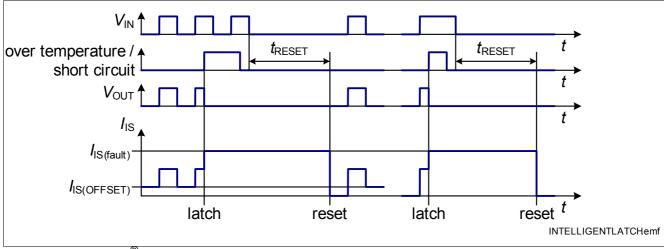

#### 5.3.3 Infineon® INTELLIGENT LATCH

The BTS50060-1TEA provides Infineon INTELLIGENT LATCH to avoid permanent resetting of a protective, latched switch OFF caused by over current shutdown or over temperature shutdown) in PWM applications. To reset a latched protective switch OFF the fault has to be acknowledged by commanding the input LOW for a minimum duration of  $t_{\rm reset}$ . See **Figure 15** for details.

Figure 15 Infineon® INTELLIGENT LATCH - fault acknowledge and latch reset

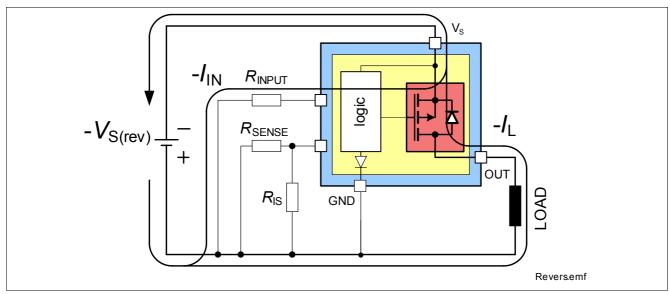

#### 5.3.4 Reverse Polarity Protection

Reverse polarity condition is the mix-up of the power supply connections of the entire application. This means, application GND connector is connected to positive supply voltage, while Vs pin is connected to negative supply voltage or ground potential. See **Figure 16** and **Figure 53**.

Figure 16 Reverse polarity condition

Under reverse polarity condition, the output stage can not block a current flow. It will conduct a load current via the intrinsic body diode. The current through the output stage has to be limited either by the load itself or by external circuitry, to avoid over heating of the power stage. Power losses in the power stage during reverse polarity condition can be calculated by **Equation (3)**:

$$P_{rev} = (-I_{L(rev)}) \times (-V_{SD(rev)})$$

(3)

Additionally, the current into the logic pins has to be limited to the maximum current described in **Chapter 4.1** with an external resistors. **Figure 53** shows a typical application. Resistors  $R_{\mathsf{INPUT}}$  and  $R_{\mathsf{SENSE}}$  are used to limit the current in the logic of the device and in the ESD protection stage. The recommended value for  $R_{\mathsf{INPUT}} = R_{\mathsf{SENSE}} = 10 \mathrm{k}\Omega$ . As long as  $|-V_{\mathsf{S(rev)}}| < 16 \mathrm{V}$ , the current through the GND pin of the device is blocked by an internal diode.

#### 5.3.5 Protection during Loss of Ground

In case of loss of the module ground or device ground connection (GND pin) the device protects itself by automatically turning OFF (when it was previously ON) or remains OFF (even if the load remains connected to ground), regardless if the input is driven HIGH or LOW. In case GND recovers the device may need a reset via the IN pin to return to normal operation.

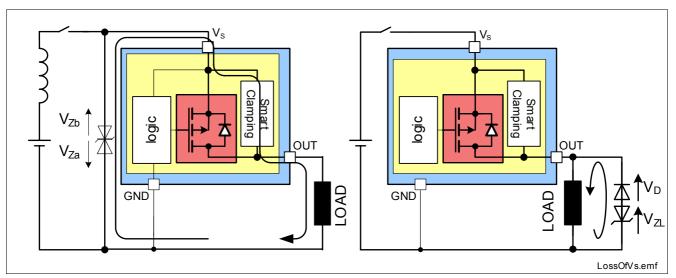

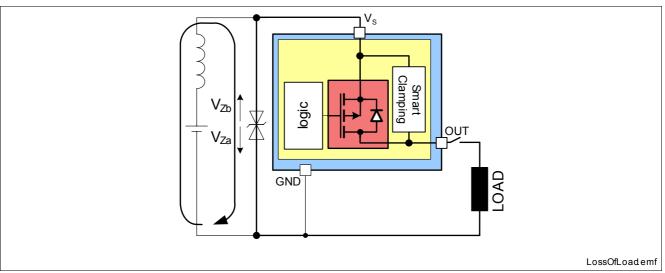

## 5.3.6 Protection during Loss of Load or Loss of V<sub>s</sub> Condition

In case of loss of load with charged primary inductances the maximum supply voltage has to be limited. It is recommended to use a Z-diode, a varistor ( $V_{\rm Za}$  < 40V) or  $V_{\rm S}$  clamping power switches with connected loads in parallel.

In case of loss of a charged inductive load, disturbances on pin OUT may require a reset on IN pin for the device to regain normal operation.

In case of loss of  $V_{\rm S}$  connection with charged inductive loads, a current path with load current capability has to be provided, to demagnetize the charged inductances. It is recommended to use a diode, a Z-diode or a varistor ( $V_{\rm ZL}$  < 16V,  $V_{\rm ZL}$  +  $V_{\rm D}$  < 16V).

For higher clamp voltages currents through all pins have to be limited according to the maximum ratings. Please see **Figure 17** and **Figure 18** for details.

Figure 17 Loss of V<sub>s</sub>

Figure 18 Loss of load

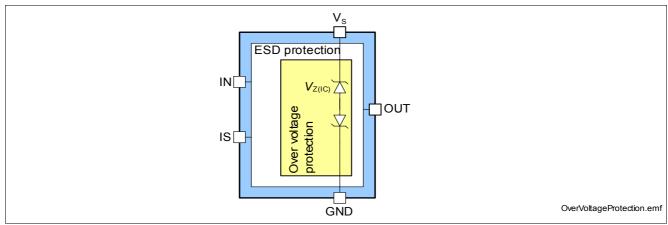

#### 5.3.7 Protection during ESD or Over Voltage Condition

All logic pins have ESD protection. A dedicated clamp mechanism protects the logic IC against transient over voltages. See **Figure 19** for details.

Figure 19 Over voltage protection

In the case  $(V_{\rm S} > {\rm max}\ V_{\rm S(SC)})\&(V_{\rm S} < V_{\rm SD(CL)})$ , the output transistor is still operational and follows the input. Parameters are no longer warranted and lifetime is reduced compared to normal mode. This specially impacts the short circuit robustness, as well as the maximum energy  $E_{\rm AS}$  the device can handle.

The BTS50060-1TEA provides Infineon <sup>®</sup> SMART CLAMPING functionality, which suppresses non nominal over voltages by actively clamping the over voltage across the power stage and the load. This is achieved by controlling the clamp voltage  $V_{\rm SD(CL)}$  depending on the junction temperature  $T_{\rm j}$  and the load current  $I_{\rm L}$ . See **Figure 14** for details. Please refer also to **Chapter 5.1.2**.

#### 5.4 Diagnosis Functions

For diagnosis purpose, the BTS50060-1TEA provides an advanced analog sense signal at the pin IS. For an overview of the diagnosis functions, you may have a look at **Figure 14** "**Diagram of Diagnosis & Protection block**".

#### 5.4.1 Sense Output

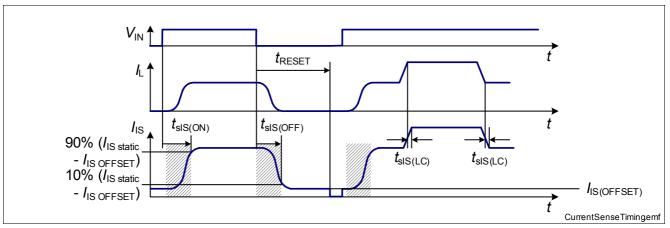

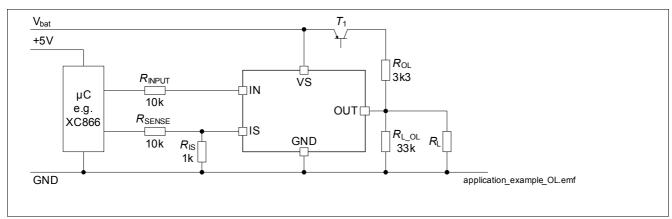

The current sense output is a current source driving a signal  $I_{\rm IS}$  proportional to the load current (see **Equation (5)**) as long as no "hard" failure mode occurs (short circuit to GND / over temperature) and  $V_{\rm SIS} = V_{\rm S} - V_{\rm IS} > 3$ V. It is activated and deactivated by the input signal. Usually, in the application a pull-down resistor  $R_{\rm IS}$  is connected between the current sense pin IS and GND pin. A typical value is  $R_{\rm IS} = 1.0~{\rm k}\Omega$ . **Figure 53** shows a simplified application setup.

**Table 5** is giving a quick reference for the logic / analog state of the IS pin during device operation.

In case a short circuit or an over temperature condition is detected, the sense output is supplying a fault signal  $I_{\rm IS(fault)}$ . The fault signal is reset by an input signal being LOW for t >  $t_{\rm RESET}$ . As long as an open load, short-to- $V_{\rm S}$  or inverse operation is detected while the device is in OFF state, the sense output also supplies the fault signal  $I_{\rm IS(fault)}$ . The timings and logic of the IS pin is described in **Figure 20**. During output turning ON or OFF, the sense signal is invalid.

Table 5 Truth Table for Sense Signal

| Operation mode                | Input level                                  | Output level                                                       | Sense output                               |

|-------------------------------|----------------------------------------------|--------------------------------------------------------------------|--------------------------------------------|

| Normal operation              | HIGH <sup>1)</sup>                           | $V_{\text{OUT}} = V_{\text{S}} - R_{\text{DS(ON)}} * I_{\text{L}}$ | $I_{IS} = (I_L / k_{IS}) + I_{IS(OFFSET)}$ |

|                               | <b>LOW</b> <sup>2)</sup> for t < $t_{RESET}$ | $V_{OUT} \sim GND$                                                 | $I_{\rm IS} = I_{\rm IS(OFFSET)}$          |

|                               | <b>LOW</b> for $t > t_{RESET}$               | $(V_{OUT} < V_{OUT(OLL)})$                                         | $Z^{3)} (I_{IS} = I_{IS(LL)})$             |

| Inverse operation             | HIGH                                         | $V_{\text{OUT}} > V_{\text{S}}$                                    | $I_{\rm IS} \leq I_{\rm IS(OFFSET)}$       |

|                               | <b>LOW</b> for $t < t_{RESET}$               |                                                                    | $I_{\rm IS} = I_{\rm IS(OFFSET)}$          |

|                               | <b>LOW</b> for $t > t_{RESET}$               |                                                                    | $I_{\rm IS} = I_{\rm IS(FAULT)}$           |

| After short circuit to GND or |                                              | $V_{OUT} \sim GND$                                                 | $I_{\rm IS} = I_{\rm IS(FAULT)}$           |

| over temperature detection    | LOW for $t < t_{RESET}$                      |                                                                    |                                            |

|                               | <b>LOW</b> for $t > t_{RESET}$               |                                                                    | $Z(I_{IS} = I_{IS(LL)})$                   |

| Short circuit to $V_{\rm S}$  | HIGH                                         | $V_{OUT} = V_{S}$                                                  | $I_{\rm IS} \leq I_{\rm IS(OFFSET)}$       |

|                               | <b>LOW</b> for $t < t_{RESET}$               |                                                                    | $I_{\rm IS} = I_{\rm IS(OFFSET)}$          |

|                               | <b>LOW</b> for $t > t_{RESET}$               |                                                                    | $I_{\rm IS} = I_{\rm IS(FAULT)}$           |

| Open load                     | HIGH                                         | $V_{OUT} = V_{S}$                                                  | $I_{\rm IS} \leq I_{\rm IS(OFFSET)}$       |

|                               | <b>LOW</b> for t < $t_{RESET}$               | $V_{\rm OUT} > V_{\rm OUT(OLH)}^{4)}$                              | $I_{\rm IS} = I_{\rm IS(OFFSET)}$          |

|                               | <b>LOW</b> for $t > t_{RESET}$               |                                                                    | $I_{\rm IS} = I_{\rm IS(FAULT)}$           |

<sup>1)</sup> HIGH:  $V_{IN} = V_{IN(H)}$ 2) LOW:  $V_{IN} = V_{IN(L)}$

<sup>3)</sup> Z: High impedance

<sup>4)</sup> Can be achieved e.g. with external pull up resistor  $R_{\rm OL}$ , see Figure 53.

Figure 20 Sense output timing

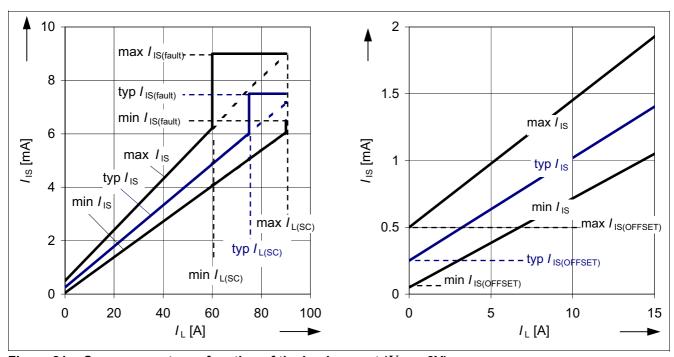

**Figure 21** shows the current sense as a function of the load current in the power DMOS. The curves represent the minimum and maximum values for the sense current, as well as the ideal sense current, assuming an ideal  $k_{\rm IS}$  factor value as well as an ideal  $I_{\rm IS(OFFSET)}$ .

Figure 21 Sense current as a function of the load current ( $V_{\rm SIS}$  > 3V)

The sense current can be calculated out of the load current by the following Equation (4):

$$I_{\rm IS} = \frac{1}{k_{\rm IS}} \times I_{\rm L} + I_{\rm IS(OFFSET)} \tag{4}$$

Or, vice versa, the load current can be calculated out of the sense current by following **Equation (5)**:

$$I_{\rm L} = k_{\rm IS} \times (I_{\rm IS} - I_{\rm IS(OFFSET)}) \tag{5}$$

For definition of  $k_{\rm IS}$ , the following **Equation (6)** is used:

$$k_{\rm IS} = \frac{I_{\rm L1} - I_{\rm L2}}{I_{\rm IS}(I_{\rm L1}) - I_{\rm IS}(I_{\rm L2})} \tag{6}$$

$I_{L1}$  and  $I_{L2}$  are two different load currents,  $I_{IS(IL1)}$  and  $I_{IS(IL2)}$  are the corresponding sense currents.

#### 5.4.2 Enhancing Accuracy of the Sense Output by End of Line Calibration

For some applications it may be necessary to measure the load current with very high accuracy. To increase the device accuracy, different methods can be used, e.g. single point calibration or dual point calibration.

The variance of the sense current at a certain load current depends on the variance of the factor  $k_{\rm IS}$  as well as on the variance of the offset current  $I_{\rm IS(OFFSET)}$ . The temperature variance of the factor  $k_{\rm IS}$  over the temperature range is described with the parameter  $\Delta k_{\rm IS,Temp}$ .

$$\Delta k_{IS(Temp)} = \max[|k_{IS}(-40^{\circ}C) - k_{IS}(25^{\circ}C)|; |k_{IS}(150^{\circ}C) - k_{IS}(25^{\circ}C)|]$$

(7)

The variance of the sense current offset over the temperature range is defined as shown in Equation (8):

$$\Delta I_{\rm IS(OFFSET)} = \max[\left|I_{\rm IS(OFFSET)}(-40^{\circ}\text{C}) - I_{\rm IS(OFFSET)}(25^{\circ}\text{C})\right|; \left|I_{\rm IS(OFFSET)}(150^{\circ}\text{C}) - I_{\rm IS(OFFSET)}(25^{\circ}\text{C})\right|] \tag{8}$$

#### 5.4.3 Short-to-Battery detection / Open Load Detection in OFF state

The BTS50060-1TEA provides open load diagnosis in OFF state. This is achieved by monitoring the OUT voltage. The open load at OFF diagnosis is activated if  $V_{\rm IN}$  = LOW for t >  $t_{\rm RESET}$ . An open load or short-to-battery is detected if  $V_{\rm OUT(OLH)}$ . To provoke this condition during Open Load, it may be necessary to use an external pull up resistor  $R_{\rm OL}$  (see **Figure 53**). In case of detecting a shorted load to battery, open load, or inverse operation in OFF state, the pin IS provides a defined fault current  $I_{\rm IS(fault)}$ . If  $V_{\rm OUT}$  drops below  $V_{\rm OUT(OLL)}$ , or  $V_{\rm IN}$  is set to HIGH, the fault signal is removed. **Figure 22** shows the behavior of the open load at OFF diagnosis. **Figure 51** and **Figure 52** provide the typical behavior of  $V_{\rm OUT(OLH)}$  and  $V_{\rm OUT(OLL)}$  as a function of the supply voltage and junction temperature. The device internally connects OUT with GND pin with an effective resistor  $R_{\rm OUT(GND)}$ . In case the application provides high leakage current outside of the BTS50060-1TEA between Vs and OUT, it may be necessary to use an external resistor  $R_{\rm L_{OL}}$  to disable open load detection. **Figure 53** gives an example of external circuitry for enabling / disabling open load detection in OFF state.

Figure 22 Open load detection in OFF state

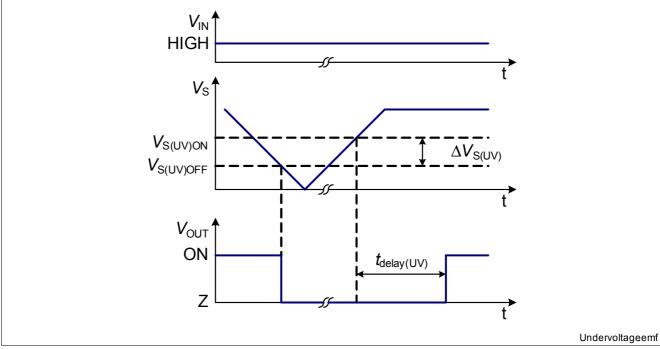

#### 5.5 Undervoltage Shutdown & Restart

The BTS50060-1TEA switches OFF whenever  $V_{\rm S}$  drops below  $V_{\rm S(UV)OFF}$ . The device restarts automatically after the supply voltage increases to a sufficient level ( $V_{\rm S} > V_{\rm S(UV)ON}$ ) and a delay time of  $t_{\rm delay(UV)}$ , if the input pin IN is HIGH. Please see **Figure 23** for details. The fault signal is reset if  $V_{\rm S}$  is below  $V_{\rm S(UV)}$  for more than typ. 70µs.

Figure 23 Undervoltage shutdown and restart

## 6 Electrical Characteristics BTS50060-1TEA

#### **6.1** Electrical Characteristics Table

Table 6 Electrical Characteristics: BTS50060-1TEA

| Parameter                                                      | Symbol                     | Values |      |      | Unit | Note /                                                                                                                                                                                                            | Number |

|----------------------------------------------------------------|----------------------------|--------|------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

|                                                                |                            | Min.   | Тур. | Max. |      | Test Condition                                                                                                                                                                                                    |        |

| Operating currents                                             |                            |        |      |      |      | •                                                                                                                                                                                                                 | •      |

| Standby current for whole device with load $T_{\rm j}$ = 25°C  | I <sub>S(OFF)_25</sub> 1)  | -      | 5    | 8    | μА   | $V_{\text{IN}}$ = LOW for<br>t > $t_{\text{RESET}}$ ,<br>$V_{\text{S}}$ = 13.5V,<br>$T_{\text{j}}$ = 25°C<br>$V_{\text{OUT}}$ < $V_{\text{OUT}(\text{OLL})}$                                                      | P_6.1  |

| Standby current for whole device with load $T_{\rm j}$ = 85°C  | I <sub>S(OFF)_85</sub> 1)  | -      | 5    | 8    | μΑ   | $V_{\text{IN}}$ = LOW for<br>t > $t_{\text{RESET}}$ ,<br>$V_{\text{S}}$ = 13.5V,<br>$T_{\text{j}}$ = 85°C<br>$V_{\text{OUT}}$ < $V_{\text{OUT}(\text{OLL})}$                                                      | P_6.2  |

| Standby current for whole device with load $T_{\rm j}$ = 150°C | $I_{\mathrm{S(OFF)\_150}}$ | -      | 20   | 60   | μΑ   | $\begin{split} V_{\text{IN}} &= \text{LOW for} \\ \text{t} &> t_{\text{RESET}}, \\ V_{\text{S}} &= 13.5 \text{V}, \\ T_{\text{j}} &= 150 ^{\circ} \text{C} \\ V_{\text{OUT}} &< V_{\text{OUT(OLL)}}, \end{split}$ | P_6.3  |

| Ground current during ON                                       | $I_{\mathrm{GND(ON)}}$     | -      | 3    | 5    | mA   | $V_{\text{IN}}$ = HIGH $t > t_{\text{ON}}$                                                                                                                                                                        | P_6.4  |

| Supply current during open load detection in OFF state         | $I_{\mathrm{S(OL)}}^{1)}$  | -      | 12   | 15   | mA   | $V_{\rm IN}$ = LOW for t > $t_{\rm RESET}$ , $V_{\rm OUT}$ > $V_{\rm OUT(OLH)}$                                                                                                                                   | P_6.5  |

| Power stage                                                    |                            |        |      |      |      |                                                                                                                                                                                                                   |        |

| On-State Resistance                                            | R <sub>DS(ON)_25</sub> 1)  | -      | 6.8  | _    | mΩ   | $V_{\rm IN}$ = HIGH,<br>$T_{\rm j}$ = 25 °C,<br>$V_{\rm S}$ = 13.5V,<br>$I_{\rm L}$ = +/-13.5A                                                                                                                    | P_6.6  |

| On-State Resistance                                            | R <sub>DS(ON)_150</sub>    | _      | 10   | 12   | mΩ   | $V_{\rm IN}$ = HIGH,<br>$T_{\rm j}$ = 150 °C,<br>$V_{\rm S}$ = 13.5V,<br>$I_{\rm L}$ = +/-13.5A                                                                                                                   | P_6.7  |

| On-State Resistance                                            | R <sub>DS(8V)_25</sub> 1)  | -      | 8    | -    | mΩ   | $V_{\rm IN}$ = HIGH,<br>$T_{\rm j}$ = 25 °C,<br>$V_{\rm S}$ = 8V,<br>$I_{\rm L}$ = +/-13.5A                                                                                                                       | P_6.8  |

| On-State Resistance                                            | R <sub>DS(8V)_150</sub> 1) | -      | 11.5 | 15   | mΩ   | $V_{IN}$ = HIGH,<br>$T_{j}$ = 150 °C,<br>$V_{S}$ = 8V,<br>$I_{L}$ = +/-13.5A                                                                                                                                      | P_6.9  |

Table 6 Electrical Characteristics: BTS50060-1TEA (cont'd)

| Parameter                                             | Symbol                              | Values |      |      | Unit | Note /                                                                                               | Number |

|-------------------------------------------------------|-------------------------------------|--------|------|------|------|------------------------------------------------------------------------------------------------------|--------|

|                                                       |                                     | Min.   | Тур. | Max. |      | <b>Test Condition</b>                                                                                |        |

| On-State Resistance at low supply voltage             | R <sub>DS(UV)_25</sub> 1)           | _      | 10.5 | _    | mΩ   | $V_{\rm IN}$ = HIGH,<br>$T_{\rm j}$ = 25 °C,<br>$V_{\rm S}$ = 4.7V,<br>$I_{\rm L}$ = +/-13.5A        | P_6.10 |

| On-State Resistance at low supply voltage             | $R_{\mathrm{DS(UV)\_150}}$          | -      | 19   | 25   | mΩ   | $V_{\rm IN}$ = HIGH,<br>$T_{\rm j}$ = 150 °C,<br>$V_{\rm S}$ = 4.7V,<br>$I_{\rm L}$ = +/-13.5A       | P_6.11 |

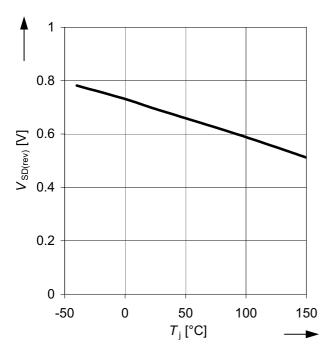

| Body diode forward voltage<br>drop <sup>2)</sup>      | -V <sub>SD(rev)</sub> <sup>1)</sup> | 300    | 600  | 1000 | mV   | $V_{\text{IN}}$ = LOW,<br>$I_{\text{L}}$ = -13.5A<br>(see <b>Figure 12</b><br>and <b>Figure 16</b> ) | P_6.12 |

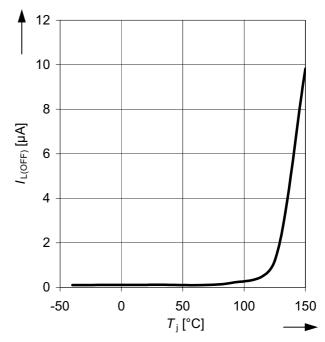

| Output leakage current <sup>3)</sup>                  | I <sub>L(OFF)_25</sub> 1)           | -      | 0.1  | 1    | μΑ   | $T_{\rm j}$ = 25°C,<br>$V_{\rm IN}$ = LOW,<br>$V_{\rm OUT}$ = 0V                                     | P_6.13 |

| Output leakage current                                | $I_{\text{L(OFF)}\_85}^{1)}$        | -      | 0.1  | 1    | μA   | $T_{\rm j}$ = 85°C,<br>$V_{\rm IN}$ = LOW,<br>$V_{\rm OUT}$ = 0V                                     | P_6.14 |

| Output leakage current                                | $I_{\text{L(OFF)}\_150}$            | -      | 1    | 60   | μΑ   | $T_{\rm j}$ = 150°C,<br>$V_{\rm IN}$ = LOW,<br>$V_{\rm OUT}$ = 0V                                    | P_6.15 |

| Switching a resistive load                            |                                     |        |      |      |      |                                                                                                      |        |

| Slew rate 30% to 70% $V_{\rm S}$                      | $(\mathrm{d}V/\mathrm{d}t)_{ON}$    | 0.12   | 0.18 | 0.36 | V/µs | $R_{\rm L} = 1\Omega$ ,                                                                              | P_6.16 |

| Slew rate 70% to 30% $V_{\rm S}$                      | $-(\mathrm{d}V/\mathrm{d}t)_{OFF}$  | 0.12   | 0.18 | 0.36 | V/µs | $V_{\rm S} = 13.5 \rm V$                                                                             | P_6.17 |

| Slew rate matching $(dV/dt)_{ON}$ - $ (dV/dt)_{OFF} $ | $\Delta dV/dt$                      | -0.15  | -    | 0.15 | V/µs | (see Figure 10 for definitions and Figure 29 to                                                      | P_6.18 |

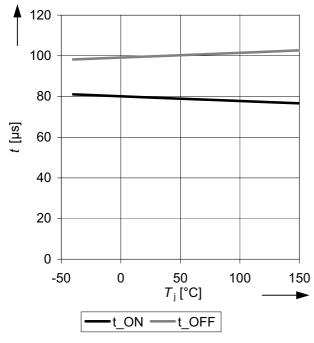

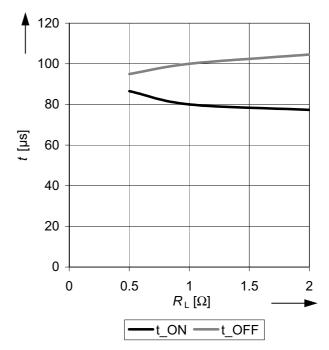

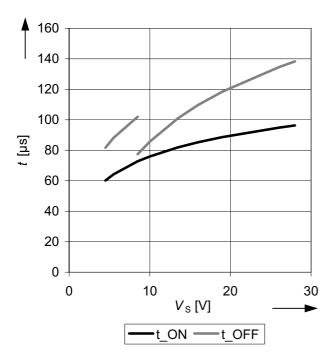

| Turn ON time to 90% $V_{\rm S}$                       | $t_{\sf ON}$                        | _      | 80   | 130  | μs   | Figure 35 for                                                                                        | P_6.19 |

| Turn OFF time to 10% $V_{\rm S}$                      | $t_{OFF}$                           |        | 100  | 150  | μs   | parameter                                                                                            | P_6.20 |

| Turn ON/OFF matching                                  | t <sub>ON</sub> -t <sub>OFF</sub>   | -70    | -20  | 30   | μs   | dependencies)                                                                                        | P_6.21 |

| Turn ON rise time 10% to 90% $V_{\rm S}$              | $t_{r}$                             | 30     | 60   | 90   | μs   |                                                                                                      | P_6.22 |

| Turn OFF fall time 90% to 10% $V_{\rm S}$             | $t_{f}$                             | 30     | 60   | 90   | μs   |                                                                                                      | P_6.23 |

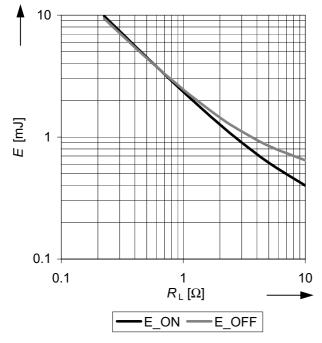

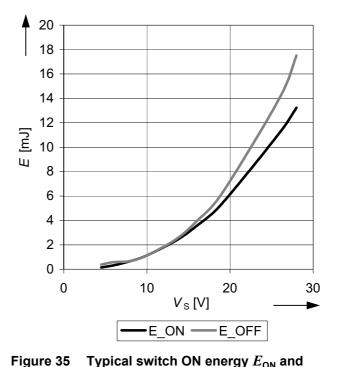

| Switch ON energy                                      | $E_{\rm ON}^{-1)}$                  | 1.1    | 2.4  | 3.6  | mJ   |                                                                                                      | P_6.24 |

| Switch OFF energy                                     | $E_{\rm OFF}^{\rm 1)}$              | 1.1    | 2.4  | 3.6  | mJ   |                                                                                                      | P_6.25 |

| Switching an inductive load                           |                                     |        |      | •    | •    |                                                                                                      |        |

| Output voltage drop limitation <sup>4)</sup>          | $V_{\rm SD(CL)\_25}^{1)}$           | 32     | 40   | _    | V    | $T_{\rm j}$ = 25°C,<br>$I_{\rm L}$ = 40mA,                                                           | P_6.26 |

| Output voltage drop limitation                        | $V_{\rm SD(CL)\_150}^{1)}$          | 40     | 48   | _    | V    | $T_{\rm j}$ = 150°C,<br>$I_{\rm L}$ = 13.5A,                                                         | P_6.27 |

| Input circuitry                                       |                                     |        | v.   |      |      | •                                                                                                    |        |

Table 6 Electrical Characteristics: BTS50060-1TEA (cont'd)

| Parameter                                                    | Symbol                                    |      | Values            |             | Unit | Note /                                                                                             | Number |

|--------------------------------------------------------------|-------------------------------------------|------|-------------------|-------------|------|----------------------------------------------------------------------------------------------------|--------|

|                                                              |                                           | Min. | Тур.              | Max.        |      | <b>Test Condition</b>                                                                              |        |

| LOW level input voltage                                      | $V_{IN(L)}$                               | -0.3 | _                 | 8.0         | V    | _                                                                                                  | P_6.28 |

| HIGH level input voltage                                     | $V_{\rm IN(H)}$                           | 2.0  | _                 | 6           | V    | _                                                                                                  | P_6.29 |

| Input voltage hysteresis                                     | $\Delta V_{IN}^{(1)}$                     | _    | 200               | _           | mV   | _                                                                                                  | P_6.30 |

| Input pull down resistor                                     | $R_{IN}$                                  | 50   | 100               | 200         | kΩ   | _                                                                                                  | P_6.31 |

| Protection                                                   |                                           |      |                   |             |      |                                                                                                    |        |

| Short circuit shutdown threshold                             | $I_{L(SC)}$                               | 60   | 75                | 95          | А    | 8V < V <sub>S</sub> < 19V                                                                          | P_6.32 |

| Short circuit shutdown<br>threshold at low supply<br>voltage | $I_{L(SC)LV}^{1)}$                        | 10   | _                 | $I_{L(SC)}$ | А    | 4.7V < V <sub>S</sub> < 8V                                                                         | P_6.33 |

| Thermal shutdown<br>temperature                              | $T_{ m jt}$                               | 150  | 175 <sup>1)</sup> | 2001)       | °C   | _                                                                                                  | P_6.34 |

| Latch reset time                                             | $t_{RESET}^{-1)}$                         | 40   | 55                | 80          | ms   | $V_{\rm IN}$ = LOW<br>6V < $V_{\rm S}$ < 28V                                                       | P_6.35 |

| Output leakage current while GND disconnected <sup>5)</sup>  | $I_{\mathrm{OUT}(\mathrm{GND})}^{-1)}$    | 0    | 0.5               | 1.0         | mA   | $V_{\rm S}$ = $V_{\rm S(EXT)}$ , GND pin disconnected                                              | P_6.40 |

| Over voltage protection of logic IC                          | $V_{Z(IC)}$                               | 45   | 50                | _           | V    | $I_{\rm GND}$ = 5mA                                                                                | P_6.41 |

| Sense Output                                                 | 1                                         | 11   |                   | 1           |      |                                                                                                    | 1      |

| Sense current steepness (reciprocal)                         | $k_{IS}$                                  | 10.5 | 13                | 15          | k    | see <b>Equation (6)</b> $I_{L1}$ = 13.5A,                                                          | P_6.42 |

| $k_{\rm IS}$ temperature variance                            | $\Delta k_{\rm IS(Temp)}^{1)}$            | -2   | 0                 | +2          | %    | $I_{L2} = 0A,$<br>$V_{S} - V_{IS} > 3V$                                                            | P_6.43 |

| Sense current $I_{L} = I_{L1}$                               | $I_{IS(L1)}$                              | 0.95 | 1.28              | 1.88        | mA   | $I_{\rm L}$ = 13.5A,<br>$V_{\rm S}$ - $V_{\rm IS}$ > 3V                                            | P_6.44 |

| Sense current offset                                         | $I_{IS(OFFSET)}$                          | 50   | 240               | 600         | μΑ   | $V_{\rm S}$ - $V_{\rm IS}$ > 3V                                                                    | P_6.46 |

| Sense current offset temperature variance                    | $\Delta I_{\text{IS(OFFSET)}}$            | -100 | 0                 | 100         | μΑ   | see Equation (8)                                                                                   | P_6.47 |

| Leakage Current at sense output                              | $I_{IS(LL)}$                              | 0    | 0.1               | 1           | μА   | $V_{\text{IN}}$ = LOW for t > $t_{\text{RESET}}$ , $V_{\text{OUT}}$ < $V_{\text{OUT}(\text{OLL})}$ | P_6.48 |

| Fault signal current at sense output                         | $I_{IS(fault)}$                           | 6.5  | 7.5               | 9           | mA   | 6)<br>V <sub>S</sub> - V <sub>IS</sub> > 3V                                                        | P_6.49 |

| Current sense settling time for turn ON to 90% $I_{ m IS}$   | $t_{\rm sis(ON)}^{1)}$                    | 0    | 90                | 300         | μs   | $V_{\rm S}$ = 13.5V, $R_{\rm L}$ = 1.0 $\Omega$ ,                                                  | P_6.50 |

| Current sense settling time for turn OFF to 10% $I_{\rm IS}$ | $t_{\rm sIS(OFF)}^{1)}$                   | 0    | 110               | 300         | μs   | $R_{\rm IS}$ = 1.0k $\Omega$ ,<br>$C_{\rm SENSE}$ < 100pF,                                         | P_6.51 |

| Current sense settling time matching                         | $t_{\rm sIS(ON)}$ - $t_{\rm sIS(OFF)}$ 1) | -70  | -20               | 30          | μs   | See Figure 20                                                                                      | P_6.52 |

#### Table 6 Electrical Characteristics: BTS50060-1TEA (cont'd)

| Parameter                                                                           | Symbol                             | Values |      |      | Unit | Note /                                                                                                                                        | Number |

|-------------------------------------------------------------------------------------|------------------------------------|--------|------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------|--------|

|                                                                                     |                                    | Min.   | Тур. | Max. |      | <b>Test Condition</b>                                                                                                                         |        |

| Current sense settling time after changes of the load current $I_{\rm L}$           | t <sub>sIS(LC)</sub> <sup>1)</sup> | 0      | 1    | 2    | μs   | $V_{\rm IN}$ = HIGH,<br>$I_{\rm L}$ = 1A $\leftrightarrow$ 50A<br>$R_{\rm IS}$ = 1.0k $\Omega$ ,<br>$C_{\rm SENSE}$ < 100pF,<br>See Figure 20 | P_6.53 |

| Turn ON current sense settling time to $I_{\rm IS(fault)}$ in case of short circuit | $t_{\rm SIS(FAULT)}^{1)}$          | 0      | 100  | 250  | μs   | $R_{\rm IS}$ = 1.0k $\Omega$ , $C_{\rm SENSE}$ < 100pF, See Figure 15                                                                         | P_6.54 |

| Open load at OFF                                                                    | +                                  | +      | 1    | 1    |      |                                                                                                                                               | -      |

| Output voltage threshold for open load detection in OFF state                       | $V_{OUT(OLH)}$                     | 5      | 5.5  | 6    | V    | $V_{\rm IN}$ = LOW,<br>for t > $t_{\rm RESET}$ ,<br>$V_{\rm S}$ = 13.5V,                                                                      | P_6.55 |

| Output voltage threshold for resetting open load detection in OFF state             | $V_{OUT(OLL)}$                     | 4.5    | 5    | 5.5  | V    | see Figure 22,<br>Figure 51 and<br>Figure 52                                                                                                  | P_6.56 |

| Output voltage hysteresis for open load detection in OFF state                      | $\Delta V_{ m OUT(OL)}^{1)}$       | -      | 500  | -    | mV   |                                                                                                                                               | P_6.57 |

| Intrinsic output pull-down resistance                                               | $R_{\rm OUT(GND)}^{1)}$            | -      | 150  | _    | kΩ   | $V_{\text{OUT}}$ = 4.5V,<br>$V_{\text{IN}}$ = LOW,<br>for t > $t_{\text{RESET}}$                                                              | P_6.63 |

| Undervoltage shutdown and                                                           | l restart                          |        | 1    |      | •    |                                                                                                                                               |        |

| Undervoltage turn ON voltage                                                        | $V_{ m S(UV)ON}$                   | _      | 4.4  | 4.7  | V    | $V_{\rm S}$ increasing, $V_{\rm IN}$ = HIGH                                                                                                   | P_6.58 |

| Undervoltage turn OFF voltage                                                       | $V_{\mathrm{S(UV)OFF}}$            | _      | 4.1  | 4.4  | V    | $V_{\rm S}$ decreasing, $V_{\rm IN}$ = HIGH                                                                                                   | P_6.59 |

| Undervoltage turn ON/OFF hysteresis                                                 | $\Delta V_{\mathrm{S(UV)}}^{-1)}$  | _      | 0.25 | _    | V    | $V_{\rm S(UV)ON} - \\ V_{\rm S(UV)OFF}, \\ V_{\rm IN} = {\rm HIGH}$                                                                           | P_6.60 |

| Undervoltage restart delay time                                                     | $t_{ m delay(UV)}$                 | 4      | 6    | 8    | ms   | $V_{IN}$ = HIGH                                                                                                                               | P_6.61 |

- 1) Not subject to production test, specified by design

- 2) Please note during ON state, the output voltage drop in inverse current operation is defined by  $V_{\rm SD(rev)}$  =  $R_{\rm DS(ON)}$  x  $I_{\rm L}$

- 3) See Figure 27 for typical temperature dependency.

- 4) See Figure 36 for typical temperature dependency.

- 5) All pins disconnected except for  $V_{\rm S}$  and OUT

- 6) Valid after over temperature or short ciruit to ground until reset (t >  $t_{\rm RESET}$ ,  $V_{\rm IN}$  = LOW, or undervoltage detection) or during detection of open load in OFF state.

# 6.2 Parameter Dependencies

#### 6.2.1 Power Stage

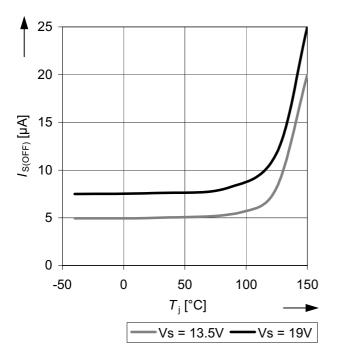

Figure 24 Typical standby current  $I_{\text{S(OFF)}}$  as a function of the junction temperature  $T_{\text{j}}$   $V_{\text{S}}$  = 13.5V,  $V_{\text{IN}}$  = LOW for t >  $t_{\text{RESET}}$

Figure 25 Typical ON state resistance  $R_{\rm DS(ON)}$  as a function of the junction temperature  $T_{\rm j}$   $V_{\rm S}$  = 13.5V,  $I_{\rm L}$  = 13.5A,  $V_{\rm IN}$  = HIGH

Figure 26 Typical ON state resistance  $R_{\rm DS(ON)}$  as a Figure 27 function of the supply voltage  $V_{\rm S}$   $T_{\rm i}$  = 25°C,  $I_{\rm L}$  = 13.5A,  $V_{\rm IN}$  = HIGH

Typ. output leakage current  $I_{\rm L(OFF)}$  as a function of the junction temperature  $T_{\rm j}$   $V_{\rm S}$  = 13.5V,  $V_{\rm IN}$  = LOW

0.35 0.3 0.25 dV/dt [V/µs] 0.2 0.15 0.1 0.05 0 0 10 20 30  $V_{S}[V]$ ·dV/dt\_ON --dV/dt\_OFF

Figure 28 Typical body diode forward voltage drop - $V_{\rm SD(rev)}$  as a function of the junction temperature  $T_{\rm j}$   $I_{\rm L}$  = -4A,  $V_{\rm IN}$  = LOW

Figure 29 Typical slew rate  $(dV/dt)_{ON}$  and  $(dV/dt)_{OFF}$  as a function of the supply voltage  $V_{S}$   $T_{i} = 25^{\circ}\text{C}, R_{I} = 1\Omega$

Figure 30 Typical turn ON time  $t_{\rm ON}$  and turn OFF time  $t_{\rm OFF}$  as a function of the junction temperature  $T_{\rm j}$   $V_{\rm S}$  = 13.5V,  $R_{\rm L}$  = 1 $\Omega$

Figure 31 Typical turn ON time  $t_{\rm ON}$  and turn OFF time  $t_{\rm OFF}$  as a function of the load resistance  $R_{\rm L}$   $V_{\rm S}$  = 13.5V,  $T_{\rm i}$  = 25°C

Figure 32 Typical turn ON time  $t_{\rm ON}$  and turn OFF time  $t_{\rm OFF}$  as a function of the supply voltage  $V_{\rm S}$   $T_{\rm i}$  = 25°C,  $R_{\rm i}$  = 1 $\Omega$

Figure 33 Typical switch ON energy  $E_{\rm ON}$  and switch OFF energy  $E_{\rm OFF}$  as a function of the junction temperature  $T_{\rm j}$   $V_{\rm S}$  = 13.5V,  $R_{\rm L}$  = 1 $\Omega$

Figure 34 Typical switch ON energy  $E_{\rm ON}$  and switch OFF energy  $E_{\rm OFF}$  as a function of the load resistance  $R_{\rm L}$   $V_{\rm S}$  = 13.5V,  $T_{\rm i}$  = 25°C

Typical switch ON energy  $E_{\rm ON}$  and switch OFF energy  $E_{\rm OFF}$  as a function of the supply voltage  $V_{\rm S}$   $T_{\rm i}$  = 25°C,  $R_{\rm L}$  = 1 $\Omega$

Figure 36 Typical output voltage drop limitation  $V_{\rm SD(CL)}$  as a function of the junction temperature  $T_{\rm j}$   $I_{\rm L}$  = 40mA,  $V_{\rm IN}$  = LOW

# 6.2.2 Input Circuit

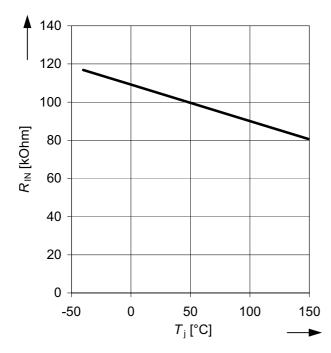

Figure 37 Typ. input pull down resistor  $R_{IN}$  as a function of the junction temperature  $T_{i}$

#### 6.2.3 Protection Functions

Figure 38 Typical short circuit shutdown threshold as a function of the supply voltage  $V_{\rm S}$ ;  $T_{\rm i}$  = 25°C

Figure 39 Typical short circuit shutdown threshold as a function of the junction temperature  $T_j$ ;  $V_S = 13.5 \text{V}$

Figure 40 Typical short circuit overshooting as a function of the  $dI_{\rm SC}/dt$  (device is in ON state when short circuit appears)  $T_{\rm j} = 25\,^{\circ}{\rm C}$

# 6.2.4 Diagnosis Functions

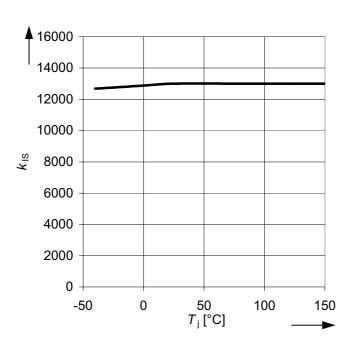

Figure 41 Typical sense current slope  $k_{\rm IS}$  as a function of the junction temperature  $T_{\rm j}$   $V_{\rm S}$  = 13.5V,  $I_{\rm L1}$ =13.5A,  $I_{\rm L2}$ =0A,  $V_{\rm IN}$ =HIGH

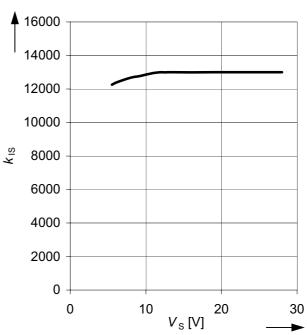

Figure 42 Typical sense current slope  $k_{\rm IS}$  as a function of the supply voltage  $V_{\rm S}$   $T_{\rm i}$  = 25°C,  $I_{\rm L1}$ =13.5A,  $I_{\rm L2}$ =0A,  $V_{\rm IN}$  = HIGH

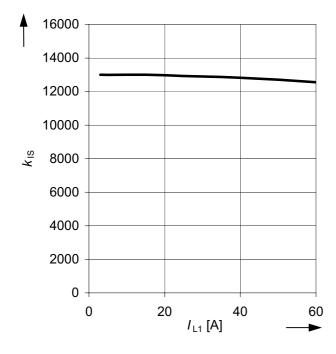

Figure 43 Typical sense current slope  $k_{\rm IS}$  as a function of the load current  $I_{\rm L1}$   $V_{\rm S}$  = 13.5V,  $T_{\rm I}$  = 25°C,  $I_{\rm L2}$ =0A,  $V_{\rm IN}$  = HIGH

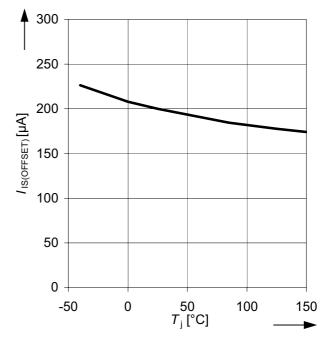

Figure 44 Typical sense current offset  $I_{\rm IS(OFFSET)}$  as a function of the junction temperature  $T_{\rm j}$   $V_{\rm S}$  = 13.5V,  $V_{\rm IN}$  = HIGH

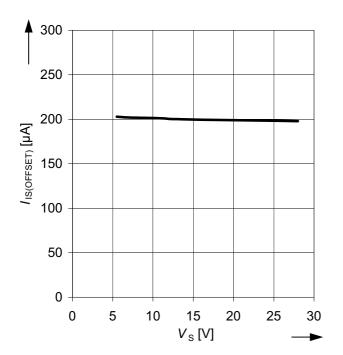

Figure 45 Typical sense current offset  $I_{\rm IS(OFFSET)}$  as a function of the supply voltage  $V_{\rm S}$   $T_{\rm i}$  = 25°C,  $V_{\rm IN}$  = HIGH

Figure 46 Typical leakage current  $I_{\rm IS(LL)}$  at the sense output as a function of the junction temperature  $T_{\rm j}$   $V_{\rm S}$  = 13.5V,  $V_{\rm IN}$  = LOW for t >  $t_{\rm RESET}$

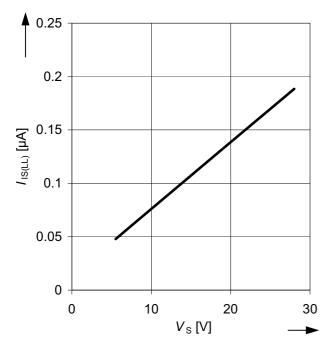

Figure 47 Typical leakage current  $I_{\rm IS(LL)}$  at the sense output as a function of the supply voltage  $V_{\rm S}$   $T_{\rm j}$  = 25°C,  $V_{\rm IN}$  = LOW for t >  $t_{\rm RESET}$

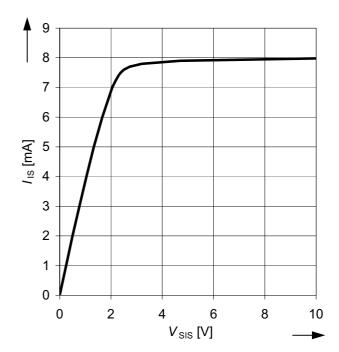

Figure 48 Typical fault current  $I_{\rm IS(fault)}$  at the sense output as a function of the voltage  $V_{\rm SIS}$  =  $V_{\rm S}$  -  $V_{\rm IS}$   $V_{\rm S}$  = 13.5V,  $V_{\rm IN}$  = HIGH

160 140 120 100 80 60 40 20 0 0 10 30 20  $V_{S}[V]$ -t\_sIS(ON) — -t\_sIS(OFF)

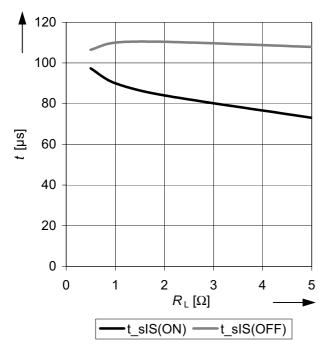

Figure 49 Typical current sense settling time for turn ON  $t_{\rm sIS(ON)}$  and turn OFF  $t_{\rm sIS(OFF)}$  as a function of the load resistance  $R_{\rm L}$   $V_{\rm S}$  = 13.5V,  $T_{\rm i}$  = 25°C

Figure 50 Typical current sense settling time for turn ON  $t_{\rm sIS(ON)}$  and turn OFF  $t_{\rm sIS(OFF)}$  as a function of the supply voltage  $V_{\rm S}$   $T_{\rm i}$  = 25°C,  $R_{\rm L}$  = 1 $\Omega$

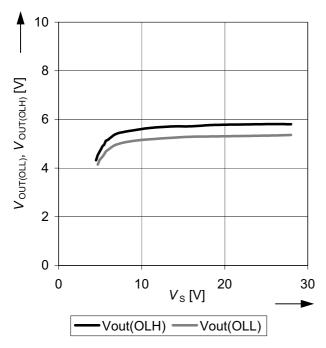

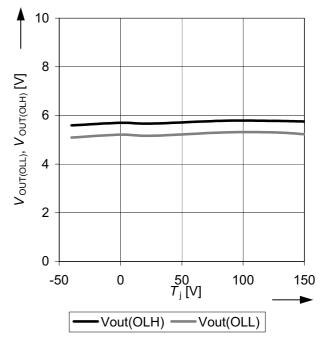

Figure 51 Typical output voltage thresholds for open load detection during OFF  $V_{\rm OUT(OLH)} \ {\rm and} \ V_{\rm OUT(OLL)} \ {\rm as} \ {\rm a} \ {\rm function} \ {\rm of} \ \ {\rm the} \ {\rm supply} \ {\rm voltage} \ V_{\rm S}$   $T_{\rm i} = 25^{\circ}{\rm C}$

Figure 52 Typical output voltage thresholds for open load detection during OFF  $V_{\rm OUT(OLH)}$  and  $V_{\rm OUT(OLL)}$  as a function of the junction temperature  $T_{\rm j}$   $V_{\rm S}$  = 13.5V

**Application Information**

# 7 Application Information