T-51-09-90

LD1104

## VIDEO DAC WITH LOOK-UP TABLE

#### DESCRIPTION

The LD1104 is a digital to analog converter with an internal look-up table designed to drive a 75 ohm line. The output of the DAC is designed to produce 0.7 volts peak white amplitude when driving a 75 ohm line with an IREF of 4.4 mA or when driving a doubly terminated 75 ohm load with an IREF of 8.8 mA. The DAC outputs will be set to their minimum values during the blanking pulse period.

#### **FEATURES**

- \* Pin to pin compatible with IMS G171/G176

- \* 256K possible colors

- \* Microprocessor compatible interface

- \* Low power CMOS design

- \* 6 bit DAC per gun and RGB analog output

- \* Pixel rates up to 65 MHz

- \* Pixel word mask

- \* TTL compatible inputs

- \* Single 5 volts operating voltage

#### APPLICATIONS

- \* VGA graphic card

- \* Workstations with color output

- \* Color terminals

- \* Raster scan video systems

#### ORDERING INFORMATION

| Part number   | Package | Operating temperature |  |  |

|---------------|---------|-----------------------|--|--|

| LD1104CP28-៤5 | Plastic | 0°C to 70°C           |  |  |

| LD1104CJ44-65 | PLCC    | 0°C to 70°C           |  |  |

| LD1104CP28-50 | Plastic | 0°C to 70°C           |  |  |

| LD1104CJ44-50 | PLCC    | 0°C to 70°C           |  |  |

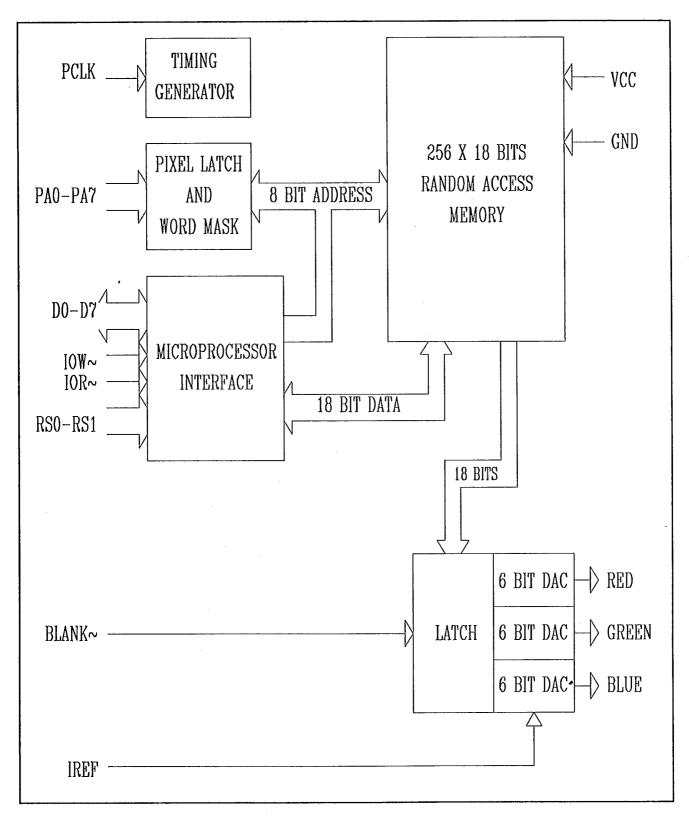

#### **GENERAL DESCRIPTION**

The LD1104 is designed to operate in a high speed analog and digital video interface environment to provide 256 different colors.

The display colors can be changed to facilitate animation, flashing or overlay objects with a single write cycle, by utilizing the pixel word mask capability without modifying the look-up table. A high speed internal random access memory has been provided to pipeline a 65 MHz pixel rate output in three clock cycles. An external blanking signal can be input to the LD1104 to synchronize the pixel stream.

The contents of the look-up table (random access memory) can be accessed via an 8 bit wide microprocessor interface bus without disturbing the video path.

## **BLOCK DESCRIPTION**

## **SYMBOL DESCRIPTION**

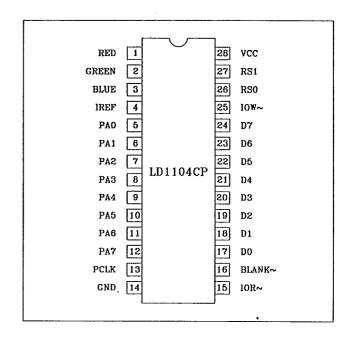

| Symbol          | Pin   | Symbol type | Pin description                                                                                                                                                                                                                     |  |  |  |  |

|-----------------|-------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| RED             | 1     | 0           | Video DAC RED signal output.                                                                                                                                                                                                        |  |  |  |  |

| GREEN           | 2     | 0           | Video DAC GREEN signal output.                                                                                                                                                                                                      |  |  |  |  |

| BLUE            | 3     | 0           | Video DAC BLUE signal output.                                                                                                                                                                                                       |  |  |  |  |

| IREF            | 4     | I           | Reference current input. The external current source is applied this pin to regulate the internal DAC current source. Each current source produces 1/30 of the IREF when turned on.                                                 |  |  |  |  |

| PA0-PA7         | 5-12  | I           | Pixel address. The byte wide value sampled on these inputs is masked by the pixel Mask Register and then used as the address into the color look-up table.                                                                          |  |  |  |  |

| PCLK            | 13    | 1           | Pixel clock. The pixel address and blanking inputs are sampled at the rising edge of PCLK.                                                                                                                                          |  |  |  |  |

| GND             | 14    | 0           | Ground. Signal and power ground.                                                                                                                                                                                                    |  |  |  |  |

| IOR~            | 15    |             | I/O read strobe. (active low) A low on this pin will transfer the contents of the addressed memory or the color information to the data bus.                                                                                        |  |  |  |  |

| BLANK~          | 16    | I           | Blanking input. (active low) A low level on this input, when sampled at the rising edge of PCLK, will cause a color value of zero to be applied to the inputs of the three DACs regardless of the color value of the current pixel. |  |  |  |  |

| D0-D7           | 17-24 | 1/0         | Bidirectional I/O data bus. The contents of the data bus are transferred from the LD1104 internal registers to the host processor or vice-versa.                                                                                    |  |  |  |  |

| IOW~            | 25    | I           | I/O write strobe. (active low) A low on this pin will transfer the contents of the data bus to the addressed register or the internal memory (RAM).                                                                                 |  |  |  |  |

| RS0             | 26    | 1           | Least significant bit of the register select.                                                                                                                                                                                       |  |  |  |  |

| RS1             | 27    | 1           | Most significant bit of the register select.                                                                                                                                                                                        |  |  |  |  |

| V <sub>cc</sub> | 28    | . 1         | Power supply input.                                                                                                                                                                                                                 |  |  |  |  |

## REGISTERS PROGRAMMING TABLE:

| RS1              | RS0              | IOW~                                                            | IOR~                                              |  |  |

|------------------|------------------|-----------------------------------------------------------------|---------------------------------------------------|--|--|

| 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | PIXEL ADDRESS A<br>COLOR VALUE<br>PIXEL MASK<br>PIXEL ADDRESS B | PIXEL ADDRESS A<br>COLOR VALUE<br>PIXEL ADDRESS B |  |  |

### REGISTER DESCRIPTIONS

#### PIXEL ADDRESS REGISTER A/B

The contents of the PIXEL ADDRESS REGISTER A are identical to the contents of the PIXEL ADDRESS REGISTER B during the read operation.

Writing to PIXEL ADDRESS A will specify an address within the color look-up table and initializes the color value register. Writing into PIXEL ADDRESS REGISTER B specifies an address within the color look-up table and loads the color value register with the contents of the location in the color look-up table address and then increments the PIXEL ADDRESS REGISTER.

### **COLOR VALUE REGISTER**

The color value register is internally an 18 bit wide (6 bits per color) register used as a buffer between the microprocessor interface and the color look-up table. To perform a read or write to this register it is required to have a sequence of three byte transfers from or to the register. Note that only the six least significant bits of the bus are used during the write mode and the rest are set to zero during the read mode. The internal address pointer is set to the RED color address and then increments to the GREEN and BLUE color addresses regardless of the read or write operation sequence.

After writing three values to this register its contents are written to the location in the color look-up table specified by the pixel address register and copied into the COLOR VALUE REGISTER. The PIXEL ADDRESS REGISTER then increments.

### **PIXEL MASK REGISTER**

The PIXEL MASK REGISTER can be used to mask selected bits of the pixel address value applied to the

PIXEL ADDRESS input (PA7-PA0). The PIXEL MASK REGISTER is logically anded with the PIXEL ADDRESS bits, writing a zero in each bit position will alter the values to zero. Note that writing a one to this register will not alter the PIXEL ADDRESS bits.

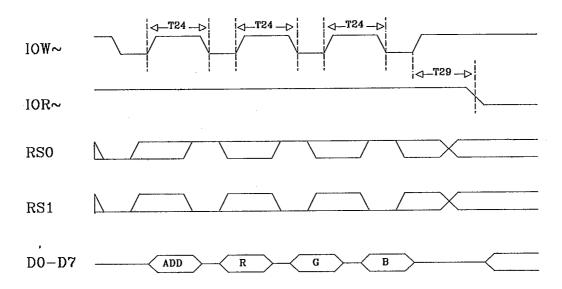

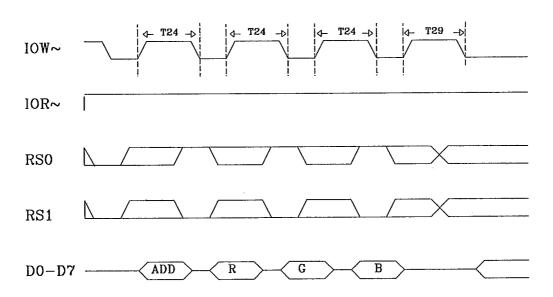

#### WRITING TO THE LOOK-UP TABLE

The color of each pixel can be changed by specifying the location (address of the pixel) in the look-up table via PIXEL ADDRESS REGISTER A. The intensity of each color (RED, GREEN, BLUE) should be written successively in the COLOR VALUE REGISTER (note that three 8 bit data are required). After the last value (BLUE) the address of the PIXEL ADDRESS REGISTER is incremented automatically to reduce the write cycle for consecutive pixel color changes.

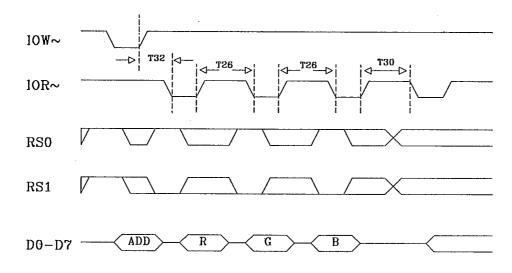

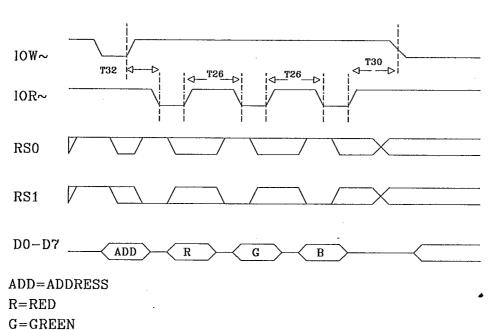

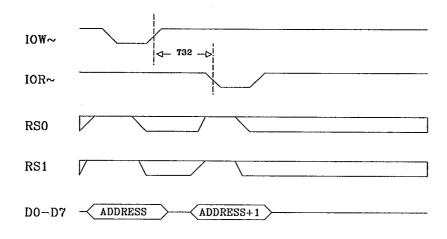

#### **READING FROM THE LOOK-UP TABLE**

The color intensity of each pixel can be read by writing the location (address of the pixel) in the look-up table via PIXEL ADDRESS REGISTER B. The color values (intensity) of each color gun (RED, GREEN, BLUE) can be accessed from the COLOR VALUE REGISTER (note that, three consecutive reads are required to complete the read cycle). After reading the last value (BLUE) the PIXEL ADDRESS REGISTER B is incremented to reduce the read cycle for consecutive pixel reads. The read cycle can be reduced if fewer values are needed to be read by changing the PIXEL ADDRESS REGISTER B. This will terminate the previous read cycle.

T-51-09-90

## **AC ELECTRICAL CHARACTERISTICS**

$T_A$ =25°C ,  $V_{CC}$ =5.0 V± 5% unless otherwise specified

| Symbol          | Parameters                  | Limits           |     |       | Units      | Conditions |

|-----------------|-----------------------------|------------------|-----|-------|------------|------------|

|                 |                             | min              | typ | max   |            |            |

| _               | DOLK marked                 | 00               |     | 40000 | <b>~</b> 0 |            |

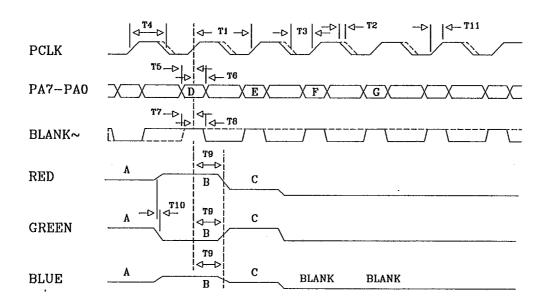

| T,              | PCLK period                 | 20               |     | 10000 | nS<br>%    | mataut     |

| T <sub>2</sub>  | PCLK jitter                 |                  |     | ±2.5  |            | note:1     |

| T <sub>3</sub>  | PCLK low width              | 6                |     | 10000 | nS<br>=0   |            |

| T₄              | PCLK high width             | 6                |     | 10000 | nS<br>~0   |            |

|                 | Pixel Word setup time       | 4                |     |       | nS         | note:2     |

| <u>T</u> 6      | Pixel Word hold time        | 4                |     |       | nS         | note:2     |

| T <sub>7</sub>  | Blank~ setup time           | 4                |     |       | nS         |            |

| T <sub>8</sub>  | Blank~ hold time            | 4                | 1   |       | nS         |            |

| T <sub>9</sub>  | PCLK to valid DAC output    | 5                |     | 30    | nS         | note:3     |

| T <sub>10</sub> | Differential output delay   |                  |     | 1     | nS         | note:4     |

| T <sub>11</sub> | Pixel clock transition time |                  |     | 50    | nS         |            |

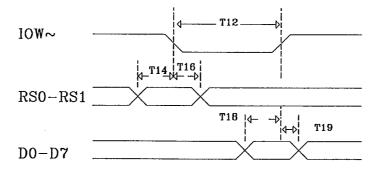

| T <sub>12</sub> | IOW~ pulse width low        | 50               |     |       | nS         |            |

| T <sub>13</sub> | IOR~ pulse width low        | 50               |     |       | nS         |            |

| T <sub>14</sub> | Register select setup time  | 10               |     |       | nS         |            |

| T <sub>15</sub> | Register select setup time  | 10               |     |       | nS         |            |

| T <sub>16</sub> | Register select hold time   | 10               |     |       | nS         |            |

| T <sub>17</sub> | Register select hold time   | 10               |     |       | nS         |            |

| T''8            | Write data setup time       | 10               |     |       | nS         |            |

| T'19            | Write data hold time        | 10               |     |       | nS         |            |

| T <sub>20</sub> | Output turn on delay        | 5                |     |       | nS         |            |

| T <sub>21</sub> | Read enable access time     |                  |     | 40    | nS         |            |

| T <sub>22</sub> | Output hold time            | 5                |     | 1     | nS         |            |

| T <sub>23</sub> | Output turn off delay time  |                  |     | 20    | nS         | note:5     |

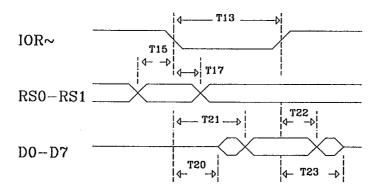

| T <sub>24</sub> | Successive write interval   | 3*T,             |     |       | nS         | 1101010    |

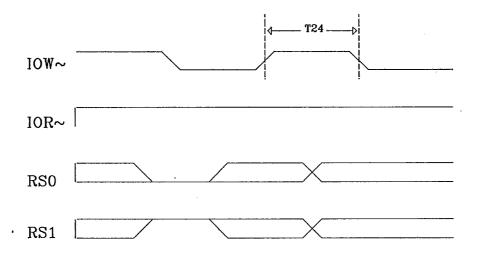

| T <sub>25</sub> | Write followed by           | 3*T,             |     |       | nS         |            |

| 1 25            | read interval               | 1 0 11           |     |       | 110        |            |

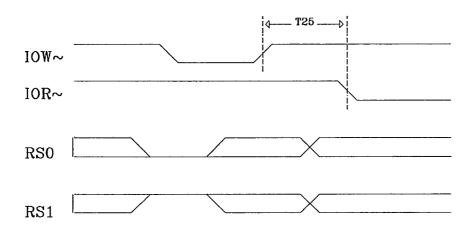

| T <sub>26</sub> | Successive read interval    | 3*T,             |     |       | nS         |            |

|                 | Read followed by            | 3*T,             |     |       | nS         |            |

| T <sub>27</sub> | write interval              | 1 0 11           |     |       | 110        |            |

| -               | Write after color write     | 3*T,             |     |       | nS         | noto:6     |

| T <sub>28</sub> | l e                         | 0"1 <sub>1</sub> |     |       |            | note:6     |

| T <sub>29</sub> | Read after color write      | 3*T,             |     |       | nS<br>~C   | note:6     |

| T <sub>30</sub> | Read after color read       | 3*T,             |     |       | nS<br>~C   | note:6     |

| T <sub>31</sub> | Write after color read      | 3*T,             |     | ]     | nS<br>0    | note:6     |

| T <sub>32</sub> | Read after read address     | 3*T,             |     |       | nS         | note:6     |

| _               | write                       | 1                |     |       | _          |            |

| T <sub>33</sub> | Write/Read enable           | 50               |     |       | nS         |            |

|                 | transition time             |                  |     |       |            |            |

|                 |                             |                  |     |       | •          |            |

| <u> </u>        | <u>L</u>                    | J                | L   | 1     | <u> </u>   | <u> </u>   |

## **ABSOLUTE MAXIMUM RATINGS**

Operating supply range Voltage at any pin Storage temperature Operating temperature Package dissipation 5 Volts ±5% GND-0.3V to V<sub>CC</sub>+0.3V -40°C to +150°C 0°C to 70°C 500mW

### DC ELECTRICAL CHARACTERISTICS

$T_A$ =25°C,  $V_{CC}$ =5.0V ± 5% unless otherwise specified

| Symbol Parameters                                                                                                                                                                  | Parameters                                                                                                                                                                                                                                          | Limits                                       |                   |                                      | Units                                          | Conditions               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-------------------|--------------------------------------|------------------------------------------------|--------------------------|

|                                                                                                                                                                                    |                                                                                                                                                                                                                                                     | min                                          | typ               | max                                  |                                                |                          |

| V <sub>CC</sub> I <sub>CC</sub> I <sub>REF</sub> V <sub>AO</sub> I <sub>AO</sub> D <sub>DTD</sub> D <sub>DIL</sub> I <sub>IL</sub> V <sub>IH</sub> V <sub>OL</sub> V <sub>OH</sub> | Operating supply Operating current Reference current DAC output level DAC output current DAC to DAC correlation DAC internal linearity Input Low current Input High current Input High level Output Low level pin D0-D7 Output High level pin D0-D7 | 4.5<br>4.0<br>1.5<br>21<br>±2<br>±0.5<br>-10 | 5.0<br>8.8<br>2.4 | 5.5<br>190<br>10<br>10<br>0.8<br>0.4 | V<br>mA<br>V<br>MA<br>%<br>LSB<br>uA<br>V<br>V | Isink=8mA<br>Isource=8mA |

T-51-09-90

#### Note: 1

This parameter for allowed variation in the PCLK frequency but does not permit the PCLK period to vary outside the minimum and maximum values for PCLK period specified above.

#### Note: 2

It is required that the Pixel address input to the color look-up table be set up as a valid logic level with the appropriate setup and hold times to each rising of PCLK.

#### Note: 3

A valid analog output is defined when the changing analog signal is half way between its successive values. This parameter is stable with time but can vary between different devices and may vary with different DC operating conditions.

#### Note: 4

Between different analog outputs on the same device.

#### Note: 5

Measured  $\pm 200$  mV from steady state output voltage.

#### Note: 6

This parameter allows for synchronization between operations on the microprocessor interface and the pixel stream being processed by the color lookup table.

#### **DESIGN CONSIDERATIONS**

The LD1104 is fabricated in 2u CMOS technology to meet 50 MHz pixel speed requirements. Extra precautions are required to prevent damages due to electrostatic voltage discharge during handling and system manufacturing.

To reduce the high speed video DAC switching noises from the board or other logics, a large value capacitor (typ. 47 uF) is recommended to be connected from  $V_{\rm CC}$  to GND pin. RGB outputs should be protected with high speed diodes going to GND and  $V_{\rm CC}$ .

For stable output levels over the temperature variations, an active current source is recommended for IREF input connection.

## **TIMING DIAGRAM**

## WRITE CYCLE

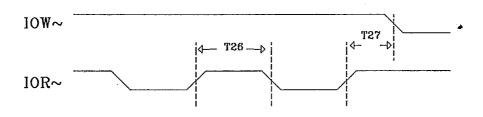

## READ CYCLE

T-51-09-90

## **TIMING DIAGRAM**

WRITE TO PIXEL MASK REGISTER FOLLOWED BY ANY ACCESS

## **TIMING DIAGRAM**

B=BLUE

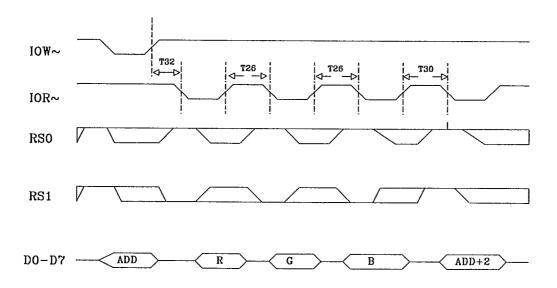

#### COLOR VALUE READ FOLLOWED BY ANY READ

## COLOR VALUE READ FOLLOWED BY ANY WRITE

7-51-09-90

## **TIMING DIAGRAM**

## COLOR VALUE WRITE FOLLOWED BY ANY READ

## COLOR VALUE WRITE FOLLOWED BY ANY WRITE

## **TIMING DIAGRAM**

### WRITE AND READ BACK ADDRESS REGISTER

T-51-09-90

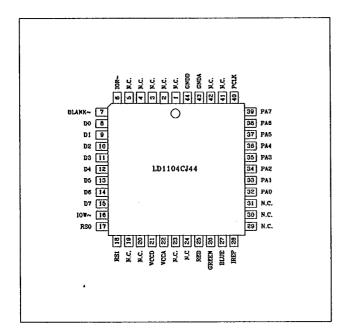

## **44 PIN PLCC PINOUT**