# Optical Comparator Array OPR5011

#### Features:

- · Precise active area location

- Surface mountable

- TTL compatible output

- · Wide supply voltage range

- · Wide operating temperature range

### **Description:**

Each **OPR5011** device is a hybrid sensor array that consists of three channels of the OPTEK OPC8332 differential optical comparator ('TRI-DOC") IC. The single chip construction ensures very tight dimensional tolerances between active areas.

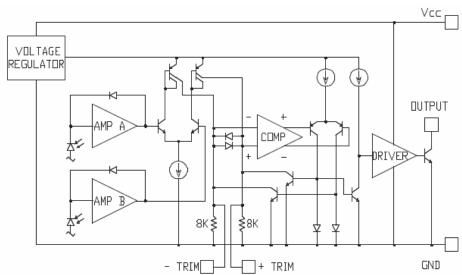

Specifically designed for high-speed/high-resolution encoder applications, the open collector output switches based on the comparison of the input photodiode's light current levels. Logarithmic amplification of the input signals facilitates operation over a wide range of light levels.

The surface-mountable opaque polyimide package shields the photodiodes from stray light and can withstand multiple exposures to the most demanding soldering conditions, while the gold-plated wraparound contacts provide exceptional storage and wetting characteristics.

#### **Applications:**

- · High-speed applications

- High-resolution applications

- Applications requiring a wide range of light levels

| Ordering Information |                                    |                  |                       |                                      |                                    |  |

|----------------------|------------------------------------|------------------|-----------------------|--------------------------------------|------------------------------------|--|

| Part<br>Number       | Sensor                             | # of<br>Elements | Icc (mA)<br>Typ / Max | Optical<br>Hysteresis (%)<br>Typical | Optical<br>Offset (%)<br>Min / Max |  |

| OPR5011              | Differential Optical<br>Comparator | 3                | 9 / 20                | 40.00                                | -40/+40                            |  |

| Pin# | Description | Pin# | Description | Pin# | Description | Pin# | Description |

|------|-------------|------|-------------|------|-------------|------|-------------|

| 1    | B - Output  | 5    | N.C.        | 9    | Z + Trim    | 13   | B + Trim    |

| 2    | B - Vcc     | 6    | A - Output  | 10   | Z -Trim     | 14   | B -Trim     |

| 3    | A + Trim    | 7    | A - Vcc     | 11   | Z - Output  |      |             |

| 4    | A -Trim     | 8    | Common      | 12   | 7 - Vcc     |      |             |

OPTEK reserves the right to make changes at any time in order to improve design and to supply the best product possible.

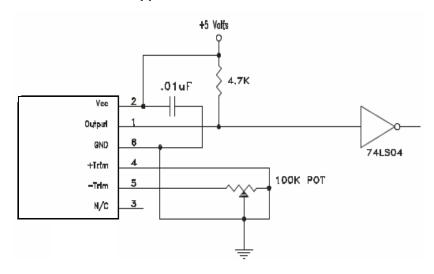

# **Application Circuit - OPR5011**

#### Notes:

- (1) The 74L2)4 is recommended as a means of isolating the "DOC" comparator circuitry from transients induced by inductive and capacitive loads.

- (2) It is recommended that a decoupling capacitor be placed as close as possible to the device.

## **Block Diagram - OPC8332**

OPTEK reserves the right to make changes at any time in order to improve design and to supply the best product possible.

# Optical Comparator Array OPR5011

### **Absolute Maximum Ratings** (T<sub>A</sub> = 25° C unless otherwise noted)

| Storage and Operating Temperature                                                    | -40° C to +100° C |

|--------------------------------------------------------------------------------------|-------------------|

| Supply Voltage                                                                       | 24 V              |

| Output Voltage                                                                       | 24 V              |

| Output Current                                                                       | 14 mA             |

| Power Dissipation                                                                    | 500 mW            |

| Solder reflow time within 5°C of peak temperature is 20 to 40 seconds <sup>(1)</sup> | 250° C            |

## **Electrical Characteristics** (T<sub>A</sub> = 25° C unless otherwise noted)

| SYMBOL           | PARAMETER                                | MIN | TYP | MAX | UNITS | TEST CONDITIONS                                  |

|------------------|------------------------------------------|-----|-----|-----|-------|--------------------------------------------------|

| I <sub>cc</sub>  | Supply Current                           | -   | 9   | 20  | mA    | V <sub>CC</sub> = 24 V                           |

| V <sub>OL</sub>  | Low Level Output Voltage <sup>(2)</sup>  | -   | 0.3 | 0.4 | V     | I <sub>OL</sub> = 14 mA, V <sub>CC</sub> = 4.5 V |

| I <sub>OH</sub>  | High Level Output Current <sup>(3)</sup> | -   | 0.1 | 1   | μΑ    | $V_{CC} = V_O = 20 \text{ V}$                    |

| OPT-HYS          | Optical Hysteresis <sup>(4)(7)</sup>     | -   | 40  | -   | %     | $V_{CC}$ = 5 V, $I_{OL}$ = 1 mA                  |

| OPT-OFF          | Optical Offset <sup>(4)(7)</sup>         | -40 | 10  | +40 | %     | $V_{CC}$ = 5 V, $I_{OL}$ = 1 mA                  |

| f <sub>max</sub> | Frequency Response <sup>(5)</sup>        | -   | 1   | -   | MHz   |                                                  |

| t <sub>lh</sub>  | Output Rise Time <sup>(6)</sup>          | -   | 1   | -   | μs    | V <sub>CC</sub> = 5 V                            |

| t <sub>hl</sub>  | Output Fall Time <sup>(6)</sup>          | -   | 300 | -   | ns    |                                                  |

#### Notes:

- (1) Solder time less than 5 seconds at temperature extreme.

- (2) Pin (+) = 100.0 nW and Pin (-) = 1.0  $\mu$ W.

- (3) Pin (+) = 1.0  $\mu$ W and Pin (-) = 100.0 nW.

- (4) Pin (-) is held at 1.0 μW while Pin (+) is ramped from 0.5 μW to 1.5 μW and back to 0.5 μW.

- (5) Pin (+) is modulated from 1.0 μW to 2.0 μW. Pin (-) is modulated from 1.0 μW to 2.0 μW with phase shifted 180° with respect to Pin (+). Use 100 kΩ trimpot to set the output signal to 50% duty cycle for maximum operating frequency.

- (6) Measured between 10% and 90% points.

- (7) Optical Hysteresis and Optical Offset are found by placing 1.0 μW of light on the inverting photodiode and ramping the light intensity of the non-inverting input from 0.5 μW up to 1.5 μW and back down. This will produce two trigger points an upper trigger point and lower trigger point. These points are used to calculate the optical hysteresis and offset.

These are defined as:

Where:

P in (-) = Light level incident upon the "-" photodiode on the IC chip (Pin) (-) = 1.0  $\mu$ W).

P rise = Value of light power level incident upon the "+" photodiode that his required to switch the digital output when the light level is an increasing level (rising edge).

P fall = Value of light power level incident upon the "+" photodiode that is required to switch the digital output when the light level is decreasing level (falling edge).

P average = (P rise + P fall)

2

OPTEK reserves the right to make changes at any time in order to improve design and to supply the best product possible