Advance Data Sheet January 1992

# ATT7C342 High-Speed CMOS 1 Mbit (64K x 16) SRAM Synchronous, Pipelined Architecture TTL Compatible Common I/O

#### **Features**

- High speed—10 ns maximum access times

- Fast read/write cycle times: 20 ns min (50 MHz)

- Ideally suited as high-speed cache memory for RISC applications

- Internal self-timed write pulse generation

- Fully pipelined architecture

- Registered addresses, data I/O, and control inputs

- Low-power operation

- Advanced 0.5 μm CMOS technology

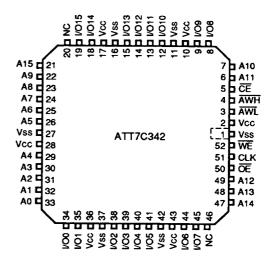

- Available in 52-pin, PLCC package

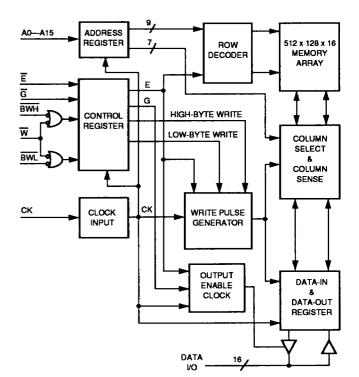

## **Description**

The ATT7C342 devices are high-performance, CMOS static RAMs organized as 65,536 words by 16 bits. The data-in and data-out signals share I/O pins. The device has single chip enable and an output enable. The output is 3-stated when either chip enable or output enable is high.

The address (A0—A15), data-in outputs (I/O0—I/O15), write enable ( WE ), high byte write enable ( BWH ), low byte write enable ( BWL ), chip enable ( CE ), and output enable ( OE ) are latched, positive edge-triggered registers.

Output registers provide full pipelined operation. At the rising edge of the clock, the output from the previous cycle is presented.

Inputs and outputs are TTL compatible. Operation is from a single 5 V power supply. Power consumption is 625 mW (typical) at 20 ns cycle time. Dissipation drops to 500  $\mu W$  (typical) when the memory is in standby mode.

#### Pin Information

**Table 1. Pin Descriptions**

| Pin        | Function                |

|------------|-------------------------|

| A0A15      | Address Inputs          |

| 1/00—1/015 | Data Input/Output       |

| CLK        | Clock Input             |

| CE         | Chip Enable             |

| OE         | Output Enable           |

| WE         | Write Enable            |

| BWL        | Lower Byte Write Enable |

| BWH        | Upper Byte Write Enable |

| GND        | Ground                  |

| Vcc        | +5 V Supply             |

| NC         | No Connection           |

Figure 2. Pin Diagram

## **Absolute Maximum Ratings**

Stresses in excess of the Absolute Maximum Ratings can cause permanent damage to the device. These are absolute stress ratings only. Functional operation of the device is not implied at these or any other conditions in excess of those indicated in the operational sections of this data sheet. Exposure to Absolute Maximum Ratings for extended periods can adversely affect device reliability.

| Parameter                               | Symbol | Min             | Max | Unit |

|-----------------------------------------|--------|-----------------|-----|------|

| Storage Temperature                     | Tstg   | -65             | 150 | °C   |

| Operating Ambient Temperature           | TA     | <del>-</del> 55 | 125 | °C   |

| Supply Voltage with Respect to Ground   | Vcc    | -0.5            | 7.0 | V    |

| Input Signal with Respect to Ground     | _      | -3.0            | 7.0 | V    |

| Signal Applied to High-impedance Output |        | -3.0            | 7.0 | V    |

| Output Current into Low Outputs         | _      |                 | 25  | mA   |

| Latch-up Current                        |        | >200            |     | mA   |

## **Handling Precautions**

The ATT7C342 device includes internal circuitry designed to protect the chip from damaging substrate injection currents and accumulations of static charge. Nevertheless, conventional precautions should be observed during storage, handling, and use to avoid exposure to excessive electrical stress.

## **Recommended Operating Conditions**

| Mode             | Temperature Range (Ambient) | Supply Voltage      |

|------------------|-----------------------------|---------------------|

| Active Operation | 0 °C to 70 °C               | 4.5 V ≤ Vcc ≤ 5.5 V |

#### **Electrical Characteristics**

Over all Recommended Operating Conditions.

**Table 2. General Electrical Characteristics**

| Parameter              | Symbol | Test Conditions             | Min      | Тур | Max       | Unit |

|------------------------|--------|-----------------------------|----------|-----|-----------|------|

| Output Voltage:        |        |                             |          |     |           |      |

| High                   | Voh    | loн = -4.0 mA, Vcc = 4.5 V  | 2.4      | _   | l —       | V    |

| Low                    | Vol    | lol = 8.0  mA, Vcc = 4.5  V | _        |     | 0.4       | V    |

| Input Voltage:         |        |                             |          |     |           |      |

| High                   | ViH    | _                           | 2.0      | _   | Vcc + 0.3 | V    |

| Low                    | ViL    | _                           | -1.0     | _   | 0.8       | V    |

| Input Current          | lix    | Ground ≤ Vin ≤ Vcc          | -10      |     | 10        | μА   |

| Output Leakage Current | loz    | CE is high                  | -10      |     | 10        | μА   |

| Vcc Current:           |        |                             |          |     |           |      |

| Active <sup>1</sup>    | ICC1   | <del></del>                 | <b> </b> | 150 | 300       | mΑ   |

| Inactive <sup>2</sup>  | ICC2   |                             | ! — ·    | 50  | 80        | mΑ   |

| Standby <sup>3</sup>   | Icc3   | <u> </u>                    | <u> </u> | 100 | 1,000     | μΑ   |

| Capacitance:           |        |                             |          |     |           |      |

| Input                  | Cı     | <del>-</del>                |          | —   | 5         | pF   |

| Output                 | Co     |                             |          |     | 7         | рF   |

Tested with outputs open, all address and data inputs at TTL level, and the clock running at maximum cycle rate. The device is continously enabled for writing, i.e., CE, OE, and WE ≤ VIL.

## **Timing Characteristics**

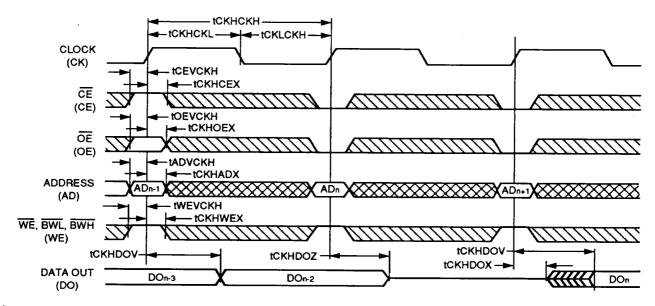

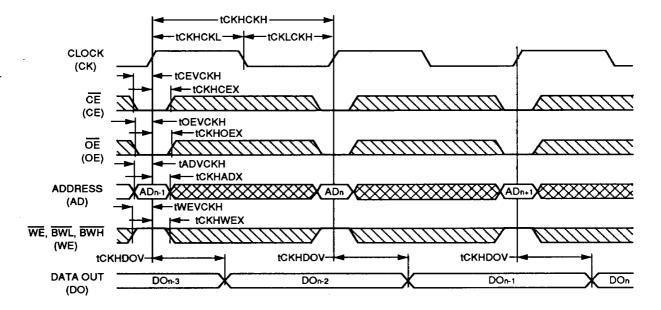

#### Table 3. Read Cycle

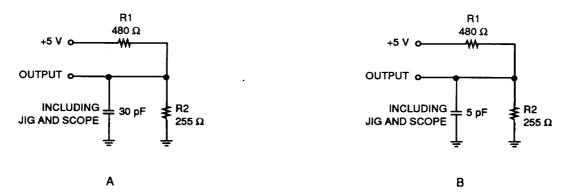

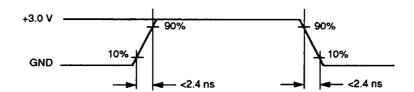

Over all Recommended Operating Conditions; all measurements in ns. Test conditions assume input transition times of <2.4 ns, reference levels of 1.5 V, input pulse levels of 0 V to 3 V (see Figure 9), and output loading for specified lo<sub>L</sub> and lo<sub>H</sub> +30 pF (see Figure 8A).

| Symbol  | Parameter                                          | Min | Max |

|---------|----------------------------------------------------|-----|-----|

| tCKHCKH | Read Cycle Time                                    | 20  | -   |

| tCKHDOV | Clock Access Time                                  |     | 10  |

| tCKHDOX | Output Active from Clock High                      | 1.5 |     |

| tCKHDOZ | Clock High to Q High Z (OE = VIH) (See Figure 8B.) |     | 6   |

| tCKLCKH | Clock Low Pulse Width                              | 7   |     |

| tCKHCKL | Clock High Pulse Width                             | 7   |     |

| tADVCKH | Setup Time for AD                                  | 3   |     |

| tCEVCKH | Setup Time for CE                                  | 3   |     |

| tOEVCKH | Setup Time for OE                                  | 3   |     |

| tWEVCKH | Setup Times for WE, BWH, BWL                       | 3   | _   |

| tCKHADX | Hold Time for AD                                   | 3   | _   |

| tCKHCEX | Hold Time for CE                                   | 3   |     |

| tCKHOEX | Hold Time for OE                                   | 3   | _   |

| tCKHWEX | Hold Time for WE                                   | 3   |     |

<sup>2.</sup> Tested with outputs open and all address and data inputs stable. The device is continuously disabled, i.e., CE = Vcc. Input levels are within 0.2 V of Vcc or ground. Clock is continuously running at maximum cycle rate.

<sup>3.</sup> CE must be ≥ Vcc – 0.2 V. All other inputs must be at either Vcc or ground level to ensure full powerdown. Clock must be running at least two cycles and stop at either Vcc or ground level.

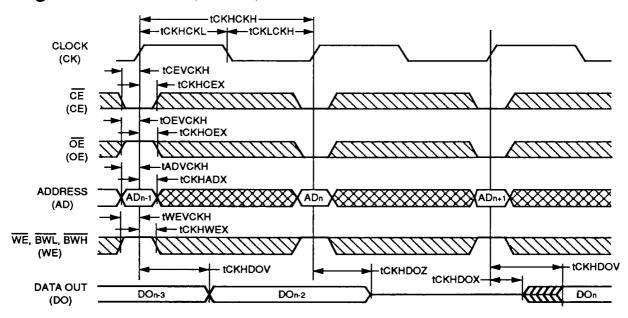

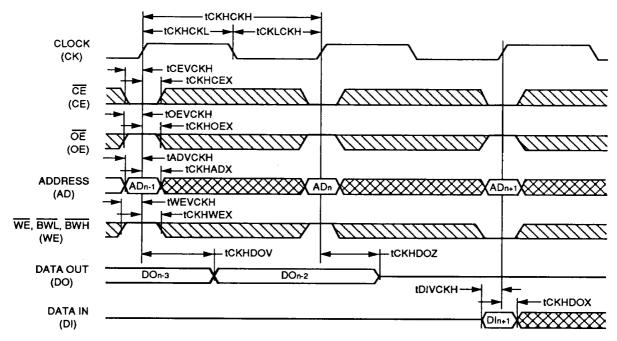

#### Table 4. Write Cycle

Over all Recommended Operating Conditions; all measurements in ns. Test conditions assume input transition times of <2.4 ns, reference levels of 1.5 V, input pulse levels of 0 V to 3 V (see Figure 9), and output loading for specified IoL and IoH +30 pF (see Figure 8A).

| Symbol  | Parameter                                          | Min | Max |

|---------|----------------------------------------------------|-----|-----|

| tCKHCKH | Write Cycle Time                                   | 20  |     |

| tCKHDOZ | Clock High to Q High Z (OE = VIH) (See Figure 8B.) | _   | 6   |

| tCKLCKH | Clock Low Pulse Width                              | 7   |     |

| tCKHCKL | Clock High Pulse Width                             | 7   | _   |

| tADVCKH | Setup Time for AD                                  | 3   |     |

| tCEVCKH | Setup Time for CE                                  | 3   |     |

| tOEVCKH | Setup Time for OE                                  | 3   |     |

| tWEVCKH | Setup Times for WE, BWH, BWL                       | 3   |     |

| tCKHADX | Hold Time for AD                                   | 3   | _   |

| tCKHCEX | Hold Time for CE                                   | 3   | _   |

| tCKHDOX | Hold Time for OE                                   | 3   |     |

| tCKHWEX | Hold Time for WE                                   | 3   |     |

| tDIVCKH | Data-in Valid to Clock High                        | 3   |     |

| tCKHDIX | Data-in Hold Time                                  | 3   |     |

| tCKHDOX | Output Active from Clock High                      | 1.5 |     |

| tCKHDOV | Clock High to Data-out Valid                       |     | 10  |

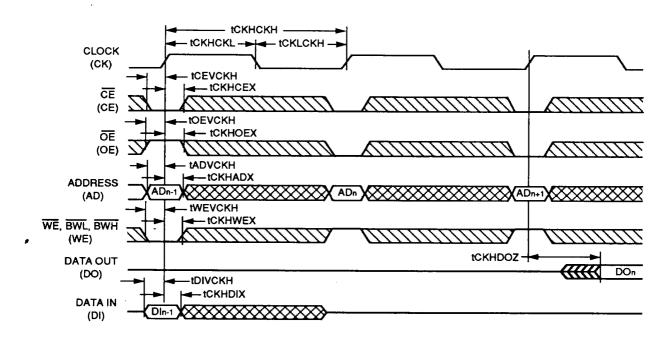

#### **Timing Diagrams**

Notes:

When the CE is high, regardless of the OE level, the outputs 3-state.

The outputs Qn-3 and Qn-2 are from two previous cycles where WE is high, and CE and OE are low.

Figure 3. Read Cycle 1

Figure 4. Read Cycle 2

Figure 5. Read Cycle 3

#### Notes:

Since the device has common I/O, the data out must be 3-stated before the data in can be applied. It is recommended that the data in is applied in the next cycle. OE must be latched in high in the previous cycle.

The outputs Qn-3 and Qn-2 are from two previous cycles where WE is high, CE and OE are low.

Figure 6. Write Cycle

Figure 7. Write/Read Cycle

Figure 8. Test Loads

Figure 9. Transition Times

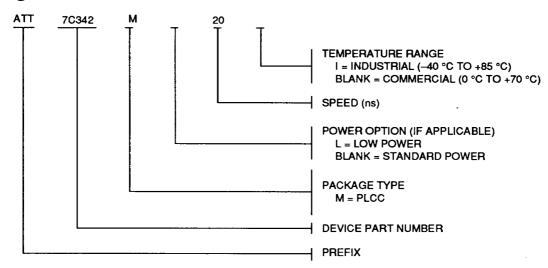

### **Ordering Information**

#### Operating Range 0 °C to 70 °C

| Package Style | Performance Speed |               |  |

|---------------|-------------------|---------------|--|

|               | 25 ns             | 20 ns         |  |

| 52-Pin PLCC   | ATT7C342M-25      | ATT7C342M -20 |  |

For additional information, contact your AT&T Account Manager or the following:

U.S.A.: AT&T Microelectronics, Dept. AL-520404200, 555 Union Boulevard, Allentown, PA 18103

1-800-372-2447, FAX 215-778-4106 (In CANADA: 1-800-553-2448, FAX 215-778-4106)

EUROPE: AT&T Microelectronics, AT&T Deutschland GmbH, Bahnhofstr. 27A, D-8043 Unterfoehring, Germany

Tel. (49) 89 95086-0, FAX (49) 89 95086-331

ASIA PACIFIC: AT&T Microelectronics Asia/Pacific, 14 Science Park Drive, #03-02A/04 The Maxwell, Singapore 0511

Tel. (65) 778-8833, FAX (65) 777-7495, Telex RS 42898 ATTM

JAPAN: AT&T Microelectronics, AT&T Japan Ltd., 31-11, Yoyogi 1-chome, Shibuya-ku, Tokyo 151, Japan

Tel. (03) 5371-2700, FAX (03) 5371-3556

SPAIN: AT&T Microelectronica de España, Poligono Industrial de Tres Cantos (Zona Oeste), 28770 Colmenar Viejo, Madrid, Spain

Tel. (34) 1-8071441, FAX (34) 1-8071420

AT&T reserves the right to make changes to the product(s) or information contained herein without notice. No liability is assumed as a result of their use or application. No rights under any patent accompany the sale of any such product(s) or information.

Copyright © 1992 AT&T All Rights Reserved Printed in U.S.A.

028312 V\_ R