# DDC ILC DATA DEVICE

# MIL-STD-1553 ADVANCED INTEGRATED MUX (AIM) HYBRID

#### **DESCRIPTION**

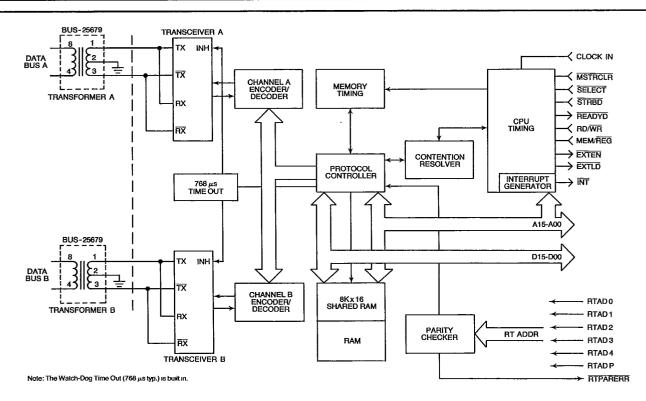

DDC's BUS-61553 Advanced Integrated Mux (AIM) Hybrid is a complete MIL-STD-1553 Bus Controller (BC), Remote Terminal Unit (RTU), and Bus Monitor (MT) device. Packaged in a single 78 pin DIP package, the BUS-61553 contains dual low-power transceivers, complete BC/RTU/MT protocol logic, a MIL-STD-1553-to-host interface unit and an 8K x 16 RAM.

Using an industry standard dual transceiver and standard status and control signals, the BUS-61553 simplifies system integration at both the MIL-STD-1553 and host processor interface levels.

1553 operations are controlled

through the CPU access to the shared 8K x 16 RAM. To ensure maximum design flexibility, memory control lines are provided for attaching external RAM to the BUS-61553 Address and Data Buses and for disabling internal memory; the total combined memory space can be expanded to 64K x 16, All 1553 transfers are entirely memory-mapped; thus the CPU interface requires minimal hardware and/or software support.

The BUS-61553 operates over the full military -55°C to +125°C temperature range. Available screened to MIL-STD-883, the BUS-61553 is ideal for demanding military and industrial microprocessor to 1553 interface applications.

**FEATURES**

- ◆ COMPLETE INTEGRATED MUX INCLUDING:

- LOW POWER DUAL TRANSCEIVER

- BC/RTU/MT PROTOCOL

- 8K x 16 SHARED RAM

- INTERRUPT LOGIC

- COMPATIBLE WITH MIL-STD-1750 AND OTHER STANDARD CPUs

- DIP OR FLATPACK HYBRID

- MINIMIZES CPU OVERHEAD

- PROVIDES MEMORY MAPPED 1553 INTERFACE

- ON-LINE & OFF-LINE SELF-TEST

- IBM PC® DEVELOPMENT TOOLS AVAILABLE

- SEAFAC TESTED

FIGURE 1. BUS-61553 BLOCK DIAGRAM

| TABLE 1. BUS-61553 SPECIFICATIONS                                                                                                                                                                             |                                       |                                                                                                           |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------|--|

| Specifications at nominal power supply voltages.                                                                                                                                                              |                                       |                                                                                                           |  |

| PARAMETER                                                                                                                                                                                                     | VALUE                                 | NOTES                                                                                                     |  |

| RECEIVER Differential Input Voltage Differential Input Impedance CMRR                                                                                                                                         | V <sub>p-p</sub><br>K Ohms<br>dB      | 40 max<br>7 min<br>40 min                                                                                 |  |

| TRANSMITTER (Direct Coupled) Differential Output Voltage Output Rise and Fall Times Output Offset Voltage                                                                                                     | V <sub>p-p</sub><br>n sec<br>mV       | 6.0 min, 9.0 max<br>100 min, 300 max<br>±90 max                                                           |  |

| LOGIC*<br>V <sub>IH</sub><br>V <sub>IL</sub>                                                                                                                                                                  | V<br>V                                | 2.2 min<br>0.8 max                                                                                        |  |

| CLOCK                                                                                                                                                                                                         | MHz                                   | 16                                                                                                        |  |

| POWER SUPPLIES +5V (Logic) -15VA (Chan A Transceiver) -15VB (Chan B Transceiver) +5VA (Chan A) +5VB (Chan B) Current Drain* (Total Package) +5V (Idle) -15V (Idle) +5V (25% Duty Cycle) -15V (25% Duty Cycle) | V<br>V<br>V<br>V<br>mA<br>mA<br>mA    | +5±5%<br>-15±10%<br>-15±10%<br>+5±5%<br>+5±5%<br>(Typ)/max<br>(85)/170<br>(45)/80<br>(85)/170<br>(80)/130 |  |

| TEMPERATURE RANGE Operating (Case) Storage                                                                                                                                                                    | ဗ္                                    | -55 to +125<br>-65 to +150                                                                                |  |

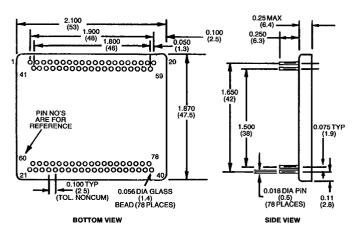

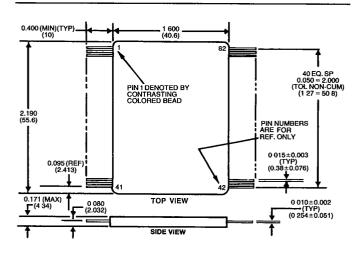

| PHYSICAL CHARACTERISTICS Size 78 pin DIP 82 pin Flatpack Weight                                                                                                                                               | in<br>(mm)<br>in<br>(mm)<br>oz<br>(g) | 2.1 x 1.87 x 0.25<br>(53 x 47.5 x 6.4)<br>2.19 x 1.6 x 1.7<br>(55.6 x 40.6 x 4.34)<br>1.0<br>(29)         |  |

<sup>\*</sup> See Table 7 for pin loading characteristics.

# **GENERAL**

The BUS-61553 is a complete MIL-STD-1553 bus interface unit containing dual low-power transceivers; Bus Controller (BC), Remote Terminal (RTU), and Bus Monitor (MT) protocol logic; 8K x 16-bit pseudo dual port RAM; and memory management arbitration control circuitry. The host processor interface consists of standard control and interrupt signals, memory expansion capability and non-multiplexed address and data buses.

Control of the BUS-61553 is accomplished entirely through the use of three internal registers and the shared RAM. Transfers to and from the BUS-61553 are executed on a word-by-word basis ensuring minimal wait time if contention occurs.

The specific mode of operation (1553 BC/RTU/MT) is software programmable. Memory is configured into unique control and data block areas based on the 1553 mode of operation. External registers are also supported by the BUS-61553 for manipulation of user data. In addition, the BUS-61553 provides dynamic, online and software initiated self-test capabilities.

#### **INTERFACING**

The BUS-61553 is compatible with most common microprocessors including, but not limited to, the Motorola 680 x 0, the Intel 808x, Zilog Z800x and MIL-STD-1750 processors.

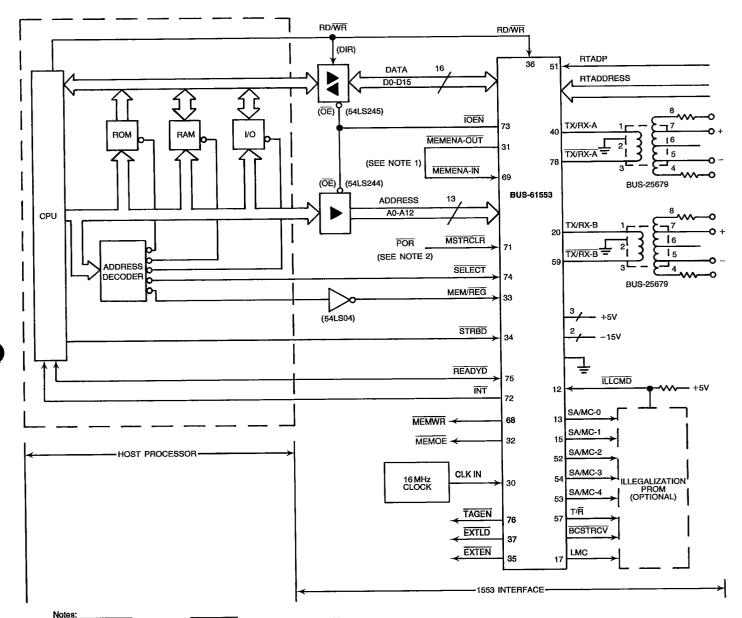

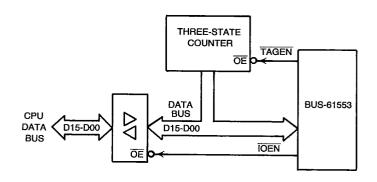

Interfacing the BUS-61553 to the MIL-STD-1553 Data Bus requires two DDC BUS-25679 pulse transformers and an external 16 MHz clock (see figure 2). Tri-state buffers are used to isolate the CPU's data and address lines.

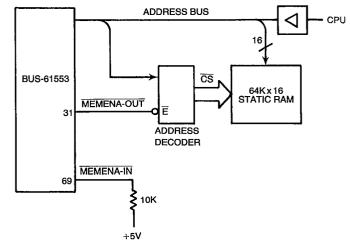

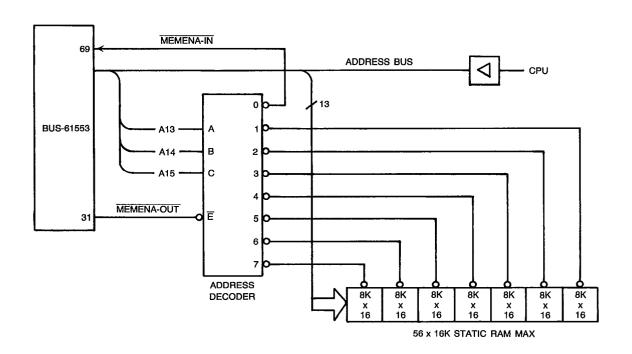

External RAM can be used instead of or in conjunction with the BUS-61553's internal 8K x 16 bits. The external RAM used by the BUS-61553 can be any standard static memory with an access time of ≤55ns. The RAM can be expanded to 64 x 16.

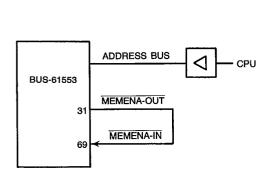

Two control signals, MEMENA-IN (pin 69) and MEMENA-OUT (pin 31) are provided in addition to the standard memory I/O signals for internal/external memory access control (see figures 3-5). MEMENA-OUT and MEMENA-IN should be tied together for Internal Memory Only configuration. Memory CS signals can be generated for configurations using external memory.

#### **MEMORY MANAGEMENT**

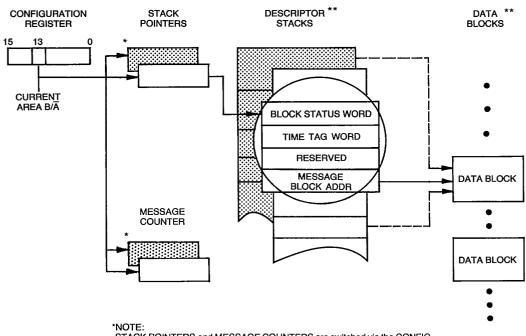

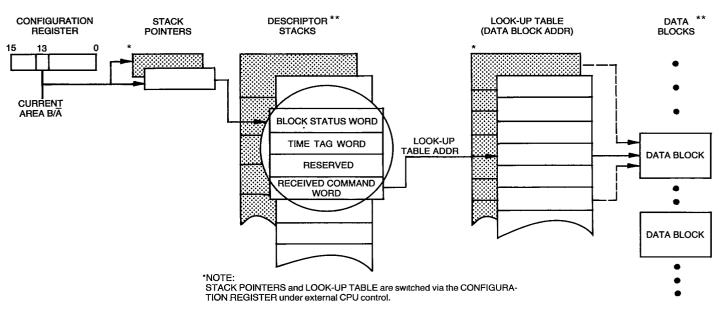

Memory can be configured to support two AREAs (A and B), each with an independent sequential stack and pointers for manipulating 1553 message and control data. The CPU can access the shared RAM while 1553 message transfers are taking place. Arbitration of the RAM is automatically implemented in a manner transparent to the subsystem (see figures 28-31). Variable length DATA BLOCKS are also stored in the shared RAM and can be addressed by setting pointers residing in Area A, Area B or both. For BC/RTU operation, each area contains a Descriptor Stack and Stack Pointer (see figures 6 and 7). BC operation further maintains a Message Count for each area (no. of 1553 messages per frame). RTU operation maintains a data block address Look-Up Table for each area. MT operation utilizes a single Stack Pointer to indicate the starting address for storage of received words and associated Identification Words.

CURRENT AREA ASSIGNMENT/SWAPPING. Current area status (currently available to the 1553 terminal) is software programmable by the host; the unassigned area automatically assumes non-current area status. Both areas are always accessible by the host. Swapping of the Current Area can be done following message transfers for user operations such as exception handling or multiple buffering of 1553 data.

The host selects the Current Area by writing to the BUS-61553's Configuration Register with bit 13 set to the appropriate logic level (0 for area A or 1 for area B). Internal circuitry ensures that the swapping of Current Area Status does not occur during an ongoing message transfer (see Configuration Register).

DESCRIPTOR STACK (BC/RTU). The DESCRIPTOR STACK (DS) is divided into 64 entries. Each stack entry contains four words which refer to one 1553 message. The Block Status Word (BSW) indicates the physical bus on which the message was received (RTU mode), reports whether or not an error was detected during message transfer and indicates message completion (see figure 8).

The user-supplied Time Tag word is loaded at the start of a message transfer and is updated at the end of the transfer (see Time Tagging).

res:

1. MEMENA-OUT is connected to MEMENA-IN only for use of internal RAM.

2. POWER-ON-RESET signal.

3. Pin numbers shown for DIP package.

FIGURE 2. BUS-61553 EXAMPLE INTERCONNECTION

FIGURE 3. INTERNAL MEMORY ONLY

FIGURE 4. EXTERNAL MEMORY ONLY

FIGURE 5. CONFIGURATION USING BOTH INTERNAL & EXTERNAL MEMORY

STACK POINTERS and MESSAGE COUNTERS are switched via the CONFIG-URATION REGISTER under external CPU control.

\*\*NOTE: DESCRIPTOR STACKS and DATA BLOCKS have 256 word boundaries which should be observed.

# FIGURE 6. USE OF DESCRIPTOR STACK - BC MODE

DESCRIPTOR STACKS and DATA BLOCKS have 256 word boundaries which should be observed.

FIGURE 7. USE OF DESCRIPTOR STACK - RTU MODE

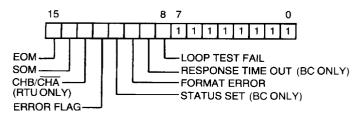

#### **BLOCK STATUS WORD**

Note In BC operation, the BUS-61553 always writes the BSW to RAM with Bit-13, CHB/CHA toggles as per the message control word setting

| DEFINITION Set at the completion of a message transfer                                                                                                                                                                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cat at the completion of a managed transfer                                                                                                                                                                                                                                                                             |

| egardless of whether any errors were detected.                                                                                                                                                                                                                                                                          |

| Set at the beginning of a message transfer and<br>Reset upon completion of the transfer.                                                                                                                                                                                                                                |

| Set in RTU mode to indicate whether the<br>nessage was received on 1553 bus A or bus B.<br>Toggles to indicate channel, in BC mode.                                                                                                                                                                                     |

| ndicates that an error was detected within the nessage transfer. The specific error condition(s) are identified in bits 8-11.                                                                                                                                                                                           |

| Set in BC mode to indicate that a status flag bit was set within the received RTU Status Word or hat the RTU address did not match the associted Command. Set in BC mode when the mesage error bit is set within the received RTU Status Word.                                                                          |

| Also set in RTU mode (RT-RT transfer, BUS-<br>i1553 is acting as the receiving RT) when the<br>ransmitting RTU Status Word contains an incor-<br>ect address. Also, set in BC or RTU mode if the<br>nessage violates MIL-STD-1553 (parity,<br>Manchester, sync bit count, non-contiguous data<br>or word count errors). |

| Set in BC mode if the addressed RTU did not espond within 14 µs. Also set when acting as a eceiving RT (RT-RT transfer) if the transmitting RT does not respond in the specified 1553 esponse time.                                                                                                                     |

| Set when the BUS-61553 does not pass the Loop<br>Test. See Self Test paragraph.                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                         |

#### FIGURE 8. DESCRIPTOR STACK-BLOCK STATUS WORD

The contents of the fourth word of the stack entry depends upon the 1553 operating mode selected. In BC mode, it contains the address of the associated 1553 message (Data Block). In RTU mode, it contains the complete (received) 1553 Command Word.

**STACK POINTER.** A Stack Pointer (SP) is maintained at a specified location in shared RAM for each Descriptor Stack (SP-A: 0100H; SP-B: 0104H). Each Stack Pointer must be initialized by the CPU to point to the Descriptor Stack Entry to be used for the first MIL-STD-1553 transmission.

The current area SP is automatically incremented by four following each message transfer thereby always pointing to the next Block Status Word.

Note: The Stack Pointer is maintained internally using an 8-BIT REGISTER for the HIGH BYTE and an 8-BIT COUNTER for the LOW BYTE. The high byte remains constant (user value) while the low byte will wrap around from FF(H) to 00(H). For example: a current Stack Pointer value of 00 FF(H) will increment to 00 00(H) and not 01 00(H).

**LOOK-UP TABLE (RTU).** A data block address Look-Up Table is used to indicate the data blocks to be used for individual commands. Look-Up is based upon the T/R (transmit/receive) and Subaddress bits of the received 1553 Command Word. See RTU Operation for detailed operation; two tables are provided for double buffering in the RTU mode.

MULTIPLE BUFFERING (BC/RTU). Unused areas of shared RAM can be used to store additional stacks, tables, data blocks and/or user (non 1553-related) data. In this way, multiple data blocks (RTU) or messages (BC) can be stored for later use: simply update respective pointers and initiate the appropriate start conditions. (BC mode requires SP, message block address and message count updating while in RTU mode, the SP and Look-Up Table entry must be updated).

#### **BUS-61553 REGISTERS**

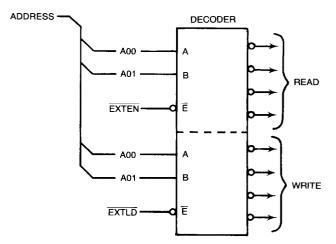

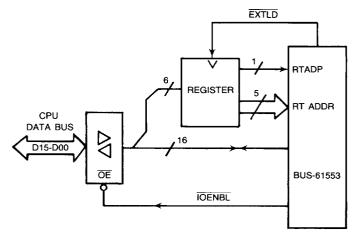

The BUS-61553 is controlled through the use of three internal registers: Interrupt Mask Register, Configuration Register and a Start/Reset register. In addition, the BUS-61553 can access up to four external, user supplied registers (see table 2). Possible external register applications include: CPU Time Tag storage and RTU Address assignment (see figures 9 and 10).

Note: A02 of the BUS-61553 must be set to logic 1 to operate with external registers.

# FIGURE 9. USE OF EXTERNAL REGISTERS

FIGURE 10. EXAMPLE CONFIGURATION USING EXTERNAL REGISTERS

CPU TO REGISTER OPERATIONS. The CPU selects a register by asserting MEM/REG low and A2 to a logic 0 (for internal registers) or logic 1 (for external registers) with A0 and A1 indicating the appropriate register address (see figures 28-32). The signals EXTEN and EXTLD are used to access the external registers.

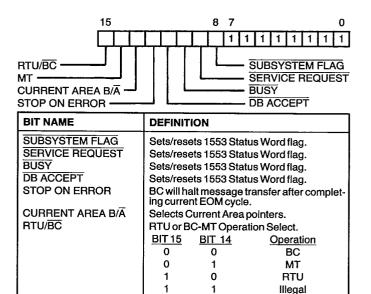

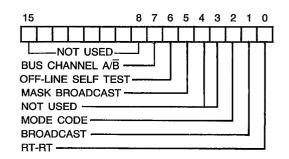

CONFIGURATION REGISTER. The Configuration Register is a 16-bit read/write register used to define the 1553 operating mode (BC, RTU, or MT); define selectable 1553 Status Word bits (RTU only); select stop-on-error option; and support the double buffering scheme (see figure 11).

Note: A logic 0 causes the corresponding bit within the RTU's status word to be set to a logic 1.

FIGURE 11. CONFIGURATION REGISTER

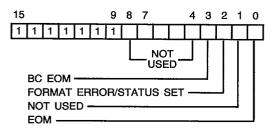

INTERRUPT MASK REGISTER (BC/RTU). This register is a 16-bit read/write register used to enable/mask interrupt conditions. If an interrupt condition occurs and the corresponding Interrupt Register bit has been enabled (set to logic 1) pin 72, INT will be pulsed low during the respective End of Message (EOM) cycle (see figure 12). Not Used bit locations can optionally be used for storing user flags.

| INTERRUPT     | DEFINITION                                                                                                                                                        |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EOM           | End of message. Set by BUS-61553 in BC or<br>RTU mode following each 1553 transfer (regard-<br>less of validity).                                                 |

| FORMAT ERROR/ | Set if one of the following occurs:                                                                                                                               |

| STATUS SET    | Loop Test Failure: Received word does not match last word transmitted.                                                                                            |

|               | Message Error: Received message contained a violation of any of the 1553 message validation criteria (parity, sync, Manchester encoding, bit/word count, etc.).   |

|               | <b>Time-Out:</b> Expected transmission was not received during the allotted time.                                                                                 |

|               | Status Set: Received Status Word contained status bit(s) set or address error.                                                                                    |

| BC EOM        | Bus Controller End of Message. Set by the BUS-61553 following transmission of all messages within the current Message Block. (Current area message count = FFFF). |

FIGURE 12. INTERRUPT MASK REGISTER

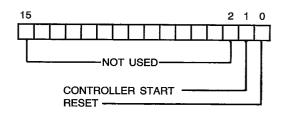

START/RESET REGISTER. This write-only register is used to reset the BUS-61553 and to start the BC and MT operations. as illustrated in figure 13.

|       | BIT 1 | BITO |

|-------|-------|------|

| START | 1     | 0    |

| RESET | 0     | 1    |

| BIT NAME            | DEFINITION                                                                                                                                                                                    |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CONTROLLER<br>START | Issued by the CPU to start message block trans-<br>mission (BC Operation) or to begin reception of<br>1553 messages (MT Operation).                                                           |

| RESET               | Issued by the CPU to place the BUS-61553 in the power-on condition; (1) aborts 1553 transfers currently in progress, and (2) resets Configuration and Interrupt Mask Register bits (logic 0). |

FIGURE 13. START/RESET REGISTER

| TABLE 2. BUS-61553 REGISTER ADDRESS DEFINITION |    |    |     |                         |

|------------------------------------------------|----|----|-----|-------------------------|

| ADDRESS BITS                                   |    |    |     |                         |

| A2                                             | A1 | A0 |     | DEFINITION              |

| 0                                              | 0  | 0  | R/W | Interrupt Mask Register |

| 0                                              | 0  | 1  | R/W | Configuration Register  |

| 0                                              | 1  | 0  | _   | Not Used                |

| 0                                              | 1  | 1  | w   | Start/Reset Register    |

| 1                                              | 0  | 0  | R/W | External Register (1)   |

| 1                                              | 0  | 1  | R/W | External Register (1)   |

| 1                                              | 1  | 0  | R/W | External Register (1)   |

| 1                                              | 1  | 1  | R/W | External Register (1)   |

Note: R/W (read/write) capability is dependent on the user's decoding implementation (see figure 9).

#### **CONTENTION HANDLING**

The BUS-61553 arbitrates shared RAM (and control register) accesses between the host CPU and the internal 1553 protocol

If the host attempts to access the RAM while an internal 1553 memory cycle is in progress, the BUS-61553 will delay the CPU's memory cycle by inserting wait states via the READYD control signal until the cycle has been completed. The maximum delay is 1.8  $\mu$ s.

If the internal 1553 protocol logic attempts to access the RAM while the host CPU has control of the memory, the internal 1553 logic will wait until the host CPU cycle has been completed. To ensure the integrity of 1553 data transfers, the host CPU must complete its memory cycle within 1.5  $\mu$ s (see figures 28-32).

# **SELF TEST**

The BUS-61553 has two self-test modes: the automatic, continuous On-Line test and the software-initiated Off-Line test. In both tests the Loop Test Fail bit within the Block Status Word will be set to a logic 1 if a failure is detected.

ON-LINE TEST. The On-Line test occurs in BC and RTU modes during transmission of each message onto the 1553 bus. This test wraps around the last word transmitted, exercising the 1553 protocol logic through the 1553 transceivers.

While operating as a BC, the last word transmitted is received, decoded, and written back into memory location immediately following the last word within the message block. The host CPU can read and compare this Loop Back Word with the last word of the message Data Block; these two words should be identical. This insures data integrity between the CPU and the BUS-61553.

While in the RTU mode, the internal 1553 Status Word will be updated to reflect the result of the self test. The Status Word's Terminal Flag bit will be set to a logic 1 if a fault was indicated by the wrap-around, self-test.

OFF-LINE TEST. The software-initiated Off-Line test can be executed only when the BUS-61553 is configured as a BC. Set the Wrap-Around Test bit within the BC Control Word to a logic 1 and initiate any standard message transfer. This inhibits the 1553 transceivers and initiates the standard wrap-around test (i.e., internal 1553 encoder output is fed back into the decoder - the word is then written into memory). See BC Operation and Figure 14, BC Control Word for more detail.

|                                | F15                                                                                                                                                                                                                                                         |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BIT NAME                       | DEFINITION                                                                                                                                                                                                                                                  |

| BUS CHANNEL A/B                | Determines whether the message will be transmitted on 1553 Bus A or Bus B. Logic 1 = A, logic 0 = B.                                                                                                                                                        |

| INITIATE OFF-LINE<br>SELF TEST | Logic 1 performs internal off-line transmit/<br>receive test. The last word of the message is<br>looped back through the decoder and placed in<br>RAM. See Self Test paragraph.                                                                             |

| MASK<br>BROADCAST (1)          | When logic 1, prevents Broadcast RCVD bit of<br>the 1553 Status Word response from signalling<br>a status error as a result of a Broadcast com-<br>mand. (A FORMAT error will be generated if the<br>BROADCAST bit is not set on the RTU's Status<br>Word.) |

| MODE CODE                      | When logic 1, the message is treated as a Mode<br>Code. (The Command Word – Word Count field<br>indicates Mode Code type.)                                                                                                                                  |

| BROADCAST                      | When logic 1, indicates that the message is a<br>Broadcast Command. (No Status Word is<br>expected.)                                                                                                                                                        |

| RT-RT                          | When logic 1, the message is treated as an RT-<br>RT transfer. (The next two words are Command<br>Words.) Both Status Word responses are<br>validated.                                                                                                      |

#### Note:

- MASK BROADCAST XOR BROADCAST BIT in Status Word = STATUS SET ERROR.

- When the BC expects the BROADCAST bit set in the Status Word. a logic 1 will mask the Status Interrupt Error flag.

### FIGURE 14. BC CONTROL WORD

# RESET

The BUS-61553 can be reset by pulsing the MSTRCLR (pin 71) low or by writing to the Start/Reset register. After a reset condition has occurred, the Configuration, Interrupt, and (internal) Block Status word register outputs are forced to a logic 0.

The BUS-61553 will automatically access an external, 3-state device (i.e., counter) at the start and end of each message in BC or RTU modes. The BUS-61553 output, TAGEN (pin 76), enables the device's output onto the common, 16-bit data highway while executing a memory-write cycle. The device's value is written into the second location of the Descriptor Stack Entry. If a counter is used, its clock, enable, and reset control lines are connected per system requirement (see figure 15). If no external device is attached to the data bus, an expected value of FFFF (H) will be written into the Time Tag location within the Descriptor Stack.

TIME TAGGING (OPTIONAL) BC & RT DESCRIPTOR

Note that the 8-bit Gap Time value generated in the 1553 MT mode of operation is implemented using an 8-bit counter internal to the BUS-61553 (see MT operation).

FIGURE 15. BC/RT TIME TAGGING (OPTIONAL)

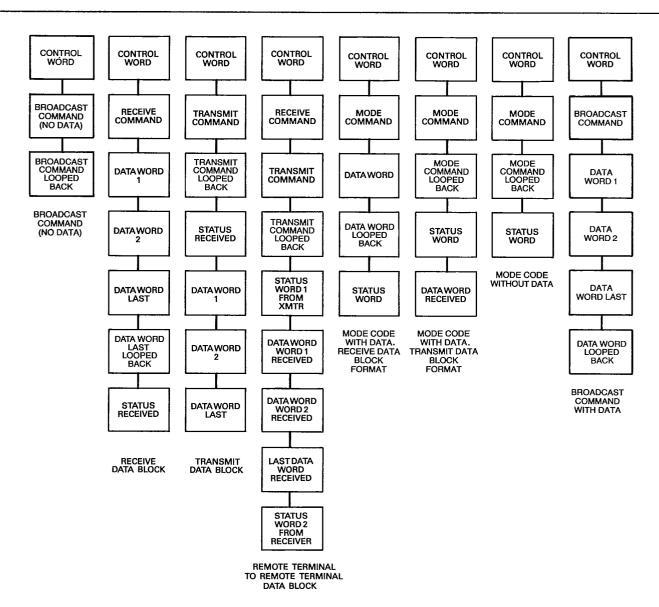

FIGURE 16. BC MESSAGE FORMATS

# **BC OPERATION**

Initialization of the BUS-61553 via a Reset or by setting the appropriate Configuration Register bits will result in placing the BUS-61553 in the BC operating mode.

65E D

BC MEMORY CONFIGURATION. The user configures the memory by: (1) writing the start address of the Descriptor Stack into the Current Area Stack Point location; (2) loading the fourth word of each Descriptor Stack Entry (DSE) with the start location of each message block; and (3) loading the Message Counter with the total number of messages to be transmitted. Note that the Message Count must be written in 1's compliment. For example, to transmit one message, load 00FE(H) (see Table 3, BC Memory Map).

If both map areas A and B are utilized, this procedure must be performed for each area. Note that the Stack Pointer and Message Counter locations are fixed; Message Block locations are user-defined.

Each message block must be proceeded by a BC Control Word (see figure 14). This word informs the BUS-61553 as to the format of the message transfer. Bit 1 of the Control Word defines whether the following message to RT 31 is to be issued in Broadcast Mode or whether RT 31 is a unique terminal. Memory locations must be reserved at the end of each message for: (1) a Loop Back Word; (2) RTU Status Word(s); and (3) received Data words. See Figure 16, BC Message Formats.

Message blocks may be loaded anywhere in the non-fixed area of the shared RAM. However, each data block may not cross a 256 word boundary (i.e., bit 8 of the starting address of the message block must match bit 8 of the address of the last word of the message block).

| TABLE 3. TYPICAL BC MEMORY MAP |                    |  |  |  |

|--------------------------------|--------------------|--|--|--|

| HEX ADDRESS                    | FUNCTION           |  |  |  |

|                                | Fixed Areas        |  |  |  |

| 0100                           | Stack Pointer A    |  |  |  |

| 0101                           | Message Count A    |  |  |  |

| 0104                           | Stack Pointer B    |  |  |  |

| 0105                           | Message Count B    |  |  |  |

|                                | User Defined Areas |  |  |  |

| 0108 - 013F                    | Not Used           |  |  |  |

| 0140 - 017F                    | Data Block 1       |  |  |  |

| 0180 - 01BF                    | Data Block 2       |  |  |  |

| 01C0 - 01FF                    | Data Block 3       |  |  |  |

|                                | •                  |  |  |  |

| •                              | •                  |  |  |  |

| 0F00 - 0FFF                    | Descriptor Stack A |  |  |  |

| 0000 - 00FF                    | Descriptor Stack B |  |  |  |

ADDITIONAL FEATURES. The Configuration Register – STOP ON ERROR bit can be set. This causes the BUS-61553 to halt operation at the end of the current message transfer if an error is detected. In addition, setting the Interrupt Mask Register bits will result in a low pulse on the Interrupt (INT) pin with each occurrence of the respective error, end of message or end of message frame condition (See Configuration Register and Interrupt Register sections).

#### **BC TRANSFER-START SEQUENCE**

After setting the CONTROLLER START bit in the Start/Reset Register, the BUS-61553 takes the following actions:

- Reads the Current Area Stack Pointer for the address of the Descriptor Stack Entry (DSE).

- 2. Stores an SOM (Start of Message) flag in the Block Status word to indicate a transfer operation in progress.

- 3. Writes the Time Tag value into the Descriptor Stack (see Time Tag).

- 4. Reads the Data Block Address from the fourth location of the DSE.

- 5. Starts the MIL-STD-1553 message transfer.

Upon completion of the MIL-STD-1553 message transfer, the BUS-61553:

- Generates an End Of Message (EOM) or Error (if applicable) interrupt if enabled.

- 2. Reads the Stack Pointer for the address of the DSE.

- 3. Updates the Block Status Word; resets SOM, sets EOM, and sets any applicable Error bits.

- 4. Writes the Time Tag value into the Descriptor Stack (see Time Tag).

- Increment Pointers: Stack Pointer incremented by 4 and Message Count incremented by 1.

- If more messages remain to be sent, a BC End Of Message (BCEOM) interrupt occurs (if enabled).

If an error occurs and Stop On Error has been enabled, the BUS-61553 stops initiating BC Transfer-Start sequences. The Stack Pointer will point to the next message to be transferred (see figure 17).

FIGURE 17. BC SEQUENCE OF OPERATION

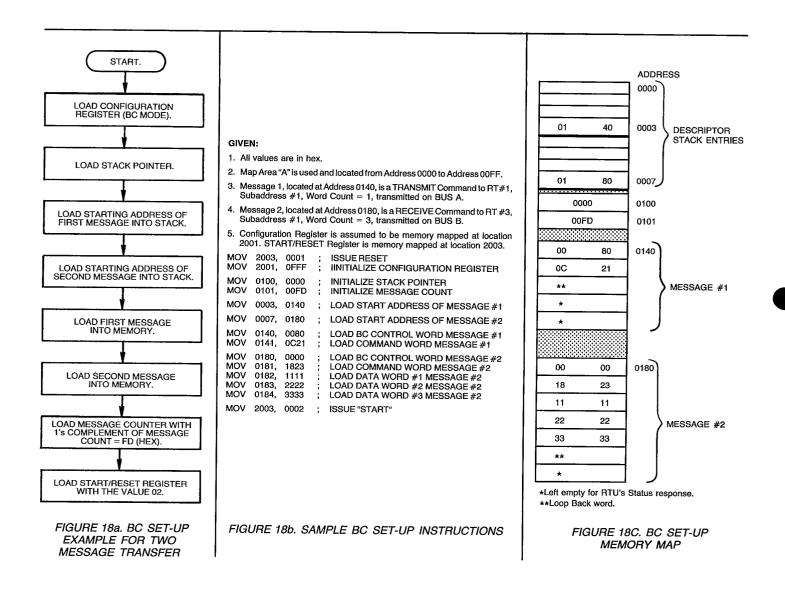

BC SETUP IMPLEMENTATION EXAMPLE

Figure 18a-c shows the BC mode examples for two message transfers, BASIC setup, and BC memory setup.

FIGURE 18. EXAMPLE: BC SET-UP IMPLEMENTATION

#### RTU OPERATION

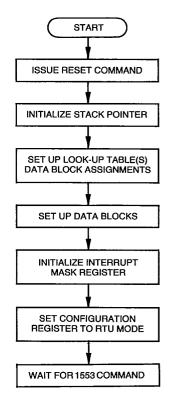

The RTU mode is selected by resetting the BUS-61553 and setting the appropriate bits in the Configuration Register.

RTU MEMORY CONFIGURATION. The user configures the memory by:

- 1. Writing the start address of the Descriptor Stack into the Stack Pointer location and

- 2. Setting up the Look-Up Table as described below.

If both map areas (A and B) are utilized, this procedure must be performed for each area. Note that the Stack Pointer and Look-Up Table locations are fixed; Data Block(s) locations are user-defined. Message blocks may be loaded anywhere in the non-fixed areas of the shared RAM. However, each data block may not cross a 256 word boundary (i.e., bit 8 of the starting address of the message block must match bit 8 of the address of the last word of the message block). An example of a typical RTU Memory Map is given in table 4. Figure 19 shows the RTU Initialization steps.

**TABLE 4. TYPICAL RTU MEMORY MAP FUNCTION HEX ADDRESS Fixed Areas** Descriptor Stack Pointer A 0100 0101 Reserved Descriptor Stack Pointer B 0104 0105 Reserved 0108 - 013F Spare 0140 - 017F Look-Up Table A 01C0 - 01FF Look-Up Table B **User Defined Areas** 0180 - 019F Data Block 1 01A0 - 01BF Data Block 2 0200 - 021F Data Block 3 0EE0 - 0EFF Data Block 107 0000 - 00FF Descriptor Stack A 0F00 - 0FFF Descriptor Stack B

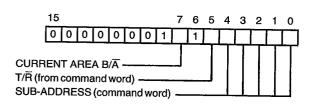

RTU LOOK-UP TABLE. The RTU mode uses a Look-Up Table in order to map the Data Blocks based upon incoming 1553 Command Words. The BUS-61553 uses the T/R and Subaddress fields to address the Look-Up Table. Each Look-Up Table (A and B) location contains a user-defined Data Block Pointer to an associated Data Block (see figures 20 and 21).

Note: The Data Block and Stack Pointers are maintained internally using an 8-BIT-REGISTER for the HIGH BYTE and an 8-BIT COUNTER for the LOW BYTE; the high byte remains constant (user value) while the low byte will wrap around from FF(H) to 00(H). For example: a current Pointer value of 10 FF(H) will increment to 10 00(H) and not 11 00(H).

The first 32 words of the Look-Up Table are reserved for Data Blocks associated with Receive Commands ( $T/\overline{R}$  bit = 0). The remaining 32 words are reserved for Data Blocks associated with Transmit Commands ( $T/\overline{R}$  bit = 1).

Mode Commands with data are mapped in the same manner as non-mode commands. A Synchronize With Data command maps to the first or thirty-second Table entry (depending upon subaddress: all 0's or all 1's), while a Transmit Vector Word command points to the thirty-third or sixty-fourth entry.

**FIGURE 19. RTU INITIALIZATION**

FIGURE 20. RTU LOOK-UP TABLE ADDRESS

|             | RECEIVED COMMAND WORDS  |                         |                                 | DATA BLOCK                                   |

|-------------|-------------------------|-------------------------|---------------------------------|----------------------------------------------|

| T/R         | SUBADD                  | WORD<br>COUNT           | LOOK-UP<br>TABLE (A)<br>ADDRESS | DATA BLOCK                                   |

| 0<br>0<br>0 | 00000<br>00001<br>00010 | XXXXX<br>XXXXX<br>XXXXX | 0140<br>0141<br>0142            | USER DEFINED<br>USER DEFINED<br>USER DEFINED |

|             | 64 LOCATION             | ONS                     | •                               |                                              |

| 1           | 11110<br>11111          | XXXXX                   | 017E<br>017F                    | USER DEFINED<br>USER DEFINED                 |

FIGURE 21. LOOK-UP TABLE EXAMPLE

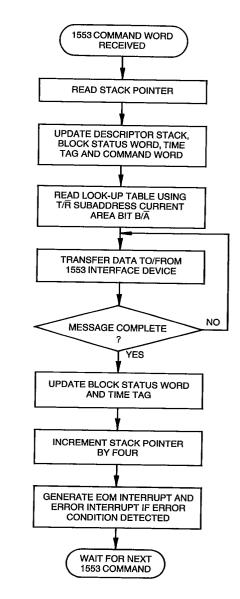

# RTU MESSAGE BLOCK TRANSFER SEQUENCE

RTU message transfer operations begin automatically upon receipt of a valid command word from the 1553 bus. A message transfer takes the form of an RTU Start Of Message (SOM) cycle followed by the 1553 Message Transfer Cycle and an RTU End Of Message (EOM) cycle (see figure 22).

During the RTU SOM cycle, the BUS-61553 takes the following actions:

- 1. Loads the 1553 command word.

- 2. Reads the current area Stack Pointer to get the address of the current Descriptor Stack Entry (DSE).

- 3. Stores an SOM flag into the Block Status Word to indicate a transfer in progress.

- 4. Writes the Time Tag value into the the Descriptor Stack.

- 5. Stores the Command Word received.

- 6. Reads the associated Data Block Address from the (current area) Look-Up Table.

The MESSAGE TRANSFER CYCLE refers to the actual transfer of the 1553 message under control of the BUS-61553. The BUS-61553 transfers data to and from the memory on a word-by-word basis.

Upon completion of the message transfer, the BUS-61553 executes an RTU End Of Message (EOM) cycle during which the BUS-61553:

- 1. Generates an EOM or Error interrupt (if enabled).

- 2. Updates the Block Status Word: clears SOM, sets EOM, and any appropriate error bits.

- 3. Writes the Time Tag value into the Descriptor Stack.

- 4. Increments the Stack Pointer by 4.

FIGURE 22. RTU MESSAGE TRANSFER OPERATION

**ADDITIONAL FEATURES.** Four 1553 Status Word flags can be programmed via the appropriate Configuration Register bits. In addition, setting Interrupt Mask Register bits will result in a low pulse on the Interrupt (INT) pin with each occurrence of the respective error or end of message condition. (See Configuration Register and Interrupt Register sections.)

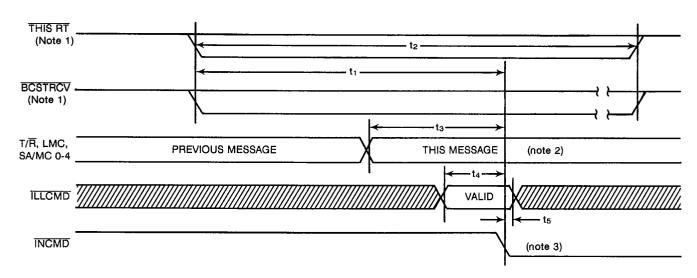

THIS RT: Each command appearing on either 1553 Bus is decoded and tested for Manchester/protocol errors. If the BUS-61553 receives a valid command word containing a RTU address equivalent to the RTAD0-RTAD4 inputs (pins 10, 9, 50, 49, and 11, respectively), THIS-RT (pin 55) will be pulsed low. This signal can be used to identify specific 1553 commands. This signal is also active in the BC mode.

Command Illegalization (Optional). The BUS-61553 has the capability to illegalize MIL-STD-1553 mode commands. In addition, valid non-mode commands can be illegalized based upon the Command Word subaddress field. An illegal command is identified by driving the Illegal Command, ILLCMD (pin 12) input low. The BUS-61553 multiplexes the Word Count and Subaddress fields (pins SA/MCO – SA/MC4).

The BUS-61553 responds to illegalized commands by transmitting its Status Word with the Message Error bit set. No data

words are transmitted; received words, however, are placed in the shared RAM locations indicated by the current area Look-Up Table.

Upon receipt of a valid mode command, the BUS-61553 will output the Command Word-Word Count field and set the Latched Mode Command (LMC) output to a logic 1. Upon receipt of a valid non-mode command, the BUS-61553 will output the Command Word-Subaddress field and set the Latched Mode Command (LMC) output to a logic 0.

An external PROM can be used for command illegalization by decoding the word count/subaddress, LMC and Broadcast Received (BCSTRCV) bits and driving ILLCMD low where appropriate (see figure 23).

**BUSY BIT.** If the user asserts the BUSY bit low in the Configuration Register, the BUS-61553 will respond with a Status Word with the BUSY bit set. In addition, no data words will be transferred from the shared RAM as indicated by the corresponding value in the current area Look-Up Table. The AIM-Hy will transfer data associated with a Receive Command into memory but will not transmit data out onto the MIL-STD-1553 bus when busy upon receipt of a Transmit Command.

| COMMAND ILLEGALIZATION TIMING |                                         |       |     |     |       |

|-------------------------------|-----------------------------------------|-------|-----|-----|-------|

| SYMBOL                        | DESCRIPTION                             | MIN   | TYP | MAX | UNITS |

| t <sub>1</sub>                | THIS RT, BCSTRCV valid delay to INCMD   | 1.475 | -   | -   | μs    |

| <b>t</b> 2                    | THIS RT, BCSTRCV validity time          | 3.7   | -   | 4.3 | μs    |

| t <sub>3</sub>                | T/R, LMC, SA/MC 0-4 setup time to INCMD | 425   | -   | -   | ns    |

| t4                            | ILLCMD setup time to INCMD              | 175   | -   | -   | ns    |

| t <sub>5</sub>                | ILLCMD hold time following INCMD        | 5     | -   | -   | ns    |

#### NOTES:

- 1.THIS RT is asserted low for messages directed to the discrete terminal address.

BCSTRCV is asserted low for messages directed to Address 31, the Broadcast Address.

- 2. T/R, LMC, SA/MC 0-4 remain valid until receipt of next command or Master Reset.

- 3. ILLCMD input sampled internally on falling edge of INCMD.

FIGURE 23. BROADCAST, T/R BIT, LMC, SUBADDRESS/MODE CODE ILLEGALIZATION TIMING

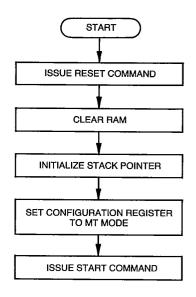

#### MT OPERATION

Initiate a Reset in order to initialize the BUS-61553. Configure the BUS-61553 as a Bus Monitor (MT) by setting the appropriate Configuration Register Bits. See figure 24 for MT initialization steps.

MT MEMORY CONFIGURATION. The user configures the memory by writing the start address for 1553 data storage into the Stack Pointer location. The Monitor Stack will automatically wrap around once the RAM has been filled (i.e., location 1FFF(H) of 8K x 16 RAM is followed by location 0000). An example of a typical MT Memory Map is given in table 5.

| TABLE 5. TYPICAL MT MEMORY MAP |                                |  |

|--------------------------------|--------------------------------|--|

| HEX ADDRESS                    | FUNCTION                       |  |

| 0000                           | First Received 1553 Word       |  |

| 0001                           | First Identification Word      |  |

| 0002                           | Second Received 1553 Word      |  |

| 0003                           | Second Identification Word     |  |

| 0004                           | •                              |  |

| 0005                           | •                              |  |

| 0006                           | •                              |  |

| •                              | •                              |  |

| •                              | •                              |  |

| 0100                           | Stack Pointer (Fixed location) |  |

| •                              | • ' '                          |  |

| •                              | •                              |  |

| 1FFF                           | •                              |  |

MT START SEQUENCE. After setting the CONTROLLER START bit in the Start/Reset Register, the BUS-61553 takes the following actions:

- 1. Reads the start address for 1553 data storage from the Stack Pointer location. The Stack Pointer location(s) will be overwritten with 1553 data once the MT mode has begun [and 1553] data is written into locations 0100(H) and 0101(H)].

- 2. Stores the received 1553 word into memory.

- 3. Increments the Stack Pointer by 1.

- Generates an Identification Word and stores this value into

- 5. Repeats steps 2-4 until a Reset condition occurs.

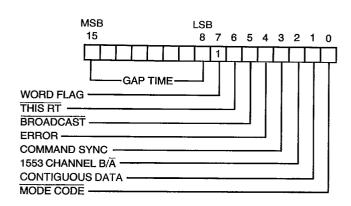

MT IDENTIFICATION WORD. The Identification word provides the CPU with information pertaining to the received 1553 word. Its format is shown in figure 25, This information allows the user to analyze the 1553 data.

THIS-RT: Each command appearing on either 1553 Bus is decoded and tested for Manchester/protocol errors. If the BUS-61553 receives a valid command word containing a Command Sync and a RTU address equivalent to the RTAD0-RTAD4 inputs (pins 10, 9, 50, 49, and 11, respectively), THIS-RT (pin 55) will be pulsed low. This signal can be used to identify specific 1553 commands or for switching to RTU mode upon receipt of a command to this address.

FIGURE 24. MT INITIALIZATION

| BIT NAME           | DEFINITION                                                                                                                                                                                          |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GAP TIME           | Indicates the time between receipt of the previous and current words. Time is indicated in 0.5 $\mu$ s increments for a maximum of 128 $\mu$ s and goes to FF over 128 $\mu$ s. (See Word Gap bit.) |

| WORD FLAG          | Always logic 1.                                                                                                                                                                                     |

| THIS RT            | Logic 0 indicates RT address field of the associ-<br>ated command or Status Word matches the RT<br>address field of the BUS-61553.                                                                  |

| BROADCAST          | Logic 0 indicates the RTU address field of the command or Status Word corresponds to address 31 (decimal).                                                                                          |

| ERROR              | Logic 1 indicates Manchester, Parity, Sync<br>and/or low bit count error.                                                                                                                           |

| COMMAND SYNC       | Logic 1 indicates 1553 Command or Status<br>Word sync field. (Logic 0 indicates a Data Word<br>sync field in received word.                                                                         |

| 1553 CHANNEL B/A   | Indicates word received on 1553 Bus A (1) or<br>Bus B (0).                                                                                                                                          |

| CONTIGUOUS<br>DATA | Logic 1 indicates the word was received within $2\mu s$ of the previous word. If logic 0, bits 8-15 contain the measured gap between the words.                                                     |

| MODE CODE          | When logic 0, the data transferred is a mode command.                                                                                                                                               |

FIGURE 25. MT IDENTIFICATION WORD

65E D

FIGURE 26. MT DATA STORAGE OPERATION

MT DATA STORAGE. Figure 26 shows the steps in a MT data storage operation.

**INTERRUPTS:** SA/MC - 0 (pin 13), SA/MC - 1 (pin 15), and SA/MC – 2 (pin 52) represents B6, B7, and B8 counter outputs in the MT mode. B6 counts every 32 words transferred, B7 every 64 words, and B8 every 128 words. These counter outputs can be used to generate interrupts to the subsystem to insure proper servicing of Memory. The Data Word and Identification Word transfers increment the counter by two.

# **BUILT-IN-TEST WORD (RTU MODE)**

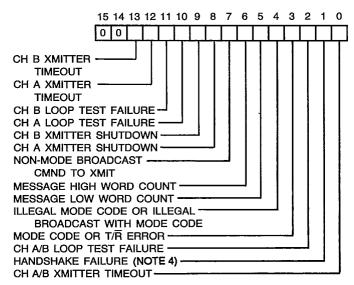

The BUS-61553 contains a 14 bit Built-In-Test (BIT) word register which stores information about the condition of the RTU. When a Mode Command is received to transmit BIT word, the contents of this register are transmitted over the 1553 data bus. Figure 27 shows the meaning of each bit in the BIT register. Information is included regarding transmitter timeouts, loop test failures, transmitter shutdown, subsystem handshake failure, and the results of individual message validations.

#### MODE CODES

The BUS-61553 implements all mode codes applicable to dualredundant systems. Mode codes can also be illegalized using the appropriate I/O signals. Mode command illegalization and handling are detailed in the RTU Operation section and listed in table 6.

# Notes:

- Bits 0-2 and 10-13 are <u>latched</u> and only cleared by a mode reset command or a master RESET.

- 2. Bits 3-7 are cleared at the start of each new message and updated

- at the end of the message. They reflect the present command word. Bits 8-9 are set by the mode command for Transmitter Shutdown and are cleared by the mode command for Override Transmitter Shutdown, Reset RTU or a master RESET.

- Handshake failure indicates that the host processor has failed to release STRBD high within 1.37 μs after READYD has gone high.

FIGURE 27. BUILT-IN-TEST WORD (RTU MODE)

#### **TABLE 6. MODE CODES**

#### **DYNAMIC BUS CONTROL (00000)**

# **MESSAGE SEQUENCE = DBC \* STATUS**

The BUS-61553 responds with status. If the subsystem wants control of the bus, it must set DBACC within the Configuration Register.

#### **ERROR CONDITIONS**

- 1. Invalid Command. No response, command ignored.

- 2. Command Followed by Data Word. No status response. Bits set: message error (SW), High Word Count (BIT Word).

- 3. T/R bit Set to Zero. No status response. Bits set: message error (SW), T/R Error (BIT Word).

- 4. Zero T/R bit and Broadcast Address. No status response. Bits set: message error, broadcast received (SW), Illegal Mode Code, T/R Error (BIT Word).

- 5. Broadcast Address. No status response. Bits set: message error, broadcast received (SW), Illegal Mode Code (BIT Word).

# SYNCHRONIZE WITHOUT DATA WORD (00001)

#### **MESSAGE SEQUENCE = SYNC \* STATUS**

The BUS-61553 responds with status. If sent as a broadcast, the broadcast receive bit will be set and status response suppressed.

# **ERROR CONDITIONS**

- 1. Invalid Command. No response, command ignored.

- 2. Command Followed by Data Word. No status response. Bits set: message error (SW), High Word Count (BIT Word).

- 3. T/R bit Set to Zero. No status response. Bits set: message error (SW), T/R Error (BIT Word).

- 4. Zero T/R bit and Broadcast Address. No status response. Bits set: message error, broadcast received (SW), Illegal Mode Code, T/R Error (BIT Word).

# TRANSMIT STATUS WORD (00010)

# MESSAGE SEQUENCE = TRANSMIT STATUS \* STATUS

The status and BIT word registers are not altered by this command and contain the resulting status from the previous command.

#### **ERROR CONDITIONS**

- 1. Invalid Command. No response, command ignored.

- 2. Command Followed by Data Word. No status response. Bits set: message error (SW), High Word Count (BIT Word).

- 3. T/R bit Set to Zero. No status response. Bits set: message error (SW), T/R Error (BIT Word).

- 4. Zero T/R bit and Broadcast Address. No status response. Bits set: message error, broadcast received (SW), Illegal Mode Code, T/R Error (BIT Word).

- 5. Broadcast Address. No status response. Bits set: message error, broadcast received (SW), Illegal Mode Code, T/R Error (BIT Word).

#### **INITIATE SELF-TEST (00011)**

#### MESSAGE SEQUENCE = SELF-TEST \* STATUS

The BUS-61553 responds with a status word. If the command was broadcast, the broadcast received bit is set and status transmission suppressed. Short-loop test is initiated on the status word transmitted. If the test fails, an RT fail flag is set.

#### **ERROR CONDITIONS**

- 1. Invalid Command. No response, command ignored.

- 2. Command Followed by Data Word. No status response. Bits set: message error (SW), High Word Count (BIT Word).

- 3. T/R bit Set to Zero. No status response. Bits set: message error (SW), T/R Error (BIT Word).

- 4. Zero T/R bit and Broadcast Address. No status response. Bits set: message error, broadcast received (SW), T/R Error (BIT Word).

- 5. Faulty Test. Bits set: terminal flag (SW), A/B Loop Test Fail, Current 1553 Bus (A or B) Loop Test Fail (BIT Word).

#### TRANSMITTER SHUTDOWN (00100)

# MESSAGE SEQUENCE = SHUTDOWN \* STATUS

This command is only used with dual redundant bus systems. The BUS-61553 responds with status. At the end of the status transmission, the BUS-61553 inhibits any further transmission from the dual redundant channel. Once shutdown, the transmitter can only be reactivated by Override Transmitter Shutdown or RESET RT commands.

# **ERROR CONDITIONS**

- 1. Invalid Command. No response, command ignored.

- 2. Command Followed by Data Word. No status response. Bits set: message error (SW), High Word Count (BIT Word).

- 3. T/R bit Set to Zero. No status response. Bits set: message error (SW), T/R Error (BIT Word).

- 4. Zero T/R bit and Broadcast Address. No status response. Bits set: message error, broadcast received (SW), Illegal Mode Code, T/R Error (BIT Word).

# **TABLE 6. MODE CODES (CONTINUED)**

# **OVERRIDE TRANSMITTER SHUTDOWN (00101)**

# MESSAGE SEQUENCE = OVERRIDE SHUTDOWN \* STATUS

This command is only used with dual redundant bus systems. The BUS-61553 responds with status. At the end of the status transmission, the BUS-65515 re-enables the transmitter of the redundant bus. If the command was broadcast, the broadcast received bit is set and status transmission is suppressed.

# **ERROR CONDITIONS**

- 1. Invalid Command. No response, command ignored.

- 2. Command Followed by Data Word. No status response. Bits set: message error (SW), High Word Count (BIT Word).

- 3. T/R bit Set to Zero. No status response. Bits set: message error (SW), T/R Error (BIT Word).

- 4. Zero T/R bit and Broadcast Address. No status response. Bits set: message error, broadcast received (SW), Illegal Mode Code, T/R Error (BIT Word).

# **INHIBIT TERMINAL FLAG BIT (00110)**

#### MESSAGE SEQUENCE = INHIBIT TERMINAL FLAG \* STATUS

The BUS-61553 responds with status and inhibits further internal or external setting of the terminal flag bit in the status register. Once the terminal flag has been inhibited, it can only be reactivated by an Override Inhibit Terminal Flag or Reset RT command. If the command was broadcast, the broadcast received bit is set and status transmission is suppressed.

#### **ERROR CONDITIONS**

- 1. Invalid Command. No response, command ignored.

- 2. Command Followed by Data Word. No status response. Bits set: message error (SW), High Word Count (BIT Word).

- 3. T/R bit Set to Zero. No status response. Bits set: message error (SW), T/R Error (BIT Word).

- 4. Zero T/R bit and Broadcast Address. No status response. Bits set: message error, broadcast received (SW), T/R Error (BIT Word).

# **OVERRIDE INHIBIT TERMINAL FLAG BIT (00111)**

# MESSAGE SEQUENCE = OVERRIDE INHIBIT TERMINAL FLAG \* STATUS

The RTU responds with status and reactivates the terminal flag bit in the status register. If the command was broadcast, the broadcast received bit is set and status transmission is suppressed.

#### **ERROR CONDITIONS**

- 1. Invalid Command. No response, command ignored.

- 2. Command Followed by Data Word. No status response. Bits set: message error (SW), High Word Count (BIT Word).

- 3. T/R bit Set to Zero. No status response. Bits set: message error (SW), T/R Error (BIT Word).

- 4. Zero T/R bit and Broadcast Address. No status response. Bits set: message error, broadcast received (SW), T/R Error (BIT Word).

# **RESET REMOTE TERMINAL (01000)**

### MESSAGE SEQUENCE = RESET REMOTE TERMINAL \* STATUS

The BUS-61553 responds with status and internally resets. Transmitter shutdown, mode commands, BIT Word, and inhibit terminal flag commands will be reset. If the command was broadcast, the broadcast received bit is set and the status word is suppressed.

# **ERROR CONDITIONS**

- 1. Invalid Command. No response, command ignored.

- 2. Command Followed by Data Word. No status response. Bits set: message error (SW), High Word Count (BIT Word).

- 3. T/R bit Set to Zero. No status response. Bits set: message error (SW), T/R Error (BIT Word).

- 4. Zero T/R bit and Broadcast Address. No status response. Bits set: message error, broadcast received (SW), T/R Error (BIT Word).

# RESERVED MODE CODES (01001-01111)

# MESSAGE SEQUENCE = RESERVED MODE CODES \* STATUS

The BUS-61553 responds with status. If the command is illegalized through an optional PROM, the message error bit is set and only the status word is transmitted.

#### **ERROR CONDITIONS**

- 1. Invalid Command. No response, command ignored.

- 2. Command Followed by Data Word. No status response. Bits set: message error (SW), High Word Count (BIT Word).

- 3. T/R bit Set to Zero. No status response. Bits set: message error (SW), Illegal Mode Code (BIT Word).

- 4. Zero T/R bit and Broadcast Address. No status response. Bits set: message error, broadcast received (SW), Illegal Mode Code (BIT Word).

#### TRANSMIT VECTOR WORD (10000)

# MESSAGE SEQUENCE = TRANSMIT VECTOR WORD \* STATUS VECTOR WORD

The BUS-61553 transmits a status word followed by a vector word.

#### **ERROR CONDITIONS**

- 1. Invalid Command. No response, command ignored.

- 2. Command Followed by Data Word. No status response. Bits set: message error (SW), High Word Count (BIT Word).

- 3. T/R bit Set to Zero. No status response. Bits set: message error (SW), T/R Error, Low Word Count (BIT Word).

- 4. Zero T/R bit and Broadcast Address. No status response. Bits set: message error, broadcast received (SW), Illegal Mode Code, T/R Error, Low Word Count (BIT Word).

- 5. Broadcast Address. No status response. Bits set: message error, broadcast received (SW), Illegal Mode Code, (BIT Word).

# SYNCHRONIZE WITH DATA WORD (10001)

# MESSAGE SEQUENCE = SYNCHRONIZE DATA WORD \* STATUS

The data word received following the command word is transferred to the RAM. The status word is then transmitted. If the command was broadcast, the broadcast received bit is set and status transmission is suppressed.

#### **ERROR CONDITIONS**

- 1. Invalid Command. No response, command ignored.

- 2. Command Not Followed by Data Word. No status response. Bits set: message error (SW), Low Word Count (BIT Word).

- 3. Command Followed by too many Data Words. No status response. Bits set: message error (SW), High Word Count (BIT Word).

- 4. Command T/R bit Set to One. No status response. Bits set: message error (SW), T/R Error, High Word Count (BIT Word).

- 5. Command T/R bit Set to Zero and Broadcast Address. No status response. Bits set: message error, broadcast received (SW), High Word Count, T/R Error (BIT Word).

# **TRANSMIT LAST COMMAND (10010)**

# MESSAGE SEQUENCE = TRANSMIT LAST COMMAND \* STATUS LAST COMMAND

The status and BIT word registers are not altered by this command. The SW contains the status from the previous command. The data word transmitted contains the previous valid command (providing it was not another TRANSMIT LAST COMMAND).

# **ERROR CONDITIONS**

- 1. Invalid Command. No response, command ignored.

- 2. Command Followed by Data Word. No status response. Bits set: message error (SW).

- 3. T/R bit Set to Zero. No status response. Bits set: message error (SW), T/R Error, Low Word Count (BIT Word).

- 4. Zero T/R bit and Broadcast Address. No status response. Bits set: message error (SW), Illegal Mode Code, T/R Error (BIT Word).

- 5. Broadcast Address. No status response. Bits set: message error, broadcast received (SW), Illegal Mode Code (BIT Word).

# TRANSMIT BIT WORD (10011)

# MESSAGE SEQUENCE = TRANSMIT BIT WORD \* STATUS BIT WORD

The BUS-61553 responds with status followed by the BIT word. The BIT word is not altered by this command; however, the next SW will reflect errors in this transmission.

#### **ERROR CONDITIONS**

- 1. Invalid Command. No response, command ignored.

- 2. Command Followed by Data Word. No status response. Bit set: message error (SW).

- 3. T/R bit Set to Zero. No status response. Bits set: message error (SW), T/R Error, Low Word Count (BIT Word).

- 4. Zero T/R bit and Broadcast Address. No status response. Bits set: message error (SW), Illegal Mode Code, T/R Error, Low Word Count (BIT Word).

- 5. Broadcast Address. No status response. Bits set: message error, broadcast received (SW), Illegal Mode Code (BIT Word).

# **TABLE 6. MODE CODES (CONTINUED)**

#### **SELECTED TRANSMITTER SHUTDOWN (10100)**

# MESSAGE SEQUENCE = TRANSMITTER SHUTDOWN DATA \* STATUS

The data word received is transferred to the subsystem and status is transmitted. No other action is taken by the BUS-65515. If the command was broadcast, the broadcast received bit is set and status transmission suppressed. Intended for use with RTs with more than one dual redundant channel.

#### **ERROR CONDITIONS**

- 1. Invalid Command. No response, command ignored.

- 2. Command Not Followed by Data Word. No status response. Bits set: message error (SW), High Word Count, Illegal Mode Code (BIT Word).

- 3. Command Followed by too many Data Words. No status response. Bits set: message error (SW), Low Word Count, Illegal Mode Code (BIT Word).

- 4. Command T/R bit Set to One. No status response. Bits set: message error (SW), Illegal Mode Code, High Word Count (BIT Word).

- 5. Command T/R bit Set to One and Broadcast Address. No status response. Bits set: message error, broadcast received (SW), Illegal Mode Code, High Word Count (BIT Word).

### **OVERRIDE SELECTED TRANSMITTER SHUTDOWN (10101)**

# MESSAGE SEQUENCE = TRANSMITTER SHUTDOWN DATA \* STATUS

The data word received after the command word is transferred to the subsystem. No other action is taken by the BUS-65515. If the command was broadcast, the broadcast received bit is set and status transmission suppressed.

#### **ERROR CONDITIONS**

- 1. Invalid Command. No response, command ignored.

- 2. Command Not Followed by Data Word. No status response. Bits set: message error (SW), Low Word Count, Illegal Mode Code (BIT Word).

- 3. Command Followed by too many Data Words. No status response. Bits set: message error (SW), High Word Count, Illegal Mode Code (BIT Word).

- 4. Command T/R bit Set to One. No status response. Bits set: message error (SW), Illegal Mode Code, High Word Count (BIT Word).

- 5. Command T/R bit Set to One and Broadcast Address. No status response. Bits set: message error, broadcast received (SW), Illegal Mode Code, High Word Count, T/R Error (BIT Word).

# RESERVED MODE CODES

# MESSAGE SEQUENCE = RESERVED MODE CODE (T/R = 1) \* STATUSRESERVED MODE CODE (T/R = 0) \* STATUS

The BUS-61553 responds with status. If the command was broadcast, the broadcast received bit is set and status transmission suppressed.

### ERROR CONDITIONS (T/R = 1)

- 1. Invalid Command. No response, command ignored.

- 2. Command Followed by Data Word. No status response. Bits set: message error (SW), High Word Count, Illegal Mode Code (BIT Word).

# ERROR CONDITIONS (T/R = 0)

- 1. Invalid Command. No response, command ignored.

- 2. Command not Followed by Contiguous Data Word. No status response. Bits set: message error (SW), Low Word Count, Illegal Mode Code (BIT Word).

- 3. Command Followed by too many Data Words. No status response. Bits set: message error (SW), High Word Count, Illegal Mode Code (BIT Word).

# Notes:

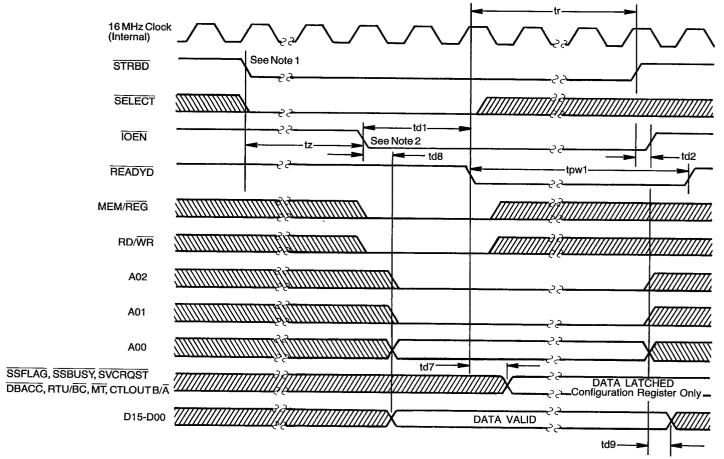

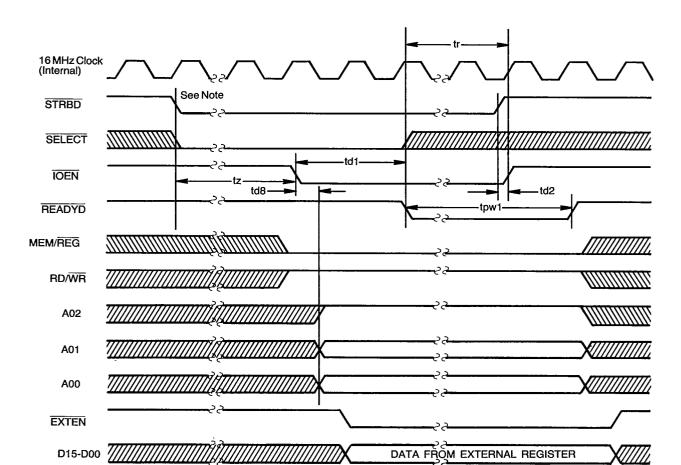

- STRBD to IOEN (low) delay is two clock cycles. If contention occurs, delay is two clock cycles following release of bus (1.8 μs max).

CPU must release STRBD within 1.5 μs of IOEN going active.

- READYD will go away within one clock cycle max.

| CPU WRITES TO INTERNAL REGISTER |                                    |     |      |       |  |  |  |  |

|---------------------------------|------------------------------------|-----|------|-------|--|--|--|--|

| SYMBOL                          | DESCRIPTION                        | MIN | MAX  | UNITS |  |  |  |  |

| td1                             | READYD low delay (CPU Handshake)   | _   | 150  | ns    |  |  |  |  |

| td2                             | IOEN high delay (CPU Handshake)    | _   | 20   | ns    |  |  |  |  |

| tpw1                            | READYD pulse width (CPU Handshake) | 50  |      | ns    |  |  |  |  |

| td7                             | Internal Register delay (write)    | _   | 60   | ns    |  |  |  |  |

| td8                             | Register Data/Address set-up time  | _   | 30   | ns    |  |  |  |  |

| td9                             | Register Data/Address hold time    | _   | 0    | ns    |  |  |  |  |

| tr                              | READYD to STRBD release            | _   | 1.37 | μs    |  |  |  |  |

| tz                              | (SELECT • STRBD) to IOEN           | _   | 1.8  | μs    |  |  |  |  |

FIGURE 28. CPU WRITES TO INTERNAL REGISTER

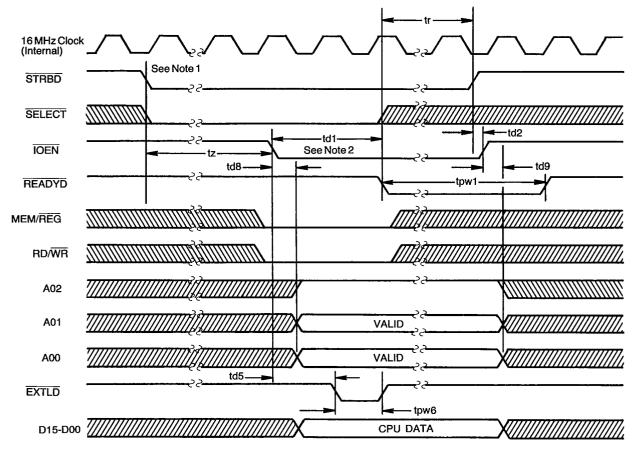

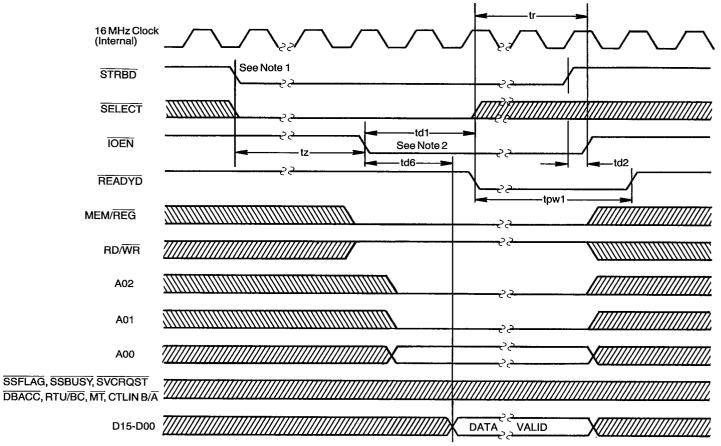

# Notes:

- STRBD to IOEN (low) delay is two clock cycles. If contention occurs, delay is two clock cycles following release of bus (1.8 μs max).

- 2. CPU must release  $\overline{\text{STRBD}}$  within 1.5  $\mu \text{s}$  of  $\overline{\text{IOEN}}$  going active. READYD will go away within one clock cycle max.

| CPU WRITES TO EXTERNAL REGISTER |                                    |     |      |       |  |  |  |  |

|---------------------------------|------------------------------------|-----|------|-------|--|--|--|--|

| SYMBOL                          | DESCRIPTION                        | MIN | MAX  | UNITS |  |  |  |  |

| td1                             | READYD low delay (CPU Handshake)   | _   | 150  | ns    |  |  |  |  |

| td2                             | IOEN high delay (CPU Handshake)    | -   | 20   | ns    |  |  |  |  |

| tpw1                            | READYD pulse width (CPU Handshake) | 50  | -    | ns    |  |  |  |  |

| td5                             | EXTLD low delay                    | 50  | _    | ns    |  |  |  |  |

| td8                             | Register Data/Address set-up time  | _   | 30   | ns    |  |  |  |  |

| td9                             | Register Data/Address hold time    | _   | 0    | ns    |  |  |  |  |

| tpw6                            | EXTLD low pulse width              | 56  | _    | ns    |  |  |  |  |

| tr                              | READYD to STRBD release            | _   | 1.37 | μs    |  |  |  |  |

| tz                              | (SELECT • STRBD) to IOEN           | _   | 1.8  | μs    |  |  |  |  |

FIGURE 29. CPU WRITES TO EXTERNAL REGISTER

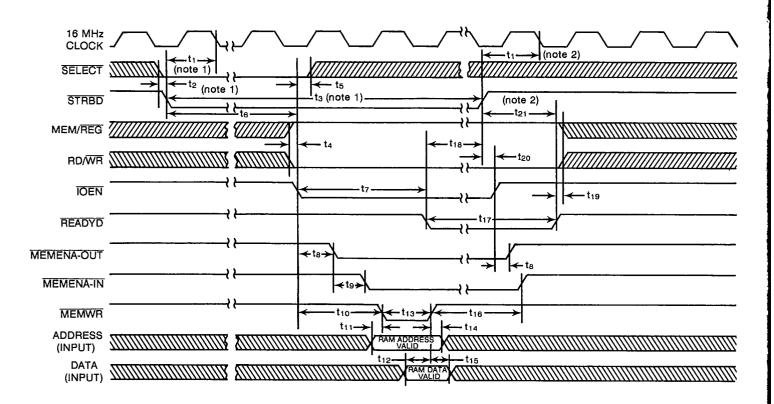

t10

| CPU READS FROM RAM TIMING (SHOWN FOR INTERNAL RAM) |                                                       |                   |                |                     |       |  |  |  |

|----------------------------------------------------|-------------------------------------------------------|-------------------|----------------|---------------------|-------|--|--|--|

| SYMBOL                                             | DESCRIPTION                                           | MIN               | TYP            | MAX                 | UNITS |  |  |  |

| t <sub>1</sub>                                     | SELECT * STRBD setup time to falling edge of clock 30 |                   |                |                     |       |  |  |  |

| t <sub>2</sub>                                     | SELECT setup time to STRBD                            | (                 | Note           | 1)                  | ns    |  |  |  |

| t <sub>3</sub>                                     | STRBD width                                           | (t <sub>6</sub> + | ⊦ <b>t</b> 7 + | - t <sub>15</sub> ) | ns    |  |  |  |

| t4                                                 | MEM/REG, RD/WR setup time to IOEN                     | 0                 | -              | -                   | ns    |  |  |  |

| t <sub>5</sub>                                     | SELECT hold time following IOEN                       | 0                 | -              | -                   | ns    |  |  |  |

| t <sub>6</sub>                                     | SELECT ∗ STRBD to IOEN delay (without contention)     | 75                | -              | 160                 | ns    |  |  |  |

| t <sub>6</sub> .                                   | SELECT * STRBD to IOEN delay (with contention)        | -                 | -              | 1.80                | με    |  |  |  |

| t <sub>7</sub>                                     | TOEN to READYD delay                                  | 115               | 125            | 150                 | ns    |  |  |  |

| t <sub>8</sub>                                     | IOEN to MEMENA-OUT delay                              | -                 | -              | 40                  | ns    |  |  |  |

| t <sub>9</sub>                                     | IOEN low to MEMOE delay                               | 55                | 62.5           | 70                  | ns    |  |  |  |

| t <sub>10</sub>                                    | MEMENA-IN to data low-Z                               | 5                 | -              | -                   | ns    |  |  |  |

| t <sub>11</sub>                                    | MEMOE to data low-Z                                   | 0                 | -              | -                   | ns    |  |  |  |

| t <sub>12</sub>                                    | MEMENA-IN to output data valid                        | -                 | -              | 55                  | ns    |  |  |  |

| t <sub>13</sub>                                    | MEMOE low to output data valid                        | -                 | -              | 30                  | ns    |  |  |  |

| t <sub>14</sub>                                    | Address access time to output data valid              | -                 | -              | 55                  | ns    |  |  |  |

| t <sub>15</sub>                                    | READYD to STRBD release time                          | -                 | -              | 1.37                | μs    |  |  |  |

| t <sub>16</sub>                                    | READYD pulse width                                    | 50                | -              | -                   | ns    |  |  |  |

| t <sub>17</sub>                                    | MEM/REG, RD/WR hold time following READYD high        | 0                 | -              | -                   | ns    |  |  |  |

| t <sub>18</sub>                                    | STRBD high delay to IOEN high                         | -                 | -              | 20                  | ns    |  |  |  |

| t <sub>19</sub>                                    | STRBD high delay to READYD high (Note 2)              | -                 | -              | 105                 | ns    |  |  |  |

| t <sub>20</sub>                                    | STRBD high delay to MEMOE high (Note 2)               | 115               | -              | 170                 | ns    |  |  |  |

| t <sub>21</sub>                                    | Data hold time after address invalid                  | 5                 | -              | -                   | ns    |  |  |  |

| t <sub>22</sub>                                    | MEMENA-IN high to data tri-state                      | -                 | -              | 25                  | ns    |  |  |  |

| t <sub>23</sub>                                    | MEMOE high to data tri-state                          | _                 | <b>-</b> _     | 25                  | ns    |  |  |  |

# NOTES:

- 1. SELECT and STRBD may be tied together. SELECT\*STRBD must be sampled low for two consecutive falling edges of the 16 MHz clock when the BUS-61553's protocol/memory management logic is not using the data bus. When this occurs IOEN goes low, starting the transfer cycle. At this time, SELECT may be released high.

- 2. READYD goes high after the first falling edge of clock input (satisfying t<sub>1</sub>) following STRBD going high. MEMOE goes high after STRBD is sampled high for a second falling clock edge.

- 3. Data tri-state occurs after t<sub>22</sub> or t<sub>23</sub>, whichever occurs first.

FIGURE 30.

CPU READS FROM RAM TIMING

(Shown for Internal RAM)

|                 | CPU WRITES TO RAM TIMING (SHOWN FOR INTERNAL RAM)  |                   |        |                   |       |  |  |  |  |

|-----------------|----------------------------------------------------|-------------------|--------|-------------------|-------|--|--|--|--|

| SYMBOL          | DESCRIPTION                                        | MIN               | TYP    | MAX               | UNITS |  |  |  |  |

| t <sub>1</sub>  | SELECT · STRBD setup time to falling edge of clock | 30                | -      | -                 | ns    |  |  |  |  |

| t <sub>2</sub>  | SELECT setup time to STRBD                         | (1                | Note : | 1)                | ns    |  |  |  |  |

| t <sub>3</sub>  | STRBD width                                        | (t <sub>6</sub> + | t7 +   | t <sub>18</sub> ) | ns    |  |  |  |  |

| t <sub>4</sub>  | MEM/REG, RD/WR setup time to IOEN                  | 0                 |        | -                 | ns    |  |  |  |  |

| t <sub>5</sub>  | SELECT hold time following IOEN (Note 1)           | 0                 | -      | -                 | ns    |  |  |  |  |

| t <sub>6</sub>  | SELECT - STRBD to IOEN delay (without contention)  | 75                | -      | 160               | ns    |  |  |  |  |

| t <sub>6</sub>  | SELECT - STRBD to IOEN delay (with contention)     | -                 | -      | 1.80              | μs    |  |  |  |  |

| t7              | IOEN to READYD delay                               | 115               | 125    | 150               | ns    |  |  |  |  |

| tg              | IOEN to MEMENA-OUT delay                           | -                 | -      | 40                | ns    |  |  |  |  |

| t <sub>9</sub>  | MEMENA-OUT to MEMENA-IN delay                      | -                 | -      | 50                | ns    |  |  |  |  |

| t <sub>10</sub> | IOEN to MEMWR delay                                | 55                | 62.5   | 70                | ns    |  |  |  |  |

| t <sub>11</sub> | Address setup time to start of MEMWR               | 0                 | -      | -                 | ns    |  |  |  |  |

| t <sub>12</sub> | Data setup time to end of MEMWR                    | 25                | -      | -                 | ns    |  |  |  |  |

| t <sub>13</sub> | MEMWR pulse width                                  | 50                | 62.5   | 70                | ns    |  |  |  |  |

| t <sub>14</sub> | Address hold time following MEMWR high             | 0                 | -      | -                 | ns    |  |  |  |  |

| t <sub>15</sub> | Data hold time following MEMWR high                | 3                 | -      | -                 | ns    |  |  |  |  |

| t <sub>16</sub> | MEMENA-IN hold time following MEMWR high           | 0                 | -      | -                 | ns    |  |  |  |  |

| t <sub>17</sub> | READYD pulse width                                 | 50                | -      | -                 | ns    |  |  |  |  |

| t18             | READYD to STRBD release time                       | -                 | -      | 1.37              | μs    |  |  |  |  |

| t <sub>19</sub> | MEM/REG, RD/WR hold time following READYD high     | 0                 | -      | -                 | ns    |  |  |  |  |

| t <sub>20</sub> | STRBD high delay to IOEN high                      | -                 | -      | 20                | ns    |  |  |  |  |

| t <sub>21</sub> | STRBD high delay to READYD high (Note 2)           |                   |        | 105               | ns    |  |  |  |  |

# NOTES:

- SELECT and STRBD may be tied together.

SELECT-STRBD must be sampled low for two consecutive falling edges of the 16 MHz clock when the BUS-61553's protocol/memory management logic is not using the data bus. When this occurs IOEN goes low, starting the transfer cycle. At this time, SELECT may be released high.

- 2. READYD goes high after the first falling clock edge (satisfying t<sub>1</sub>) after STRBD goes high.

FIGURE 31. **CPU WRITES TO RAM TIMING** (Shown for Internal RAM)

# Note:

STRBD to IOEN (low) delay is two clock cycles. If contention occurs, delay is two clock cycles following release of bus.

| CPU READS FROM EXTERNAL REGISTER |                                    |     |      |       |  |  |  |  |

|----------------------------------|------------------------------------|-----|------|-------|--|--|--|--|

| SYMBOL                           | DESCRIPTION                        | MIN | MAX  | UNITS |  |  |  |  |

| td1                              | READYD low delay (CPU Handshake)   | _   | 150  | ns    |  |  |  |  |