SD14 SD15 GND \*SPKROUT \*INTR

TINTH TRIO IOCHRDY TMEMCS16 TOCS16 TZWS

IRO9 IRO7 IRO5 IRO4 IRO3 VCC IRO10 IRO11 IRO12

IRO12 IRO14 IRO15 GND B\_CD2 B\_D10 B\_WP GND B\_D2 B\_D9

B\_01 B\_08 B\_00

B\_CA7 B\_CA24 B\_CA12 B\_CA23 VCC B\_CA15 B\_CA22

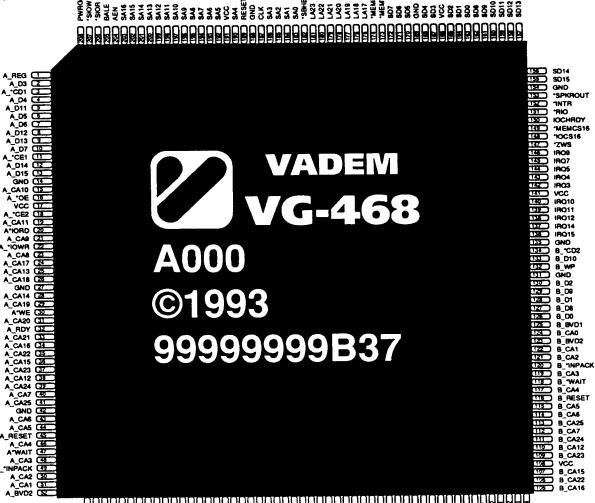

#### Pin Diagram

This section provides the pin assignment, signal description, block diagram, and pin descriptions for the VG-468 PC Card Socket Controller.

Pin Diagram Figure 1-1

DEFAULT PIN ASSIGNMENT

A DB A DB VCC VCCEN A DB VCCEN A VPPTENI A VPPTENI A VPPTENI B GPPTENI B GPTENI B GPTENI

#### ALTERNATIVE PIN DEFINITIONS

| PIN#   | DEFAULT | ALTERNATIVE(S) |   |

|--------|---------|----------------|---|

| 32,103 | ADY/BSY | *IREO          | _ |

| 52,123 | BVD2    | *SPKR          | _ |

| 54,125 | BVD1    | *STSCHG, *RI   | _ |

| 61,132 | WP      | *IOIS16        |   |

| 67.68  | GPIO    | *VPPVALIO      |   |

M151017-00

## **PRELIMINARY**

#### **Signal Description**

| Pin#                                                                                                                                   | Signal Names       | Туре | Characteristics                            | # Pins |

|----------------------------------------------------------------------------------------------------------------------------------------|--------------------|------|--------------------------------------------|--------|

| 204                                                                                                                                    | AEN                | I    | TTL Compatible                             | 1      |

| 205                                                                                                                                    | BALE               | I    | TTL Compatible                             | 1      |

| 54, 125                                                                                                                                | BVD1 (*STSCHG/*RI) | I    | CMOS Schmitt Trigger                       | 2      |

| 52, 123                                                                                                                                | BVD2 (*SPKR)       | I    | CMOS Schmitt Trigger                       | 2      |

| 15,19,21,<br>23-26,28,29<br>31,33-41,43<br>44,46,48,50<br>51,53,86,90<br>92,94-99,<br>102,104-107<br>109-115,117<br>119,121,122<br>124 | CA[25:0]           | 0    | 4mA Tri-State                              | 52     |

| 63,3,134,74                                                                                                                            | *CD[2:1]           | I    | CMOS Schmitt Trigger                       | 4      |

| 89,83,18,11                                                                                                                            | *CE[2:1]           | 0    | 4mA Tri-State                              | 4      |

| 187                                                                                                                                    | CLK                | I    | TTL Compatible                             | 1      |

| 2,4-10,12,13<br>55-58,60,62<br>73,76-82,84<br>85,126-130<br>133                                                                        | D[15:0]            | ľO   | I = TTL Compatible O = 4mA Output          | 32     |

| 14,27,42,75<br>101,131,135<br>154,169,188                                                                                              | GND                |      |                                            | 10     |

| 67,68                                                                                                                                  | GPIO               | I/O  | I = CMOS Schmitt Trigger O = 4mA Tri-State | 2      |

| 49,120                                                                                                                                 | *INPACK            | I    | TTL Compatible                             | 2      |

| 152                                                                                                                                    | *INTR              | I/O  | I = TTL Compatible O = 4mA Tri-State       | 1      |

| 150                                                                                                                                    | IOCHRDY            | 0    | 16 mA Tri-State                            | 1      |

| 148                                                                                                                                    | *IOCS16            | 0    | 16 mA 5V Open Drain                        | 1      |

| 20,91                                                                                                                                  | *IORD              | 0    | 4mA Tri-State                              | 2      |

| 22,93                                                                                                                                  | *IOWR              | 0    | 4mA Tri-State                              | 2      |

| 136-140<br>146-142                                                                                                                     | IRQs               | 0    | 4mA Tri-State                              | 10     |

## **PRELIMINARY**

# Signal Description (cont.)

| Pin#                                   | Signal Names     | Type | Characteristics                      | # Pins |

|----------------------------------------|------------------|------|--------------------------------------|--------|

| 181-175                                | LA[23:17]        | I    | TTL Compatible                       | 7      |

| 149                                    | *MEMCS16         | 0    | 16 mA 5V Open Drain                  | 1      |

| 174                                    | *MEMR            | I    | TTL Compatible                       | 1      |

| 173                                    | *MEMW            | I    | TTL Compatible                       | 1      |

| 16,87                                  | *OE              | 0    | 4mA Tri-State                        | 2      |

| 208                                    | PWRGOOD          | I    | Schmitt Trigger                      | 1      |

| 32,103                                 | RDY/*BSY (*IREQ) | I    | CMOS Schmitt Trigger                 | 2      |

| 1,72                                   | *REG             | 0    | 4mA Tri-State                        | 2      |

| 45,116                                 | RESET            | 0    | 4mA Tri-State                        | 2      |

| 189                                    | RESETDRV         | I    | Schmitt Trigger with pull-down       | 1      |

| 151                                    | *RIO/LED         | I/O  | I = TTL Compatible O = 4mA Tri-State | 1      |

| 203-192,190<br>186-183                 | SA[16:0]         | I    | TTL Compatible                       | 17     |

| 182                                    | *SBHE            | I    | TTL Compatible                       | 1      |

| 206                                    | *SIOR            | I    | TTL Compatible                       | 1      |

| 207                                    | *SIOW            | I    | TTL Compatible                       | 1      |

| 155-162,<br>172-170,168<br>167,165-163 |                  | I/O  | I = TTL Compatible O = 8mA Tri-State | 16     |

| 153                                    | *SPKROUT         | I/O  | I = TTL Compatible O = 4mA Tri-State | 1      |

| 17,59,88,<br>108,141,166<br>191        | VCC              |      |                                      | 7      |

| 66,69                                  | *VCCEN           | 0    | 4mA Output                           | 2      |

| 65,70                                  | VPP1EN1          | 0    | 4mA Output                           | 2      |

| 64,71                                  | VPP2EN1          | 0    | 4mA Output                           | 2      |

| 47,118                                 | *WAIT            | I    | TTL Compatible                       | 2      |

| 30,100                                 | *WE/*PRGM        | 0    | 4mA Tri-State                        | 2      |

| 61,132                                 | WP (*IOIS16)     | I    | TTL Compatible                       | 2      |

| 147                                    | *ZWS             | 0    | 16mA 5V Open Drain                   | 1      |

M151017-00 5

#### **Pin Descriptions**

| Symbol                | Type | Pin No.                                                                                                                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------------|------|---------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AEN                   | I    | 204                                                                                                                             | System Address Enable. High during DMA cycles, low otherwise.                                                                                                                                                                                                                                                                                                                                                                                                                |

| BALE                  | I    | 205                                                                                                                             | Bus Address Latch Enable. An active high input used to latch LA[23:17] at the beginning of a bus cycle.                                                                                                                                                                                                                                                                                                                                                                      |

| BVD1<br>(*STSCHG/*RI) | I    | 54,125                                                                                                                          | If BVD1 is negated by a memory PC Card with a battery, it indicates that the battery is no longer serviceable and data is lost.                                                                                                                                                                                                                                                                                                                                              |

|                       |      |                                                                                                                                 | For I/O PC Cards, this signal is held high when either or both the Signal on Change bit and Changed bit in the Card Status Register on the PC Card are set to zero. When both the bits are one, the signal is held low. The Changed bit is the logical OR of the bits CVBAT1, CVBAT2, CWP and CBSYRDY in the Pin Replacement Register on the PC Card. Or this pin is connected to Ring Indicate, which is qualified by Ring Indicate Enable to be passed on to the *RIO pin. |

| BVD2<br>(*SPKR)       | I    | 54,123                                                                                                                          | BVD1 and BVD2 are generated by memory PC Cards with onboard batteries. These signals indicate the health of the battery Both are asserted high when the battery is ir good condition. When BVD2 is negated while BVD1 is still asserted, the battery should be replaced, although data integrity or the memory PC Card is still assured.                                                                                                                                     |

|                       |      |                                                                                                                                 | When the I/O interface is selected, BVD2 may be used to provide a single amplitude Digital Audio waveform intended to be passed through to the system's speake without signal conditioning.                                                                                                                                                                                                                                                                                  |

| CA[25:12]             | Ο    | 15,19,21<br>23-26,28<br>28,31<br>33-41,43<br>44,46,48<br>50,51,53<br>86,90,92<br>94-99,102<br>104-107<br>109-115,1<br>119,121,1 | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

## Pin Descriptions (continued)

| Symbol   | Type | Pin No.                                                                  | Description                                                                                                                                                                                                                                                                                                                            |

|----------|------|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *CD[2:1] | I    | 63,3<br>134,74                                                           | Detects proper card insertion. The signals are connected to ground internally on the PC Card and will be forced low whenever a card is placed in a host socket. Status is available to software through the Interface Status Register.                                                                                                 |

| *CE[2:1] | O    | 89,83<br>18,11                                                           | Active low card enable signals. *CE1 is used to enable even bytes, *CE2 for odd bytes. A multiplexing scheme based on A0, *CE1, *CE2 allows 8-bit hosts to access all data on Card Data[7:0] if desired.                                                                                                                               |

| CLK      | I    | 187                                                                      | System clock.                                                                                                                                                                                                                                                                                                                          |

| D[15:0]  | I/O  | 2,4-10<br>12,13<br>55-58<br>60,62,73<br>76-82<br>84,85<br>126-130<br>133 | Card data.                                                                                                                                                                                                                                                                                                                             |

| GPIO     | I/O  | 67,68                                                                    | General purpose input/output. May be used for one of several purposes.  - An active low input indicates that Vpp power line has reached the user specified range.  - An input indication a card eject or card insertion pending.  - An input source for generating a card status change interrupt.  - Programmable chip select output. |

| *INPACK  | I    | 49,120                                                                   | Input Acknowledge. Asserted by some PC Cards during I/O read cycles. This signal is used by the VG-468 to control the enable of its input data buffer between the card and CPU.                                                                                                                                                        |

M151017-00

# VADEM VG-468 PC CARD SOCKET

## **PRELIMINARY**

## Pin Descriptions (continued)

CONTROLLER

| Symbol    | Туре | Pin No.            | Description                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------|------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *INTR     | I/O  | 152                | Interrupt Request output: Active low output requesting a nonmaskable interrupt to the CPU. Also, a resistor strapping input during RESETDRV to determine the mapping of socket A and socket B to one of four groups.                                                                                                                                                                              |

| IOCHRDY   | O    | 150                | I/O Channel Ready. This active high signal indicates that the current I/O bus cycle has completed. When a PC Card needs to extend a Read or Write cycle, the VG-468 pulls IOCHRDY low. IOCHRDY can be deasserted by either *WAIT, or by programming to add wait states for 16-bit memory and I/O cycles. If *WAIT is used in 16-bit mode, the wait state generator has to be set to 1 wait state. |

| *IOCS16   | 0    | 148                | This active low I/O 16-bit chip select signal indicates to the host system the current I/O cycle is a 16-bit access. A 16-bit to 8-bit conversion is done if it is inactive.                                                                                                                                                                                                                      |

| *IORD     | 0    | 20,91              | I/O Read signal is driven active to read data from the PC Card's I/O space. The *REG signal and at least one of the Card Enable signals must also be active for the I/O transfer to take place.                                                                                                                                                                                                   |

| *IOWR     | 0    | 22,93              | I/O Write signal is driven active to write data to the PC Card's I/O space. The *REG signal and at least one of the Card Enable signals must also be active for the I/O transfer to take place.                                                                                                                                                                                                   |

| IRQs      | 0    | 136-140<br>146-142 | IRQ[15, 14, 12:9, 7, 5:3].                                                                                                                                                                                                                                                                                                                                                                        |

| LA[23:17] | I    | 181-175            | Local Address bus used to address memory devices on the ISA-bus. Together with the system address signals, they address up to 16MB on the ISA bus.                                                                                                                                                                                                                                                |

| *MEMCS16  | 0    | 149                | This active low 16-bit memory chip select signal indicates to the host system that the current memory cycle is a 16-bit access. A 16-bit to 8-bit conversion is done if it is inactive.                                                                                                                                                                                                           |

## **PRELIMINARY**

## Pin Descriptions (continued)

| Symbol              | Type | Pin No. | Description                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------|------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *MEMR               | I    | 174     | Active low signal indicates a memory read cycle.                                                                                                                                                                                                                                                                                                                                           |

| *MEMW               | Ι    | 173     | Active low signal indicates a memory write cycle.                                                                                                                                                                                                                                                                                                                                          |

| *OE                 | 0    | 16,87   | Active low signal used to gate memory reads from memory cards.                                                                                                                                                                                                                                                                                                                             |

| PWRGOOD             | I    | 208     | Power Good is an active high signal which indicates that power to the system is stable. Connect to ground if not used. Combined with RESETDRV, it will indicate to VG-365 whether a cold reset, or a resume reset has occurred, to decide whether to reset the slot configuration registers. System implementations without a "POWERGOOD" as resume indication should tie this signal low. |

| RDY/*BSY<br>(*IREQ) | I    | 32,103  | Memory PC Cards drive Ready / *Busy low to indicate that the memory card circuits are busy processing a previous write command. It is set high when they are ready to accept a new data transfer command.                                                                                                                                                                                  |

|                     |      |         | For I/O PC Cards, this pin is used as an interrupt request and driven low to indicate to the host that a device on the I/O PC Card requires service by the host software. The signal is held at the inactive level when no interrupt is requested.                                                                                                                                         |

| *REG                | Ο    | 1,72    | Select attribute memory. This signal is set inactive (high) for all accesses to common memory of a PC Card. When it is active, access is limited to Attribute Memory when *WE or *OE are active, and to I/O ports when *IORD or *IOWR are active. I/O PC Cards will not respond to *IORD or *IOWR when the *REG signal is inactive. During DMA operations the *REG signal is inactive.     |

## **PRELIMINARY**

## Pin Descriptions (continued)

| Symbol   | Туре | Pin No.                                    | Description                                                                                                                                                                                                                                                                                                                                                                 |

|----------|------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET    | 0    | 45,116                                     | Provides a hard reset to a PC Card and clear<br>the Card Configuration Option Register, thu<br>placing card in an unconfigured (memor<br>interface) state.                                                                                                                                                                                                                  |

| RESETDRV | I    | 189                                        | Active high indicates a main system reset.                                                                                                                                                                                                                                                                                                                                  |

| *RIO/LED | I/O  | 151                                        | Ring Indicate Output. Pass through of Rin Indicate output from I/O PC Card. VG-46 can also be configured to activate *RIO card detect changes. *RIO will be function in *CS controlled power down. When disdrive LED enable is set this signal becomes driver for disk drive LED. Also, a resist strapping input during RESETDRV determine the functions of pin B_CA[11:4]. |

| SA[16:0] | I    | 203-192<br>190<br>186-183                  | System Address bus used to address memorand I/O devices on the ISA bus. The signals are latched and are valid throughouthe bus cycle.                                                                                                                                                                                                                                       |

| *SBHE    | I    | 182                                        | System Byte High Enable. When asserte this active low signal indicates that a datransfer is occurring on the upper byte of t system data bus.                                                                                                                                                                                                                               |

| SD[7:0]  | I/O  | 155-162,<br>172-170,<br>168,167<br>165-163 | System Data Bus.                                                                                                                                                                                                                                                                                                                                                            |

| *SIOR    | I    | 206                                        | This active low I/O read signal instructs t VG-468 to drive data onto the data bus.                                                                                                                                                                                                                                                                                         |

| *SIOW    | I    | 207                                        | This active low I/O write signal instructs t VG-468 to latch the data on the data bus.                                                                                                                                                                                                                                                                                      |

| *SPKROUT | I/O  | 153                                        | Digital audio signal which provides a sing amplitude (digital) audio waveform to dri the system's speaker. Passes through *SPK from an I/O PC Card. This signal must held high when no audio signal is prese Also, a resistor strapping input duri RESETDRV to determine the mapping socket A and socket B to one of four group                                             |

## PRELIMINARY

## Pin Descriptions (continued)

| Symbol          | Type | Pin No. | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------|------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *VCCEN          | O    | 66,69   | Power Control signal for card Vcc.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| VPP1EN1         | 0    | 65,70   | Power Control signal for card Vpp1.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| VPP2EN1         | 0    | 64,71   | Power Control signal for card Vpp2.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| *WAIT           | I    | 47,118  | This signal is driven by the PC Card to delay completion of the memory or I/O cycle in progress.                                                                                                                                                                                                                                                                                                                                                                                                 |

| *WE/*PRGM       | 0    | 30,100  | The host uses *WE for gating memory write data, and for memory PC Cards that employ programmable memory.                                                                                                                                                                                                                                                                                                                                                                                         |

| WP<br>(*IOIS16) | I    | 61,132  | Reflects the status of the Write Protect switch on some memory PC Cards. If the memory PC Card has no write protect switch, the card will connect this line to ground (the card can always be written) or to Vcc (permanently write protected).                                                                                                                                                                                                                                                  |

|                 |      |         | When the I/O interface is selected, this pin is used for the "I/O is 16-bit Port" function: asserted by the PC Card when the address on the bus corresponds to an address to which the PC Card responds, and the I/O Port which is addressed is capable of 16-bit access. If this signal is not asserted during a 16-bit I/O access, the system will generate 8-bit references to the even and odd byte of the 16-bit port being accessed. If 8-bit window size is selected, *IOIS16 is ignored. |

| *ZWS            | 0    | 147     | Zero Wait State. An active low output indicates that the PC Card wishes to terminate the present bus cycle without inserting additional wait states. This cycle will not be driven during a 16-bit I/O access.                                                                                                                                                                                                                                                                                   |