# L64118 MPEG-2 Transport Controller with Embedded MIPS CPU (TR4101)

**Preliminary Datasheet**

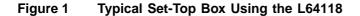

LSI Logic's L64118 MPEG-2 Transport Controller with Embedded MIPS CPU (TR4101) is a highly integrated set-top box control and communication device, combining most of the logic needed for a digital broadcast system (DBS) or cable set-top box onto a single chip. The L64118's embedded 32-bit TinyRISC<sup>™</sup> MIPS CPU core provides processing power to support transport and system data, as well as general-purpose system control.

The L64118 interfaces directly to LSI Logic's L64704 and L64724 (satellite), and the L64768 (cable) single-chip channel decoders, as well as to the L64105 MPEG-2 A/V decoder.

The MPEG-2 transport and system demultiplexer can handle 32 Packet Identifications (PIDs) simultaneously, including audio, video, and generalpurpose data services. It integrates a Digital Video Broadcasting (DVB)compliant descrambler block, substantially increasing the security of the set-top box.

The L64118's synchronous External System Bus (EBus) communicates with external peripherals. The L64118 communicates with peripherals through serial, parallel, SmartCard, and infrared ports. Several general-purpose I/O pins are provided that let system designers expand the system's capabilities.

The L64118 supports industry-standard SDRAM memory of up to 16 Mbytes, using 16 and 64 Mbit SDRAMs. The SDRAM interface supports PC66/100-compliant SDRAMS.

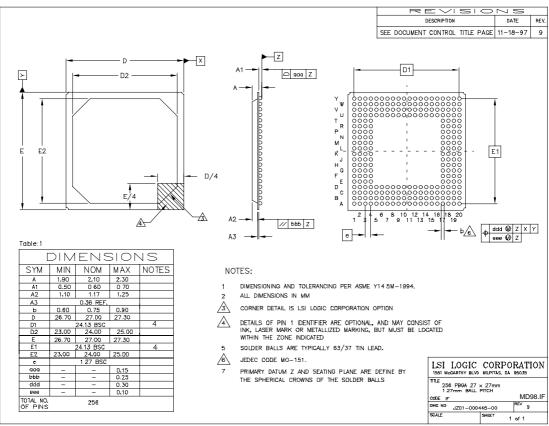

The L64118 is offered in LSI Logic's 3.3 V G10<sup>®</sup>-p cell-based technology and is packaged in a 256-pin PBGA (IF) package.

The L64118's embedded 32-bit MIPS CPU (TR4101) runs at 54 MHz. The chip's CPU block is 32 bit, while the bus interface to external memory (through the SDRAM controller) is 16 bit. The CPU can run MIPS16 and MIPS32 instructions. The 32-bit operations allow high-performance operation, while 16-bit operations allow for code optimization and memory savings. Since most transport processing and filtering is implemented in hardware, much of the CPU's processing power can be devoted to system processing. The L64118 processes the transport data packets in the PID Processing Unit (PPU) according to the MPEG-2 standard draft 13818-1, making Packetized Elementary Stream (PES), Program Specific Information (PSI), Service Information (SI), and Private data available to the system. It also buffers and transfers audio and video PES data packets to the external decoder device.

The L64118 interfaces directly to LSI Logic's L64105 MPEG-2 A/V decoder. It outputs demultiplexed audio and video PES streams for processing by the L64105. This decoder's extended channel buffer feature lets you use part of the L64118 SDRAM space to store A/V PES data directed to the L64105. One benefit of this is that it lets you free memory in the L64105 and increases its On-Screen Display (OSD) capability.

The L64118 also interfaces directly to LSI Logic's family of single-chip channel decoders (L64704, L64724, and L64768), which allows channel data to be transferred in parallel or serial modes. The L64118 implements an automatic sync locking mechanism with a programmable hysteresis function for reliable locking onto MPEG-2 (0x47) transport packet sync bytes.

The External System Bus (EBus) is a general-purpose, 32-bit wide system bus. It is controlled by the L64118 for communication with external components in the system. This bus provides the system designer with an interface that permits the glueless connection of devices such as FLASH, ROMs, and external peripherals.

The L64118's peripheral interface blocks let you connect external systems directly to the set-top box. The RS232 ports let you connect a PC, modem, or terminal directly to the chip. The IEEE1284 parallel port lets you connect to fast peripheral devices and transfer filtered transport packets. The IEEE1284 parallel port includes an on-chip DMA controller for expediting data transfers between memory to, and from, the port.

The L64118 includes an infrared transmitter (blaster) port for applications such as (remotely) programming a VCR, as well as two independent infrared receiver ports, which can be used to program the set-top box using a remote controller.

The 27 MHz system clock drives the L64118 internal demultiplexer block, as well as most of the peripheral modules. The PLL block generates 54 MHz from the 27 MHz system clock to drive the CPU logic.

The L64118 includes four DMA channels (one dedicated to the IEEE1284 port, three independent) that can be used to transfer data between peripheral ports and memory, from one memory location to another, or from memory to an external system device.

# Features

The L64118 provides additional system features for a set-top box application, including:

# Channel

- Compliance with ISO/IEC 13818-1 (MPEG-2) Transport specifications

- Sustained rates up to 90 Mbits/s serial and up to 13.0 Mbytes/s parallel transport stream input interface

- Direct interface to LSI Logic single-chip channel decoder devices, such as the L64704, the L64768, and the L64724

# Demux

- PID filtering (32 user-programmable PIDs)

- Hardware-assisted section filtering for 30 general-purpose PIDs (PSI, SI, and Private)

- Each filter includes 12 match bytes and 12 mask bytes

- Each PID can select up to 32 filters simultaneously

- Support of a Program Clock Reference (PCR) PID

- CRC32 in parallel to all sections in the filtering process

- Descrambler core compliant to DVB common scrambling specifications

- Support for transport-level and PES-level descrambling

- Seamless support of scrambled and unscrambled data

- Support of up to 12 pairs of 64-bit keys

- Two 256-byte transport buffers for supporting audio and video PES streams

- 32 programmable cyclic buffers in SDRAM memory assignable to a PID or section filter index

- Support for an additional programmable cyclic buffer in SDRAM to post data to adaptation fields

- Program Clock Reference (PCR) recovery and locking

- Automatic detecting and switching of audio and video PIDs on splice points

- Audio oversampling (256 or 384 times oversampling) clock generation

# **CPU and Subsystems**

- Integration of the CPU system:

- 32-bit TR4101 54 MHz TinyRISC CPU

- MIPS16 and MIPS-II instruction set compatible

- Four Kbyte Data (direct mapped) and Eight Kbyte (two-way set associative) instruction cache

- Basic Bus and Cache Controller unit (BBCC)

- Multiply/Divide Unit (MDU)

- Debugger Building Module (DBX)

- 32-bit Timers and Interrupt Controller

- In-Circuit Emulator (ICE) port

- Two interrupt handling modes:

- Interrupt Compatibility mode supports 12 interrupt ports and six main interrupt levels. This mode is compatible with the L64108 interrupt structure.

- Interrupt Extension mode supports 25 interrupt ports with a software index to each interrupt source. This new mode can reduce interrupt latency.

# Peripherals

- Programmable audio clock generator for oversampling audio DAC (ACLK)

- Three RS232 serial I/O channels

- IEEE1284 parallel interface port (shared with the Aux port)

- Two ISO7816 SmartCard interfaces

- Two Infrared (IR) receivers

- One IR transmitter

- Auxiliary (Aux) fast input/output port with multiple configurations and settings (shared with the IEEE1284 port)

- Teletext serial interface port with direct interface to NTSC or PAL encoders

- I<sup>2</sup>C-compatible interface port supporting multimaster or slave modes for interfacing to external devices

- Four DMA channels (one dedicated to IEEE1284 port, three independent)

- Synchronous extension bus

- 32-bit external addressing

- 8-/16-/32-bit data bus width

- Multiplexed address/data as well as eight demultiplexed address pins

- Synchronous to a 27 MHz output clock

- Up to 47 general-purpose pins

- Six programmable chip-select output signals (five dedicated and one multiplexed)

- Enhanced serial I/O for modem use

# **SDRAM Controller**

- SDRAM Controller supports 16 and 64 Mbit SDRAM devices

- SDRAM Controller support for up to 16 Mbytes

# General

- On-chip PLL (54 MHz) with internal loop filter

- JTAG support

- 256-pin Plastic Ball Grid Array (PBGA) Package

- Commercial temperature range 0 °C-70 °C ambient

- Low-power, 3.3 V (± 10%) process

# **Architectural Overview**

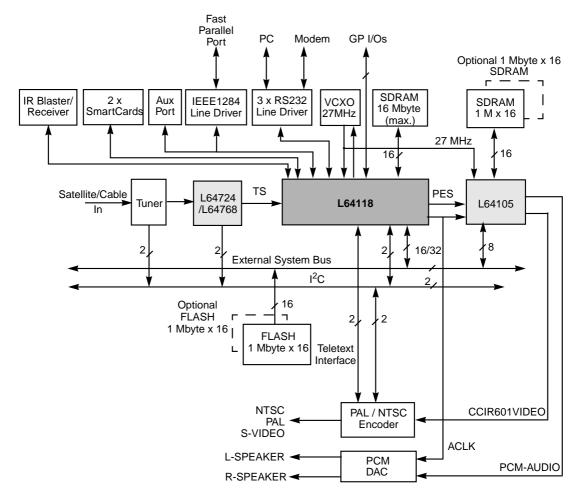

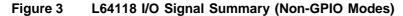

The components of the L64118 are integrated to provide a complete system solution for demultiplexing and processing incoming MPEG-2 Transport Stream packets. Figure 2 shows the three main blocks of the L64118: the TR4101 CPU and associated core building blocks, the transport (demultiplexer) block, and the peripheral device interfaces.

Additionally, the L64118 has three main buses:

• Basic Bus (BBus)

The BBus is an internal 32-bit bus that connects the CPU core and building blocks with internal memory and peripherals through the CPU-to-Peripheral (C2P) bridge.

• Peripheral Bus (PBus)

The PBus is the internal peripheral bus; it links the CPU to SDRAM memory, internal peripheral devices, and the demultiplexer using the C2P bridge.

• External System Bus (EBus)

The EBus is a general-purpose 16- and 32-bit synchronous system bus that lets the L64118 communicate with external components in the system. The EBus connects to the BBus through the EBus controller.

The following subsections provide an overview of the chip's main blocks.

# Figure 2 L64118 Internal Block Diagram

# **TinyRISC MIPS CPU Core**

With its powerful MIPS CPU, the L64118 can support all of the system's general-purpose control requirements, including:

- Complete set-top system initialization and testing

- Security handling

- Communication ports protocol processing

- Remote control handling

- PCR recovery and locking

- Audio/video synchronization for lip-syncing

The CPU also supports transport and system data software processing on data posted to the SDRAM by the transport processing block. This includes operations such as:

- PSI and DVB SI table maintenance (Program Association Table (PAT), Conditional Access Table (CAT), Program Map Table (PMT), Network Information Table (NIT))

- Private Section filtering

- Subtitle processing and OSD overlay

- Closed caption and teletext

- Electronic Program Guide

The MIPS CPU in the L64118 has more than enough processing power to implement all the tasks listed above.

The CPU core can be programmed with 16- or 32-bit instructions. The 32-bit operations allow high-performance operation; using the 16-bit architecture permits a reduced code size, saving memory. Both 16- and 32-bit instructions can be used in the same design.

The L64118's TR4101 MIPS CPU is part of LSI Logic's CoreWare<sup>®</sup> technology. The chip integrates the complete CPU subsystem, including:

- CPU (TR4101)

- Cache memory for instruction (2 x 4 Kbyte) and data (4 Kbyte) cache

- Basic BIU and Cache Controller (BBCC)

- Timers (including watchdog timer)

- Interrupt Controller

- Debugger Building Module (DBX)

- Multiply/Divide Unit (MDU)

- ICE port (full-duplex, serial receive and transmit port)

- CPU-to-Peripheral bus (C2P)

The L64118's embedded 32-bit MIPS CPU runs at 54 MHz. This clock rate permits a peak processing rate of 54 MIPS. The chip's internal CPU core is implemented in 32-bit architecture, but it can execute both 16-bit and 32-bit instructions. The L64118 has a 16-bit data interface to external SDRAM, and a 32-bit data interface to the external system bus (EBus). The CPU operates in Big Endian<sup>1</sup> mode.

Since most transport processing and filtering is implemented in hardware, much of the CPU's processing power can be devoted to system processing. The chip includes address decoding logic for directly interfacing to external memory (FLASH, SDRAM) without requiring external glue logic.

The interface between the CPU subsystem and the rest of the L64118 is implemented by the C2P unit. The C2P module translates 32-bit data accesses by the CPU to 8- and 16-bit data accesses on the Peripheral Bus, which connects all other blocks. The PBus is synchronous to the 27 MHz system clock.

# Transport Demultiplexer Block

The transport demultiplexer block processes the transport stream data coming from the channel interface. The input of the L64118 transport block interfaces to the channel decoder; the output interfaces to the

<sup>1.</sup> Big-Endian means that the address of a multiple-byte data type is the address of its most significant byte.

SDRAM controller module. The block includes a PID processor unit (PPU) that is compliant with DVB and JSAT and meets the requirements of many other service providers, including Canal+, SkyPerfect, and BSkyB.

The unit can process up to 32 PIDs simultaneously. It provides extensive filtering of PSI, SI, and Private Sections. The PSI, SI, and Private Sections are filtered according to 32 user-programmable match/mask PIDs. Section data that passes filtering is stored in cyclic buffers (in off-chip memory) associated with each PID. Each section in each PID can be filtered against 32 filters. (Every section undergoes a CRC32 check. An enable bit controls the CRC checking of all section types.) The on-chip descrambler unit increases system security. The audio and video data are reduced to PES streams and delivered to the A/V decoder.

# **SDRAM Controller**

The SDRAM controller and resource arbitration logic makes efficient use of SDRAM bandwidth. This chip's low-cost system implementation approach dictates usage of the external SDRAM for both transport and general system functions. The L64118 supports various SDRAM configurations using 16 Mbit and 64 Mbit devices, for a total memory size of 2, 8, or 16 Mbytes of external SDRAM.

The SDRAM controller arbitrates access to the external SDRAM. This logic provides the maximum possible SDRAM bandwidth to the on-chip CPU without increasing the need for buffers or other resources.

# External System Bus (EBus)

The External System Bus is a general-purpose 16- and 32-bit system bus used for communication with external components in the system. This bus provides the system designer with an interface that permits the glueless connection of devices like FLASH, ROMs, and external peripherals.

The EBus comprises a 32-bit wide interface with multiplexed address and data. Eight address bits are available as demultiplexed bits for easy interface to devices that do not need the full address space. In addition a demultiplexed mode can be configured to provide a 24-bit address and 16-bit data bus.

The EBus controller registers let the user program customized timing for each address space used in a given system. Six address spaces are supported, each with a dedicated chip select output.

The main features of the EBus are:

- 32-bit physical addressing space

- 32-bit data width

- Synchronized to 27 MHz clock

- Five external interrupt ports

The EBus supports the following main signals:

- 32-bit multiplexed address/data

- 8-bit demultiplexed (low order) address bits

- RDn

- WRn

- EACKn

- ALE (Address latch enable)

- Five dedicated chip-selects and one multiplexed (with memory strobe) chip select

- 4-bit byte enable bus

- 27 MHz output clock

# Peripherals

The L64118 integrates several serial and parallel ports, providing a high degree of connectivity to various types of peripherals. The communication ports include:

• Three 8251 RS232 serial communication ports connect the set-top box to a dumb monitor, modem, or PC. The modem communicates between the subscriber and the main station, or back channel.

One serial I/O includes a V24-compatible UART for a glueless connection to modem datapump ICs.

- One IEEE1284 parallel communication port for fast communication with a PC or workstation. The L64118 includes an on-chip DMA controller dedicated for data transfers between the IEEE1284 parallel communication port and the main memory.

- One I<sup>2</sup>C-compatible serial communication port to communicate with devices using I<sup>2</sup>C data links. This type of bus is common in video encoders, audio DACs, remote control devices, and RF tuners.

- Two independent SmartCard ports ISO-7816-3 compliant SmartCard ports interface through a SmartCard coupler, and support the T = 0, T = 1 asynchronous protocol. The ports also feature  $V_{CC}$ ,  $V_{PP}$  control.

- One Teletext port that interfaces to an NTSC or PAL encoder and allows for direct insertion of teletext data into an NTSC or PAL video encoder device. The teletext data usually is transmitted using a special-purpose PID. The data is then extracted by the Transport processor and posted to SDRAM. Finally, the L64118 controller transfers the teletext data to the Teletext port upon request from the video encoder device. The Teletext port includes a FIFO between the real-time timing required on the output pins and the internal data transfer.

- An Aux parallel port for outputting/inputting transport packets from/to the internal demultiplexer. The port's direction is controlled through a configuration bit or through the AUXTX input pin. The port can be programmed to deliver or receive transport packets at various points within the demultiplexer's pipeline. This port is multiplexed with signals from the IEEE1284 port.

- An Infrared port with a single IR blaster with two identical output pins and two identical, yet independent, IR receiver modules. The IRT (transmitter) can be used to communicate with off-board elements (e.g., to program a VCR). The two IR receivers, IR0 and IR1, support remote control of the STB.

- Forty-seven general-purpose I/O pins (GPIOs) are configurable and can be used to control and monitor a subset of processor functions, thus easing system integration and minimizing external glue logic.

Forty-one of these I/Os are multiplexed, six are dedicated GPIOs.

# **DMA Controller**

The L64118 integrates a four-channel DMA controller that reduces a major portion of the load the CPU might incur during data transfer between peripheral ports, memory, and elements residing on the EBus.

One DMA channel is dedicated for data transfers between the IEEE1284 port and main memory. The other three DMA channels are general-purpose. One general-purpose DMA channel (Channel #1) supports transfers between PBus and Ebus devices.

In typical applications, one DMA channel can be assigned to a SmartCard, one channel to a serial port, and one to memory to memory data transfers.

# Addressing

The MIPS architecture uses two types of addresses: virtual addresses (used in a program), and physical addresses (that appear on an address bus). This allows support of kernel and user modes, while combining cacheable and noncacheable addresses.

Virtual addresses are partitioned into four, fixed-size segments: *kuseg*, *kseg0*, *kseg1*, and *kseg2*, according to Table 1.

| Virtual CPU Address [31:29] | Segment          | Size       |

|-----------------------------|------------------|------------|

| 0b000–0b011                 | kuseg            | 2 Gbytes   |

| 0b100                       | kseg0 (cache)    | 512 Mbytes |

| 0b101                       | kseg1 (noncache) | 512 Mbytes |

| 0b110–0b111                 | kseg2 (not used) | 1 Gbytes   |

## Table 1 Memory Segment Address Mapping

The *kuseg* addresses are accessible in user and kernel mode; they are for use by user-mode programs, while also providing direct access (requiring no system call) to those same addresses in kernel mode.

Because the L64118 does not have a Memory Management Unit (MMU), *kuseg* addresses are mapped unchanged to physical addresses. The L64118 does not map *kseg2*; thus, *kseg2* addresses cannot be used by

the programmer. Noncacheable *kseg1* addresses are used for accessing peripheral registers and for code that requires noncacheability (for example, initialization code that is executed before the caches have been flushed). Cacheable *kseg0* addresses are used for all other code.

The on-chip CPU performs virtual to physical address translation; the resultant 32-bit physical addresses are output on the internal BBus. The CPU to Peripheral (C2P) bridge module maps the 32-bit BBus address to the internal 24-bit PBus address. The EBus interface module (which resides on the internal BBus) maps the 32-bit BBus address to the 24/32<sup>1</sup>-bit EBus address, according to the mode in which the EBus interface is configured and the width of the area being accessed.

The L64118 supports a 16 or 32 Mbyte physical address space (depending on the size of the SDRAM supported in the system). Virtual addresses in *kseg0* and *kseg1* are always mapped to the same physical addresses, namely to the lowest 16 (or 32) Mbytes of physical memory. The programmer can differentiate between cacheable and noncacheable addresses by using a virtual address either in *kseg0* or *kseg1* (e.g., PSI/PES data is stored in a noncacheable location, since they are posted by the PID processor).

As part of the CPU subsystem, the L64118 a small module (the MMU Stub) that maps the *kseg0* and *kseg1* segments to the same physical address. It does this by clearing the three most significant bits of the address in the *kseg0* and *kseg1* segments presented by the CPU (on the internal CPU bus). Segments *kuseg* and *kseg2* are unaffected by the MMU Stub.

Note that the L64118 CPU operates only in Big-Endian mode; the Ebus must be set to operate in Big-Endian mode. A strap option on the GPIO[42] pin (sampled during reset) determines the physical connection on the EBus.

<sup>1.</sup> The EBus uses either a 24-bit address or a 32-bit address, depending on the address space being accessed.

The address space of the L64118 is partitioned into the following areas:

• CPU/Peripheral

This address space contains the control and status registers for the CPU and core building blocks.

- Configuration Register Space

The space contains registers that define the configuration of each

peripheral on the PBus. It is partitioned into 1 Kbyte segments,

where each segment corresponds to the Configuration register entry

for each PBus component. See Table 3.

- Attribute Register Space

The Attribute register space contains the Attribute register 0 for each peripheral on the PBus. This space is partitioned into 1 Kbyte segments, where each segment corresponds to the Attribute register entry for each PBus component. See Table 3.

Internal I/O

The internal I/O space contains I/O registers and functions for each peripheral on the PBus. It is partitioned into 256 4 Kbyte segments, where each segment corresponds to an I/O entry for a PBus component. See Table 3.

External ROM

External ROM contains the operating system, user's application programs (*kseg0*), configuration code, and initialized data (*kseg1*).

• External space for the EBus

The external space is used for user-defined external memory and external devices residing on the EBus. It is divided into three subspaces, each one supporting devices with a different width (8, 16, 32 bits).

Primary SDRAM

The lowest 2/8/16 Mbytes of addressable space are mapped to the external SDRAM through the internal SDRAM controller. See Table 2, "PBus to EBus Address Mapping,"

| 118 EBus        | PBus Address            |

|-----------------|-------------------------|

| 2 Mbytes SDRAM  | 0x0000.0000-0x1F.FFFF   |

| 8 Mbytes SDRAM  | 0x0100.0000–0x017F.FFFF |

| 16 Mbytes SDRAM | 0x0100.0000-0x01FF.FFFF |

# Table 2 PBus to EBus Address Mapping

Note that the PBus addresses are not driven on the EBus, but rather are routed to the SDRAM controller. The two Mbyte and eight Mbyte mode are software compatible with the L64108 code, since the External Space 2 (ES2) of the L64108 is located at PBus address 0x0080.0000 (by default).

Table 3 summarizes the L64118 address space.

# Table 3 L64118 Address Mapping

| Virtual CPU Ba           | se Address     |                      |                                            | PBus/EBus                                      |                  |

|--------------------------|----------------|----------------------|--------------------------------------------|------------------------------------------------|------------------|

| Noncache<br>kseg1        | Cache<br>kseg0 | BBus Base<br>Address | Address Space<br>Name                      | Physical<br>Base<br>Address                    | Size<br>(Mbytes) |

| 0xBFFF.0000              | N/A            | 0x1FFF.0000          | CPU/Peripheral<br>(Reserved <sup>1</sup> ) | Not used                                       | 0.50             |

| 0xBFF8.0000              | N/A            | 0x1FF8.0000          | Not used                                   | Not used                                       | 0.50             |

| 0xBFF4.0000              | N/A            | 0x1FF4.0000          | Internal<br>Configuration<br>Registers     | 0xF4.0000<br>(PBus)                            | 0.25             |

| 0xBFF0.0000              | N/A            | 0x1FF0.0000          | Internal Attribute<br>Registers            | 0xF0.0000<br>(PBus)                            | 0.25             |

| 0xBFE0.0000              | N/A            | 0x1FE0.0000          | Internal I/O                               | 0xE0.0000<br>(PBus)                            | 1                |

| 0xBFC0.0000              | 0x9FC0.0000    | 0x1FC0.0000          | External ROM                               | 0xC0.0000<br>(EBus demux<br>mode)              | 2                |

| 0xB800.0000 <sup>2</sup> | 0x9800.0000    | 0x1800.0000          | 8-bit devices in the<br>External Space     | 0x00.0000<br>(EBus demux<br>mode) <sup>3</sup> | ≤ 64             |

| 0xB400.0000 <sup>4</sup> | 0x9400.0000    | 0x1400.0000          | 16-bit devices in<br>the External<br>Space | 0x00.0000<br>(EBus demux<br>mode) <sup>5</sup> | ≤ 64             |

| 0xB000.0000 <sup>6</sup> | 0x9000.0000    | 0x1000.0000          | 32-bit devices in<br>the External<br>Space | 0x1000.0000<br>(EBus mux<br>mode) <sup>7</sup> | ≤ 64             |

# Table 3 L64118 Address Mapping (Cont.)

| Virtual CPU Ba    | ase Address    |                      |                                                             | PBus/EBus<br>Physical |                  |

|-------------------|----------------|----------------------|-------------------------------------------------------------|-----------------------|------------------|

| Noncache<br>kseg1 | Cache<br>kseg0 | BBus Base<br>Address | Address Space<br>Name                                       | Base<br>Address       | Size<br>(Mbytes) |

| 0xA000.0000       | 0x8000.0000    | 0x0000.0000          | Primary SDRAM<br>when 2 Mbytes of<br>SDRAM is used          | 0x0000.0000<br>(PBus) | 2                |

| 0xA000.0000       | 0x8000.0000    | 0x0000.0000          | Primary SDRAM<br>when 8 or<br>16 Mbytes of<br>SDRAM is used | 0x0100.0000<br>(PBus) | 8 or 16          |

1. These transactions do not appear on the PBus. This space is used only when the CPU accesses BBus components (BBCC, Timer, C2P, INTC, ICEport).

- 2. Within this range, used for 8-bit devices, specific address ranges can be selected (and the mode in which they are accessed) using the Ebus address compare registers.

- 3. Bits [23:0] of the BBus address are reflected onto the EBus Address bus for eight-bit devices.

- 4. Within this range used for 16-bit devices, specific address ranges can be selected (and the mode in which they are accessed) using the EBus Address Compare registers.

- 5. Bits [23:0] of the BBus address are reflected onto the EBus Address bus for 16-bit devices.

- 6. Within this range used for 32-bit devices, specific address ranges can be selected (and the mode in which they are accessed) using the EBus Address Compare registers.

- 7. Same address used on the EBus and BBus when 32-bit devices are accessed.

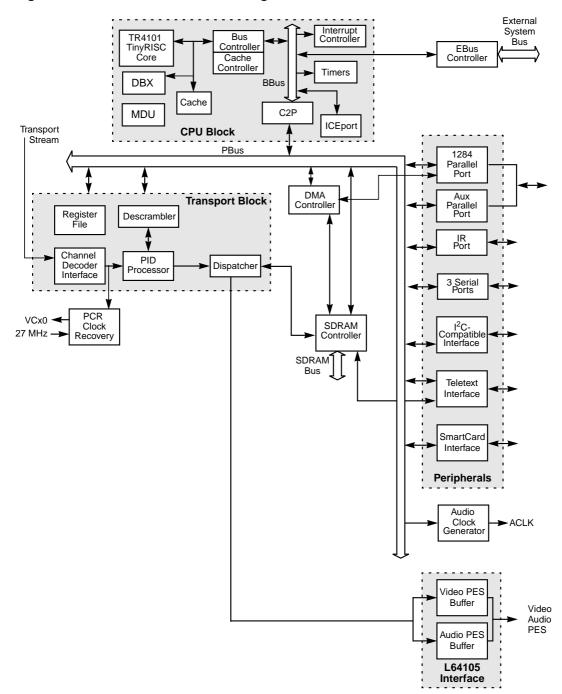

# Signals

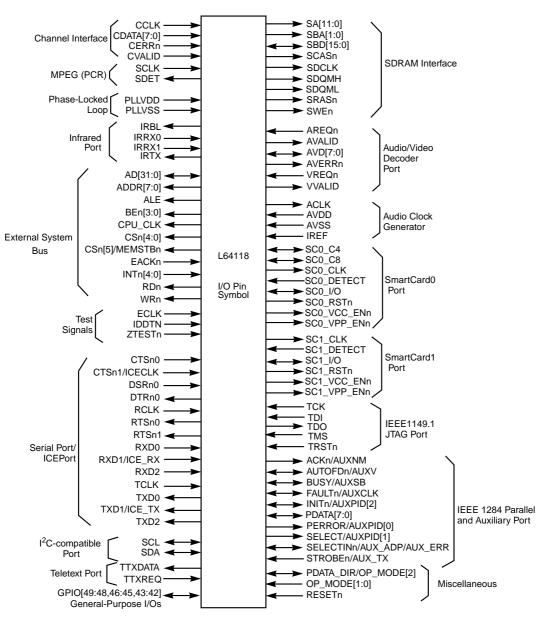

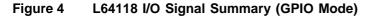

This section describes the signals used by the L64118. Figure 3 shows the L64118 non-GPIO mode signals in functional groups and Figure 4 shows the L64118 GPIO mode signals. The signals are described by group. Within each group, signals are listed in alphabetic order.

Table 4 lists the default values of the output and bidirectional signals. Note that during reset, all bidirectional signals (and some output signals) are floating.

| Signal                        | Default Value            | Notes |

|-------------------------------|--------------------------|-------|

| ACKn/AUXNM                    | not asserted             |       |

| ACLK                          | inactive (LOW)           |       |

| AD[31:0]                      | driving an unknown value |       |

| ADDR[7:0]                     | driving an unknown value |       |

| ALE                           | not asserted             |       |

| AUTOFDn/AUXV                  | not asserted             |       |

| AVALID                        | not asserted             |       |

| AVD[7:0]                      | driving an unknown value |       |

| AVERRn                        | not asserted             |       |

| BEn[3:0]                      | not asserted             |       |

| BUSY/AUXSB                    | not asserted             |       |

| CSn[4:0]                      | not asserted             |       |

| CSn[5]/MEMSTBn                | not asserted             |       |

| DTRn0                         | not asserted             |       |

| FAULTn/AUXSB                  | not asserted             |       |

| GPIO42, 43, 45,<br>46, 48, 49 | floating                 |       |

| INITn/AUXPID[0]               | not asserted             |       |

| IRTX                          | not asserted             |       |

| PDATA_DIR/<br>OP_MODE[2]      | drives assertion         |       |

| PDATA[7:0]                    | floating                 |       |

| RDn                           | not asserted             |       |

# Table 4Default Values for L64118 Output and Bidirectional<br/>Signals After Reset1

| Signal         | Default Value                                | Notes              |

|----------------|----------------------------------------------|--------------------|

| RTSn0/1        | not asserted                                 |                    |

| SA[11:0]       | driving an unknown value                     |                    |

| SBA[1:0]       | driving an unknown value                     |                    |

| SBD[15:0]      | floating                                     |                    |

| SC0_C4, SC0_C8 | pulled up by an external pull-up resistor    |                    |

| SCASn          | not asserted                                 |                    |

| SCx_CLK        | not asserted                                 |                    |

| SCx_DETECT     | floating                                     | serves as an input |

| SCx_IO         | pulled up by an external pull-up resistor    |                    |

| SCx_RSTn       | not asserted                                 |                    |

| SCx_VPP_ENn    | not asserted                                 |                    |

| SCx_VCC_ENn    | not asserted                                 |                    |

| SCL            | pulled up using an external pull-up resistor |                    |

| SDA            | pulled up using an external pull-up resistor |                    |

| SDCLK          | toggling                                     |                    |

| SDQMH          | not asserted                                 |                    |

| SDQML          | not asserted                                 |                    |

| SRASn          | not asserted                                 |                    |

| SWEn           | not asserted                                 |                    |

# Table 4Default Values for L64118 Output and Bidirectional<br/>Signals After Reset1 (Cont.)

| Signal        | Default Value | Notes               |

|---------------|---------------|---------------------|

| TTXREQ/GPIO12 | floating      | behaves as an input |

| TTXDATA       | not asserted  |                     |

| TXD0/2        | asserted      |                     |

| TXD1/ICE_TX   |               |                     |

| VVALID        | not asserted  |                     |

| WRn           | not asserted  |                     |

# Table 4Default Values for L64118 Output and Bidirectional<br/>Signals After Reset1 (Cont.)

1. A few cycles after reset (RESETn is driven HIGH), the L64118 initiates a transaction on the EBus, changing some of the default values in this table.

# **Channel Interface Port**

These signals provide the physical connection to Channel Interface devices, such as LSI Logic's L64724 or L64768. This port supports both parallel and serial connections.

# CCLK Channel Clock Input When CVALID is asserted HIGH, the L64118 latches CDATA[7:0] on the rising edge of CCLK. In serial mode, the L64118 uses only CDATA[0]. In serial mode, the maximum clock rate is 60 MHz; in parallel mode, it is 13 MHz. The CCLK must toggle during reset to ensure proper reset of the channel interface block. CDATA[7:0] Channel Data Input

These signals deliver channel information to the L64118. When CVALID is asserted, the chip latches the data on every rising edge of CCLK. When the L64118 is in parallel input mode, all CDATA[7:0] signals deliver data. When the L64118 is in serial mode, only CDATA[0] delivers data.

| CERRn  | Channel Data ErrorInputThis active LOW input signal indicates that an<br>uncorrected error occurred in the preceding channel<br>interface. When CVALID is asserted, CERRn is latched<br>on the rising edge of CCLK. |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CVALID | Channel Data Valid Input<br>This active HIGH input signal indicates that CDATA[7:0]                                                                                                                                 |

This active HIGH input signal indicates that CDATA[7:0] and CERRn are carrying valid data. When CVALID is asserted, a rising edge of CCLK latches the CDATA[7:0] signals into the L64118.

# MPEG Program Clock Reference (PCR) Recovery

These signals recover the Program Clock Reference (PCR). They interface to the external VCxO, which provides the 27 MHz clock to the decoder.

- SCLK27 MHz System ClockInputThis input provides the clock signal to the L64118. It must<br/>be driven by the external 27 MHz VCxO (the voltage<br/>control input is controlled by SDET and the external<br/>RC filter).

- **SDET** System Clock Sigma-Delta Control Voltage Output This converter output signal from a 16-bit Sigma-Delta modulator inside the L64118 drives a simple low-pass filter to produce an analog control voltage to an external VCxO.

# Phase-Locked Loop (PLL)

These signals supply power and ground to the internal PLL, which generates the internal 54 MHz CPU clock from the external 27 MHz SCLK input. The 54 MHz internal clock is then divided by two to generate the internal 27 MHz clock used by other internal modules. Isolate the PLLVDD and the PLLVSS signals from digital noise and digital logic on the PCB using layout and bypass filtering techniques.

| PLLVDD | PLL Analog VDD Input                                       |

|--------|------------------------------------------------------------|

|        | This provides a separate filtered 3.3 V to the PLL circuit |

|        | through PLLVDD so that switching noise from the digital    |

|        | portion of the chip can not affect PLL stability.          |

# PLLVSS PLL Analog VSS

Input

This provides a separate ground to the PLL circuit through PLLVSS so that switching noise from the digital portion of the chip does not affect PLL stability.

# **External System Bus (EBus)**

The EBus comprises a 32-bit wide interface with multiplexed address and data. Eight address bits are available as demultiplexed bits for an easy interface to devices that do not need the full address space. All bus transactions are synchronous to the 27 MHz output CPU\_CLK.

A subset of these signals can be programmed to act as general-purpose I/O signals by setting bit [0] in the General-Purpose Mode register.

- AD[31:0] Multiplexed Address/Data Bus Bidirectional AD[31:0] is the multiplexed address/data bus. The L64118 can be programmed to drive the full address on this bus at access start. After this address phase the bus presents write data for a write or the external device drives data on the bus in a read.

- ADDR[7:0]

Demuxed Address Bus

Output

ADDR[7:0] provides eight bits of demultiplexed address

bits. This bus allows some designs to remove the

external address latch on the multiplexed address/data

bus to hold the address throughout the transaction. The

EBus uses byte addressing. All 16-bit devices must

ignore ADDR[0]. All 32-bit devices must ignore

ADDR[1:0].

Address batch Facility

- ALE Address Latch Enable Output This active HIGH signal controls the latches for demultiplexing the address from the AD bus.

# **BEn[1:0]** Byte Enables Output The four byte enable outputs are asserted during a read or write transaction on the EBus to control which of the four byte lanes are enabled. The byte lane selection is dependent on the width of the transaction (word, halfword, or byte) and the data width of the external device (32, 16, or 8 bits).

The byte enables always correspond to the same physical lines on the AD bus: BEn[1] corresponds to AD[15:8], BEn[0] to AD[7:0].

# BEn[2] Byte Enable

The four byte enable outputs are asserted during a read or write transaction on the EBus to control which of the four byte lanes are enabled. The byte lane selection is dependent on the width of the transaction (word, halfword, or byte) and the data width of the external device (32, 16, or 8 bits).

The byte enables always correspond to the same physical lines on the AD bus: BEn[2] corresponds to AD[23:16].

# GPIO2

# Bidirectional

BEn[2] can serve as a general-purpose I/O signal (GPIO2) by setting bit 0 in the General-Purpose Mode register.

# BEn[3] Byte Enable Outputs are assorted during a read

The four byte enable outputs are asserted during a read or write transaction on the EBus, to control which of the four byte lanes are enabled. The byte lane selection is dependent on the width of the transaction (word, halfword, or byte) and the data width of the external device (32, 16, or 8 bits).

The byte enables always correspond to the same physical lines on the AD bus: BEn[3] corresponds to AD[31:24].

# GPIO3

# Bidirectional

BEn[3] can serve as a general-purpose I/O signal (GPIO4) by setting bit 0 in the General-Purpose Mode register.

# CPU\_CLK EBus Output Clock

This 27 MHz output clock is generated dividing the on-chip 54 MHz clock by two. This clock serves as the reference signal for all transactions on the EBus. The timing relationship between the SDCLK output clock, the 27 MHz SCLK input and the 27 MHz CPU\_CLK output is unknown.

26

# Output

# Output

# CSn[3:0] Programmable Chip Selects

Each chip select pin can be programmed to assert in a specific address area. These pins are used to select specific external devices according to on-chip address decoding. They make interfacing to various peripherals easier, as they can remove the need for external address decoders.

# CSn[4] Programmable Chip Select

This pin is similar in function to the other five chip select output pins. It is used to select specific external devices according to on-chip address decoding.

# GPIO1

# **Bidirectional**

CSn[4] can serve as a general-purpose I/O signal (GPIO1) by setting bit 0 in the General-Purpose Mode register.

# CSn[5]/MEMSTBn

## Chip Select[5] or Memory Strobe Output This pin is similar in function to the other five chip select

output pins but holds the characteristic of being able to function as the MEMSTBn (active LOW memory strobe) signal. The MEMSTBn signal is a general-purpose signal. It can be used to indicate that a memory transaction is in progress. It is asserted in both read and write cycles. The timing on this signal is programmable.

# EACKn Target Acknowledge

This signal indicates to the L64118 that the external device is ready to complete the current read or write cycle. The transaction will finish if both EACKn is asserted and the internal wait state generator has expired. This mechanism allows devices to extend an access beyond the number of wait states programmed for that particular address area.

EACKn can be programmed to be either active HIGH or LOW, using the XPOS bit in the CEBUSMODE register. EACKn must be deasserted before the next transaction acknowledge cycle.

For self-acknowledge devices, the external EACKn pin can be ignored, so the transaction completes when the wait state generator expires. This is controlled by the XACK bit in the CECFGn register.

# Output

Output

### Input

| INTn4     | Interrupt Input<br>This unmaskable interrupt can be used for highest priority<br>system needs.                                                                                                                                                                                                                                                                                                                                         |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INTn[3:0] | InterruptsInputThese four external interrupts can be programmed to be<br>level- or edge-triggered sensitive. Interrupts INTn[3:0] are<br>maskable and for general-purpose use. When the<br>L64118 receives an interrupt, the internal CPU completes<br>the execution of the current instruction and jumps to a<br>preprogrammed location in the memory containing the<br>handler for this interrupt. By default, these signals are<br> |

| RDn       | ReadOutputThe active LOW read strobe is asserted during readoperations, and deasserted during writes.                                                                                                                                                                                                                                                                                                                                  |

| WRn       | Write EnableOutputThe active LOW write strobe is asserted during write<br>operations and deasserted during reads.                                                                                                                                                                                                                                                                                                                      |

# **Miscellaneous Signals**

28

These general signals are not necessarily associated with a specific function or module of the L64118.

# OP\_MODE[1:0]

## **Operational Mode**

These signals, along with OP\_MODE[2], are used as strap options to configure various LSI Logic test modes. For normal operation, configure OP\_MODE[2:0] to 0b000. That is, OP\_MODE[1:0] should be tied LOW, and OP\_MODE[2] should be pulled LOW with a 10 k $\Omega$  resistor.

# OP\_MODE[2]/PDATA\_DIR

# **Operational Mode**

This signal is used as a strap option during reset in conjunction with the OP\_MODE[1:0] pins, and must be pulled LOW with a 10 k $\Omega$  resistor for proper device operation.

# Input

Input

Parallel Data DirectionOutputAfter reset, this signal serves as the PDATA\_DIR output,<br/>which controls the parallel data bus buffers for the 1284<br/>PDATA[7:0] data lines. When the 1284 port is used as an<br/>Aux port, this pin is driven HIGH.

RESETnAsynchronous ResetInputAsserting this active LOW signal resets the L64118 to its<br/>power on state. To ensure a complete reset of the<br/>L64118, RESETn must be asserted for at least 16 SCLK<br/>cycles.

# **Test Signals**

These signals are for LSI Logic test purposes. They must be tied to a constant value in normal operational mode.

| ECLK   | <b>Connect to VSS</b><br>This is an LSI Logic manufacturing test pin.                                                     | Input |

|--------|---------------------------------------------------------------------------------------------------------------------------|-------|

| IDDTN  | <b>Connect to VSS</b><br>This is an LSI Logic manufacturing test pin.                                                     | Input |

| ZTESTn | <b>Connect to VDD</b><br>This is an LSI Logic manufacturing test pin. It is<br>deasserted HIGH for normal chip operation. | Input |

# Serial Port/ICEPort

These signals connect the L64118 to an external modem, PC, terminal, or other host that includes an RS232 interface. The L64118 contains three serial ports that comply with the asynchronous specification of the RS232 standard. The on-chip baud rate generators support the standard bit rate for serial communication.

Three of the SIO1 signals can be configured to serve the internal ICEport module.

| CTSn0 | Clear to Send Port 0                                 | Input   |

|-------|------------------------------------------------------|---------|

|       | When reset LOW, this signal indicates that the exte  | ernal   |

|       | receiver is ready for data transfer through TxD0/Rx  | D0. If  |

|       | the Transmit Enable bit in the SIO Command regis     | ster is |

|       | set HIGH when CTSn0 is reset LOW, data from th       | e       |

|       | Transmit register of Port 0 is serialized through Tx | D0.     |

# Bidirectional

CTSn0 can serve as a general-purpose I/O signal (GPIO7) by setting bit 1 in the General-Purpose Mode register.

# CTSn1/ICECLK

# Clear to Send Port1

This pin can serve as either the Clear to Send signal of SIO1, or as the ICEport clock input for the ICEport module. The strap option on GPIO[43] controls this pin's functionality and usage. If GPIO[43] is sampled HIGH during reset, this pin serves as CTSn1.

When reset LOW, this signal indicates that the external receiver is ready for data transfer through TxD1/RxD1. If the Transmit Enable bit in the SIO Command register is set HIGH when CTSn1 is reset LOW, data from the Transmit register of Port 1 is serialized through TxD1.

# Serial ICE Clock

When serial ICE mode is enabled, this pin functions as ICECLK, the synchronous ICE port clock input.

### DSRn0 Data Set Ready Port 0

Input When reset to LOW, this general-purpose input control signal indicates that an external terminal device is ready for data transfer. The polarity of DSRn0 is latched in Port 0 Status register for the CPU to read.

# GPIO9

# Bidirectional

Output

DSRn0 can serve as a general-purpose I/O signal (GPIO9) by setting bit 1 in the General-Purpose Mode register.

### DTRn0 Data Terminal Ready Port 0

When this general-purpose output control signal is reset to LOW. data for the external terminal device is ready to be transmitted. DTRn0 can be set or reset by programming the DTR bit in the SIO Command register. By default, this signal is not asserted after reset.

# GPI08

## Bidirectional

DTRn0 can serve as a general-purpose I/O signal (GPIO8) by setting bit 1 in the General-Purpose Mode register.

# Input

Input

| RCLK  | Receive Serial Data ClockInputThis signal is used for the receive clock input in the<br>enhanced UART mode.                                                                                                                                                                                          |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RTSn0 | Request to Send Port 0OutputWhen this general-purpose, programmable control signal<br>is reset to LOW, Port 1 is ready to send data through<br>TxD1. This signal is set and reset by programming the<br>RTS bit in the SIO Command register. By default, this<br>signal is not asserted after reset. |

|       | <b>GPIO10 Bidirectional</b><br>RTSn0 can serve as a general-purpose I/O signal<br>(GPIO10) by setting bit 1 in the General-Purpose Mode<br>register.                                                                                                                                                 |

| RTSn1 | Request to Send Port1OutputWhen this general-purpose, programmable control signal<br>is reset to LOW, Port 1 is ready to send data through<br>TxD1. This signal is set and reset by programming the<br>RTS bit in the SIO Command register.                                                          |

| RXD0  | Receive Data Port 0InputThis signal provides serial data from an external RS232device. Its protocol is similar to that of TxD0. The receivebaud rate can be programmed in the SIO Baud Rateregister. The data received on RXD0 is latched in theReceive register of Port 0.                          |

|       | <b>GPIO11 Bidirectional</b><br>RXD0 can serve as a general-purpose I/O signal<br>(GPIO11) by setting bit 1 in the General-Purpose Mode<br>register.                                                                                                                                                  |

# RXD1/ICE\_RX

## **Receive Data Port 1**

## Input

This pin serves either as the Receive port signal of SIO1, or as the ICEport receive input for the ICEport module. The strap option on GPIO[43] controls this pin's functionality and usage. If GPIO[43] is sampled HIGH during reset, this pin serves as RXD1. In that case, this signal provides serial data from an external RS232 device.

The protocol of this pin is similar to that of TxD1. The receive baud rate is determined by programming the SIO Baud Rate register. The data received on RXD1 is latched in the Receive register of Port 1. If GPIO[43] is sampled LOW during reset, then this pin serves as the receive port for the ICEport in the L64118.

### Receive Data - Serial ICE Port

When the serial ICE mode is enabled, this pin functions as ICE\_RX, the receive data port input.

Input

Output

# RXD2Receive Data Port 2InputThis signal provides serial data from an external RS232<br/>device. The protocol of this pin is similar to that of TxD2.<br/>The receive baud rate is determined by programming the<br/>SIO Baud Rate register. The data received on RXD2 is<br/>latched in the Receive register of Port 2.TCLKTransmit Serial Data ClockInput

This signal is used for the transmit clock in the enhanced UART mode.

# TXD0Transmit Data Port 0OutputThis signal outputs data in compliance with the RS232<br/>protocol's asynchronous specification. The transmit baud<br/>rate is determined by programming the SIO Baud Rate<br/>register. Data transmitted on TXD0 comes from the<br/>Transmit register of Port 0. By default, this signal is not<br/>asserted after reset.

## TXD1/ICE\_TX

# Transmit Data Port 1

This pin can serve as either the Transmit Data port signal of SIO1, or as the ICEport receive input for the ICEport module. The strap option on GPIO[43] controls this pin's functionality and usage. If GPIO[43] is sampled HIGH during reset, this pin serves as TXD1.

When set to TXD1, this signal outputs data in compliance with the RS232 protocol's asynchronous specification. The data rate on this pin is determined by programming the SIO Baud Rate register. Data transmitted on TXD1 comes from the Transmit register of Port 1. Transmit Data - Serial ICEPortOutputIf GPIO[43] is sampled LOW during reset, this pin serves<br/>as ICE\_TX, the serial ICE transmit data output port. By<br/>default, this signal is not asserted after reset.DutputTXD2Transmit Data Port 2<br/>This signal outputs data in compliance with the RS232<br/>protocol's asynchronous specification. The data rate on<br/>this pin is determined by programming the SIO Baud<br/>Rate register. Data transmitted on TXD2 comes from the

Transmit register of Port 2. By default, this signal is not

# **SDRAM** Interface

The following group of signals provides the interface between the L64118 and external SDRAM devices. The SDRAM interface works with PC66/100 compliant SDRAMs. The L64118 SDRAM interface runs at 54 MHz and is capable of accessing 2, 4, 8, or 16 Mbyte memory configurations using 16 Mbit or 64 Mbit devices.

asserted after reset.

This interface has a 16-bit data bus (SBD[15:0]). The upper and lower byte mask signals (SDQMH and SDQML) control halfword and byte accesses. The SBA[1:0] outputs support two- and four-bank SDRAM devices. The L64118 automatically performs SDRAM refreshes.

The L64118 does not support the Chip Select (CSn) and Clock Enable (CKE) signals. Tie these SDRAM signals active LOW and HIGH, respectively, on the SDRAM device(s) used.

- SA[11:0]

SDRAM Address Bus

Output

These signals carry the 12-bit SDRAM address bus. The number of row and column address bits used is programmable in the SDRAM Configuration register.

Output

- SBA[1:0] SDRAM Bank Select Output These signals allow access to SDRAM devices with either two or four banks. The number of bank select bits used is programmable in the SDRAM Configuration register.

| SBD[15:0] | SDRAM Data BusBidirectionalThis data bus is driven by the SDRAM during a readoperation, and driven by the L64118 during a writeoperation. It is 3-stated after reset and when there are nomemory accesses.                            |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCASn     | Column Address StrobeOutputThis signal is the active LOW column address strobe. Itis used in conjunction with the SRASn and SWEn outputsto form the SDRAM command.                                                                    |

| SDCLK     | SDRAM ClockOutputThis is the master SDRAM clock. All output signals are<br>referenced to the rising edge of SDCLK. The<br>programmable SDRAM timing parameters are expressed<br>in SDCLK periods.                                     |

| SDQMH     | High Byte MaskOutputThis active HIGH signal is the high byte data mask, which<br>controls the high byte input/output buffer of the external<br>SDRAM. When asserted, it disables (masks) the high<br>data byte of the SDRAM data bus. |

|           | <b>GPIO6 Bidirectional</b><br>SDQMH can serve as a general-purpose I/O signal<br>(GPIO6) by setting bit [0] in the General-Purpose Mode<br>register.                                                                                  |

| SDQML     | Low Byte Mask Output<br>This active HIGH signal is the low byte data mask, which<br>controls the low byte input/output buffer of the external                                                                                         |

|           | SDRAM. When asserted, it disables (masks) the low data byte of the SDRAM data bus.                                                                                                                                                    |

| SRASn     |                                                                                                                                                                                                                                       |

# Audio/Video Decoder Port

These signals provide the interface between the L64118 and an external MPEG-2 Audio/Video decoder. This interface supports a seamless connection between the L64118 and LSI Logic's L64105 A/V decoders. It supports a serial data transfer rate up to 27 Mbits/s in serial mode, 9 Mbytes/s in parallel mode. The actual data rate is controlled by the audio and video request signals coming out from the A/V decoder device.

- AREQN Audio Data Request Input When asserted, this signal indicates that the external A/V decoder is requesting the audio bit to be clocked in to the external A/V decoder. Deassertion of AREQn indicates that the A/V decoder is not ready to accept audio data.

- AVALID Audio Data Valid Output When asserted, this signal indicates that valid audio data is available on the AVD[7:0] bus. A LOW-to-HIGH transition of SCLK causes the audio data bit on AVD to be latched in the external A/V decoder. In serial mode, AVALID is active HIGH. In parallel mode, AVALID latches data on the rising edge. This signal is not asserted after reset.

- AVD[7:0] Audio Video Compressed Data Bidirectional This bus provides data to the external A/V decoder. In serial mode, AVD[0] carries the data. In parallel mode, the entire bus carries the byte-wide data. The L64118 outputs PES audio and video data from the on-chip buffers and SDRAM buffers through AVD[7:0]. These signals drive an unknown value after reset.

- AVERRnAudio Video Data ErrorOutputWhen asserted, this signal indicates that there is an<br/>uncorrected error in the bit stream entering the external<br/>A/V decoder. The L64118 generates AVERRn as a result<br/>of detection of discontinuity in the transport packets of the<br/>audio and/or video program being decoded. Usually, the<br/>discontinuity is the result of loss of packets from<br/>uncorrected errors. This signal is not asserted after reset.VREQnVideo Data RequestInput<br/>When asserted, this signal indicates that the external

When asserted, this signal indicates that the external A/V decoder device is requesting the video bit to be

clocked in to the external A/V decoder. Deassertion of VREQn indicates that the A/V decoder is not ready to accept video data.

VVALID is active HIGH. In parallel mode, VVALID latches data on the rising edge. This signal is not asserted after

# VVALID Video Data Valid Output When asserted, this signal indicates that valid video data is available on the AVD line. The LOW-to-HIGH transition of SCLK causes the video data bit on the AVD[7:0] bus to be latched in the external A/V decoder. In serial mode,

reset.

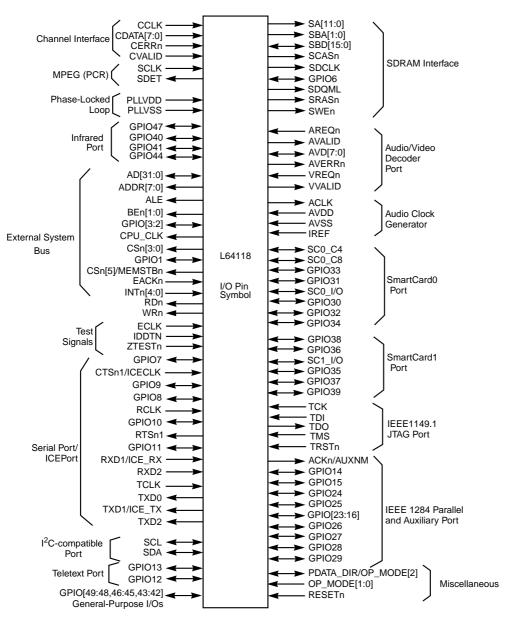

Audio Clock Generator

These signals generate the oversampling audio clock, which drives the L64105 external A/V decoder and a low-cost audio DAC. The audio clock generation circuit provides oversampling audio frequencies locked to the 27 MHz program clock. The fully programmable circuit supports a wide range of oversampling audio frequencies. It is implemented using advanced mixed-signal technology.

| ACLK | Audio Clock C<br>ACLK provides the oversampling audio clock that of<br>the L64105 audio clock input and the system clock<br>pin of conventional stereo audio DAC. This signal<br>driven LOW after reset. | input |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| AVDD | <b>Analog VDD 3.3 V</b><br>AVDD provides the power voltage to the analog circ<br>the audio clock generator. It must be isolated from<br>Digital VDD (DVDD) by a 10 μH ferrite insulator.                 |       |

| AVSS | Analog Ground<br>AVSS provides the analog ground to the audio clo<br>generator circuit. It should must be isolated from t<br>digital ground supply (DGND).                                               |       |

| IREF | <b>Current Reference</b><br>This pin must be connected as shown in Figure 5.                                                                                                                             |       |

IREF Connection to RC Devices

### IEEE 1149.1 (JTAG) Port

This group of signals drive the IEEE1149.1 Test Access Port (TAP).

| ТСК   | Test ClockInputThis is the clock pin to sample the JTAG input data.                                                                                         |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TDI   | Test Data InInputThis line is for the JTAG input test data.                                                                                                 |

| TDO   | Test Data OutOutputThis line is for the JTAG output test data.                                                                                              |

| TMS   | Test Mode SelectInputThis line lets you select between active and JTAG mode.When in JTAG mode, the I/Os are serialized. Active modeis for normal operation. |

| TRSTn | Test Port ResetInputWhen asserted LOW, this signal resets the internal JTAGcontroller. It does not reset the chip.                                          |

### **IEEE1284 Parallel Port and Auxiliary Port**

These signals provide a parallel connection between the L64118 and an external peripheral device. The port complies to IEEE1284 standards and supports several modes. The 1284 mode is enabled when the AUX SEL bit is reset (System Mode register, bit 4).

This port also serves as an auxiliary port for receiving and transmitting transport bitstreams from various points in the on-chip demultiplexer pipeline. The Aux mode is enabled when the AUX SEL bit is set (System Mode register, bit 4).

The following list shows each pin's functionality as an IEEE1284 port and Aux port signal. Some of these pins also can serve as general-purpose I/O pins.

### ACKn/AUXNM

### 1284 - Acknowledge

When the L64118 asserts this signal, valid data is latched in the L64118 IEEE1284 input register. By default, this signal is not asserted after reset.

### Aux - Aux No Match

### In Aux mode, this signal functions as AUXNM to indicate that the data being sent through the auxiliary port is for a transport packet that failed PID filtering.

### AUTOFDn/AUXV

38

1284 - Autofeed Input In 1284 mode, this pin functions as the Autofeed input.

### Aux - Data Valid

In Aux mode, this pin functions as AUXV, which is used as a qualifier indicating that the data presented on the auxiliary data bus is valid.

### **GPI014**

### This signal can serve as a general-purpose I/O signal (GPIO14) by setting bit 3 in the General-Purpose Mode register.

Bidirectional

### Output

Output

# Bidirectional

### **BUSY/AUXSB**

### 1284 - Peripheral Busy

In 1284 mode, this signal functions as BUSY. When this signal is HIGH, the 1284 port is not ready for a data transfer. By default, this signal is not asserted after reset.

### Aux - Sync Byte

### In Aux mode, this signal functions as AUXSB to indicate that the data being sent through the auxiliary port is the first byte (sync byte) of a transport packet.

### GPIO15

### **Bidirectional**

This signal can serve as a general-purpose I/O signal (GPIO15) by setting bit 3 in the General-Purpose Mode register.

### FAULTn/AUXCLK

### 1284 - Peripheral Fault Operation Bidirectional

In 1284 mode, this signal functions as FAULTn. This signal indicates that the 1284 port encountered an error during operation. Typically, this error is due to overrun, underrun, or parity error.

### Aux - Aux Port Clock

### In Aux mode, this signal functions as AUXCLK, which is the reference clock for all transactions on the auxiliary port. When the Aux port is configured as an output port, this signal is an output with programmable frequencies of 13.5, 6.75 and 3.375 MHz. When the Aux port is configured as an input port, this signal is an input with a frequency based on the input transport stream data rate.

### GPIO24

### **Bidirectional**

This signal can also serve as a general-purpose I/O signal (GPIO24) by setting bit 3 in the General-Purpose Mode register.

### INIT/AUXPID[2]

### 1284 - Peripheral Initialization

In 1284 mode, this signal functions as INITn. When reset LOW, this signal resets the IEEE1284 port and returns the logic to the compatibility and idle state.

### L64118 MPEG-2 Transport Controller with Embedded MIPS CPU (TR4101) 39

### Bidirectional

### Bidirectional

Bidirectional

Input

### Aux - Packet ID [2]

### Output

In Aux mode, this signal is part of a three-bit packet ID that can be assigned to PIDs that are output to the Aux port.

### GPIO25

### Bidirectional

This signal can also serve as a general-purpose I/O signal (GPIO25) by setting bit 3 in the General-Purpose Mode register.

### PDATA[7:0] Parallel I/O Data Signals 1284 Bidir

### **Bidirectional**

In 1284 mode, these signals carry the data transferred between the host and the IEEE1284 port.

### Aux

### Bidirectional

In Aux mode, PDATA[7:0] carry the transport packets from/to the L64118 demultiplexer and the Aux port.

### GPIO[23:16]

### Bidirectional

Output

Input

Output

These signals can also serve as a general-purpose I/O bus (GPIO[23:16]) by setting bit 3 in the General-Purpose Mode register.

By default, this signal is not asserted after reset.

### PDATA\_DIR/OP\_MODE[2]

### 1284 - Peripheral Data Direction

After reset, this signal serves as the PDATA\_DIR output signal that controls the parallel data bus buffers in 1284 mode. In Aux mode, this pin is driven HIGH.

### **Operational Mode 2**

# This signal is used as a strap option during reset. For normal device operation, use a 10 $k\Omega$ to pull this signal LOW during reset.

### PERROR/AUXPID[0]

### 1284 - Peripheral Error

In 1284 mode, this signal functions as PERROR. When HIGH, this signal indicates that the L64118 IEEE1284 port encountered an error during the data processing. FAULTn is asserted whenever PERROR is activated.

### Aux - Packet ID [0]

signal (GPIO28) by setting bit 3 in the General-Purpose

In Aux mode, this signal is part of a three-bit packet ID that can be assigned to PIDs that are output to the Aux port.

### GPIO26

This signal can also serve as a general-purpose I/O signal (GPIO26) by setting bit 3 in the General-Purpose Mode register.

### SELECT/AUXPID[1]

### 1284 - Peripheral Select

When set HIGH, this signal indicates that the L64118 IEEE1284 port was selected and is connected to the host.

### Aux - Packet ID [1]

In Aux mode, this signal is part of a three-bit packet ID that can be assigned to PIDs that are output to the aux port.

### **GPI027**

### This signal can also serve as a general-purpose I/O signal (GPIO27) by setting bit 3 in the General-Purpose Mode register.

### SELECTINn/AUX ADP/AUX ERR

### 1284 - Peripheral Selection Indicator

In 1284 mode, this signal (when asserted LOW) indicates that the external host is attempting to select a peripheral.

### Aux - Adaptation Field Flag

In Aux output mode, this signal functions as AUX ADP, which indicates if the output byte is part of an adaptation field.

### Aux - Error Indicator

In Aux input mode, this signal functions as AUX ERR, which indicates if the incoming byte is part of a packet that has an error.

### GPIO28

Mode register.

### Bidirectional This signal can also serve as a general-purpose I/O

# Bidirectional

Output

# Output

### Output

Input

Input

# Bidirectional

Output

### STROBEn/AUX\_TX

### 1284 - Data Strobe

In 1284 mode, this signal functions as STROBEn. When set LOW, this signal indicates that valid data is present on PDATA[7:0]. L64118 latches the data on the rising edge of STROBEn.

### Aux - Aux Port Direction

In Aux mode, this signal is used to specify the direction of the aux port if the PINACT bit (bit 4) is set in the Aux Control register. If AUX\_TX is HIGH, then the Aux port is an output. If AUX\_TX is LOW, then the Aux port is an input.

### GPIO29

### Bidirectional

This signal can also serve as a general-purpose I/O signal (GPIO29) by setting bit 3 in the General-Purpose Mode register.

## I<sup>2</sup>C-Compatible Port

These signals connect the L64118 to an external  $I^2C$  device. The L64118 uses them to initialize external devices in the system that have this interface.

| SCL | <b>Serial Clock</b><br>SCL provides the clock signal for transmitt<br>receiving data through SDA.                                                                   | Bidirectional ting and |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| SDA | <b>Serial Data</b><br>SDA provides the data connection to the $I^2$ port. Data is transmitted and received thro<br>according to the $I^2$ C protocol. This signal s | ough this line         |

pulled HIGH by an external pull-up resistor.

### Input

# Input

### **Teletext Port**

These signals connect the L64118 to an external NTSC/PAL video encoder with a Teletext port.

### TTXDATA Teletext Data Master

### Output

This signal supplies the teletext data to the external video encoder. The L64118 outputs teletext data when TTXREQ is asserted and there are enough bits in the teletext output buffer to supply one complete teletext line. By default, this signal is not asserted after reset.

### GPIO13

### Bidirectional

Input

TTXDATA can serve as a general-purpose I/O signal (GPIO13) by setting bit 2 in the General-Purpose Mode register.

### TTXREQ Teletext Data Request Master

When set HIGH, this signal indicates that the external video encoder device requests teletext data to be transferred through TTXDATA. The L64118 outputs teletext data on the TTXDATA pin as long as TTXREQ is asserted. You must program the Video Encoder device so the length of assertion of TTXREQ is compatible with the exact number of teletext bits per line. The L64118 Teletext port supports a direct connection to the Teletext port of NTSC/PAL video encoders. During normal operation, this is an input signal. By default, this signal is not asserted after reset.

### GPIO12

### Bidirectional

TTXREQ can serve as a general-purpose I/O signal (GPIO12) by setting bit 2 in the General-Purpose Mode register.

### SmartCard Port

These signals provide the connection between the L64118 and external SmartCard devices. These signals are used by the L64118 to initialize external devices in a system with such a port. The L64118 supports two independent SmartCard devices.

- SC0 C4 SmartCard 0 Pin 4 Bidirectional This signal is connected to the C4 pin on the SmartCard. This signal should be pulled up by an external pull-up resistor after reset. SC0 C8 SmartCard 0 Pin 8 Bidirectional

- This signal is connected to the C8 pin on the SmartCard. This signal should be pulled up by an external pull-up resistor after reset.

- SC0 CLK SmartCard 0 Clock Output

### This signal is the output clock for SmartCard 0.

### GPIO33

SC0 CLK can serve as a general-purpose I/O signal (GPIO33) by setting bit 4 in the General-Purpose Mode register.

By default, this signal is not asserted after reset.

### SC0 DETECT

44

### SmartCard 0 Detect

### When HIGH, this signal indicates that a card is inserted in slot 0.

### GPIO31

### Bidirectional

Bidirectional

SC0 DETECT can serve as a general-purpose I/O signal (GPIO31) by setting bit 4 in the General-Purpose Mode register.

By default, this signal floats after reset.

### SC0 I/O SmartCard 0 I/O

This signal transfers data (using the coupler) between SmartCard 0 and the SmartCard port of the L64118. It is open-drain. This signal must be pulled up by an external resistor after reset.

### SC0 RSTn SmartCard 0 Reset

This signal resets SmartCard 0.

### **GPIO30**

SC0\_RSTn can serve as a general-purpose I/O signal (GPIO30) by setting bit 4 in the General-Purpose Mode register.

By default, this signal is not asserted after reset.

Input

### Output

Bidirectional

Bidirectional

### SC0 VCC ENn

### SmartCard 0 VCC Enable

This signal turns the power supply of SmartCard 0 on or off. When LOW, it enables the VCC supply.

### **GPIO32**

### Bidirectional

SC0 VCC ENn can serve as a general-purpose I/O signal (GPIO32) by setting bit 4 in the General-Purpose Mode register.

By default, this signal is not asserted after reset.

off. When LOW, it enables the VCC supply.

### SC0 VPP ENn

### This signal turns the power supply of SmartCard 0 on or

SmartCard 0 VPP Enable

### GPIO34

### **Bidirectional**

Output

SC0\_VPP\_ENn can serve as a general-purpose I/O signal (GPIO34) by setting bit 4 in the General-Purpose Mode register.

By default, this signal is not asserted after reset.

### SC1\_CLK SmartCard 1 Clock

This signal clocks the output of SmartCard1.

### GPIO38

### Bidirectional

SC1\_CLK can serve as a general-purpose I/O signal (GPIO38) by setting bit 5 in the General-Purpose Mode register.

By default, this signal is not asserted after reset.

### SC1 DETECT

### SmartCard 1 Detect

Input When HIGH, this signal indicates that a card is inserted in slot 1.

### GPIO36

### Bidirectional

SC1\_CLK can serve as a general-purpose I/O signal (GPIO36) by setting bit 5 in the General-Purpose Mode register.

By default, this signal floats after reset.

### Output

# Output

SC1 I/O SmartCard 1 I/O This signal transfers the data (using the coupler) between SmartCard1 and the SmartCard port of the L64118. It is open-drain. This signal must be pulled up by an external resistor after reset.

### SmartCard 1 Reset SC1 RSTn

This signal resets SmartCard1.

### GPIO35

SC1 RSTn can serve as a general-purpose I/O signal (GPIO35) by setting bit 5 in the General-Purpose Mode register.

By default, this signal is not asserted after reset.

### SC1 VCC ENn

### SmartCard 1 VCC Enable

Output This signal turns the power supply of SmartCard1 on or off. When LOW, it enables the VCC supply.

### GPIO37

# Bidirectional

SC1 VCC ENn can serve as a general-purpose I/O signal (GPIO37) by setting bit 5 in the General-Purpose Mode register.

By default, this signal is not asserted after reset.

### SC1\_VPP\_ENn

### SmartCard 1 VPP Enable

### This signal turns the power supply of SmartCard 0 on or off. When LOW, it enables the VPP pin.

**GPIO39** SC1\_VPP\_ENn can serve as a general-purpose I/O signal (GPIO39) by setting bit 4 in the General-Purpose Mode register.

By default, this signal is not asserted after reset.

### Bidirectional

### Bidirectional

Output

# Bidirectional

Output

### **Infrared Port**

These signals provide the connection between the L64118 and an external infrared receiver and transmitter.

| IRBL                | Infrared Blaster 0                                        | Dutput |

|---------------------|-----------------------------------------------------------|--------|

|                     | This signal is the infrared blaster output. This signated | al can |

|                     | be configured to reflect the value of the infrared        |        |

| transmitter output. |                                                           |        |

|                     |                                                           |        |

# **GPIO47**

**Bidirectional**

Input

IRBL can serve as a general-purpose I/O signal (GPIO47) by setting bit 7 in the General-Purpose Mode register.

By default, this signal floats after reset.

### IRRX0 Infrared Receiver 0

This signal serves as the receive port for the demodulated signal of one of the two infrared receivers ports.

### GPIO40

### Bidirectional IRRX0 can serve as a general-purpose I/O signal (GPIO40) by setting bit 7 in the General-Purpose Mode register.

By default, this signal floats after reset.

### IRRX1 Infrared Receiver 1 Input This signal serves as the receive port for the demodulated signal of one of the two infrared receivers ports.

### GPIO41

### Bidirectional

IRRX1 can serve as a general-purpose I/O signal (GPIO41) by setting bit 7 in the General-Purpose Mode register.

By default, this signal floats after reset.

### IRTX Infrared Transmitter

This signal serves as the infrared transmitter output.

### GPIO44

**Bidirectional**