# 8-BIT OTP/EPROM MCUs WITH A/D CONVERTER

- 3.0 to 6.0V Supply Operating Range

- 8 MHz Maximum Clock Frequency

- -40 to +85°C Operating Temperature Range

- Run, Wait and Stop Modes

- 5 Interrupt Vectors

- Look-up Table capability in OTP/EPROM

- Data OTP/EPROM: User selectable size (in program OTP/EPROM)

- Data RAM: 64 bytes

- 9 I/O pins, fully programmable as:

- Input with pull-up resistor

- Input without pull-up resistor

- Input with interrupt generation

- Open-drain or push-pull output

- Analog Input

- 3 I/O lines can sink up to 20mA to drive LEDs or TRIACs directly

- 8-bit Timer with 7-bit programmable prescaler

- Digital Watchdog

- 8-bit A/D Converter with 4 analog inputs

- On-chip Clock oscillator can be driven by Quartz crystal or Ceramic resonator

- Power-on Reset

- One external Non-Maskable Interrupt

- ST626x-EMU2 Emulation and Development System (connects to an MS-DOS PC via a parallel port).

## **DEVICE SUMMARY**

| DEVICE  | EPROM<br>(Bytes) | OTP<br>(Bytes) | I/O Pins |

|---------|------------------|----------------|----------|

| ST62T00 |                  | 1036           | 9        |

| ST62T01 |                  | 1836           | 9        |

| ST62E01 | 1836             |                | 9        |

# Table of Contents ———

| ST62T00/ST62T01, E01                               | 1      |

|----------------------------------------------------|--------|

| 1 GENERAL DESCRIPTION                              |        |

| 1.1 INTRODUCTION                                   | 5      |

| 1.2 PIN DESCRIPTIONS                               |        |

| 1.3 MEMORY MAPS                                    |        |

| 1.3.1Program Memory Maps                           | 7      |

| 1.3.2Data Space                                    | 7      |

| 1.4 PARTICULARITIES OF OTP AND EPROM DEVICES       |        |

| 1.4.1OTP/EPROM Programming                         | 8      |

| 1.4.2Eprom Erasure                                 | 8      |

| 2.1 INTRODUCTION                                   |        |

| 2.2 CPU REGISTERS                                  | o<br>O |

| 3 CLOCKS, RESET, INTERRUPTS AND POWER SAVING MODES | 9      |

| 3.1 CLOCK SYSTEM                                   |        |

| 3.2 RESETS                                         |        |

| 3.3 DIGITAL WATCHDOG                               | -      |

| 3.4 INTERRUPTS                                     |        |

| 3.5 POWER SAVING MODES                             | 9      |

| 4 ON-CHIP PERIPHERALS                              | 9      |

| 4.1 I/O PORTS                                      |        |

| 4.2 TIMER                                          | 9      |

| 4.3 A/D CONVERTER (ADC)                            | 9      |

| 5 SOFTWARE                                         | 9      |

| 5.1 ST6 ARCHITECTURE                               |        |

| 5.2 ADDRESSING MODES                               | 9      |

| 5.3 INSTRUCTION SET                                |        |

| 6 ELECTRICAL CHARACTERISTICS                       |        |

| 6.1 ABSOLUTE MAXIMUM RATINGS                       | 10     |

| 6.2 THERMAL CHARACTERISTICS 1                      |        |

| 6.3 RECOMMENDED OPERATING CONDITIONS               |        |

| 7 GENERAL INFORMATION                              |        |

| 7.1 PACKAGE MECHANICAL DATA 1                      | 12     |

# Table of Contents

| <b>ST62</b> | 00B, ST6201B                                    | 5        |

|-------------|-------------------------------------------------|----------|

| 1 GENE      | ERAL DESCRIPTION:                               | 16       |

|             | INTRODUCTION                                    |          |

| 1.2         | PIN DESCRIPTION                                 | 17       |

| 1.3         | MEMORY MAP                                      | 18       |

|             | 1.3.1 Introduction                              | 18       |

|             | 1.3.2 Program Space                             |          |

|             | 1.3.3 Data Space                                |          |

|             | 1.3.4 Stack Space                               |          |

|             | RAL PROCESSING UNIT                             |          |

|             | INTRODUCTION                                    |          |

|             | CPU REGISTERS                                   |          |

|             | CKS, RESET, INTERRUPTS AND POWER SAVING MODES   |          |

| 3.1         | CLOCK SYSTEM                                    | 24       |

|             | 3.1.1 Main Oscillator                           |          |

|             | 3.1.2 Low Frequency Auxiliary Oscillator (LFAO) | 25       |

| 2.2         | 3.1.3 Oscillator Safe Guard                     | 25       |

|             | RESETS                                          |          |

|             | 3.2.2 Power-on Reset                            |          |

|             | 3.2.3 Watchdog Reset                            |          |

|             | 3.2.4 Application Notes                         | 29       |

|             | 3.2.5 MCU Initialization Sequence               | 29       |

|             | DIGITAL WATCHDOG                                |          |

|             | 3.3.1 Digital Watchdog Register (DWDR)          |          |

|             | 3.3.2 Application Notes                         |          |

|             | 3.4.1 Interrupt Vectors                         |          |

|             | 3.4.2 Interrupt Priorities                      | 35<br>35 |

|             | 3.4.3 Interrupt Option Register (IOR)           | 37       |

|             | 3.4.4 External Interrupt Operating Modes        | 37       |

| 3.5         | 3.4.5 Interrupt Procedure                       |          |

| 5.5         | 3.5.1 WAIT Mode                                 |          |

|             | 3.5.2 STOP Mode                                 |          |

|             | 3.5.3 Exit from WAIT and STOP Modes             | .40      |

| 4 ON-C      | CHIP PERIPHERALS                                |          |

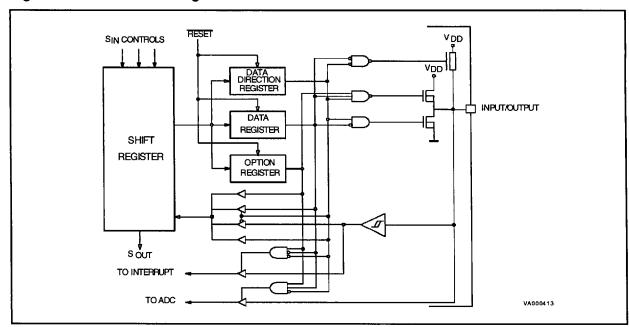

| 4.1         | I/O PORTS                                       | 41       |

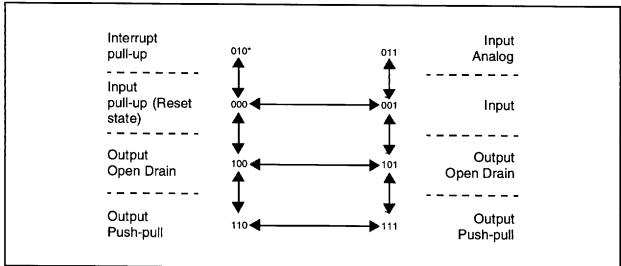

|             | 4.1.1 Operating Modes                           |          |

|             | 4.1.2 I/O Port Option Registers                 | .42      |

|             | 4.1.3 I/O Port Data Direction Registers         |          |

|             | 4.1.5 Safe I/O State Switching Sequence         | 42<br>42 |

|             |                                                 | 0        |

# Table of Contents —

| 4.2   | TIMER                                     | 45  |

|-------|-------------------------------------------|-----|

|       | 4.0.1 Timor Operation                     | 45  |

|       | 4.2.1 Timer Operation                     | 46  |

|       | 4.2.2 Timer Interrupt                     | 46  |

|       | 4.2.3 Application Notes                   | 46  |

|       | 4.2.4 Timer Registers                     | 47  |

| 4.3   | A/D CONVERTER (ADC)                       | 48  |

|       | 4.3.1 Application Notes                   |     |

| 5 SOF | TWARE                                     | 50  |

| 5.1   | ST6 ARCHITECTURE                          | 50  |

| 5.2   | ADDRESSING MODES                          | 50  |

| 5.3   | INSTRUCTION SET                           | 51  |

|       | CTRICAL CHARACTERISTICS                   |     |

| 6.1   | ABSOLUTE MAXIMUM RATINGS                  | .56 |

| 6.2   | THERMAL CHARACTERISTIC                    | 56  |

|       | RECOMMENDED OPERATING CONDITIONS          |     |

| 6.4   | READOUT PROTECTION FUSE                   | .59 |

|       | ERAL INFORMATION                          |     |

|       | PACKAGE MECHANICAL DATA                   |     |

|       | ORDERING INFORMATION                      |     |

|       |                                           |     |

|       | 7.2.1 Transfer of Customer Code           |     |

|       | 7.2.2 Listing Generation and Verification | 62  |

## 1 GENERAL DESCRIPTION

#### 1.1 INTRODUCTION

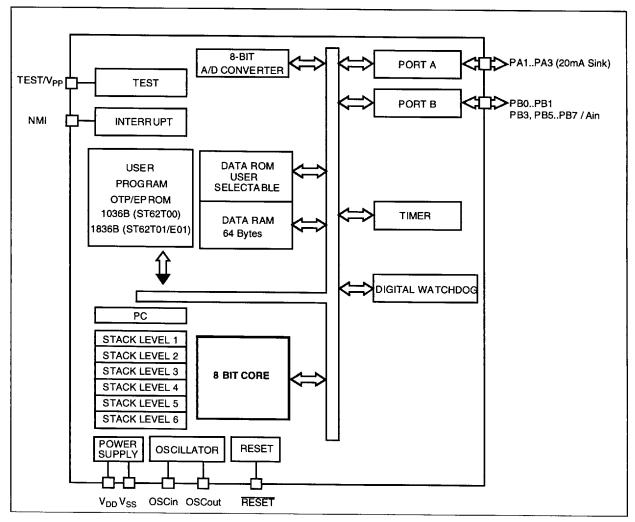

The ST62T00, T01 and E01 devices are low cost members of the 8-bit HCMOS ST62xx family of microcontrollers, which is targeted at low to medium complexity applications. All ST62xx devices are based on a building block approach: a common core is surrounded by a number of on-chip peripherals.

The ST62E01 device is an erasable EPROM version of the ST62T01 device, which may be used to emulate the T00 and T01, as well as the respective ST6200B and 01B ROM based devices.

OTP and EPROM devices are functionally identical. The ROM based versions offer the following additional features: RC Oscillator, Oscillator Safeguard, external Stop mode control, program code readout protection and the possibility of having an internal pullup on the NMI pin.

OTP devices offer all the advantages of user programmability at low cost, which make them the ideal choice in a wide range of applications where frequent code changes, multiple code versions or last minute programmability are required.

EPROM devices, thanks to their ease of erasure and reprogrammability, are best suited for program development and evaluation.

These compact low-cost devices feature a Timer comprising an 8-bit counter and a 7-bit programmable prescaler, an 8-bit A/D Converter with 4 analog inputs and a Digital Watchdog timer, making them well suited for a wide range of automotive, appliance and industrial applications.

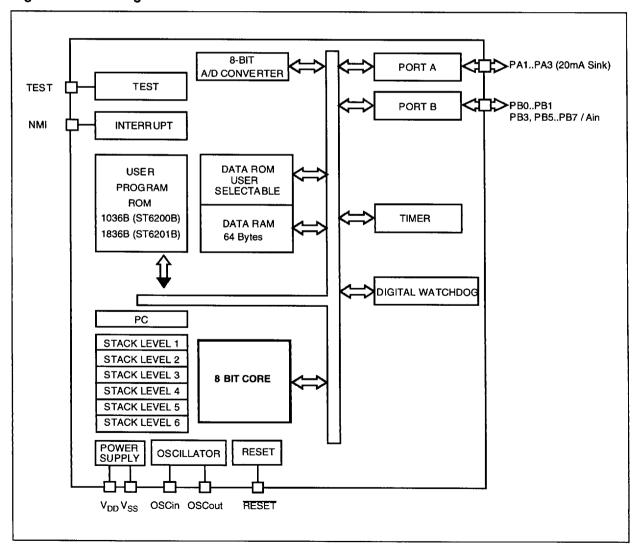

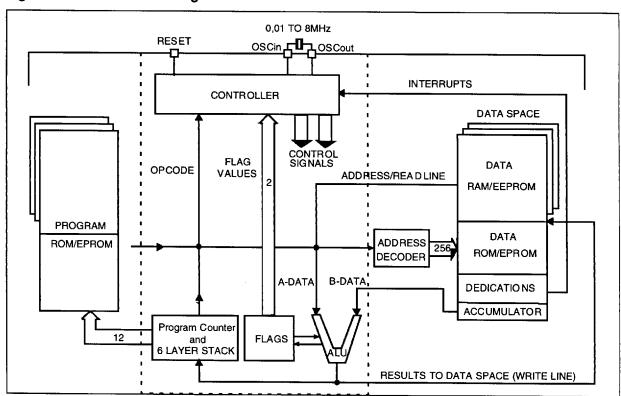

Figure 1. Block Diagram

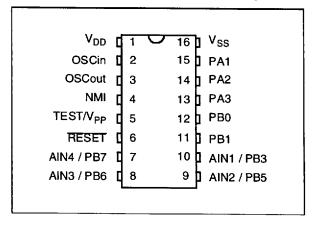

#### 1.2 PIN DESCRIPTIONS

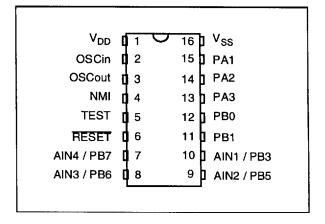

$V_{DD}$  and  $V_{SS}$ . Power is supplied to the MCU via these two pins.  $V_{DD}$  is the power connection and  $V_{SS}$  is the ground connection.

OSCin and OSCout. These pins are internally connected to the on-chip oscillator circuit. A quartz crystal, a ceramic resonator or an external clock signal can be connected between these two pins. The OSCin pin is the input pin, the OSCout pin is the output pin.

**RESET**. The active-low **RESET** pin is used to restart the microcontroller.

**TEST/Vpp.** This pin must be held at  $V_{SS}$  for normal operation (an internal 100lΩ pull-down resistor selects normal operating mode if the TEST pin is not connected externally). The OTP/EPROM programming mode is entered by connecting this pin to a 12.5V level during the Reset phase.

NMI. The NMI pin provides the capability for asynchronous interruption, by applying an external non maskable interrupt to the MCU. The NMI input is falling edge sensitive. A pull-up device must be provided externally on OTP and EPROM devices.

PA1-PA3. These 3 lines are organized as an I/O port (A). Each line may be configured under software control as an input with or without internal

pull-up resistors, as an interrupt generating input with pull-up resistors, or as an open-drain or push-pull output. PA1-PA3 can sink up to 20mA for direct LED drive capability.

PB0, PB1, PB3, PB5-PB7. These 6 lines are organized as one I/O port (B). Each line may be configured under software control as an input with or without internal pull-up, as an interrupt generating input with pull-up, or as an open-drain or push-pull output. PB5-PB7 and PB3 may also be used as analog inputs to the A/D converter.

Figure 2. ST62T00, T01, E01 Pin Configuration

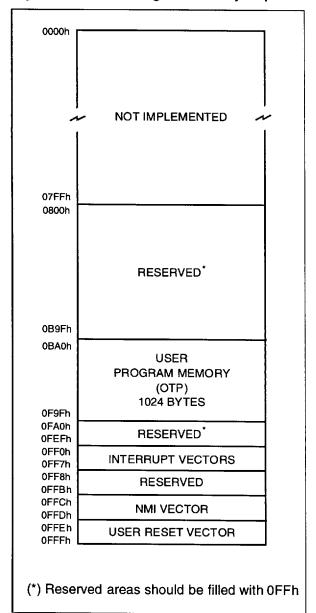

#### 1.3 MEMORY MAPS

## 1.3.1 Program Memory Maps

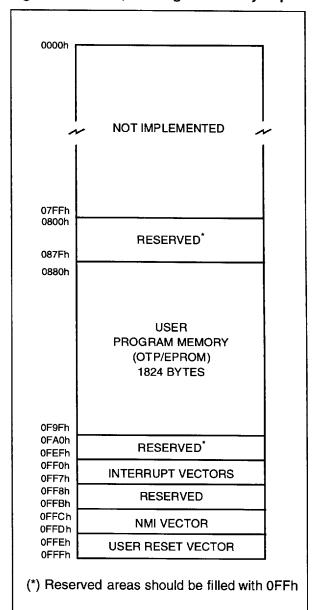

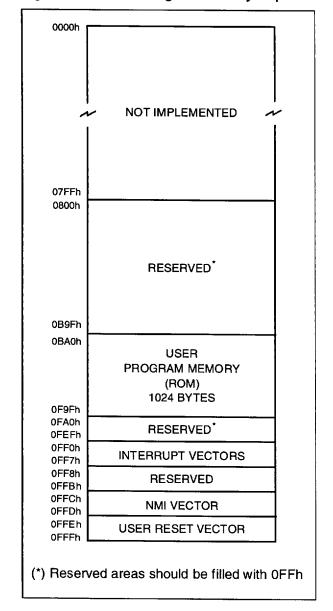

Figure 3. ST62T00 Program Memory Map

Figure 4. ST62T01,E01 Program Memory Map

## 1.3.2 Data Space

Data Space accommodates all the data necessary for processing the user program. This space comprises the RAM resource, the processor core and peripheral registers, as well as read-only data such as constants and look-up tables in OTP/EPROM.

The Data Space is fully described and illustrated on page 20.

## 1.4 PARTICULARITIES OF OTP AND EPROM DEVICES

OTP and EPROM devices are identical save for the package which, in the EPROM device, is fitted with a transparent window to allow erasure of memory contents by exposure to UV light.

Both OTP and EPROM parts may be programmed using programming equipment approved by SGS-THOMSON.

## 1.4.1 OTP/EPROM Programming

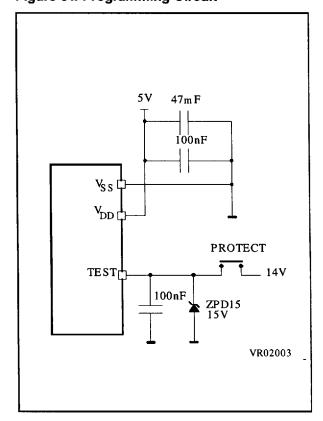

Programming mode is selected by applying a 12.5V voltage to the V<sub>PP</sub>/TEST pin during reset. Programming of OTP and EPROM parts is fully described in the EPROM Programming Board User Manual.

## 1.4.2 Eprom Erasure

Thanks to the transparent window present in the EPROM package, its memory contents may be erased by exposure to UV light.

Erasure begins when the device is exposed to light with a wavelength shorter than 4000Å. It should be noted that sunlight, as well as some types of artificial light, includes wavelengths in the 3000-4000Å range which, on prolonged exposure, can cause erasure of memory contents. It is thus recommended that EPROM devices be fitted with an opaque label over the window area in order to prevent unintentional erasure.

The recommended erasure procedure for EPROM devices consists of exposure to short wave UV light having a wavelength of 2537Å. The minimum recommended integrated dose (intensity x exposure time) for complete erasure is 15Wsec/cm². This is equivalent to an erasure time of 15-20 minutes using a UV source having an intensity of 12mW/cm² at a distance of 25mm (1 inch) from the device window.

## **2 CENTRAL PROCESSING UNIT**

#### 2.1 INTRODUCTION

The CPU Core may be thought of as an independent central processor communicating with on-chip I/O, memory and peripherals. For further details refer to page 16.

## 2.2 CPU REGISTERS

The CPU Core features six registers and three pairs of flags available to the programmer. For a detailed description refer topage 22.

## 3 CLOCKS, RESET, INTERRUPTS AND POWER SAVING MODES

#### 3.1 CLOCK SYSTEM

The Oscillator may be driven by an external clock, or by a crystal or ceramic resonator. ROM devices also offer RC oscillator and Oscillator Safeguard features. For a complete description refer topage 24.

#### 3.2 RESETS

The MCU can be reset in three ways: by the external Reset input being pulled low, by the Power-on Reset circuit, or by the Digital Watchdog timing out. For further details refer topage 28.

#### 3.3 DIGITAL WATCHDOG

The Digital Watchdog can be used to provide controlled recovery from software upsets. Software and Hardware enabled Watchdog options are available in order to achieve optimum trade-off between power consumption and noise immunity. For a complete description and a selection guide refer to page 31.

#### 3.4 INTERRUPTS

The CPU can manage four Maskable and one Non-Maskable Interrupt source. Each source is associated with a specific Interrupt Vector. An internal pullup option on the NMI pin is available on ROM devices. For a complete description refer to page 35.

#### 3.5 POWER SAVING MODES

WAIT mode reduces electrical consumption during idle periods, while STOP mode achieves the lowest power consumption by stopping all CPU activity. For a complete description refer topage 39

## 4 ON-CHIP PERIPHERALS

#### **4.1 I/O PORTS**

Input/Output lines may be individually programmed as one of a number of different configurations. For further details refer topage 41.

## **4.2 TIMER**

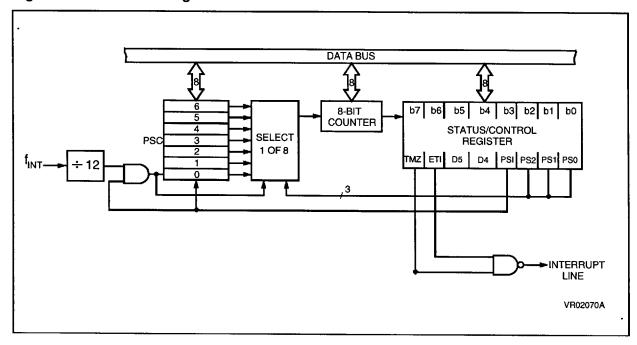

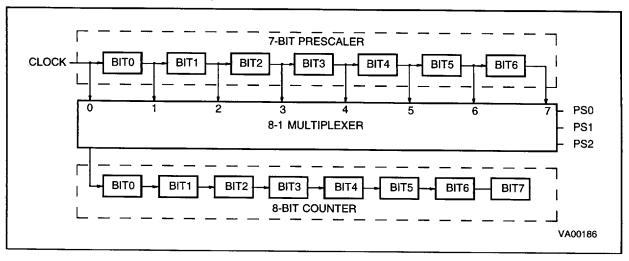

The on-chip Timer peripheral consists of an 8-bit counter with a 7-bit programmable prescaler, giving a maximum count of 2<sup>15</sup>. For a complete description refer to page 45.

## 4.3 A/D CONVERTER (ADC)

The 8-bit on-chip ADC features multiplexed analog inputs, as alternate I/O functions. Conversion is by successive approximations, with a typical conversion time of 70us, at 8MHz oscillator frequency. For a complete description refer topage 48

## **5 SOFTWARE**

#### **5.1 ST6 ARCHITECTURE**

The ST6 architecture has been designed to exploit the hardware in the most efficient way possible, while keeping byte usage to a minimum. For further details refer to page 50.

## 5.2 ADDRESSING MODES

The ST6 core offers nine addressing modes: Immediate, Direct, Short Direct, Extended, Program Counter Relative, Bit Direct, Bit Test & Branch, Indirect, and Inherent. For a complete description of the available addressing modes, refer topage 50.

#### **5.3 INSTRUCTION SET**

The ST6 core offers a set of 40 basic instructions which, when combined with nine addressing modes, yield 244 usable opcodes; these may be subdivided into six types: load/store, arithmetic/logic, conditional branch, control, jump/call, and bit manipulation. For further details refer to page 51.

## **6 ELECTRICAL CHARACTERISTICS**

## **6.1 ABSOLUTE MAXIMUM RATINGS**

This product contains devices designed to protect the inputs against damage due to high static voltages; however, it is advisable to take normal precautions to avoid applying voltages higher than the specified maximum ratings.

For proper operation, it is recommended that V and  $V_O$  be higher than  $V_{SS}$  and lower than  $V_{DD}$ . Reliability is enhanced if unused inputs are connected to an appropriate logic voltage level ( $V_{DD}$  or  $V_{SS}$ ).

**Power Considerations.** The average chip-junction temperature,  $T_j$ , in degrees Celsius can be obtained from:

$$T_j = T_A + P_D \times R_{thJA}$$

Where:

$T_A =$  Ambient Temperature.

R<sub>thJA</sub> =Package thermal resistance (junction-to ambient).

$P_D = P_{int} + P_{port}$

$P_{int} = I_{DD} \times V_{DD}$  (chip internal power).

P<sub>port</sub> =Port power dissipation (to be determined by the user)

| Symbol            | Parameter                                             | Value                                                         | Unit |  |

|-------------------|-------------------------------------------------------|---------------------------------------------------------------|------|--|

| V <sub>DD</sub>   | Supply Voltage                                        | -0.3 to 7.0                                                   | V    |  |

| V <sub>I</sub>    | Input Voltage                                         | V <sub>SS</sub> - 0.3 to V <sub>DD</sub> + 0.3 <sup>(1)</sup> | V    |  |

| Vo                | Output Voltage                                        | $V_{SS}$ - 0.3 to $V_{DD}$ + 0.3 <sup>(1)</sup>               | V    |  |

| V <sub>PP</sub>   | OTP/EPROM Programming Voltage                         | 13                                                            | V    |  |

| lo                | Current Drain per Pin Excluding VDD, VSS              | 10                                                            | mA   |  |

| I <sub>INJ+</sub> | Pin Injection current (positive), All I/O, VDD = 4.5V | +5                                                            | mA   |  |

| I <sub>INJ-</sub> | Pin Injection current (negative), All I/O, VDD = 4.5V | -5                                                            | mA   |  |

| IV <sub>DD</sub>  | Total Current into V <sub>DD</sub> (source)           | 50 <sup>(2)</sup>                                             | mA   |  |

| IV <sub>SS</sub>  | Total Current out of V <sub>SS</sub> (sink)           | 50 <sup>(2)</sup>                                             | mA   |  |

| T <sub>j</sub>    | Junction Temperature                                  | 150                                                           | °C   |  |

| T <sub>STG</sub>  | Storage Temperature                                   | -60 to 150                                                    | °C   |  |

#### Notes:

Stresses above those listed as "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device under these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

(1) Within these limits, clamping diodes are non-conducting. Voltages outside these limits are authorised provided injection current is kept within the specification.

(2) The total current through ports A and B combined may not exceed 50mA. If the application is designed with care and observing the limits stated above, total current may reach 50mA.

#### **6.2 THERMAL CHARACTERISTICS**

| Symbol            | Parameter                                | Test Conditions | Value |      |      |      |

|-------------------|------------------------------------------|-----------------|-------|------|------|------|

|                   | Latameter                                |                 | Min.  | Тур. | Max. | Unit |

| R <sub>thJA</sub> | T                                        | PDIP16          |       |      | 60   |      |

|                   | Thermal Resistance (junction to ambient) | PSO16           |       |      | 80   |      |

|                   | (Janouon to ambient)                     | CDIP16W         |       |      | n/a  |      |

## 6.3 RECOMMENDED OPERATING CONDITIONS

| Symbol            | Parameter                                                    | Test Conditions                      |            | Value |          |      |

|-------------------|--------------------------------------------------------------|--------------------------------------|------------|-------|----------|------|

|                   | i didilietei                                                 | rest Conditions                      | Min.       | Тур.  | Max.     | Unit |

| TA                | Operating Temperature                                        | 6 Suffix Version<br>1 Suffix Version | -40<br>· 0 |       | 85<br>70 | °C   |

| V <sub>DD</sub>   | Operating Supply Voltage                                     |                                      | 3.0V       |       | 6.0V     | V    |

| V <sub>PP</sub>   | Programming Voltage                                          |                                      | 12         | 12.5  | 13       | V    |

| I <sub>INJ+</sub> | Pin Injection Current (positive) Digital Input Analog Inputs | V <sub>DD</sub> = 4.5 to 5.5V        |            |       | +5       | mA   |

| I <sub>INJ-</sub> | Pin Injection Current (negative) Digital Input Analog Inputs | V <sub>DD</sub> = 4.5 to 5.5V        |            |       | -5       | mA   |

#### Notes:

If a total current of +1mA is flowing into a single analog channel, or if the total current flowing into all the analog inputs is 1mA, all resulting A/D conversions will be shifted by + 1 LSB. If a total positive current is flowing into a single analog channel, or if the total current flowing into all analog inputs is 5mA, all the resulting conversions are shifted by + 2 LSB.

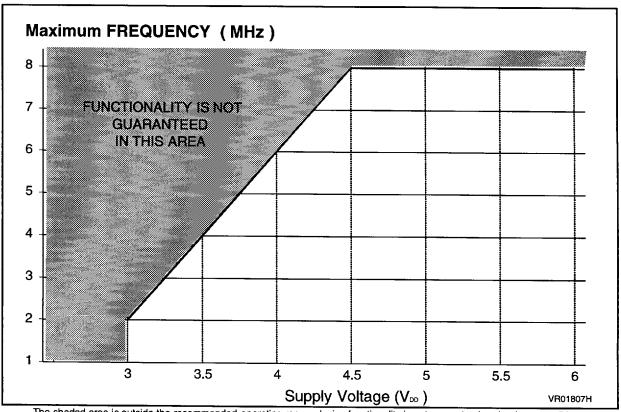

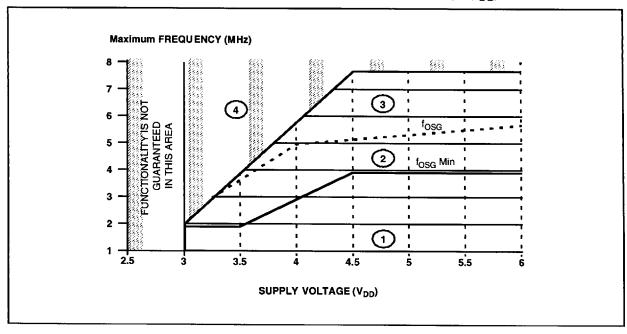

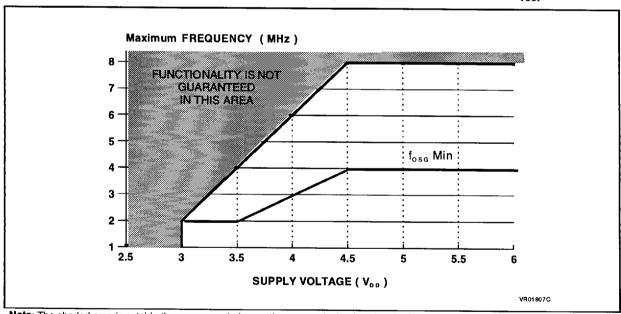

Figure 5. Maximum Operating FREQUENCY ( $f_{MAX}$ ) Versus SUPPLY VOLTAGE ( $V_{DD}$ )

The shaded area is outside the recommended operating range; device functionality is not guaranteed under these conditions.

## **7 GENERAL INFORMATION**

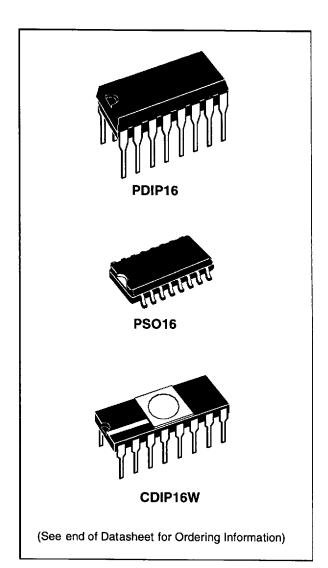

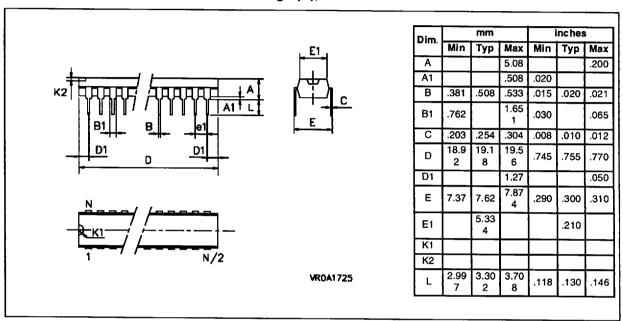

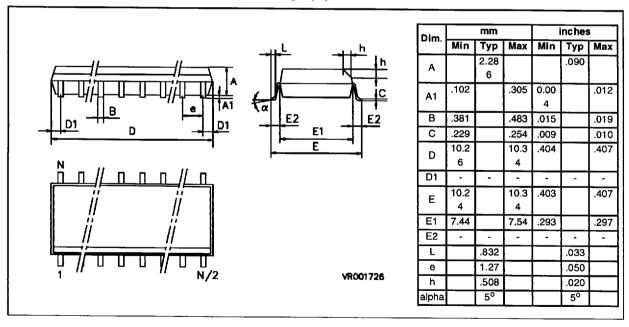

## 7.1 PACKAGE MECHANICAL DATA

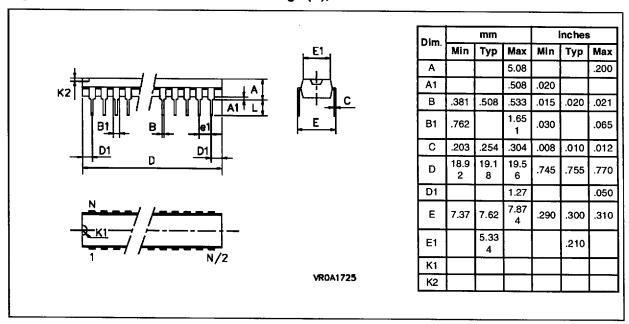

Figure 6. 16-Pin Plastic Dual In Line Package (B), 300-mil Width

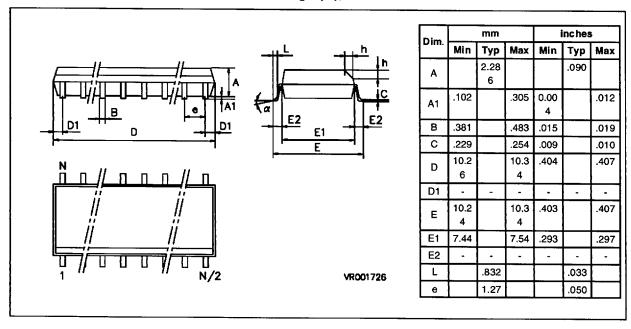

Figure 7. 16-Pin Plastic Small Outline Package (M), 300-mil Width

**Table 1. OTP Device Sales Types**

| Sales Type    | I/O Pins | Option            | Temperature range | Package |  |

|---------------|----------|-------------------|-------------------|---------|--|

| ST62T00B6/HWD | 9        | Hardware Watchdog |                   |         |  |

| ST62T00B6/SWD | 9        | Software Watchdog |                   | PDIP16  |  |

| ST62T00M6/HWD | 9        | Hardware Watchdog |                   | 20010   |  |

| ST62T00M6/SWD | 9        | Software Watchdog | 1                 | PSO16   |  |

| ST62T01B6/HWD | 9        | Hardware Watchdog | -40°C TO +85°C    |         |  |

| ST62T01B6/SWD | 9        | Software Watchdog |                   | PDIP16  |  |

| ST62T01M6/HWD | 9        | Hardware Watchdog |                   | 22212   |  |

| ST62T01M6/SWD | 9        | Software Watchdog |                   | PSO16   |  |

**Table 2. EPROM Device Sales Types**

| Sales Type    | I/O Pins | Option            | Temperature range | Package  |

|---------------|----------|-------------------|-------------------|----------|

| ST62E01F1/HWD | 9        | Hardware Watchdog | 0 TO +70°C        | 00104044 |

| ST62E01F1/SWD | 9        | Software Watchdog | 010+700           | CDIP16W  |

Notes:

577

## 8-BIT HCMOS MCUs WITH A/D CONVERTER

- 3.0 to 6.0V Supply Operating Range

- 8 MHz Maximum Clock Frequency

- -40 to +85°C Operating Temperature Range

- Run, Wait and Stop Modes

- 5 Interrupt Vectors

- Look-up Table capability in ROM

- Data ROM: User selectable size (in program ROM)

- Data RAM: 64 bytes

- ROM readout Protection

- PDIP16, PSO16 packages

- 9 I/O pins, fully programmable as:

- Input with pull-up resistor

- Input without pull-up resistor

- Input with interrupt generation

- Open-drain or push-pull output

- Analog Input

- 3 I/O lines can sink up to 20mA to drive LEDs or TRIACs directly

- 8-bit Timer with 7-bit programmable prescaler

- Digital Watchdog

- Oscillator Safe Guard

- 8-bit A/D Converter with 4 analog inputs

- On-chip Clock oscillator can be driven by Quartz crystal, Ceramic resonator or RC network

- Power-on Reset

- One external Non-Maskable Interrupt

- 9 powerful Addressing Modes

- ST626x-EMU2 Emulation and Development System (connects to an MS-DOS PC via a parallel port).

#### **DEVICE SUMMARY**

| DEVICE  | ROM<br>(Bytes) | I/O Pins |

|---------|----------------|----------|

| ST6200B | 1036           | 9        |

| ST6201B | 1836           | 9        |

## 1 GENERAL DESCRIPTION

#### 1.1 INTRODUCTION

The ST6200B and ST6201B microcontrollers are members of the ST62xx 8-bit HCMOS family of devices, which is targeted at low to medium complexity applications. All ST62xx devices are based on a building block approach: a common core is surrounded by a number of on-chip peripherals.

The ST6200B and ST6201B devices are functionally identical, save for their program memory size. The devices feature the following peripherals: a Timer comprising an 8-bit counter and a 7-bit programmable prescaler, an 8-bit A/D Converter with

4 analog inputs (A/D inputs are I/O pin alternate functions), and a Digital Watchdog timer.

The ST6200B and ST6201B devices feature a choice of Quartz, Ceramic or RC oscillators, an Oscillator Safe Guard circuit, Readout Protection against unauthorised copying of program code, and an External STOP Mode Control option to enlarge the range of power consumption versus reliability trade-offs.

These devices are well suited for automotive, appliance and industrial applications. The user programmable part for program development is the ST62E01.

Figure 1. Block Diagram

#### 1.2 PIN DESCRIPTION

${

m V_{DD}}$  and  ${

m V_{SS}}$ . Power is supplied to the MCU via these two pins.  ${

m V_{DD}}$  is the power connection and  ${

m V_{SS}}$  is the ground connection.

OSCin and OSCout. These pins are internally connected to the on-chip oscillator circuit. When the QUARTZ/CERAMIC RESONATOR Mask Option is selected, a quartz crystal, a ceramic resonator or an external clock signal can be connected between these two pins. When the RC OSCILLATOR Mask Option is selected, a resistor must be connected between the OSCout pin and ground. The OSCin pin is the input pin, the OSCout pin is the output pin.

**RESET.** The active-low RESET pin is used to restart the microcontroller.

**TEST.** The TEST pin must be held at  $V_{SS}$  for normal operation (an internal 100 $k\Omega$  pull-down resistor selects normal operating mode if the TEST pin is not connected externally).

NMI. The NMI pin provides the capability for asynchronous interruption, by applying an external non maskable interrupt to the MCU. The NMI is falling edge sensitive. A ROM mask option makes available an on-chip pull-up on the NMI pin.

PA1-PA3. These 3 lines are organized as an I/O port (A). Each line may be configured under software control as an input with or without internal pull-up resistors, as an interrupt generating input with pull-up resistors, or as an open-drain or push-pull output. PA1-PA3 can sink up to 20mA for di-

rect LED drive capability. When the External STOP Mode Control option is enabled, PA2 must be defined as an input.

PB0, PB1, PB3, PB5-PB7. These 6 lines are organized as one I/O port (B). When the External STOP Mode Control option is disabled, each line may be configured under software control as an input with or without internal pull-up resistor, as an interrupt generating input with pull-up resistor, or as an open-drain or push-pull output. PB7-PB5 and PB3 can also be used as analog inputs to the A/D converter. When the External STOP Mode Control option is enabled, PB0 can only be configured as open-drain in output mode (push-pull output is not available). The other lines are unchanged.

Figure 2 ST6200B and 01B Pin Configuration

#### 1.3 MEMORY MAP

#### 1.3.1 Introduction

The MCU operates in three separate memory spaces: Program space, Data space, and Stack space. Operation in these three memory spaces is described in the following paragraphs.

Briefly, Program space contains user program code in ROM and user vectors; Data space contains user data in RAM and in ROM, and Stack space accommodates six levels of stack for subroutine and interrupt service routine nesting.

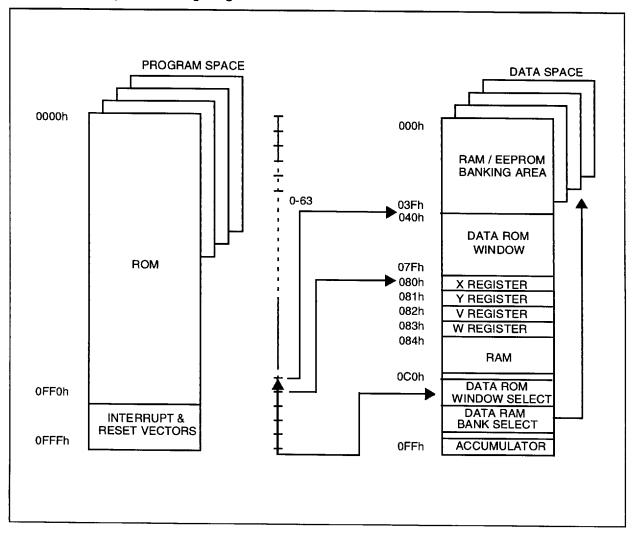

Figure 3. Memory Addressing Diagram

## **MEMORY MAP** (Cont'd)

## 1.3.2 Program Space

Program Space is physically implemented in ROM memory. It comprises the instructions to be executed, the data required for immediate addressing mode instructions, the reserved factory test area and the user vectors. Program Space is addressed via the 12-bit Program Counter register (PC register)

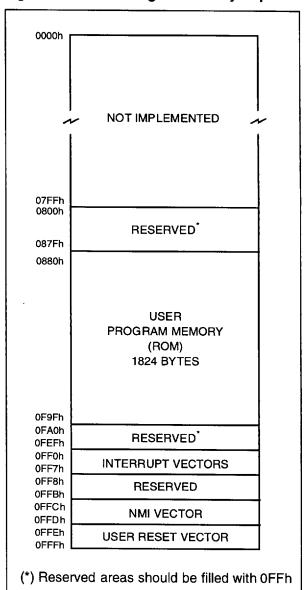

Figure 4. ST6200B Program Memory Map

#### 1.3.2.1 ROM Protection

The Program Space can be protected against external readout of ROM contents when the READ-OUTPROTECTION mask option is chosen. This option allows the user to blow a dedicated fuse on the silicon, by applying a high voltage at Vp (see detailed information in the "Electrical Specification").

Note: Once the Readout Protection fuse is blown, it is no longer possible, even for SGS-THOMSON, to gain access to the ROM contents. Returned parts with a blown fuse can therefore not be accepted.

Figure 5. ST6201B Program Memory Map

#### **MEMORY MAP** (Cont'd)

## 1.3.3 Data Space

Data Space accommodates all the data necessary for processing the user program. This space comprises the RAM resource, the processor core and peripheral registers, as well as read-only data such as constants and look-up tables in ROM.

#### 1.3.3.1 Data ROM

All read-only data is physically stored in ROM memory, which also accommodates the Program Space. The ROM memory consequently contains the program code to be executed, as well as the constants and look-up tables required by the application.

The Data Space locations in which the different constants and look-up tables are addressed by the processor core may be thought of as a 64-byte window through which it is possible to access the read-only data stored in ROM.

#### 1.3.3.2 Data RAM

The data space includes 60 bytes of RAM, the accumulator (A), the indirect registers (X), (Y), the short direct registers (V), (W), the I/O port registers, the peripheral data and control registers, the interrupt option register and the Data ROM Window register (DRW register).

## 1.3.4 Stack Space

Stack space consists of six 12-bit registers which are used to stack subroutine and interrupt return addresses, as well as the current program counter contents.

**Table 1. Data Memory Space**

| NOT IMPLEMENTED           |

|---------------------------|

| DATA ROM WINDOW           |

| 64 BYTES                  |

| X REGISTER                |

| Y REGISTER                |

| V REGISTER                |

| W REGISTER                |

| DATA RAM 60 BYTES         |

| PORT A DATA REGISTER      |

| PORT B DATA REGISTER      |

| RESERVED                  |

| RESERVED                  |

| PORT A DIRECTION REGISTER |

| PORT B DIRECTION REGISTER |

| RESERVED                  |

| RESERVED                  |

| INTERRUPT OPTION REGISTER |

| DATA ROM WINDOW REGISTER  |

| RESERVED                  |

| PORT A OPTION REGISTER    |

| PORT BOPTION REGISTER     |

| RESERVED                  |

| RESERVED                  |

| A/D DATA REGISTER         |

| A/D CONTROL REGISTER      |

| TIMER PSC REGISTER        |

| TIMER DATA REGISTER       |

| TIMER TSCR REGISTER       |

| RESERVED                  |

| WATCHDOG REGISTER         |

| RESERVED                  |

| ACCUMULATOR               |

| * WRITE ONLY DECISTED     |

<sup>\*</sup> WRITE ONLY REGISTER

000h 03Fh 040h 07Fh 080h 081h 082h 083h 084h 0BFh 0C0h 0C1h 0C2h 0C3h 0C4h 0C5h 0C6h 0C7h 0C8h\* 0C9h\* 0CAh 0CBh 0CCh 0CDh 0CEh 0CFh 0D0h 0D1h 0D2h 0D3h 0D4h 0D5h 0D7h 0D8h 0D9h 0FEh

0FFh

## MEMORY MAP (Cont'd)

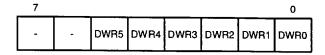

## 1.3.5 Data Window Register (DWR)

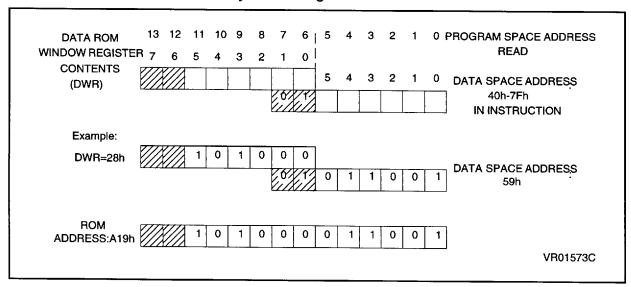

The Data ROM window is located from address 0040h to address 007Fh in Data space. It allows direct reading of 64 consecutive bytes located anywhere in ROM memory, between address 0000h and 1FFFh (top memory address depends on the specific device). All the ROM memory can therefore be used to store either instructions or readonly data. Indeed, the window can be moved in steps of 64 bytes along the ROM memory by writing the appropriate code in the Write-only Data Window register (DWR register, location 00C9h).

The DWR register can be addressed like any RAM location in the Data Space at address 00C9h, it is however a write-only register and cannot be accessed using single-bit operations. This register is used to move the 64-byte read-only data window (from address 40h to address 7Fh of the Data space) up and down the ROM memory of the MCU in steps of 64 bytes. The effective address of the byte to be read as data in ROM memory is obtained by concatenating the 6 least significant bits of the register address given in the instruction (as least significant bits) and the content of the DWR register (as most significant bits, seeFigure 6). So when addressing location 0040h of the Data Space, with 0 loaded in the DWR register, the physical location addressed in ROM is 00h. The DWR register is not cleared on reset, therefore it must be written to prior to the first access to the Data ROM window area.

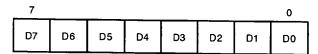

## **Data Window Register (DWR)**

Address: 0C9h — Write Only

Bit 7 = This bit is not used.

Bit 6-0 = **DWR6-DWR0:** Data ROM Window Register Bits. These are the Data ROM Window bits that correspond to the upper bits of the data ROM space.

Caution: This register is undefined on reset. Neither read nor single bit instructions may be used to address this register.

Note: Care is required when handling the DWR register as it is write only. For this reason, it is not allowed to change the DWR contents while executing interrupt service routine, as the service routine cannot save and then restore its previous content. If it is impossible to avoid the writing of this register in the interrupt service routine, an image of this register must be saved in a RAM location, and each time the program writes to the DWR it must write also to the image register. The image register must be written first, so if an interrupt occurs between the two instructions the DWR is not affected.

Figure 6. Data ROM Window Memory Addressing

## 2 CENTRAL PROCESSING UNIT

## 2.1 INTRODUCTION

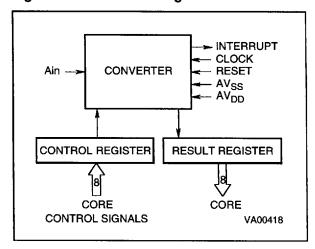

The CPU Core of ST6 devices is independent of the I/O or Memory configuration. As such, it may be thought of as an independent central processor communicating with on-chip I/O, Memory and Peripherals via internal address, data, and control buses. In-core communication is arranged as shown in Figure 7; the controller being externally linked to both the Reset and Oscillator circuits, while the core is linked to the dedicated on-chip peripherals via the serial data bus and indirectly, for interrupt purposes, through the control registers.

#### 2.2 CPU REGISTERS

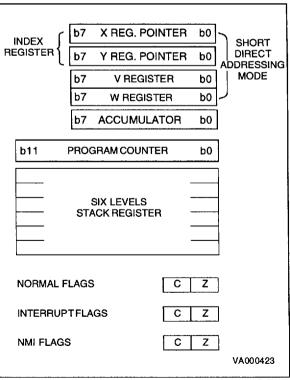

The ST6 Family CPU core features six registers and three pairs of flags available to the programmer. These are described in the following paragraphs.

Accumulator (A) The accumulator is an 8-bit general purpose register used in all arithmetic calculations, logical operations, and data manipulations. The accumulator can be addressed in Data space as a RAM location at address FFh. Thus the ST6 can manipulate the accumulator just like any other register in Data space.

Indirect Registers (X, Y). These two indirect registers are used as pointers to memory locations in Data space. They are used in the register-indirect addressing mode. These registers can be addressed in the data space as RAM locations at addresses 80h (X) and 81h (Y). They can also be accessed with the direct, short direct, or bit direct addressing modes. Accordingly, the ST6 instruction set can use the indirect registers as any other register of the data space.

Short Direct Registers (V, W). These two registers are used to save a byte in short direct addressing mode. They can be addressed in Data space as RAM locations at addresses 82h (V) and 83h (W). They can also be accessed using the direct and bit direct addressing modes. Thus, the ST6 instruction set can use the short direct registers as any other register of the data space.

Program Counter (PC). The program counter is a 12-bit register which contains the address of the next ROM location to be processed by the core. This ROM location may be an opcode, an operand, or the address of an operand. The 12-bit length allows the direct addressing of 4096 bytes in Program space.

Figure 7. ST6 Core Block Diagram

## **CPU REGISTERS** (Cont'd)

However, if the program space contains more than 4096 bytes, the additional memory in program space can be addressed by using the Program Bank Switch register.

The PC value is incremented after reading the address of the current instruction. To execute relative jumps, the PC and the offset are shifted through the ALU, where they are added; the result is then shifted back into the PC. The program counter can be changed in the following ways:

- JP (Jump) instructionPC=Jump address

- CALL instructionPC= Call address

- Relative Branch InstructionPC= PC +/- offset

- Interrupt PC=Interrupt vector

- ResetPC= Reset vector

- RET & RETI instructionsPC= Pop (stack)

- Normal instructionPC= PC + 1

Flags (C, Z). The ST6 CPU includes three pairs of flags (Carry and Zero), each pair being associated with one of the three normal modes of operation: Normal mode, Interrupt mode and Non Maskable Interrupt mode. Each pair consists of a CARRY flag and a ZERO flag. One pair (CN, ZN) is used during Normal operation, another pair is used during Interrupt mode (CI, ZI), and a third pair is used in the Non Maskable Interrupt mode (CNMI, ZN-MI).

The ST6 CPU uses the pair of flags associated with the current mode: as soon as an interrupt (or a Non Maskable Interrupt) is generated, the ST6 CPU uses the Interrupt flags (resp. the NMI flags) instead of the Normal flags. When the RETI instruction is executed, the previously used set of flags is restored. It should be noted that each flag set can only be addressed in its own context (Non Maskable Interrupt, Normal Interrupt or Main routine). The flags are not cleared during context switching and thus retain their status.

The Carry flag is set when a carry or a borrow occurs during arithmetic operations; otherwise it is cleared. The Carry flag is also set to the value of the bit tested in a bit test instruction; it also participates in the rotate left instruction.

The Zero flag is set if the result of the last arithmetic or logical operation was equal to zero; otherwise it is cleared.

Switching between the three sets of flags is performed automatically when an NMI, an interrupt or a RETI instructions occurs. As the NMI mode is automatically selected after the reset of the MCU, the ST6 core uses at first the NMI flags.

Stack. The ST6 CPU includes a true LIFO hardware stack which eliminates the need for a stack pointer. The stack consists of six separate 12-bit RAM locations that do not belong to the data space RAM area. When a subroutine call (or interrupt request) occurs, the contents of each level are shifted into the next higher level, while the content of the PC is shifted into the first level (the original contents of the sixth stack level are lost). When a subroutine or interrupt return occurs (RET or RETI instructions), the first level register is shifted back into the PC and the value of each level is popped back into the previous level. Since the accumulator, in common with all other data space registers, is not stored in this stack, management of these registers should be performed within the subroutine. The stack will remain in its "deepest" position if more than 6 nested calls or interrupts are executed, and consequently the last return address will be lost. It will also remain in its highest position if the stack is empty and a RET or RETI is executed. In this case the next instruction will be executed.

Figure 8. ST6 CPU Programming Mode

ST6CPU.FM

## 3 CLOCKS, RESET, INTERRUPTS AND POWER SAVING MODES

#### 3.1 CLOCK SYSTEM

The MCU features a Main Oscillator which can be driven by an external clock, or used in conjunction with an AT-cut parallel resonant crystal or a suitable ceramic resonator, or with an external resistor (R<sub>NET</sub>). In addition, a Low Frequency Auxiliary Oscillator (LFAO) can be switched in for security reasons, to reduce power consumption, or to offer the benefits of a back-up clock system.

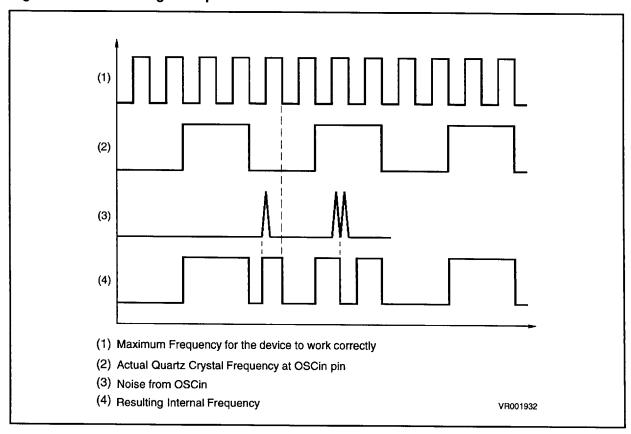

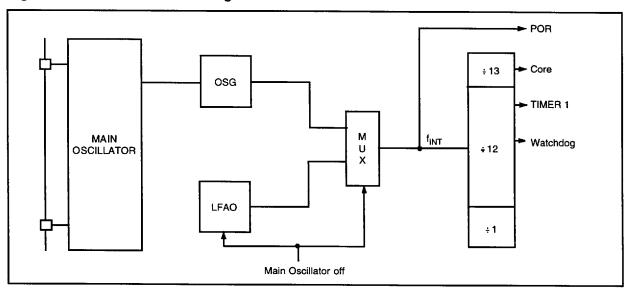

The Oscillator Safeguard (OSG) option filters spikes from the oscillator lines, provides access to the LFAO to provide a backup oscillator in the event of main oscillator failure and also automatically limits the internal clock frequency ( $f_{NT}$ ) as a function of  $V_{DD}$ , in order to guarantee correct operation. These functions are illustrated in Figure 10, Figure 11, Figure 12 and Figure 13.

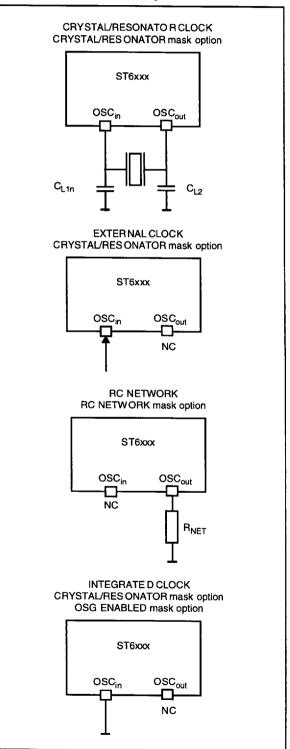

Figure 9 illustrates various possible oscillator configurations using an external crystal or ceramic resonator, an external clock input, an external resistor ( $R_{NET}$ ), or the lowest cost solution using only the LFAO.  $C_{L1}$  an  $C_{L2}$  should have a capacitance in the range 12 to 22 pF for an oscillator frequency in the 4-8 MHz range.

The internal MCU clock frequency ( $f_{NT}$ ) is divided by 12 to drive the Timer, the A/D converter and the Watchdog timer, and by 13 to drive the CPU core, as may be seen in Figure 12.

With an 8MHz oscillator frequency, the fastest machine cycle is therefore 1.625µs.

A machine cycle is the smallest unit of time needed to execute any operation (for instance, to increment the Program Counter). An instruction may require two, four, or five machine cycles for execution.

#### 3.1.1 Main Oscillator

The oscillator configuration may be specified by selecting the appropriate mask option. When the CRYSTAL/RESONATOR option is selected, it must be used with a quartz crystal, a ceramic resonator or an external signal provided on the OSCin pin. When the RCNETWORK option is selected, the system clock is generated by an external resistor.

The main oscillator can be turned off (when the OSG ENABLED mask option is selected) by setting the OSCOFF bit of the ADC Control Register. The Low Frequency Auxiliary Oscillator is automatically started.

Figure 9. Oscillator Configurations

## **CLOCK SYSTEM** (Cont'd)

Turning on the main oscillator is achieved by resetting the OSCOFF bit of the A/D Converter Control Register or by resetting the MCU. Restarting the main oscillator implies a delay comprising the oscillator start up delay period plus the duration of the software instruction at £FAO clock frequency.

# 3.1.2 Low Frequency Auxiliary Oscillator (LFAO)

The Low Frequency Auxiliary Oscillator has three main purposes. Firstly, it can be used to reduce power consumption in non timing critical routines. Secondly, it offers a fully integrated system clock, without any external components. Lastly, it acts as a safety oscillator in case of main oscillator failure.

This oscillator is available when the OSG ENA-BLED mask option is selected. In this case, it automatically starts one of its periods after the first missing edge from the main oscillator, whatever the reason (main oscillator defective, no clock circuitry provided, main oscillator switched off...).

User code, normal interrupts, WAIT and STOP instructions, are processed as normal, at the reduced f<sub>LFAO</sub> frequency. The A/D converter accuracy is decreased, since the internal frequency is below 1MHz.

At power on, the Low Frequency Auxiliary Oscillator starts faster than the Main Oscillator. It therefore feeds the on-chip counter generating the POR delay until the Main Oscillator runs.

The Low Frequency Auxiliary Oscillator is automatically switched off as soon as the main oscillator starts.

#### **ADCR**

Address: 0D1h — Read/Write

| 7         |           |           |           |           |            | 0         |

|-----------|-----------|-----------|-----------|-----------|------------|-----------|

| ADCR<br>7 | ADCR<br>6 | ADCR<br>5 | ADCR<br>4 | ADCR<br>3 | OSC<br>OFF | ADCR<br>0 |

Bit 7-3, 1-0= ADCR7-ADCR3, ADCR1-ADCR0 ADC Control Register. These bits are not used.

Bit 2 = **OSCOFF**. When low, this bit enables main oscillator to run. The main oscillator is switched off when OSCOFF is high.

## 3.1.3 Oscillator Safe Guard

The Oscillator Safe Guard (OSG) affords drastically increased operational integrity in ST62xx devices. The OSG circuit provides three basic functions: it filters spikes from the oscillator lines which would result in over frequency to the ST62 CPU; it gives access to the Low Frequency Auxiliary Oscillator (LFAO), used to ensure minimum processing in case of main oscillator failure, to offer reduced power consumption or to provide a fixed frequency low cost oscillator; finally, it automatically limits the internal clock frequency as a function of supply voltage, in order to ensure correct operation even if the power supply should drop.

The OSG is enabled or disabled by choosing the relevant OSG mask option. It may be viewed as a filter whose cross-over frequency is device dependent.

Spikes on the oscillator lines result in an effectively increased internal clock frequency. In the absence of an OSG circuit, this may lead to an over frequency for a given power supply voltage. The OSG filters out such spikes (as illustrated in Figure 10). In all cases, when the OSG is active, the maximum internal clock frequency,  $f_{NT}$ , is limited to  $f_{OSG}$ , which is supply voltage dependent. This relationship is illustrated in Figure 13.

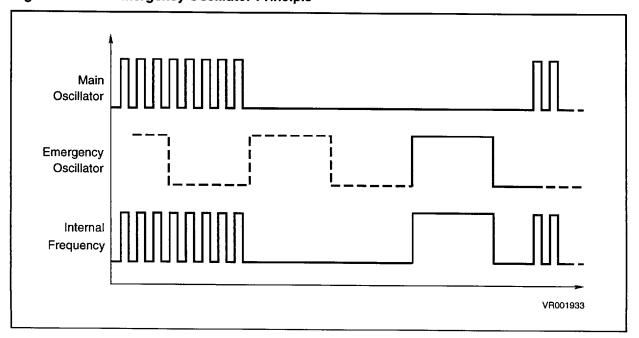

When the OSG is enabled, the Low Frequency Auxiliary Oscillator may be accessed. This oscillator starts operating after the first missing edge of the main oscillator (see Figure 11).

Over-frequency, at a given power supply level, is seen by the OSG as spikes; it therefore filters out some cycles in order that the internal clock frequency of the device is kept within the range the particular device can stand (depending on  $V_{DD}$ ), and below  $f_{OSG}$ : the maximum authorised frequency with OSG enabled.

**Note.** The OSG should be used wherever possible as it provides maximum safety. Care must be taken, however, as it can increase power consumption and reduce the maximum operating frequency to fosg.

## **CLOCK SYSTEM** (Cont'd)

Figure 10. OSG Filtering Principle

Figure 11. OSG Emergency Oscillator Principle

26/62

7929237 0079940 914

## **CLOCK SYSTEM (Cont'd)**

Figure 12. Clock Circuit Block Diagram

Figure 13. Maximum Operating Frequency ( $f_{MAX}$ ) versus Supply Voltage ( $V_{DD}$ )

#### Notes:

- 1. In this area, operation is guaranteed at the quartz crystal frequency.

- 2. When the OSG is disabled, operation in this area is guaranteed at the crystal frequency. When the OSG is enabled, operation in this area is guaranteed at a frequency of at least fosg Min.

- 3. When the OSG is disabled, operation in this area is guaranteed at the quartz crystal frequency. When the OSG is enabled, access to this area is prevented. The internal frequency is kept a fosg.

- 4. When the OSG is disabled, operation in this area is not guaranteed When the OSG is enabled, access to this area is prevented. The internal frequency is kept at fosc.

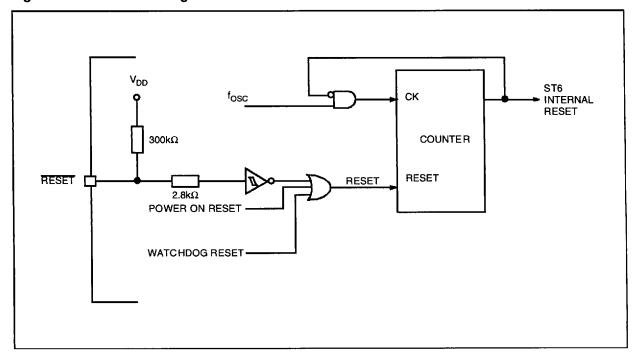

#### 3.2 RESETS

The MCU can be reset in three ways:

- by the external Reset input being pulled low;

- by Power-on Reset;

- by the digital Watchdog peripheral timing out.

## 3.2.1 RESET Input

The RESET pin may be connected to a device of the application board in order to reset the MCU if required. The RESET pin may be pulled low in RUN, WAIT or STOP mode. This input can be used to reset the MCU internal state and ensure a correct start-up procedure. The pin is active low and features a Schmitt trigger input. The internal Reset signal is generated by adding a delay to the external signal. Therefore even short pulses on the RESET pin are acceptable, provided V<sub>DD</sub> has completed its rising phase and that the oscillator is running correctly (normal RUN or WAIT modes). The MCU is kept in the Reset state as long as the RESET pin is held low.

If RESET activation occurs in the RUN or WAIT modes, processing of the user program is stopped (RUN mode only), the Inputs and Outputs are configured as inputs with pull-up resistors and the main Oscillator is restarted. When the level on the RESET pin then goes high, the initialization sequence is executed following expiry of the internal delay period.

If RESET pin activation occurs in the STOP mode, the oscillator starts up and all Inputs and Outputs are configured as inputs with pull-up resistors. When the level of the RESET pin then goes high, the initialization sequence is executed following expiry of the internal delay period.

#### 3.2.2 Power-on Reset

The function of the POR circuit consists in waking up the MCU at an appropriate stage during the power-on sequence. At the beginning of this sequence, the MCU is configured in the Reset state: all I/O ports are configured as inputs with pull-up resistors and no instruction is executed. When the power supply voltage rises to a sufficient level, the oscillator starts to operate, whereupon an internal delay is initiated, in order to allow the oscillator to fully stabilize before executing the first instruction. The initialization sequence is executed immediately following the internal delay.

The internal delay is generated by an on-chip counter. The internal reset line is released 2048 internal clock cycles after release of the external reset.

#### Notes:

To ensure correct start-up, the user should take care that the reset signal is not released before the  $V_{DD}$  level is sufficient to allow MCU operation at the chosen frequency (see Recommended Operating Conditions).

A proper reset signal for a slow rising  $V_{DD}$  supply can generally be provided by an external RC network connected to the RESET pin.

Figure 14. Reset and Interrupt Processing

## **RESETS** (Cont'd)

## 3.2.3 Watchdog Reset

The MCU provides a Watchdog timer function in order to ensure graceful recovery from software upsets. If the Watchdog register is not refreshed before an end-of-count condition is reached, the internal reset will be activated. This, amongst other things, resets the watchdog counter.

The MCU restarts just as though the Reset had been generated by the RESET pin, including the built-in stabilisation delay period.

## 3.2.4 Application Notes

No external resistor is required between  $V_{DD}$  and the Reset pin, thanks to the built-in pull-up device.

The POR circuit operates dynamically, in that it triggers MCU initialization on detecting the rising edge of  $V_{DD}$ . The typical threshold is in the region of 2 volts, but the actual value of the detected threshold depends on the way in which  $V_{DD}$  rises.

The POR circuit is NOT designed to supervise static, or slowly rising or falling  $V_{DD}$ .

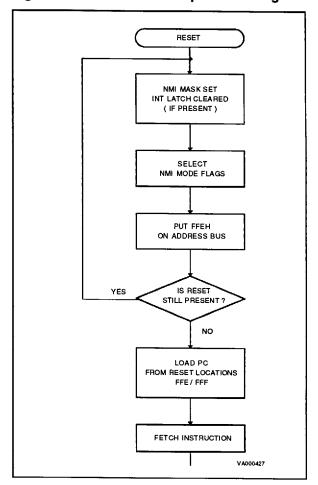

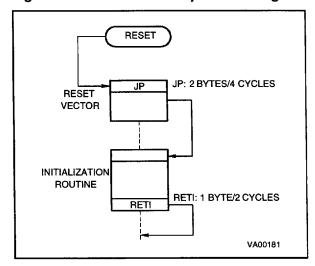

## 3.2.5 MCU Initialization Sequence

When a reset occurs the stack is reset, the PC is loaded with the address of the Reset Vector (located in program ROM starting at address 0FFEh). A jump to the beginning of the user program must be coded at this address. Following a Reset, the Interrupt flag is automatically set, so

that the CPU is in Non Maskable Interrupt mode; this prevents the initialisation routine from being interrupted. The initialisation routine should therefore be terminated by a RETI instruction, in order to revert to normal mode and enable interrupts. If no pending interrupt is present at the end of the initialisation routine, the MCU will continue by processing the instruction immediately following the RETI instruction. If, however, a pending interrupt is present, it will be serviced.

Figure 15. Reset and Interrupt Processing

Figure 16. Reset Block Diagram

## RESETS (Cont'd)

**Table 2. Register Reset Status**

| Register                                                                                                                                   | Address(es)                                                  | Status            | Comment                                                                                               |  |

|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------|--|

| Port Data Registers (PA, PB) Port Direction Register (PA, PB) Port Option Register (PA, PB) Interrupt Option Register Timer Status/Control | 0C0h to 0C1h<br>0C4h to 0C5h<br>0CCh to 0CDh<br>0C8h<br>0D4h | 00h               | I/Os are Inputs with pull-up<br>I/Os are Inputs with pull-up<br>Interrupts disabled<br>Timer disabled |  |

| X, Y, V, W Register<br>Accumulator<br>Data RAM<br>Data ROM Window Register<br>A/D Result Register                                          | 080h to 083h<br>0FFh<br>084h to 0BFh<br>0C9h<br>0D0h         | Undefined         |                                                                                                       |  |

| Timer Counter Register Timer Prescaler Register Watchdog Counter Register                                                                  | 0D3h<br>0D2h<br>0D8h                                         | FFh<br>7Fh<br>FEh | Maximum count loaded                                                                                  |  |

| A/D Control Register                                                                                                                       | 0D1h                                                         | <b>40</b> h       | A/D in Stand-by, main oscillator on                                                                   |  |

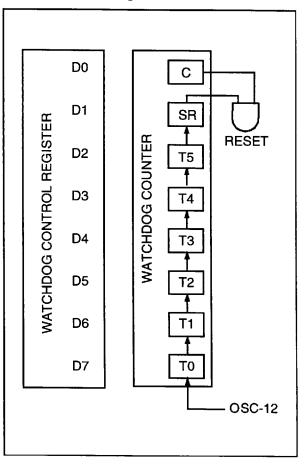

#### 3.3 DIGITAL WATCHDOG

The digital Watchdog consists of a reloadable downcounter timer which can be used to provide controlled recovery from software upsets.

The Watchdog circuit generates a Reset when the downcounter reaches zero. User software can prevent this reset by reloading the counter, and should therefore be written so that the counter is regularly reloaded while the user program runs correctly. In the event of a software mishap (usually caused by externally generated interference), the user program will no longer behave in its usual fashion and the timer register will thus not be reloaded periodically. Consequently the timer will decrement down to 00h and reset the MCU. In order to maximise the effectiveness of the Watchdog function, user software must be written with this concept in mind.

Watchdog behaviour is governed by two mask options, known as "WATCHDOG ACTIVATION" (i.e. HARDWARE or SOFTWARE) and "EXTERNAL STOP MODE CONTROL" (see Table 3).

In the SOFTWARE mask option, the Watchdog is disabled until bit C of the DWDR register has been set. When the Watchdog is disabled, low power Stop mode is available. Once activated, the Watchdog cannot be disabled, save by resetting the MCU.

In the HARDWARE mask option, the Watchdog is permanently enabled. Since the oscillator will run continuously, low power mode is not available. The STOP instruction is interpreted as a WAIT instruction, and the Watchdog continues to countdown.

However, when the EXTERNAL STOP MODE CONTROL mask option (available in ROM versions only) has been selected low power consumption may be achieved in Stop Mode.

Execution of the STOP instruction is then governed by a secondary function associated with the NMI pin. If a STOP instruction is encountered when the NMI pin is low, it is interpreted as WAIT, as described above. If, however, the STOP instruction is encountered when the NMI pin is high, the Watchdog counter is frozen and the CPU enters STOP mode.

When the MCU exits STOP mode (i.e. when an interrupt is generated), the Watchdog resumes its activity.

**Note**: when the EXTERNAL STOP MODE CONTROL mask option has been selected, port PB0 must be defined as an open-drain output, and PA2 as an input.

**Table 3. Recommended Mask Option Choices**

| Functions Required   | Recommended Mask Options                   |  |  |

|----------------------|--------------------------------------------|--|--|

| Stop Mode & Watchdog | "EXTERNAL STOP MODE" & "HARDWARE WATCHDOG" |  |  |

| Stop Mode            | "SOFTWARE WATCHDOG"                        |  |  |

| Watchdog             | "HARDWARE WATCHDOG"                        |  |  |

## **DIGITAL WATCHDOG** (Cont'd)

The Watchdog is associated with a Data space register (Digital WatchDog Register, DWDR, location 0D8h) which is described in greater detail in Section 3.3.1. This register is set to 0FEh on Reset: bit C is cleared to "0", which disables the Watchdog; the timer downcounter bits, T0 to T5, and the SR bit are all set to "1", thus selecting the longest Watchdog timer period. This time period can be set to the user's requirements by setting the appropriate value for bits T0 to T5 in the DWDR register. The SR bit must be set to "1", since it is this bit which generates the Reset signal when it changes to "0"; clearing this bit would generate an immediate Reset.

It should be noted that the order of the bits in the DWDR register is inverted with respect to the associated bits in the down counter: bit 7 of the DWDR register corresponds, in fact, to T0 and bit 2 to T5. The user should bear in mind the fact that these bits are inverted and shifted with respect to the physical counter bits when writing to this register. The relationship between the DWDR register bits and the physical implementation of the Watchdog timer downcounter is illustrated in Figure 17.

Only the 6 most significant bits may be used to define the time period, since it is bit 6 which triggers the Reset when it changes to "0". This offers the user a choice of 64 timed periods ranging from 3,072 to 196,608 clock cycles (with an oscillator frequency of 8MHz, this is equivalent to timer periods ranging from 384µs to 24.576ms).

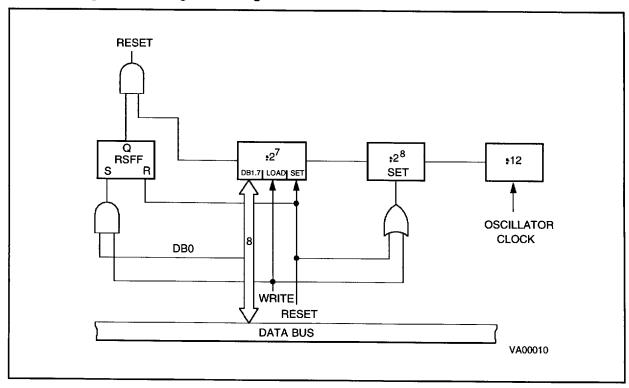

**Figure 17. Watchdog Counter Control**

## **DIGITAL WATCHDOG** (Cont'd)

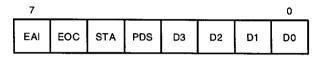

## 3.3.1 Digital Watchdog Register (DWDR)

Address: 0D8h — Read/Write

Reset status: 1111 1110b

| 7  |    |    |    |    | •  |    | 0 |

|----|----|----|----|----|----|----|---|

| ТО | T1 | T2 | Т3 | T4 | T5 | SR | С |

Bit 0 = C: Watchdog Control bit

If the hardware option is selected, this bit is forced high and the user cannot change it (the Watchdog is always active). When the software option is selected, the Watchdog function is activated by setting bit C to 1, and cannot then be disabled (save by resetting the MCU).

When C is kept low the counter can be used as a 7-bit timer.

This bit is cleared to "0" on Reset.

Bit 1 = SR: Software Reset bit

This bit triggers a Reset when cleared.

When C = "0" (Watchdog disabled) it is the MSB of the 7-bit timer.

This bit is set to "1" on Reset.

Bits 2-7 = T5-T0: Downcounter bits

It should be noted that the register bits are reversed and shifted with respect to the physical counter: bit-7 (T0) is the LSB of the Watchdog downcounter and bit-2 (T5) is the MSB.

These bits are set to "1" on Reset.

## 3.3.2 Application Notes

The Watchdog plays an important supporting role in the high noise immunity of ST62xx devices, and should be used wherever possible. Watchdog related options should be selected on the basis of a trade-off between application security and STOP mode availability.

When STOP mode is not required, hardware activation without EXTERNAL STOP MODE CONTROL should be preferred, as it provides maximum security, especially during power-on.

When STOP mode is required, hardware activation and EXTERNAL STOP MODE CONTROL should be chosen. NMI should be high by default, to allow STOP mode to be entered when the MCU is idle.

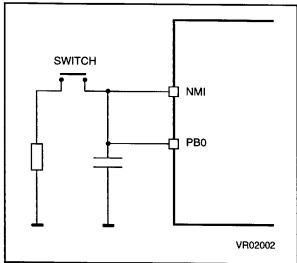

The NMI pin can be connected to PB0 (seeFigure 18) to allow its state to be controlled by software. PB0 can then be used to keep NMI low while Watchdog protection is required, or to avoid noise or key bounce. When no more processing is required, PB0 is released and the device placed in STOP mode for lowest power consumption.

When software activation is selected and the Watchdog is not activated, the downcounter may be used as a simple 7-bit timer (remember that the bits are in reverse order).

The software activation option should be chosen only when the Watchdog counter is to be used as a timer. To ensure the Watchdog has not been unexpectedly activated, the following instructions should be executed within the first 27 instructions:

jrr 0, WD, #+3

ldi WD, 0FDH

## **DIGITAL WATCHDOG** (Cont'd)

These instructions test the C bit and Reset the MCU (i.e. disable the Watchdog) if the bit is set (i.e. if the Watchdog is active), thus disabling the Watchdog.

In all modes, a minimum of 28 instructions are executed after activation, before the Watchdog can generate a Reset. Consequently, user software should load the watchdog counter within the first 27 instructions following Watchdog activation (software mode), or within the first 27 instructions executed following a Reset (hardware activation).

It should be noted that when the GEN bit is low (interrupts disabled), the NMI interrupt is active but cannot cause a wake up from STOP/WAIT modes.

Figure 18. A typical circuit making use of the EXERNAL STOP MODE CONTROL feature

Figure 19. Digital Watchdog Block Diagram

#### 3.4 INTERRUPTS

The CPU can manage four Maskable Interrupt sources, in addition to a Non Maskable Interrupt source (top priority interrupt). Each source is associated with a specific Interrupt Vector which contains a Jump instruction to the associated interrupt service routine. These vectors are located in Program space (see Table 4).

When an interrupt source generates an interrupt request, and interrupt processing is enabled, the PC register is loaded with the address of the interrupt vector (i.e. of the Jump instruction), which then causes a Jump to the relevant interrupt service routine, thus servicing the interrupt.

**Table 4. Interrupt Vector Map**

| Interrupt Source | Associated Vector         |             |

|------------------|---------------------------|-------------|

| NMI pin          | Interrupt vector #0 (NMI) | (FFCh-FFDh) |

| Port A pins      | Interrupt vector #1       | (FF6h-FF7h) |

| Port B pins      | Interrupt vector #2       | (FF4h-FF5h) |

| TIMER peripheral | Interrupt vector #3       | (FF2h-FF3h) |

| ADC peripheral   | Interrupt vector #4       | (FF0h-FF1h) |

#### 3.4.1 Interrupt Vectors

Interrupt vectors are Jump addresses to the associated service routine, which reside in specific areas of Program space. The following vectors are present:

The interrupt vector associated with the non-maskable interrupt source is referred to as Interrupt Vector #0. It is located at addresses 0FFCh and 0FFDh in Program space. This vector is associated with the falling edge sensitive Non Maskable Interrupt pin (NMI).

- The interrupt vector associated with Port A pins is referred to as interrupt vector #1. It is located at addresses 0FF6h, 0FF7h is named. It can be programmed either as falling edge sensitive or as low level sensitive, by setting the Interrupt Option Register (IOR) accordingly.

- The interrupt vector associated with Port B pins is referred to as interrupt vector #2. It is located at addresses 0FF4h, 0FF5h is named. It can be programmed either as falling edge sensitive or as rising edge sensitive, by setting the Interrupt Option Register (IOR) accordingly.

- The two interrupt vectors located respectively at addresses 0FF2h, 0FF3h and addresses 0FF0h, 0FF1h are respectively known as Interrupt Vectors #3 and #4. Vector #3 is associated with the TIMER peripheral and vector #4 with the A/D Converter peripheral.

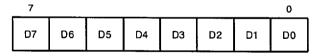

Each on-chip peripheral has an associated interrupt request flag (TMZ for the Timer, EOC for the A/D Converter), which is set to "1" when the peripheral generates an interrupt request. Each on-chip peripheral also has an associated mask bit (ETI for the Timer, EAI for the A/D Converter), which must be set to "1" to enable the associated interrupt request.

#### 3.4.2 Interrupt Priorities

The Non Maskable Interrupt request has the highest priority and can interrupt any interrupt routine at any time; the other four interrupts cannot interrupt each other. If more than one interrupt request is pending, these are processed by the processor core according to their priority level: vector #1 has the higher priority while vector #4 the lower. The priority of each interrupt source is fixed.

## **IINTERRUPTS** (Cont'd)

## 3.4.3 Interrupt Option Register (IOR)

The Interrupt Option Register (IOR) is used to enable/disable the individual interrupt sources and to select the operating mode of the external interrupt inputs. This register is write-only and cannot be accessed by single-bit operations.

Address: 0C8h — Write Only

Reset status: 00h

| <br> |     |     |   |   | 0 |

|------|-----|-----|---|---|---|

| LES  | ESB | GEN | • | - | - |

Bit 7, Bits 3-0 = Unused.

Bit 6 = LES: Level/Edge Selection bit

When this bit is set to one, the interrupt #1 (Port A) is low level sensitive, when cleared to zero the negative edge sensitive interrupt is selected.

Bit 5 = **ESB**: Edge Selection bit.

When this bit is set to one, the interrupt #2 (Port B) is positive edge sensitive, when cleared to zero the negative edge sensitive interrupt is selected.

Bit 4 = **GEN**: Global Enable Interrupt When this bit is set to one, all interrupts are enabled. When this bit is cleared to zero all the interrupts (excluding NMI) are disabled.

When the GEN bit is low, the NMI interrupt is active but cannot cause a wake up from STOP/WAIT modes.

This register is cleared on reset.

**Table 5. Interrupt Options**

| GEN | SET     | Enables all interrupts                                    |  |  |  |

|-----|---------|-----------------------------------------------------------|--|--|--|

|     | CLEARED | Disables all interrupts                                   |  |  |  |

| ESB | SET     | Rising edge mode on Interrupt Port B                      |  |  |  |

| LOD | CLEARED | Falling edge mode on Interrupt Port B                     |  |  |  |

| LES | SET     | Level sensitive mode on Interrupt<br>Port A               |  |  |  |

|     | CLEARED | Falling edge sensitive mode on Inter-<br>rupt mode Port A |  |  |  |

## 3.4.4 External Interrupt Operating Modes

The NMI interrupt is associated with the external interrupt pin. This pin is falling edge sensitive and the interrupt pin signal is latched by a flip-flop which is automatically reset by the core at the beginning of the non-maskable interrupt service routine. A Schmitt trigger is present on the NMI pin. The user can choose to have an on-chip pull-up on the NMI pin by specifying the appropriate ROM mask option (see Option List at the end of the Datasheet).

The two interrupt sources associated with the falling/rising edge mode of the external interrupt pins (Port A-vector #1, Port B-vector #2) are connected to two internal latches. Each latch is set when a falling/rising edge occurs during the processing of the previous one, will be processed as soon as the first one has been serviced (unless a higher priority interrupt request is present). If more than one interrupt occurs while processing the first one, the subsequent ones will be lost.

Storage of interrupt requests is not available in level sensitive detection mode. To be taken into account, the low level must be present on the interrupt pin when the MCU samples the line after instruction execution.

At the end of every instruction, the MCU tests the interrupt lines: if there is an interrupt request the next instruction is not executed and the appropriate interrupt service routine is executed instead.

When the GEN bit is low, the NMI interrupt is active but cannot cause a wake up from STOP/WAIT modes.

# **IINTERRUPTS** (Cont'd)

#### 3.4.5 Interrupt Procedure

The interrupt procedure is very similar to a call procedure, indeed the user can consider the interrupt as an asynchronous call procedure. As this is an asynchronous event, the user cannot know the context and the time at which it occurred. As a result, the user should save all Data space registers which may be used within the interrupt routines. There are separate sets of processor flags for normal, interrupt and non-maskable interrupt modes, which are automatically switched and so do not need to be saved.

The following list summarizes the interrupt procedure:

#### MCU

- The interrupt is detected.

- The C and Z flags are repliced by the interrupt flags (or by the NMI flags).

- The PC contents are stored in the first level of the stack.

- The normal interrupt lines are inhibited (NMI still active).

- The first internal latch is cleared.

- The associated interrupt vector is loaded in the PC.

#### User

- User selected registers are saved within the interrupt service routine (normally on a software stack).

- The source of the interrupt is found by polling the interrupt flags (if more than one source is associated with the same vector).

- The interrupt is serviced.

- Return from interrupt (RETI)

#### MCU

Automatically the MCU switches back to the normal flag set (or the interrupt flag set) and pops the previous PC value from the stack.

The interrupt routine usually begins by the identifying the device which generated the interrupt request (by polling). The user should save the registers which are used within the interrupt routine in a software stack. After the RETI instruction is executed, the MCU returns to the main routine.

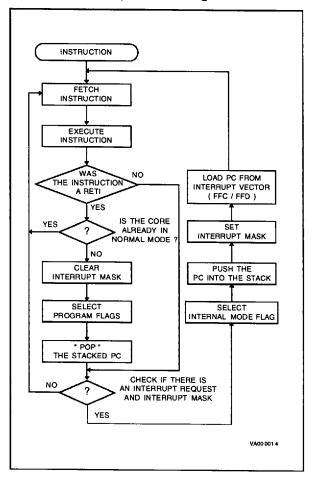

Figure 20. Interrupt Processing Flow Chart

# **IINTERRUPTS** (Cont'd)

**Table 6. Interrupt Requests and Mask Bits**

| Peripheral    | Peripheral Register |         | Mask bit   | Masked Interrupt Source      | Interrupt<br>vector |

|---------------|---------------------|---------|------------|------------------------------|---------------------|

| GENERAL       | IOR                 | C8h     | GEN        | All Interrupts, excluding NM | _                   |

| TIMER         | TSCR                | D4h     | ETI        | TMZ: TIMER Overflow          | Vector 3            |

| A/D CONVERTER | ADCR                | D1h     | EAI        | EOC: End of Conversion       | Vector 4            |

| Port PAn      | ORA-DDRA            | C4h-CCh | ORAn-DDRAn | PAn pin                      | Vector 1            |

| Port PBn      | ORB-DDRB            | C5h-CDh | ORBn-DDRBn | PBn pin                      | Vector 2            |

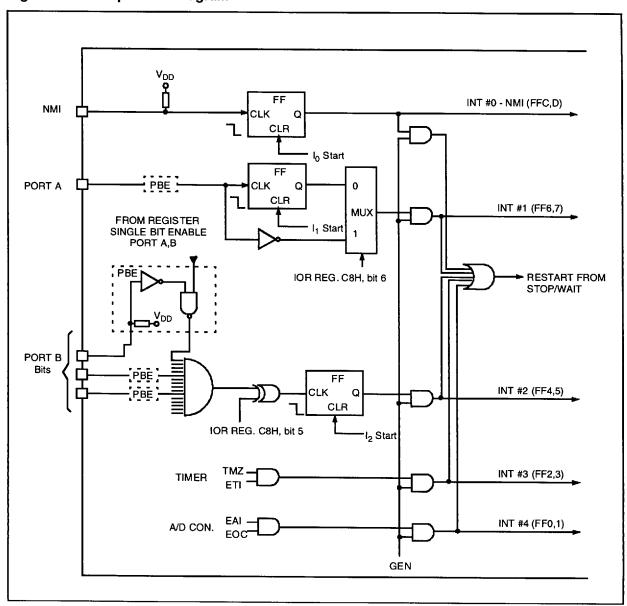

Figure 21. Interrupt Block Diagram

#### 3.5 POWER SAVING MODES

The WAIT and STOP modes have been implemented in the ST62xx family of MCUs in order to reduce the product's electrical consumption during idle periods. These two power saving modes are described in the following paragraphs.

In addition, the Low Frequency Auxiliary Oscillator (LFAO) can be used instead of the main oscillator to reduce power consumption in RUN and WAIT modes.

#### 3.5.1 WAIT Mode

The MCU goes into WAIT mode as soon as the WAIT instruction is executed. The microcontroller can be considered as being in a "software frozen" state where the core stops processing the program instructions, the RAM contents and peripheral registers are preserved as long as the power supply voltage is higher than the RAM retention voltage. In this mode the peripherals are still active.

WAIT mode can be used when the user wants to reduce the MCU power consumption during idle periods, while not losing track of time or the capability of monitoring external events. The active oscillator (main oscillator or LFAO) is not stopped in order to provide a clock signal to the peripherals. Timer counting may be enabled as well as the Timer interrupt, before entering the WAIT mode: this allows the WAIT mode to be exited when a Timer interrupt occurs. The same applies to other peripherals which use the clock signal.

If the power consumption has to be further reduced, the Low Frequency Auxiliary Oscillator (LFAO) can be used in place of the main oscillator, if its operating frequency is lower. If required, the LFAO must be switched on before entering the WAIT mode.

If the WAIT mode is exited due to a Reset (either by activating the external pin or generated by the Watchdog), the MCU enters a normal reset procedure. If an interrupt is generated during WAIT mode, the MCU's behaviour depends on the state of the processor core prior to the WAIT instruction, but also on the kind of interrupt request which is generated. This is described in the following paragraphs. The processor core does not generate a delay following the occurrence of the interrupt, because the oscillator clock is still available and no stabilisation period is necessary.

#### 3.5.2 STOP Mode

If the Watchdog is disabled, STOP mode is available. When in STOP mode, the MCU is placed in the lowest power consumption mode. In this operating mode, the microcontroller can be considered as being "frozen", no instruction is executed, the oscillator is stopped, the RAM contents and peripheral registers are preserved as long as the power supply voltage is higher than the RAM retention voltage, and the ST62xx core waits for the occurrence of an external interrupt request or a Reset to exit the STOP state.

If the STOP state is exited due to a Reset (by activating the external pin) the MCU will enter a normal reset procedure. Behaviour in response to interrupts depends on the state of the processor core prior to issuing the STOP instruction, and also on the kind of interrupt request that is generated.

This case will be described in the following paragraphs. The processor core generates a delay after occurrence of the interrupt request, in order to wait for complete stabilisation of the oscillator, before executing the first instruction.

# POWER SAVING MODE (Cont'd)

#### 3.5.3 Exit from WAIT and STOP Modes

The following paragraphs describe how the MCU exits from WAIT and STOP modes, when an interrupt occurs (not a Reset). It should be noted that the restart sequence depends on the original state of the MCU (normal, interrupt or non-maskable interrupt mode) prior to entering WAIT or STOP mode, as well as on the interrupt type.

Interrupts do not affect the oscillator selection, consequently, when the LFAO is used, the user program must manage oscillator selection as soon as normal RUN mode is resumed.

#### 3.5.3.1 Normal Mode

If the MCU was in the main routine when the WAIT or STOP instruction was executed, exit from Stop or Wait mode will occur as soon as an interrupt occurs; the related interrupt routine is executed and, on completion, the instruction which follows the STOP or WAIT instruction is then executed, providing no other interrupts are pending.

#### 3.5.3.2 Non Maskable Interrupt Mode

If the STOP or WAIT instruction has been executed during execution of the non-maskable interrupt routine, the MCU exits from the Stop or Wait mode as soon as an interrupt occurs: the instruction which follows the STOP or WAIT instruction is executed, and the MCU remains in non-maskable interrupt mode, even if another interrupt has been generated.

### 3.5.3.3 Normal Interrupt Mode

40/62

If the MCU was in interrupt mode before the STOP or WAIT instruction was executed, it exits from STOP or WAIT mode as soon as an interrupt occurs. Nevertheless, two cases must be considered: