#### 1. Introduction

The Extended Data Rate Adapter (EDRA) is a CMOS integrated circuit for ISDN applications developed to adapt synchonous and asynchronous user data rates on the CCITT R-interface to a 64 kbit/s data stream and vice versa.

#### 1.1. Features

- \* Data rate adaption to 64 kbit/s according CCITT V.110/X.30 and ECMA-102 recommendations.

- \* Synchronous data rates supported:

- 600, 1200, 2400, 4800, 9600, 19200, 38400, 48000, 56000 and 64000 bit/s.

- \* Asynchronous data rates supported (using RAO asynchronous-synchronous conversion):

- full duplex with the same rates:

- 300, 600, 1200, 2400, 4800, 9600, 19200

- or full duplex with:

- 1200/75 and 75/1200 bit/s.

- \* Asynchronous automatic data rate adaption from 0 upto 19.2 kbit/s using a multiple sampling method with additional transition coding (based on CCITT rec. R.111), for compatibility with its predecessor the PCB2320 DRA. Useful for data rates as:

- 50, 75, 110, 134.5, 150, 200, 3600, 7200, 12000, 14400 and 19200 bit/s.

- \* Flexible synchronous data interface, which supports both long and short frame synchronisation, i.e. connectable to:

- -2.048 Mbit/s Terminal highway;

- -SLD interface;

- -IOM interface (not in MPX mode);

- \* Submultiplexing, according to CCITT rec. I.460, permits upto 8 EDRAs to share one 64 kbit/s channel on the synchronous data interface.

- $\star$  Serial interface for the DTE/DCE. A complete set of V- or X-series interchange circuits is supported.

- \* Microcontroller interface with multiplexed data/address lines.

- $\star$  Built in UART for microcontroller access to both local and remote side of the data channel.

118

PCB2325

- \* Local flowcontrol by control of lead 106 or X-ON/X-OFF.

- \* End to end flowcontrol.

- \* Inband Parameter Exchange (IPE), according to ECMA-102 recommendation:

- -unrestricted 64 kbit/s;

- -restricted 56 kbit/s;

- -asynchronous RAO;

- -asynchronous multiple-sampling.

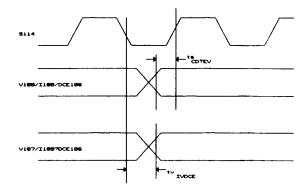

- \* Network Independent Clocking (NIC) (for synchronous data rates), according to CCITT rec. V.110 and ECMA-102, for the data rates of:

- 4800, 9600 and 19200 bit/s.

- \* Automatic speed recognition with aid of the microcontroller for data rates upto 19.2 kbit/s.

- \* EDRA is usable in an interrupt driven environment (open drain interrupt output).

- \* Monitoring and clamping of the interchange circuits (by microcontroller).

- \* Low power (power consumption < 40 mW).

- \* Powerdown mode (power consumption in powerdown mode < 0.2 mW).

- \* Maintenance loops.

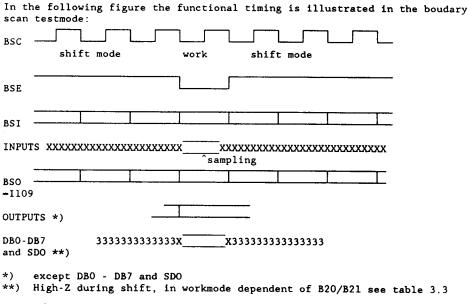

- \* Boundary scan test.

- \* Single 5V supply power.

### 1.2. Ordering information

| TYPE NUMBER | TEMPERATURE<br>RANGE <sup>O</sup> C | PACKAGE |

|-------------|-------------------------------------|---------|

| PCB2325     | -10 75°C                            | PLCC 44 |

| PCB2325     | -10 75°C                            | DIL 40  |

October 1990

119

### 1.3. Signal description

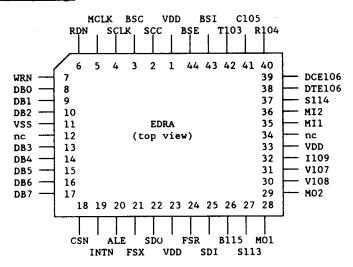

### 1.3.1. PLCC 44 package

Figure 1.3-1 Pinning diagram (PLCC 44)

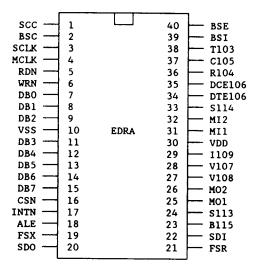

### 1.3.2. DIL 40 package

Figure 1.3-2 Pinning diagram (DIL 40)

The signals names which are illustrated in figure 1.3-1 and figure 1.3-2 are now described. The pin numbers refer to the PLCC 44 package (figure 1.3-1) and the pin numbers between brackets refer to the DIL 40 package (figure 1.3-2).

- Power supply connection +5V. 1 VDD SCC Scan Control input. Together with BSI (pin 43 (39)) and BSE 2 (1) (pin 44 (40)) the test-mode of the EDRA is determined. (2) BSC Boundary scan clock input. (3) SCLK Synchronous interface clock input (64 kHz - 2.048 MHz). SCLK determines the data rate on the synchronous data interface. (4) MCLK Master clock input (2.048 MHz). Read Not input (active low). Data is set on the  $\mu$ C-bus by (5) RDN EDRA (if selected by CSN), after the trailing edge of RDN. Write Not input (active low). The  $\mu$ C writes data into the 7 (6) WRN EDRA (if selected by CSN). Data is latched on the leading edge of WRN. 8 (7) DBO Data/address line 0 (LSB). 9 (8) DB1 Data/address line 1. DB2 Data/address line 2. 10 (9) 11 (10) vss Ground 12 n.c. Not connected 13 (11) DB3 Data/address line 3. 14 (12) DB4 Data/address line 4. 15 (13) DB5 Data/address line 5. 16 (14) DB6 Data/address line 6. 17 (15) DB7 Data/address line 7 (MSB). 18 (16) CSN Chip Select input (active low). 19 (17) INTN Interrupt output (active low, open drain). 20 (18) ALE Address Latch Enable input. Indicates that the combined data/address bus contains an address.

- October 1990 122

| 21 (19) 1        | FSX          | Transmit Frame Select input. FSX aligns every 125 $\mu$ s the 8 data bits on SDO (pin 22 (20)).                                                                                                                                                                                                                       |

|------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22 (20)          | SDO          | Synchronous Data output. Data output of the synchronous data interface.                                                                                                                                                                                                                                               |

| 23               | VDD          | Power supply connection +5V.                                                                                                                                                                                                                                                                                          |

| 24 (21)          | FSR          | Receive Frame Select input. FSR aligns every 125 $\mu s$ the 8 data bits for the EDRA on SDI (pin 25 (22)).                                                                                                                                                                                                           |

| 25 (22)          | SDI          | Synchronous data input. Serial data input of the synchronous data interface.                                                                                                                                                                                                                                          |

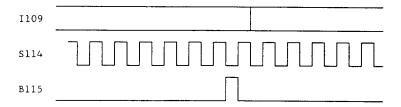

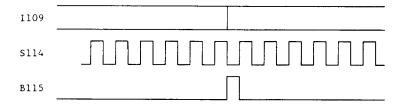

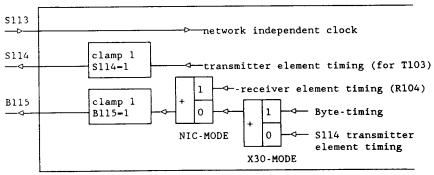

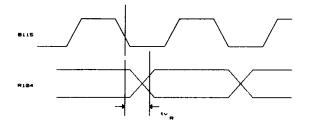

| 26 (23) 1        | <b>B11</b> 5 | Byte timing (B) or receiver element timing output. Signal B is a CCITT X-series defined control signal. This circuit provides the DTE the byte timing signal. The output pin B indicates the last bit of a data-byte. It will be HIGH during one period of S114 (pin 37 (33)) and will be LOW within the byte-period. |

|                  |              | Receiver element timing output. Circuit 115 (V-series) generates the data element clock for circuit R104 (pin 40 $(36)$ ).                                                                                                                                                                                            |

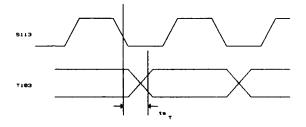

| 27 (24) 5        | S113         | Transmitter element timing input (provided by the DTE). S113 provides the data element timing for T103 (pin 42 $(38)$ ).                                                                                                                                                                                              |

| 28 (25) h        | <b>M</b> 01  | Multifunctional output 1.                                                                                                                                                                                                                                                                                             |

| 29 (26) h        | <b>M</b> O2  | Multifunctional output 2.                                                                                                                                                                                                                                                                                             |

| 30 (27)          | V108         | Data Terminal Ready input. Indicates that the associated terminal is ready to receive and transmit data.                                                                                                                                                                                                              |

| 31 (28) 1        | V107         | Data Set Ready output. Indicates that to the terminal that the EDRA is ready to receive data. Output V107 indicates the state of the remote subscribers V108 circuit.                                                                                                                                                 |

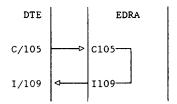

| 32 (29)          | 1109         | Data channel received line signal detector/indication. Output which indicates the state of the remote subscribers C105 circuit. Under control of the $\mu$ C, I109 can be made byte-timing synchronous. This pin is in boundary test mode boundary scan output.                                                       |

| 33 (30) 1        | VDD          | Power supply connection +5V.                                                                                                                                                                                                                                                                                          |

| 34 r             | n.c.         | Not connected.                                                                                                                                                                                                                                                                                                        |

| 35 (31) A        | MI1          | Multifunctional input 1.                                                                                                                                                                                                                                                                                              |

| 36 (32) <b>1</b> | MI2          | Multifunctional input 2.                                                                                                                                                                                                                                                                                              |

| October 1990     |              | 123                                                                                                                                                                                                                                                                                                                   |

### PCB2325

### Extended data rate adaptor

- 37 (33) S114 Transmitter element timing output. In synchronous mode S114 generates the data element clock for circuit T103 (pin 42 (38)).

- 38 (34) DTE106 Request To Send input (EDRA=DTE).

- 39 (35) DCE106 Request To Send output. Output which indicates the state of the remote subscribers DTE106 circuit.

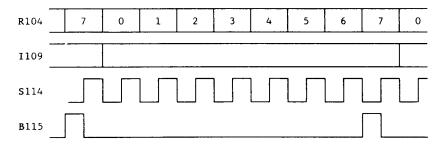

- 40 (36) R104 Received data output. R104 provides circuit 104 for V- and R for X-series of interfaces. Circuit R104 will be shifted out every trailing edge of S114 (pin 37 (33)).

- 41 (37) Cl05 For V-series, Cl05 performs as circuit 105, for X-series as circuit C. Cl05 is a signalling channel which corresponds with Il09 of the remote subscriber.

- 42 (38) T103 Transmit data input. Transmit input has to be connected to the transmit (T for X-, circuit 103 for V-series) output of the DTE equipment. For synchronous speeds T103 will be sampled at every leading edge of B115 (pin 26 (23)).

- 43 (39) BSI Boundary scan input.

- 44 (40) BSE Boundary scan enable.

#### 2. Functional description

### 2.1. General description

The EDRA adapts synchronous and asynchronous user data rates on the so called R-interface fully in accordance to CCITT rec. X.30/V.110 and ECMA-102 recommendations to a 64 kbit/s channel (ISDN B-channel) and vice versa.

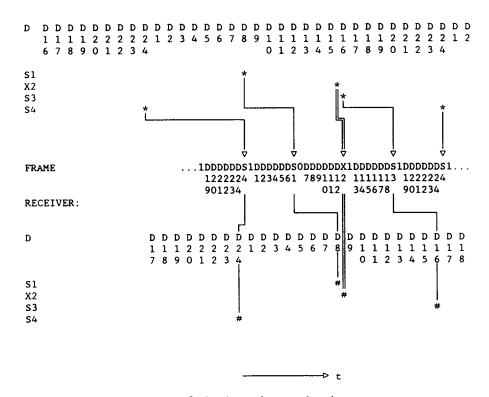

To be compatible with the EDRAs predecessor, the PCB2320 Data Rate Adapter (DRA) also multiple sampling is used. Asynchronous user data rates from 0 upto 19.2 kbit/s on the R-interface are also supported using the multiple sampling method with additional transition coding based on CCITT rec. R.lll. With this multiple sampling method it is possible to convert every asynchronous user data rate to a 64 kbit/s data stream without the need of programming the EDRA for the specific user data rate of the DTE.

Network independent clocking is supported by the EDRA. It allows the EDRA to be connected to a synchronous modem with a data rate upto 19.2 kbit/s not locked to the user data rate of the EDRA without loss of data.

In order to provide a means to transfer data by  $\mu$ C to the remote EDRA, an IPE exchange mode is implemented. In this mode the  $\mu$ C can access the 64 kbit/s channel to transmit data to and receive data from the remote EDRA.

To be able to communicate with the DTE the  $\mu C$  connected to the EDRA can be connected to the R-interface. In this way the  $\mu C$  can demand the DTE for call setup information.

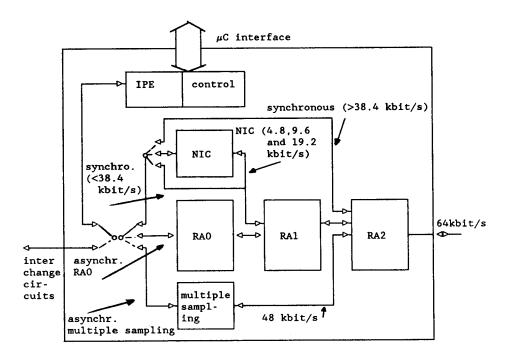

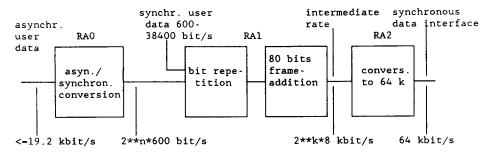

The conversion between user data rates and the 64 kbit/s data rate takes place RAO, RA1 and RA2 adaption stages as decribed in the CCITT X.30 and V.110 and ECMA-102 recommendations. The RAO adaption stage performs the asynchronous-synchronous conversion, while the RA1 and RA2 adaption stage perform the conversion between a synchronous data rate (or synchronous data from the RAO stage) to 64 kbit/s. In figure 2.1-1 a survey is given of the different data paths within the EDRA.

Figure 2.1-1 Data paths within the EDRA

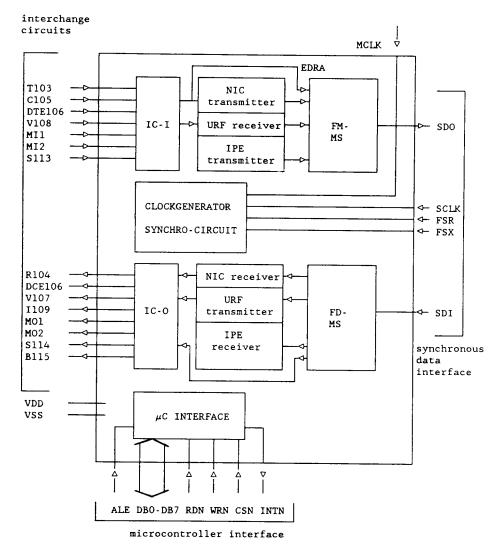

In the EDRA different functional blocks can be distinghuised. These blocks are illustrated in blockdiagram 2.1-2.

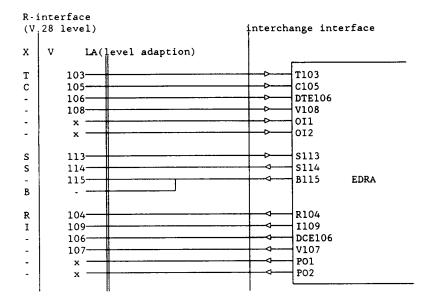

A brief description of the interfaces of the EDRA is given before the functional blocks are described. In blockdiagram 2.1-2 three interfaces can be destinguished:

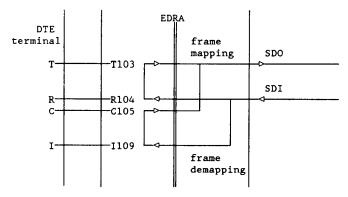

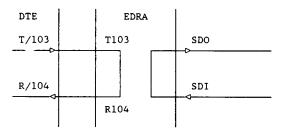

\*The interchange interface. A set of V-type interchange circuits: 103, 104, 105, 106, 107, 108, 109, 113, 114, 115 and two multifunctional input and two multifunctional outputs or X-type data interface interchange circuits: T, R, C, I, S and B can be connected to the EDRA via level converters. This interchange interface is described in section 2.3.

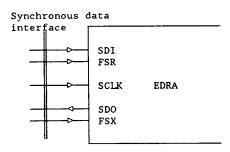

\*The synchronous data interface can have a transmission rate between 64 kbit/s and 2.048 Mbit/s. The interface consists of two unidirectional data lines (SDI and SDO), a clock line (SCLK) determining the transmission rate on this interface, a frame select transmit signal (FSX) and frame select receive signal (FSR) which indicate the transmit and receive timeslot on the synchronous data interface. The synchronous data interface is described in section 2.4.

All the blocks in the EDRA are controlled via the  $\mu C$  interface and receive their timing from the clock generator/synchronisation circuit.

Figure 2.1-2 Block diagram of the EDRA.

\*The 8 bit microcontroller interface is a data/address multiplexed microcontroller interface. The microcontroller interface performs the interface for the control stages of the EDRA. The EDRA can be programmed and monitored via the microcontroller interface. The settings of the EDRA can be programmed in a set of write registers. The following settings can be programmed:

- selection of functional mode

- data rate setting

- the mapping scheme (interchange circuits to S- and X-bits)

- clamping of interchange circuits

- testloop selection

- communications control via UART

- interrupt masking

- 64 kbit/s channel framing and synchronisation control

- setting UART/flow control parameters

The EDRA can be monitored by reading out the read registers. The following functions can be read out:

- in/out synchronisation-indication

- activity check on interchange circuits

- readout logic state of interchange circuits.

- readout of the interrupt source.

- readout the UART

The microcontroller interface description and the detailed description of the registers is provided in section 2.9.

\*Clock generator and synchronisation circuit

The clock generator and synchronisation circuit provides all internal clocks of the EDRA. It generates i.e. the baud rates on circuits S114 and 115 and provides byte timing on circuit B. (B and 115 are physically one circuit, but can be switched by the microcontroller). The baudrate on the interchange interface can be selected with register W01, see section 2.9.1.2.

\*Interchange circuits (inputs/outputs) (IC-I/IC-0)

The interchange circuit (input and output) blocks (IC-I and IC-O) interface with the connected data equipment. All interchange circuits can be monitored via the  $\mu$ C-interface. Via this block, the mapping of the interchange circuits to the S- and X-bits in the frame on the synchronous data interface can be chosen. A detailed desciption of these blocks is given in section 2.3.

\*Frame mapping and demapping block and multiple-sampling coding/decoding (FM-MS/FD-MS)

The translation between synchronous user data rates and the 64 kbit/s channel takes place in the frame mapping block (FM in figure 2.1-2) while the reverse action is performed by the frame demapping block (FD). These blocks perform the RA1 and RA2 stages as described in CCITT rec. X.30/V.110 and ECMA-102. The asynchronous to synchronous conversion according to the multiple sampling method with additional transition coding is also performed in the frame mapping/demapping block. A detailed description of the frame mapping/demapping block is given in section 2.8.

\*URF transmitter/receiver

URF transmitter/receiver block is a combination of three functions, UART, RAO adaption stage (according ECMA-102 and CCITT rec. V.22), flow-control (FLC). A detailed description of the URF transmitter/receiver is given in section 2.5.

\*IPE transmitter/receiver

The Inband Parameter Exchange (IPE) function is discussed in 2.6.

\*Network independent clocking transmitter/receiver

The NIC block allows the EDRA to be connected to a synchronous modem with a data rate of 4800, 9600 or 19.2 kbit/s. A detailed description of the NIC function is given in section 2.7.

### 2.2. Modes of operation

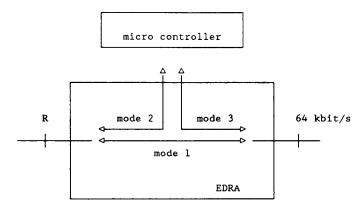

The EDRA can be used in three different modes of operation (illustrated in figure 2.2-1) which can be programmed by the microcontroller:

- \* Transmission-mode 1: Local DTE to remote DTE.

- -1A: synchronous, data rate adaption according to CCITT rec. V.110 or X.30 (V.110 (asynchronous or bit synchronous) or X.30 mode (byte-synchronous) can be selected);

- -1B: asynchronous with the RAO coding;

- -1C: asynchronous with flow control;

- -1D: asynchronous with multiple sampling and additional transition coding. In this mode the break character can be filtered out by microcontroller and user data can be read out via the microcontroller interface.

- \* Transmission-mode 2: Local DTE to local microcontroller.

In this mode, the microcontroller can communicate to the DTE/DCE via the UART. Only asynchronous transmission is possible, the URF will be used as asynchronous receiver transmitter (the UART function).

- \* Transmission-mode 3: Local microcontroller to 64 kbit/s channel.

- -3A: asynchronous, the 64 kbit/s channel data will be coded according the multiple sampling method. the URF will be used as asynchronous receiver transmitter (the UART function);

- -3B: asynchronous, IPE mode with RAO coded data in 64 kbit/s channel. the URF will be used as asynchronous receiver transmitter (the UART function);

- -3C: synchronous, IPE mode with 64 or 56 kbit/s data rate in the 64 kbit/s channel, The microcontroller uses the UART for parallel-serial conversion and the data in the 64 kbit/s channel will be coded according to the selected mode (56 or 64 kbit/s).

Figure 2.2-1 The three transmission modes of the EDRA

### 2.3. Interchange circuits

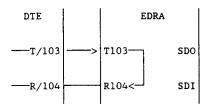

The interchange interface of the EDRA connects to level converters which then connect to the DTE (or DCE) (see figure 2.3-1). The interchange interface consists of:

```

*T103 :Circuit 103 (V-series), Transmitted Data.

T (X-series), Transmit.

*R104 :Circuit 104 (V-series), Received Data.

R (X-series), Receive.

*C105 :Circuit 105 (V-series), Request To Send.

C (X-series), Control.

*DTE106 :Circuit 106 (V-series), Clear To Send (the EDRA is DTE).

*DCE106 :Circuit 106 (V-series), Clear To Send (the EDRA is DCE).

```

PCB2325

| *V107 | :Circuit 107 (V-series), Data Set Ready.                                                                 |

|-------|----------------------------------------------------------------------------------------------------------|

| *V108 | :Circuit 108 (V-series), Data Terminal Ready.                                                            |

| *1109 | :Circuit 109 (V-series), Data channel received line signal detector. I (X-series), Indication.           |

| *S113 | :Circuit 113 (V-series), Transmit signal element timing (from DTE). S (X-series), Signal element timing. |

| *S114 | :Circuit 114 (V-series), Transmit signal element timing (from DCE). S (x-series), Signal element timing. |

| *B115 | :Circuit 115 (V-series), Receiver signal element timing. B (X-series), Byte timing.                      |

| *MO1  | :Multifunctional output 1.                                                                               |

| *MO2  | :Multifunctional output 2.                                                                               |

| *MI1  | :Multifunctional input 1.                                                                                |

| *MI2  | :Multifunctional input 2.                                                                                |

Figure 2.3-1 The interchange interface.

#### 2.3.1. Mapping of the interchange circuits in Data. S- and X-bits

ECMA and CCITT specify the interchange circuits that should be mapped into the frame used in the 64 kbit/s channel. In the EDRA the mapping of interchange circuits into the 64 kbit/s channel can be performed in three ways (see register W00, section 2.9.1.1):

- -V.110 mode: in this mode the EDRA is asynchronous or bit synchronous but not byte synchronous (see section 2.3.3).

- -X.30 mode: in this mode the EDRA is byte synchronous (see section 2.3.3).

- $\mu\text{C}$  mode: in this mode the S- and X-bits in the frame can be set and read by  $\mu\text{C}\,.$

For user data rates  $\leq 38.4$  kbit/s a 10 bytes multiframe is used (see section 2.8.2 and appendix B for the description of this frame). Table 2.3.1-1 shows the mapping of interchange circuits in the bits of the 10-bytes multiframe.

|             | local subscriber  | frame bits         | remote subscriber |

|-------------|-------------------|--------------------|-------------------|

| V.110       | V108              | \$1,\$3,\$6,\$8    | V107              |

| mode        | C105              | S4,S9              | 1109              |

|             | frame sync/DTE106 | X2,X7              | DCE106            |

|             | T103              | D1 - D48           | R104              |

| X.30        | C105              | SP, SQ, SR         | 1109              |

| mode        | frame sync/DTE106 | X2, X7             | DCE106            |

|             | T103              | P1 - R8            | R104              |

| <b>μ</b> C- | register W07      | S1,X2,S3,S4,S6,X7, | register R24      |

| mode        |                   | S8,S9              | (bit 0-7)         |

Table 2.3.1-1 Mapping of interchange circuits for user data rates  $\leq$  38.4 kbit/s.

For the user data rate of 48 kbit/s a four bytes frame is used (see section 2.8.2 and appendix B for the description of this frame). In table 2.3.1-2 the mapping of the interchange circuits in the bits of the 4 bytes frame is illustrated.

For a user data rate of 56 kbit/s only one S-bit is available (in the 4 bytes frame) to transmit one interchange circuit. The mapping of the interchange circuits for the user data rate of 56 kbit/s is illustrated in table 2.3.1-3 (see section 2.8.2 and appendix B for a description of this frame).

| local subscriber           | frame bits                                                                  | remote subscriber                                                                                                                                 |

|----------------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| V108                       | \$1,83                                                                      | V107                                                                                                                                              |

| C105                       | S4                                                                          | 1109                                                                                                                                              |

| frame sync/DTE106          | X2                                                                          | DCE106                                                                                                                                            |

| T103                       | D1 - D24                                                                    | R104                                                                                                                                              |

| C105                       | SP, SQ, SR                                                                  | 1109                                                                                                                                              |

| frame sync/DTE106          | X2                                                                          | DCE106                                                                                                                                            |

| T103                       | P1 - R8                                                                     | R104                                                                                                                                              |

| register W07<br>(S6-S9 not | S1,X2,S3,S4                                                                 | register R24<br>(bit 0-3)                                                                                                                         |

|                            | V108 C105 frame sync/DTE106 T103  C105 frame sync/DTE106 T103  register W07 | V108 S1,S3 S4 S4 S1 T103 S4 S1 T103 S4 S1 T103 S4 S1 T103 S1 T103 SP, SQ, SR S1 T103 SP, SQ, SR S1 T103 S1,X2,S3,S4 S1 S1,X2,S3,S4 S1 S1,X2,S3,S4 |

Table 2.3.1-2 Mapping of interchange circuits for a user data rate of 48 kbit/s.

|              | local subscriber | frame bits                             | remote subscriber                 |

|--------------|------------------|----------------------------------------|-----------------------------------|

| X.30<br>mode | C105<br>T103     | S<br>D1 - D28                          | I109<br>R104                      |

| μC-<br>mode  |                  | be influenced by to the coupled to lea | W07 in the $\mu$ C-mode, ad C105. |

|              | clamping of C105 | s                                      | register R24, bit 0               |

Table 2.3.1-3 Mapping of interchange circuits for a user data rate of 56 kbit/s.

#### 2.3.2. Relation between ON/OFF and their binary values

In the december '84 ECMA specification, the binary values of S- and X-bits in the data stream on the synchronous data interface are given related to ON or OFF conditions of the interchange circuits:

For the S- and X-bits, a zero corresponds with the ON condition, a one with the OFF condition.

In the september '84 ECMA report this definition was reverse: zero corresponds with OFF, a one with ON.

To meet both definitions (and so to be upwards compatible with the DRA), both definitions can be selected in registers W5/W10 (section 2.9.1). When the EDRA is connected to a DRA, the EDRA must code the S- and X-bits according the september ECMA definition. When other networks are involved, the EDRA must be V.110 compatible (december '84 ECMA definition) and can not cooperate with the DRA anymore. In figure 2.3.2-1 the relation between the signals on the interchange circuits and the signals on the EDRA pins are depicted.

| Signal                                                                   | V.28 level<br><3V                             | V.28 level<br>>= 3V        | comment                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------------------------------------------------|-----------------------------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T103<br>R104                                                             | 1                                             | 0                          | Condition 0 on V.28 level - condition 0 in the data bits on the SD interface.  Condition 1 on V.28 level - condition 1 in the data bits on the SD interface.                                                                                                                                                                                                                                                                |

| C105<br>DTE106<br>DCE106<br>V107<br>V108<br>I109<br>S113<br>S114<br>B115 | OFF<br>OFF<br>OFF<br>OFF<br>OFF<br>OFF<br>OFF | ON ON ON ON ON ON ON ON ON | Condition ON on V.28 level = condition 0 in the S- and X-bits on the SD interface (V.110 mode). Condition OFF on V.28 level = condition 1 in the S- and X-bits on the SD interface (V.110 mode). Condition ON on V.28 level = condition 1 in the S- and X-bits on the SD interface (DRA-mode). Condition OFF on V.28 level = condition 0 in the S- and X-bits on the SD interface (DRA-mode) to the SD interface (DRA-mode) |

Table 2.3.2-1 Relation between the signals on the interchange circuits and the signals on the EDRA.

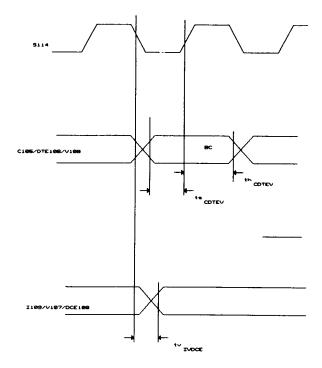

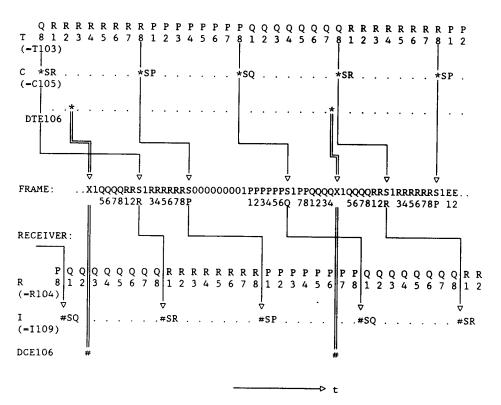

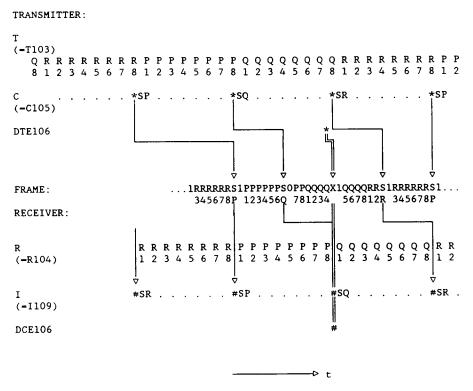

### 2.3.3. Functional timing relations

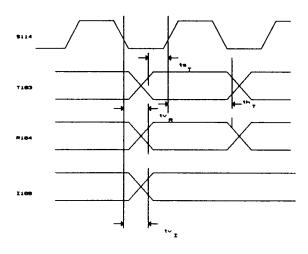

In X.30 mode, the byte timing interchange circuit B is provided for character alignment (pin B115). Circuit C (pin C105) is sampled together with bit 8 of the preceding character (on T103). The timing of the outgoing interchange circuits is related to this byte timing signal. Circuit I (pin I109) is changing its state at the boundaried between old and new character at circuit R (pin R104). In figure 2.3.3-1 the relation in timing between the interchange circuits is depicted. The receiver block provides byte- and bit-synchronisation, and delaying of circuits I and R, to fit the byte-timing for X.21 interfaces.

Figure 2.3.3-1 Byte timing relation between data and S bits.

In appendix A the sampling moments and the moment of state changes of the interchange circuits in X.30 mode are depicted for the 4 bytes frame and the 10 bytes multiframe (see also section 2.8.2).

In V.110 mode the receiver data (on pin R104) is not byte synchronous with the transmitter data (T103). The received S-bits are related to databits as follows depicted in table 2.3.3-2.

| S-bit | D-bit |

|-------|-------|

| \$1   | D8    |

| \$3   | D16   |

| \$4   | D24   |

| \$6   | D32   |

| S8    | D40   |

| S9    | D48   |

Table 2.3.3-2 Coordination of S-bits to D-bits.

In appendix A the sampling moments and the moment of state changes of the interchange circuits in V.110 mode are illustrated for the 4 bytes frame and the 10 bytes multiframe (see also section 2.8.2).

### 2.4. Synchronous data interface

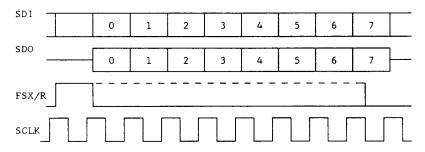

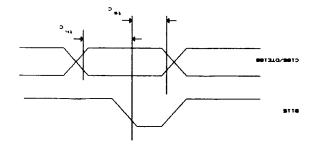

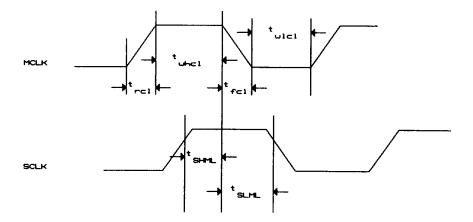

The synchronous data interface (illustrated in figure 2.4-1) consists of :

- SDI: Synchronous data input;

- SDO: Synchronous data output;

- SCLK: Data element clock (64 kHz 2.048 MHz);

- FSR: Receive frame select;

- FSX: Transmit frame select.

2.4-1 Synchronous data interface.

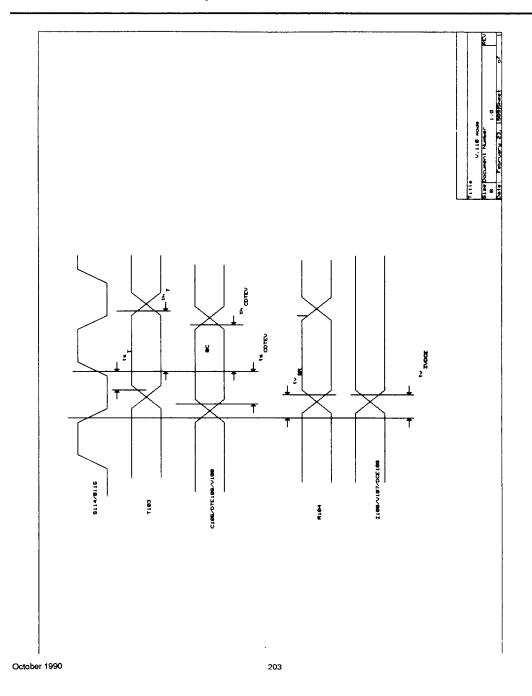

The synchronous data interface can operate between at a data rate between  $64 \, \text{kbit/s}$  and  $2.048 \, \text{Mbit/s}$ . The synchronous data interface operates in short synchronisation mode. However, a long synchronisation signal may be used if a minimal off-time Tw is taken into account (see figure 2.4.1-1 and section 3.3).

Figure 2.4.1-1 Synchronous data interface functional timing.

PCB2325

The last data rate adaption stage, RA2, converts intermediate rates from the RA1 adaption stage to the 64 kbit/s data rate (see section 2.8.2). Instead of the adaption from the intermediate rate to the 64 kbit/s data rate, the intermediate data rate can be placed in a part of the 64 kbit/s channel of the synchronous data interface. This means that for an intermediate rate of 8 kbit/s (user data upto 4.8 kbit/s) only the one of the eight bits of the timeslot is used and eight EDRAs can be (time division) multiplexed in one 64 kbit/s channel. For an intermediate rate of 16 kbit/s, four EDRAs can share the same 64 kbit/s channel and for an intermediate rate of 32 kbit/s two EDRAs.

Via the microcontroller interface the selection of the bit position that will be occupied in the 64 kbit/s bitstream can be chosen: an 8 kbit/s intermediate bitstream may occupy any bit position, a 16 kbit/s intermediate stream occupies bit positions (0,1) or (2,3) or (4,5) or (6,7), a 32 kbit/s intermediate stream occupies bit positions (0,1,2,3) or (4,5,6,7); the bit position selections can be made in register WO3 (section 2.9.1.4). The order of transmission of the bits at each intermediate rate will be identical at transmitter and receiver. The highway output will 3-state all unused bits, this to enable another EDRA to transmit data in the same timeslot on the synchronous data interface.

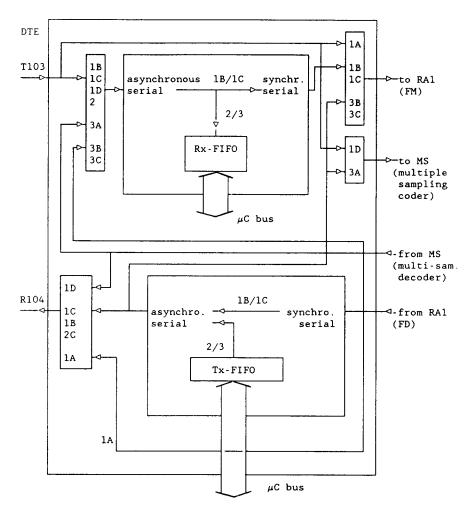

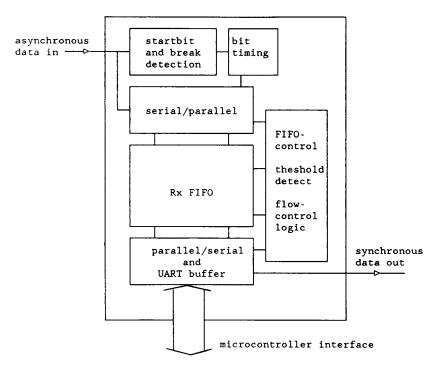

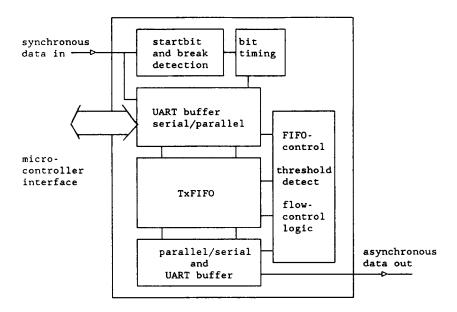

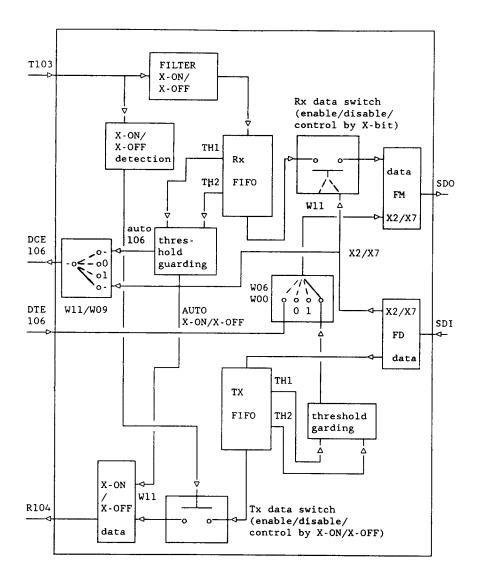

#### 2.5. URF transmitter/receiver

URF transmitter/receiver performs three functions, UART, RAO, flow-control (FLC). In figure 2.5-1 the URF transmitter/receiver block is illustrated. In this figure the data streams for the different operational modes of the EDRA (as discussed in section 2.2) are shown. In addition to figure 2.5-1 the URF transmitter and receiver are shown in more detail in figure 2.5-2 and figure 2.5-3. The different functions of the URF transmitter/receiver are discussed in the following sections.

Figure 2.5-1 The URF transmitter/receiver.

Figure 2.5-2 URF receiver

Figure 2.5-3 URF transmitter

### 2.5.1. RAO converter

In transmission mode 1B, 1C and 3B the RAO function is used. Function RAO is an asynchronous to synchronous conversion stage (and vice versa), using the technique of ECMA-102/CCITT V.22. RAO converts asynchronous user data to synchronous data of 2\*\*n \* 600 bit/s, where n=[0,1,2,3,4,5] (speed setting by  $\mu$ C is needed). This will be done by adding stopbits to fit the nearest synchronous channel. In table 2.5.1-1 the supported speeds and their relations to synchronous- and intermediate rate are depicted.

| URF data-<br>rate bps                               | rate tol-<br>erance % *                                                                  | data<br>bits                                                         | added<br>parity                 | stop bits                                                                    | possible FRAME<br>speed selections                                                                                            |

|-----------------------------------------------------|------------------------------------------------------------------------------------------|----------------------------------------------------------------------|---------------------------------|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| 300<br>600<br>1200<br>2400<br>4800<br>9600<br>19200 | +4.8/ -4.8<br>+1 / -4.8<br>+1 / -4.8<br>+1 / -4.8<br>+1 / -4.8<br>+1 / -4.8<br>+1 / -4.8 | 5/7/8<br>5/7/8<br>5/7/8<br>5/7/8<br>5/7/8<br>5/7/8<br>5/7/8<br>5/7/8 | odd/even/<br>none/<br>mark/spac | 1 or 2<br>1 or 2 | 600 - 38400<br>600 - 38400<br>1200 - 38400<br>2400 - 38400<br>4800 - 38400<br>9600 - 38400<br>19200 - 38400<br>fixed 1200 bps |

| 75/1200                                             | +1 / -4.8                                                                                | 5/7/8                                                                | ,,,                             | 1 or 2                                                                       | fixed 1200 bps                                                                                                                |

<sup>\*</sup> tolerances without Flowcontrol-setting. With FLC all tolerances are +/- 4.8 %

Table 2.5.1-1 Asynchronous data rates.

### 2.5.1.1. RAO asynchronous to synchronous conversion

In this section the asynchronous to synchronous conversion algorithm performed by the RAO-function is discussed. The asynchronous to synchronous conversion takes place in two stages. In the first stage an asynchronous data byte is received and placed in the Rx-FIFO (illustrated in figure 2.5-2). In the second stage the data byte is taken out of the Rx-FIFO and transmitted synchronously.

The following actions are performed by the URF receiver for the conversion of asynchronous data (on pin T103) to the Rx-FIFO:

- detects a period of n stopbits. This is needed for character synchronisation.

- 12. detects the trailing edge of the startbit.

- 13. and starts counting to the middle of this bit (at frequency 16\*baudrate), checks state zero. If not back to I1.

- I4. starts latching incoming bitstream in a shift-in register

- 15. increment bitcounter.

- 16. at expected stopbit, checks of state one. If so, loads contents of shift-in register into the Rx-FIFO and goto I2.

- I6a. If not and a null character has been shifted in, it loads a null character and gives a breaksignal. It waits until a rising edge of a stopbit, goto I2.

- I6b. If no stopbit is present at the expected moment and no null character is received, it loads the shift in character into the Rx-FIFO and gives the frame-error signal and continues counting to the next expected middle of a databit, checks if this bit is a start- or a stopbit. If it is a stopbit goto I2. Otherwise goto I4.

The following actions are performed to convert the data from the Rx-FIFO to the synchronous data stream:

- O1. When a character is available in the Rx-FIFO, data is loaded into a shift-out register (parallel/serial and UART buffer block in figure 2.5-2).

- O2. The shift-out register is clocked continuously with the used synchronous clock. After shifting out the parallel loaded Rx-FIFO information, the shift-out register continues sending ones (stopbits) until a character is available in the Rx-FIFO.

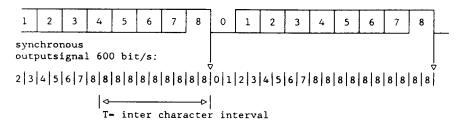

In figure 2.5.1.1-1 this procedure is illustrated for asynchronous user data of 300 baud with 7 data bits, 1 start bit and 1 stopbit.

input signal (300 baud):

Figure 2.5.1.1-1 RAO adaption of a 300 baud asynchronous user data rate.

In case the asynchronous user data has a baud rate that is a fraction higher than the nominal baud rate (overspeed), the intervaltime T (figure 2.5.1.1-1) will become smaller because of the insertion of less stopbits. This implies that at a certain user data rate the RAO-transmitter may sometimes delete the only stopbit there is. This causes problems at the remote DEDRA when the transmitted characters are sent with minimal spacing.

This problem is due to the RAO method. In CCITT rec. V.110 and ECMA-102 the following solution recommended: Because of the overspeed, the contents of the Tx-FIFO (at the remote EDRA) is increasing. To prevent the FIFO to overflow, the EDRA detects a fixed threshold level of the FIFO at two characters. Now the stopbits of the asynchronous to be sent characters are shortened to 7/8 of the normal length. In the case that two stopbits per character are selected, only one stopbit is shortened.

If the baud rate of the user data is somewhat less than the nominal rate (underspeed), the interval T may be longer than nominal because of an extra insertion of a stopbit. This extra stopbit does not affect the transmission.

#### 2.5.1.2. RAO synchronous to asynchronous conversion

In this section the synchronous to asynchronous conversion by the RAO-function is discussed. The synchronous to asynchronous conversion takes place in two stages. In the first stage a synchronous data byte is received and placed in the Tx-FIFO. In the second stage the data byte is taken out of the Tx-FIFO and transmitted asynchronously (see figure 2.5-3).

The following actions are performed by the URF transmitter to convert synchronous data to the Tx-FIFO:

- Il. It starts up with a longer period of stopelements.

- I2. searches for the startbit; samples the received synchronous bitstream on the S114 falling edge. The first detected zero is the startbit.

- 13. shifts the following characterbits in a shiftin register.

- I4. when the whole character is shifted in, the character wil be loaded into the Tx-FIFO, and goto I2.

The following actions are performed to transfer data from from Tx-FIFO to the asynchronous user data stream (R104 output):

- Ol. until a character is available in the Tx-FIFO, it will transmit stopbits.

- 02. loads the character into the shift-out register including a startbit and the selected number of stopbits. In case that the fixed threshold is reached, one stopbit is shortened to 7/8. After this go back to 01.

For 1% overspeed, maximum once per eight characters, a stop-element will be deleted.

#### 2.5.1.3. Break signal detection

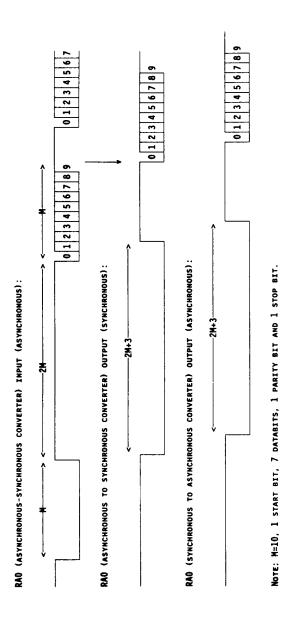

RAO asynchronous to synchronous converter is able to detect a break signal (continuous zeros on input T103) of the DTE connected to the EDRA. If the RAO converter detects M to 2M+3 bits, all of start polarity (zero), where M is the number of bits per character in the selected format including start, parity- and stopbits, RAO transmits 2M+3 bits of start polarity (at the synchronous speed). If RAO detects more than 2M+3 bits of start polarity, it transmits all these bits as start polarity.

M = nr. of databits + paritybit + startbit + stopbits.

#### Note:

The DTE must transmit on circuit 103 at least 2M bits of stop polarity after the start polarity break signal, before sending further data characters. The RAO converter will then be able to regain character synchronisation from the following stop/start transition, else character synchronisation may be lost. This fully in accordance to CCITT rec. V.110.

If 2M+3 or more bits of start polarity are received from the remote EDRA these bits are output to the DTE connected to the EDRA.

In figure 2.5.1.3-1 the transmission of the break signal is illustrated: October 1990

Powered by ICminer.com Electronic-Library Service CopyRight 2003

Figure 2.5.1.3-1 the transmission of the break signal

#### 2.5.2. UART

The UART is used in transmission mode 2 of the EDRA. It is also used in transmission mode 1B, 1C, 3A, 3B, 3C to do the serial parallel conversion (and vice versa) as was discussed in section 2.5.1. In mode 1D the UART can be used to monitor the data from the DTE.

The UART that is part of the URF transmitter/receiver has the following capabilities:

- Receive buffer: 32 bytes FIFO.

- Transmit buffer: 32 bytes FIFO.

- Threshold levels for FIFO guarding are programmable (for different flow control situations).

- Split speeds 1200/75 only.

- All registers directly addressable.

- Receiver and transmit interrupt indication in general interrupt status register.

- 5/7/8 bits/char excluding parity.

- number of stop bits: one or two.

- odd, even ,mark ,space or no parity.

- break generation and detection.

- parity, overrun and framing error detection.

- Two basic I/O modes are supported: polling and interrupt driven.

#### 2.5.2.1. Asynchronous receive

The number of bits per character is controlled by the command-code register W11. Five, seven or eight bits per character may be selected also by this register. Data is right-justified (to the least significant bits) with the unused bits set to 1's. The parity of the transmitted character, and the parity check of a received character can be set to Even, Odd, Mark, Space and None. The parity bit is transferred to the receive FIFO with the data if the character length selected, including parity, is 8 bits or less and can be read out of register R27.

The receiver always checks for a stop bit. If after character assembly the stop is found to be '0', the framing error bit is set. This error bit is coupled to the data and can be read in register R27 before the data is read out.

The Break condition is continuous O's, as opposed to the usual continuous ones during idle. The EDRA recognizes the Break condition upon seeing a null character plus a framing error (see register R27). Upon recognizing this sequence the break bit will be set (register R27) and will remain set until a one is received. At this point the Break condition is no longer present. At the termination of a break the receive data FIFO contains a single null character which should be read and discarded. The Framing Error bit nor the Parity Error bit will be set for this character.

#### 2.5.2.2. Receive interrupts

The receive interrupts of the UART are enabled/disabled as a group by the Receive Interrupt Enable bit (register W4 RxGIE). If the interrupt capabilities are not needed, polling may be used. This is selected by disabling the receiver interrupts and polling the receiver status register (register R27). If receiver status is to be checked, it must be done before the data is read because reading the data pops both the data and error conditions belonging to that data.

The Group Interrupt Pending bit will always be set if one of the receiver activity detectors are set, but an interrupt will only be given if the source is enabled and the RxGIE is set.

### 2.5.2.3. Asynchronous transmit

The number of stopbits that will be transmitted can be selected in command-code register Wll. The setting of character length and parity are common to both the receiver and the transmitter. In all cases the data is in the least significant bits of the data word written by the processor.

The transmitter may be programmed to send a Break. To do this the Send Break bit (register W10) may be written by the processor. Setting of this bit causes the transmitter to transmit continuous 0's from the first transmit clock edge after the bit is set, until the first clock edge after this bit is reset. When this bit is set, the character that's currently beeing sent shall be corrupted and internally the Tx-FIFO is stopped to prevent lost of more characters. An additional status bit for use in asynchronous mode is the All Sent bit. This bit is set when the transmit shift register is empty and all previous data or stop bits have been shifted out. This bit can be used by the processor as an indication that the transmitter may be safely disabled.

### 2.5.2.4. Transmit interrupts

Transmit interrupts are controlled by the Transmit Group Interrupt Enable bit. There are a number of transmit interrupt sources: Tx-buffer empty, Tx-shift register all sent, overflow and, when enabled, the threshold interrupts.

If the interrupt capabilities are not required polling may be used. This is selected by a reset of the register W04 TxGIE bit and polling the Tx status and activity bits in register R20.

### 2.5.3. Flow control

The flow control function is used in transmission mode 1C of the EDRA.

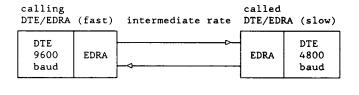

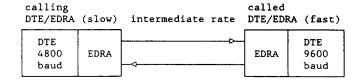

Flow control allows the connection of two EDRAs with asynchronous terminals operating at different user data rates, by reducing the character output of the faster to that of the slower terminal. Each EDRA has a data rate setting that is equal to the data rate of the DTE that it is connected to. Between the two EDRA/DTE combinations a rate difference may be present.

Data rate differences between the two EDRAs is taken care of by the end to end flowcontrol mechanism (manipulation of the X-bit in the data stream on the synchronous data interface). While the data transfer between EDRA and DTE is handled with local flow control. This local flow control can be performed by X-ON/X-OFF or by control of lead 106.

According to ECMA, the intermediate rate between the two EDRAs is determined by the calling EDRA. And so two situations be distinguished:

- A fast EDRA/DTE combination calls a slow EDRA/DTE combination;

- A slow EDRA/DTE combination calls a fast EDRA/DTE combination.

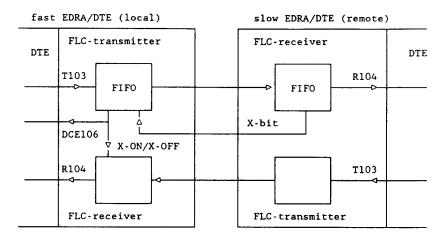

These two situations are illustrated in figure 2.5.3-1.

2.5.3-1 Examples of the two flow-control situations.

When a faster EDRA/DTE calls a slower EDRA/DTE, the situation is illustrated in figure 2.5.3-2:

Figure 2.5.3-2 Fast EDRA/DTE calls a slow EDRA/DTE.

In the FLC-receiver of the EDRA at the remote side, data on the synchronous data interface is coming in faster than it is going out to the DTE. The FIFO gets filled. When threshold level 1 is reached (see section 2.5.3.1) the X-bit is turned off ('1'). When the FLC-receiver of the local EDRA detects the X-bit to be turned off, transmission of data over the synchronous data interface is blocked. While data is still coming from the local DTE, the data in the FIFO at the local EDRA reaches the threshold level 1. (This threshold level is also reached is the local DTE transmits with overspeed.) At this point an interrupt (EDRA transmitter TH1) is generated (if enabled). When the command 'AUTO 106' has been given, the DTE will be stopped with lead DCE106. If the connected DTE can only handle XON/XOFF, also 'AUTO XON/XOFF' can be selected. After the local DTE has stopped transmitting data, and the remote EDRAs FIFO level has decreased below threshold level 2, the X-bit will be turned on. The FIFO level from the local EDRA will decrease and lead DCE106 becomes high or a X-ON character will be generated by the EDRA.

The remote control with the X-bit is called end-to-end flow control. The situation at the calling DTE/EDRA, caused by the end-to-end flow control and the overspeed of the DTE, is handled as local flow control.

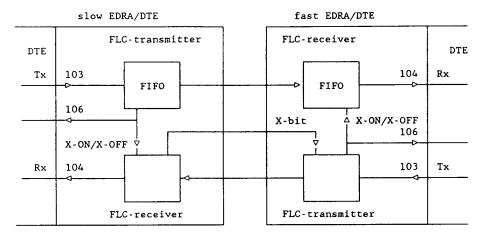

The second situation the calling DTE/EDRA (local) is slower as the called DTE/EDRA (remote). This situation is illustrated in figure 2.5.3-3.

Figure 2.5.3-3 Slow EDRA/DTE calls fast EDRA/DTE.

At the local side, the DTE can cause overspeed due to the fact that the intermediate is determined by the local EDRA. This overspeed is handled with local flow control.

The remote DTE transmits its data faster than the synchronous data interface can handle. Also this situation is solved with the local flow control procedure.

The X-bit in the data stream from local to remote DTE/EDRA is still used, but is continu ON ('0'), unless overspeed occurs because of insertion X-ON/X-OFF characters in the receiver at the local side.

### 2.5.3.1. Flow control FIFOs

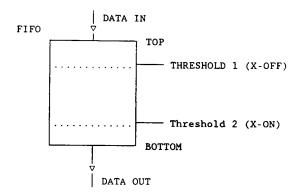

The FIFOs, which are used for flow control, have a capacity of 32 bytes. They are equiped with two threshold level detectors, which can be programmed in registers W12 and W14 (section 2.9.1). The threshold detectors give an indication if the contents of the FIFO is higher than level 1 or lower than level 2. An illustration of the FIFOs is given in figure 2.5.3.1-1.

Figure 2.5.3.1-1. Flow control FIFO.

For both receiver- and transmitter FIFO a threshold register is available to be able to program both threshold levels. The register is divided into two parts. The first part contains threshold level TH1 (4 bits), the second part contains threshold level TH2 (4 bits) (see section 2.9.1.13). Both thresholds can only have an odd values. With the four bits in the threshold register only the four most significant bits can be programmed. The least significant bit is always 1. So all odd threshold levels between 1 and 31 can be programmed.

### 2.5.3.2. FIFO threshold levels

The setting of the FIFO threshold levels concerning flow-control, depends on the type of data connection. Determining factors are whether the EDRA is on the calling or called side of a data connection, and if its DTE data rate is faster or slower than the data rate of the DTE at the remote EDRA.

Resuming, there are 4 different situations:

- 1. The EDRA is at the calling side of the connection, local DTE is faster than remote.

- 3. The EDRA is at the called side of the connection, local DTE is slower than remote.

- 4. The EDRA is at the called side of the connection, local DTE is faster than remote.

Each situation requires it specific setting of the threshold levels of the FIFOs. The settings are determined by the following characteristics:

- -Overspeed of the DTE;

- -DTE responce on lead 106 or X-OFF, the number of characters transmitted by the DTE after "X-OFF" or DCE106 LOW;

- -Local/remote DTE data rate difference;

- -Delay of the network.

Flow control can be used in different ways, automatically or microprocessor controlled. The flowcontrol mode can be set in write register W00 (section 2.9.1.1). The specific flowcontrol features can be selected in write register W11 (section 2.9.1.12). The monitoring of flowcontrol is performed by the FIFO threshold levels 1 and 2. When threshold level TH1 is reached, the incoming data must be stopped as soon as possible. When the level drops below threshold level TH2, the FIFO can accept data again.

#### 2.5.3.3. End to end flowcontrol

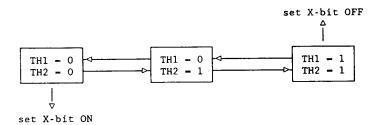

For end to end flowcontrol, the X-bit in the synchronous data interface frame controls the transfer of data via that interface. The end to end flow control can be automatically performed by the EDRA or can be managed by the microcontroller.

If the EDRA is in the automatic flow control mode the X-bit is switched ON and OFF according the values of the threshold levels TH1 and TH2 of the FLC-receiver. In figure 2.5.3.3-1 the switching of the X-bit is illustrated.

Figure 2.5.3.3-1 X-bit control by the threshold levels.

When the EDRA is not in automatic mode, the microcontroller must know the state of the FIFO thresholds of the FLC-receiver to be able to perform flowcontrol.

The threshold levels can be monitored by polling read register R20 (section 2.9.2.1) or if bit THD GIE of write register W04 is enabled and (TH1-0 and TH2-0) or (TH1-1 and TH2-1) an interrupt will be generated.

The microcontroller has to perform the following actions:

If an interrupt was generated and the interrupt source was the FLC-receiver THl or (in polling mode) THl = 0, the X-bit must be clamped '1' (OFF)

In an interrupt was generated and the interrupt source was the FLC-receiver TH2 or (in polling mode) TH2 = 1, the X-bit must be clamped '0' (ON)

The remote EDRA will stop the transmission of data on the synchronous data interface when the received X-bit is ON. When the received X-bit is OFF, it can restart transmission.

### 2.5.3.4. Local flowcontrol

If local flow control is performed in automatic mode the EDRA performs the folling actions:

When threshold level TH1 is reached at the FLC transmitter, the transmission of data from DTE to the EDRA must be stopped. If the FIFO level of the FLC transmitter drops below threshold level TH2, the DTE can start the data transmission again.

The EDRA can start and stop the transmission of the DTE data in two ways:

- -In the 'AUTO 106' mode lead DCE106 will be controlled by the flow control logic.

- -If the EDRA is in 'AUTO XON/XOFF' mode, character 'X-OFF' (DC3 ASCII) or 'X-ON' (DC1 ASCII) are inserted in the data, and transmitted via lead Tl04 to the DTE. The ASCII code for XON/XOFF can be downloaded in write registers W16 and W17).

If the local flowcontrol is performed by the microcontroller, the threshold levels TH1 and TH2 can be monitored by polling read register R20 (section 2.9.2.1) or if bit THD GIE of write register W04 is enabled and (TH1=0 and TH2=0) or (TH1=1 and TH2=1) an interrupt will be generated. The actions that must performed on the interrupt from TH1 and TH2 of the URF-transmitter are illustrated in figure 2.5.3.4-1.

| interrupt-<br>source | DTE reacts on<br>lead DCE106 | DTE reacts on<br>XON/XOFF character |

|----------------------|------------------------------|-------------------------------------|

| TH1 - 1              | clamp DCE106 to 1 (OFF)      | EDRA sends one X-OFF character      |

| TH2 - 0              | clamp DCE106 to 0 (ON)       | EDRA sends one X-ON<br>character    |

Figure 2.5.3.4-1 Local flowcontrol procedure by  $\mu$ C.

#### 2.5.3.5. X-ON/X-OFF

The X-ON and X-OFF characters can be downloaded by the microcontroller into register W16 and W17 (section 2.9.1). Only the data must be written, parity, start and stop bits will be auto generated by the EDRA according the settings in register W11 (section 2.9.1.12).

The X-ON/X-OFF characters are generated by the EDRA in the AUTO X-ON/X-OFF mode. However the X-ON/X-OFF characters can be inserted in the data stream on lead T104 by microcontroller (see register W11).

It is possible to filter the X-ON/X-OFF characters that are received on lead T103. This can only be done if they do not contain any parity and/or frame errors. This feature is needed when local flow-control is used with X-ON/X-OFF because if a X-ON/X-OFF character is transmitted to the remote EDRA/DTE, the local flow-control at this remote EDRA/DTE can be disturbed. These filter can prevent the transfer of X-ON/X-OFF characters in the data stream to the remote EDRA. The filters can be enabled/disabled by  $\mu C$  in write register Wll.

The default setting of the filters (when a transmission mode is selected in write register W00) is 'OFF' (no filtering). When in transmission mode 1C (flow-control) the AUTO X-ON/X-OFF mode will be selected, both filters will be active.

Two data switches are implemented in URF. One in the data path from T103 to SDO (just after the Rx-FIFO), and one in the data-flow from SDI to R104 (just after the Tx-FIFO). By switching the data switches the data flow inbvolved can be stopped.

Both switches can be independently enabled/disabled by the microcontroller, or be controlled by the X-bit from SDI for the Rx data switch and controlled by the X-ON/X-OFF character-detection (T103) for the Tx data switch.

The settings for control of the data switches are written in register Wll by microcontroller.

By selection of any transmission mode, both the Tx and Rx data switches will be enabled, except for transmission mode 1C. In this case the data switches will be controlled by the X-bit from the remote EDRA. When in transmission mode 1C 'AUTO X-ON/X-OFF' mode is selected, the Tx data switch will be default controlled by the X-ON/X-OFF character recognition.

In figure 2.5.3.5-1 the data paths of the EDRA in flowcontrol mode are illustrated.

Figure 2.5.3.5-1 Flow control in the EDRA.

#### 2.6. Inband Parameter Exchange

The EDRA allows transfer of parameter information within the user data stream of an established connection. This transfer of parameter information is called Inband Parameter Exchange (IPE). The EDRA supports the three different types of IPE that are recommended by ECMA-102:

- asynchronous IPE mode with RAO coded data in the 64 kbit/s channel (EDRAs transmission mode 3B).

- unrestricted synchronous IPE mode at 64kbit/s rate in the 64 kbit/s channel (EDRAs transmission mode 3C).

- restricted synchronous IPE mode at 56kbit/s rate in the 64 kbit/s channel (EDRAs transmission mode 3C).

and also is supported:

multiple sampling coded data in the 64 kbit/s channel (EDRAs transmission mode 3A).

In all four modes the transmit data is to be written into write register W15 while the received data must be read from read register R26.

### 2.6.1. Asynchronous IPE mode

In the asynchronous IPE mode, the data is RAO coded on an intermediate rate or 64 kbit/s channel. The number of data bits in a data byte, the number of stopbits and the parity bit should be programmed in the UART (see section 2.5.2).

In the ECMA recommendations IPE is specified for three speeds: 19200, 9600 and 4800 bit/s. The EDRA supports IPE for all RAO speeds. The interchange circuits can be used as in all other modes.

Data written to register W15 and is placed in the Tx-FIFO. Then it is shifted out on the synchronous data interface. When all data is transmitted, the transmitter starts sending l's until a new character is available for transmission.

The received data can be readout of the Rx-FIFO (read register R26).

### 2.6.2. Synchronous IPE mode at 64 kbit/s

The synchronous IPE function for unrestricted transfer. For this mode only one additional setting must be done in write register Wll: the character length should be set on 8 bits/char. Data written to register Wl5, will be placed in the Tx-FIFO and is shifted out on the synchronous data interface, without additions. When the Tx-FIFO is empty, the last byte that was transmitted, will be repeated until a new character is available.

The received data can be readout of the Rx-FIFO (read register R26).

#### 2.6.3. Restricted synchronous IPE mode at 56 kbit/s

The synchronous IPE function for restricted transfer. For the EDRA this mode is equal to unrestricted 64 kbit/s IPE mode.

For this mode only one additional setting must be done in write register W11: the character length should be set on 8 bits/char. Only the lowest 7 bits can be used in write register W15. The MSB should be set '1'. The data written to register W15, will be placed in the Tx-FIFO and is shifted out on the synchronous data interface, without additions. When the Tx-FIFO is empty, the last byte that was transmitted, will be repeated until a new character is available.

The received data can be readout of the Rx-FIFO (read register R26).

#### 2.6.4. Multiple sampling IPE mode

In the multiple sampling IPE mode, the data is coded according the multiple sampling method and placed in the 64 kbit/s channel. The number of data bits in a data byte, the number of stopbits and the parity bit should be programmed in the UART (see section 2.5.2).

The data that is written in register W15, will be placed in the Tx-FIFO and is shifted out to the multiple sampling coder. When all data is transmitted, the transmitter starts sending l's until a new character is available for transmission.

The received data can be readout of the Rx-FIFO (read register R26).

#### 2.7. Network independent clocking

When the EDRA must adapt synchronous data of which the timing is not synchronised to the EDRA timing, a method, called bit-stuffing is used to enable transfer of those data signals (for V-series only). The EDRA supports the NIC function as it is decribed in the ECMA-102/CCITT V.110 recommendations.

In this section the term modem-clock (on lead S113) will be used when the independent clock is meant and EDRA-clock (on lead S114) for the system locked clock.

The NIC function consists of the following parts:

- a phase comparator that measures the phase difference between the EDRA- and modem-timing and a buffer for transmit data.

- a coder that provides the E-bits in the synchronous data interface bitstream with compensation information.

- and a decoder to translate the incoming E-bits of the synchronous data interface to data and clock correction.

In figure 2.7-1 a blockdiagam is illustrated of the NIC transmitter while in figure 2.7-2 the NIC receiver is illustrated.

Figure 2.7-1 Block diagram of the NIC transmitter.

Figure 2.7.2 Block diagram of the receiver.

158

#### 2.7.1. NIC transmitter

The measurement of the phase difference:

The phase difference between the following two frequencies is measured (according to ECMA-102 recommendation):

R1 = 0.6 \* intermediate rate of the EDRA (synchronised to EDRA) R2 = 0.6 \* intermediate rate of the modem, derived from and synchronised to the modem signal element timing

The relation between R1, R2 and their intermediate rate is depicted in table 2.7.1-1.

| intermediate rate | R1,R2 |

|-------------------|-------|

| 8000              | 4800  |

| 16000             | 9600  |

| 32000             | 19200 |

Table 2.7.1-1 Nominal R1/R2 frequencies for given intermediate.

Phase measurements are given relative to R1 by the formula below:

PD (phase difference) = phase(R2) - phase(R1)

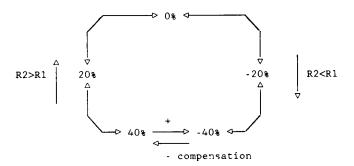

The system will know the next five phases: 0%, 20%, 40%, -40%, -20%. These phases will be coded and transmitted to the receiving EDRA in the E-field (of the 10 bytes frame).

Compensation:

The next drawing shows the states of the phase of R2 relative to R1.

Figure 2.7.1-2 Network independent clocking state diagram.

Every 10 bytes frame the EDRA connected to the modem codes the phase difference state into the E4, E5 and E6 positions of the E-field. To avoid continuous jitter in the transmitted code, it will be changed after an increased phase difference of 15% (of the R1 clock period). So, a code 000 (20%) will be changed in 001 (40%), when the measured phase difference is 35% or more, and changed in 111 (0%) when 5% or less.

In the case the data rate of the modem is higher than the rate of the EDRA the situation occurs that the phase difference is 40%. When the phase difference is 40%, the modem nearly transmits more information than the EDRA can handle. At a certain moment the phase difference will be 55%. This means that the EDRA will miss one data bit received from the modem. With the compensation method this bit will be transmitted in the E-bits. This is called positive stuffing and the transmitted code will indicate compensation of a binary 1 or 0.

In the case the data rate of the modem is lower than the rate of the EDRA the situation occurs that the phase difference is -40%. When the phase difference is -40%, the EDRA is nearly transmitting more information than the modem offers. At -40% to 40% transition the code indicates the receiving EDRA to 'stuff' a bit (negative compensation). In table 2.7.1-3 the coding of the E-bits used for network independent clocking is illustrated.

| Displacement (in % of nominal R1 clock period at n * 4800 bps, n=1, 2 or 4)                     |                  | Coding in the 80-bits frame |                  |  |  |

|-------------------------------------------------------------------------------------------------|------------------|-----------------------------|------------------|--|--|

| at ii ~ 4000 bps, n=1, 2 or 4)                                                                  | E4               | E5                          | E6               |  |  |

| nominally 0<br>+20<br>+40<br>-40<br>-20                                                         | 1<br>0<br>0<br>0 | 1<br>0<br>0<br>1<br>1       | 1<br>0<br>1<br>0 |  |  |

| Compensation control                                                                            | E4               | <b>E</b> 5                  | E6               |  |  |

| Positive compensation of binary 1<br>Positive compensation of binary 0<br>Negative compensation | 1<br>1<br>1      | 0<br>0<br>1                 | 1<br>0<br>0      |  |  |

Table 2.7.1-3 Coding of the E bits.

### 2.7.2. NIC receiver

The NIC receiver contains a decoder/phase shifter and a receiver data-mux. By means of the received frame, the phase of the receiver-clock (to DTE) must be changed in steps of 20%, as described in chapter 2.7.1.

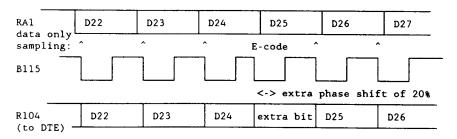

Figure 2.7.2-1 Positive compensation.

Figure 2.7.2-1 shows the received data (from the RA1) and the EDRA clock. In the previous frames the E4, E5 and E6 bits indicated a phase shift that resulted in a +40% clock. After bit D24 a new E-Field is received indicating positive-compensating of a bit. This results in new phase shift of the clock of 20% to +60% (-40%). The received data-mux now selects the extra bit coming from the E-Field. The next clock-edge will be just in time to sample bit D25. The achieved clock-delay will now be -40%.

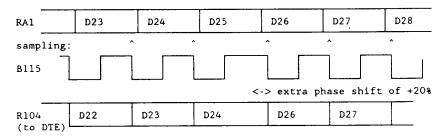

Figure 2.7.2-2 Negative compensation.

Figure 2.7.2-2 shows a -40% clock. The next received E-field indicate a negative compensation. This will result in an extra clock-delay of 20% to -60% (+40%). After this clock shift, bit D25 will be skipped.

The place in the framing where compensation takes place is bit D25. Positive compensation inserts a bit between D24 and D25, negative compensation deletes bit D25.

Max frequency deviation modem clock for 4800, 9600 and 19200 bit/s =  $\pm$ 0.347 % while the allowed jitter on modem clock for 4800, 9600 and 19200 bit/s is 1 bit jitter on 48 bits interval. This is a 1.97 % modem clock deviation, provided that the mean deviation over 48 bits is zero.

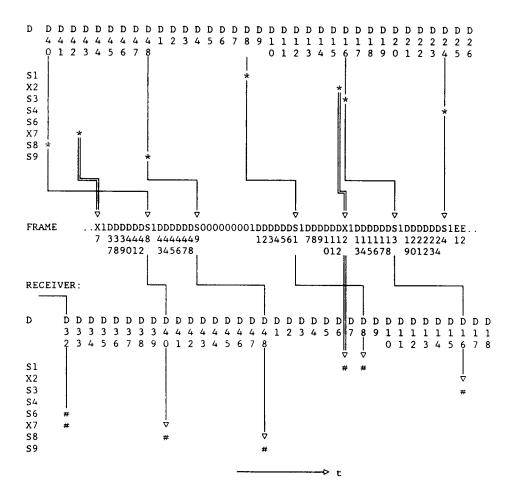

#### 2.8. Frame mapping/demapping and multiple sampling

### 2.8.1. Multiple sampling method

For asynchonous user data to synchronous 64 kbit/s conversion, the EDRA has the multiple sampling method available as it is implemented in its predecessor the PCB2320 DRA. Every asynchronous data rate lower than or equal to 19200 bit/s can be adapted without a specific speed setting on the EDRA (the local and remote DTE however should have the same data rate setting).

Concerning the interchange circuits, two points must be taken into account: The EDRA must be in X30-mode (see register W00, section 2.9.1.1). The relation between ON/OFF of the interchange circuits and the binary values of the S- and X-bits on the synchronous data interface should be according the ECMA-102 september definition (see section 2.3.2).

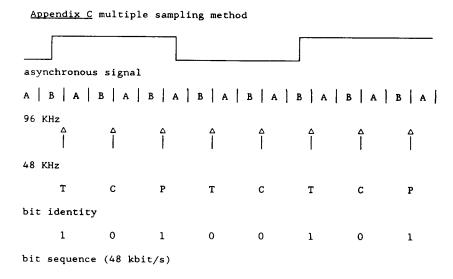

This coding/sampling method is based on the technique of multiple sampling with additional transition coding as depicted in CCITT recommendation R.111.

This method doesn't recognise character lenght or start-stop bits. It samples the incoming data with 96 kHz. Only transitions are coded in two bits: a transition bit T and coding bit C.

The transition bit T is used to indicate the polarity after a transition, and the second bit C (coding) defines in which half A or B of a 48 kbit/s clock period the transition has occurred. Transitions of data rates upto 24 kbit/s can be coded by the 48 kbit/s. Because one bit can discriminate two phases (A or B), the sampling frequency has to be 96 kHz.

In the lower data-rates, more than two 48 kHz pulses will fall between two signal element transitions. In this case the resulting 48 kbit databits P (polarity) will repeat the polarity and are therefore equal to the previous bit T.

The phase jitter on the received data stream varies for the different bit rates from 20 % for 19.2 kbit/s down to 2.5 % for 2400 bit/s or even lower for slow data.

The 48 kbit/s data stream is further handled as 48 kbit/s synchronous data stream.

In appendix C the multiple sampling method is illustrated.

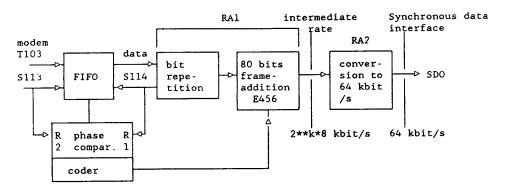

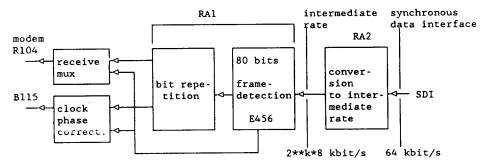

### 2.8.2. Frame mapping/demapping

For synchronous data rates of 600, 1200, 2400, 4800, 9600, 19200 and 38400 bit/s, a X.30/V.110 defined multiframe of 10 bytes bits is used (see appendix B). It consists of two 5 bytes frames, using subrates of 8, 16 and 32 kHz. An incoming data rate will be first translated to the next higher rate expressed by 2\*\*\*\*k\*\*\*8 kHz where k=[0,1,2,3] (see table 2.8.2-1). For speeds 600, 1200, 2400 a first rate adaption to 4800 bit/s is done by bit repetition. This first stage of rate adaption is called the RA1 function and is illustrated in figure 2.8.2-2.

| Data rate (bit/s)     | framespeed (Hz) |

|-----------------------|-----------------|

| 600, 1200, 2400, 4800 | 8000            |

| 9600                  | 16000           |

| 19200                 | 32000           |

| 38400                 | 64000           |

Table 2.8.2-1 First step in data rate adaption.

Figure 2.8.2-2 Bit rate adaption of synchronous data received from the RAO blocks and synchronous user data  $\leq 38400$  bit/s.

The multiframe consists of 10 bytes containing 8\*6 data bits, 8 S-bits, two X-bits, 17 bits for the frame synchronisation pattern and 7 E-bits used for the following purposes:

| E1 | E2                   | E3 | E4 | E5                   | E6 | É7                                     |

|----|----------------------|----|----|----------------------|----|----------------------------------------|

|    | i indica<br>remote l |    |    | rk inder<br>ing code |    | 600 and 1200 bit/s multiframe syncbits |

The three speed indication bits can be filled in via the  $\mu$ C-interface and are transmitted to the remote EDRA transparently. The E4 to E6 bits are used to transmit the positive or negative bit-stuffing coding. Bit E7 is used for slow-data synchronisation purposes (see section 2.9.1.4).

The data rate conversion is completed after the conversion of the intermediate rate to 64 kbit/s by block RA2 as illustrated in figure 2.8.2-2.

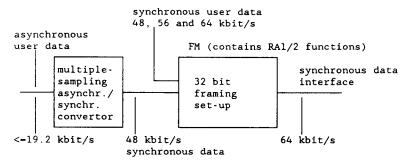

The 48, 56 and 64 kbit/s synchronous user data are adapted to 64 kbit/s in one step using a 32 bit frame. Asynchronous user data  $\leq$  19200 bit/s, that is coded with the multiple sampling method, is also inserted at this level as a 48000 bit/s data stream. In figure 2.8.2-3 this rate adaption stage is illustrated.

164

Figure 2.8.2-3 Bit rate adaption of synchronous user data  $\geq$ =48000 bps and asynchronous user data (multiple sampling).

For the data rate of 48000 bit/s a 32 bits frame is used (see appendix B). This frame consists of 4 bytes containing 4\*6 data bits, 3 S-bits, one X-bit and 4 frame synchronisation bits.

For the data rate of 56000 bit/s the 32 bits frame structure is used (see appendix B). Only now 4\*7 bits consist for data and four S-bits. No frame bits for synchronisation can be used.

For the data rate of 64000 bit/s no rate adaption is needed and the DRA is transparent for this speed (see appendix B).

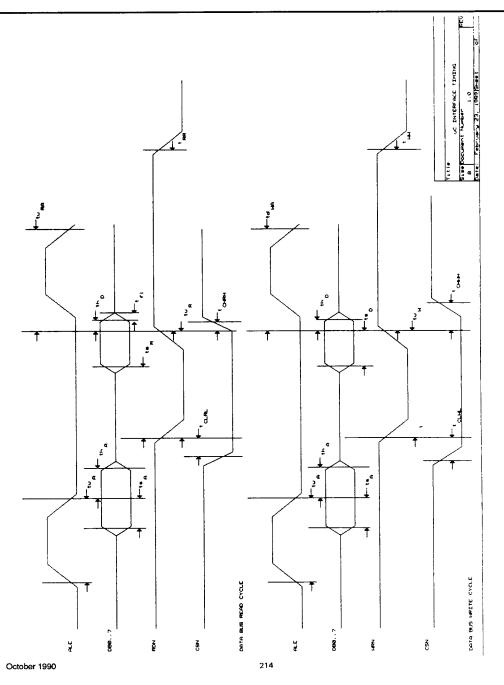

### 2.9. Microcontroller interface

The EDRA is controllable by the 8-bit INTEL compatible microcontroller bus.

The bus consists of:

- \* 8 data/address multiplexed I/O lines (DB7 to DB0)

- \* A read not input (RDN)

- \* A write not input (WRN)

- \* An address latch enable input (ALE)

- \* A chip select not input (CSN)

- \* An interrupt not open drain output (INTN)

When ALE is HIGH and the EDRA is selected, the address on the DB7-DB0 I/O port is latched into the address latch. One of the eightteen write registers or one of the nine read registers may be selected (see table 2.9-1). This selection is made by the five least significant data/address lines (DB0-DB4) and the CSN signal whereby the EDRA is selected by CSN and register is selected by the address lines.

When RDN is LOW the EDRA writes the data byte from the selected read register to the data-bus I/O port. On the leading edge of WRN, the data-byte from the data-bus I/O port is written into the addressed write register.

| DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 | address | write reg  | read reg |

|-----|-----|-----|-----|-----|-----|-----|-----|---------|------------|----------|

| х   | х   | х   | 0   | 0   | 0   | 0   | 0   | 0       | wo         | -        |

| Х   | X   | Х   | 0   | 0   | 0   | 0   | 1   | 1       | W1         | -        |

| l x | X   | X   | 0   | 0   | 0   | 1   | 0   | 2       | W2         | -        |

| Х   | Х   | Х   | 0   | 0   | 0   | 1   | 1   | 3       | W3         | -        |

| Х   | Х   | Х   | 0   | 0   | 1   | 0   | 0   | 4       | W4         | -        |

| Х   | Х   | X   | 0   | 0   | 1   | 0   | 1   | 5       | W5         | -        |

| Х   | Х   | X   | 0   | 0   | 1   | 1   | 0   | 6       | W6         | -        |

| Х   | Х   | Х   | 0   | 0   | 1   | 1   | 1   | 7       | <b>W</b> 7 | -        |

| Х   | Х   | X   | 0   | 1   | 0   | 0   | 0   | 8       | W8         | -        |

| Х   | X   | X   | 0   | 1   | 0   | 0   | 1   | 9       | W9         | -        |

| Х   | X   | Х   | 0   | 1   | 0   | 1   | 0   | 10      | W10        | -        |

| х   | X   | Х   | 0   | 1   | 0   | 1   | 1   | 11      | W11        | -        |

| Х   | X   | X   | 0   | 1   | 1   | 0   | 0   | 12      | W12        | -        |

| х   | X   | Х   | 0   | 1   | 1   | 0   | 1   | 13      | W13        | -        |

| x   | Х   | X   | 0   | 1   | 1   | 1   | 0   | 14      | W14        | -        |

| Х   | Х   | X   | 0   | 1   | 1   | 1   | 1   | 15      | W15        | -        |