# Microcomputer for multi-key remote controllers

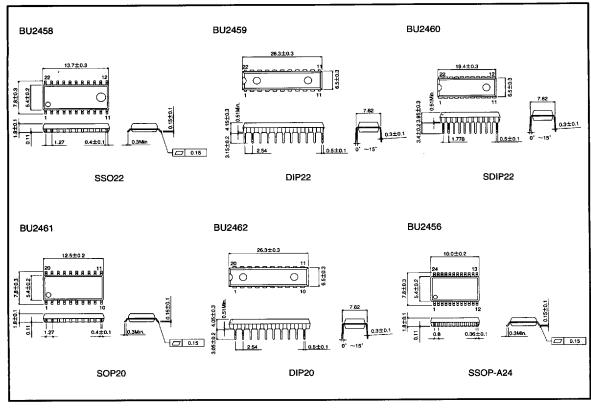

# BU2456/BU2458/BU2459/BU2460/BU2461/BU2462

The BU2458 series are four-bit, single-chip microcomputers on which all of the functions required for a remote control transmitter can be configured on a single chip, which can be used as a microcontroller for a remote control encoder.

These are ideal for keeping system sizes compact, keeping prices low, and building sophisticated functions.

#### Applications

Remote control encoders

## Specification

| Series                        | BU2456/BU2458/BU2459/BU2460     | BU2461/BU2462      |  |

|-------------------------------|---------------------------------|--------------------|--|

| Program memory (ROM) (bytes)  | 1024                            | 1024               |  |

| Data memory (RAM) (bits)      | 32×4                            | 32×4               |  |

| Subroutine nesting levels     | 3                               | 3                  |  |

| Instruction sets              | 43                              | 42                 |  |

| Large-current output port     | 1                               | 1                  |  |

| Input ports                   | 4                               | 4                  |  |

| Output ports                  | 8                               | 8                  |  |

| I/O ports                     | 4                               | 2                  |  |

| Instruction cycle ( µs)       | 13.2 (f <sub>OSC</sub> =455kHz) | 13.2 (fosc=455kHz) |  |

| Power supply voltage (V) typ. | 3                               | 3                  |  |

#### Features

- Five types of internal carrier generator circuits for infrared remote control signals (selectable via program)

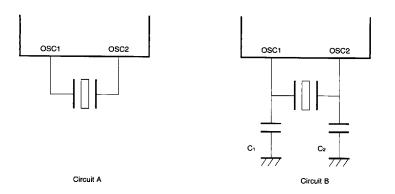

- Internal capacitor for ceramic oscillation circuit (mask option)

- 3) Internal watchdog timer

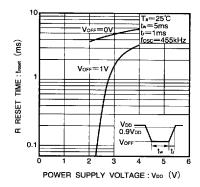

- 4) Internal Power On Reset function

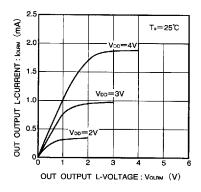

- Large-current output port (for remote control signal output)

- 6) Clock frequency: 300kHz ~ 1MHz

- 7) Program memory (ROM) of 1024 bytes

- 8) Data memory (RAM) of 32 × 4 bits

- 9) 3 levels of subroutine nesting

- 10) 4-bit input ports (for key scanning)

- 4-bit input/output ports (for key scanning and expansion pins)

- 12) 8-bit individual output ports (for key scanning)

- 13) Instruction cycle of 13.2  $\mu$ s (when fosc = 455kHz)

- HALT function can be cancelled through key input

|     | 7828999 | 0057755 | 666 |  |

|-----|---------|---------|-----|--|

| 448 |         | ROHM    |     |  |

# ●Absolute maximum ratings (Ta=25°C)

| Parameter Symbol Limits                                                 |                  | Limits                    | Unit |

|-------------------------------------------------------------------------|------------------|---------------------------|------|

| Power supply voltage                                                    | V <sub>DD</sub>  | -0.3~5.0                  | ٧    |

| 550*1 (BU2458/BU2461)<br>600*2 (BU2459/BU2460/BU2462)<br>800*3 (BU2456) |                  | mW                        |      |

| Storage temperature                                                     | T <sub>stg</sub> | <b>−55∼</b> +125          | °C   |

| Input voltage                                                           | Vin              | -0.3~V <sub>DD</sub> +0.3 | ٧    |

| Output voltage                                                          | Vout             | -0.3~V <sub>DD</sub> +0.3 | ٧    |

- \*1 Reduced by 5.5mW for each increase in Ta of 1  $^{\circ}\text{C}~$  over 25  $^{\circ}\text{C}~.$

- \*2 Reduced by 6mW for each increase in Ta of 1°C over 25°C.

- \*3 Reduced by 8.0mW for each increase in Ta of 1  $^{\circ}$  over 25  $^{\circ}$ C.

#### Recommended operating conditions

| Parameter             | Symbol           | Limits               | Unit |

|-----------------------|------------------|----------------------|------|

| Power supply voltage  | $V_{DD}$         | 2.0~4.0              | V    |

| Operating temperature | T <sub>opr</sub> | -25~ <del>+</del> 75 | °C   |

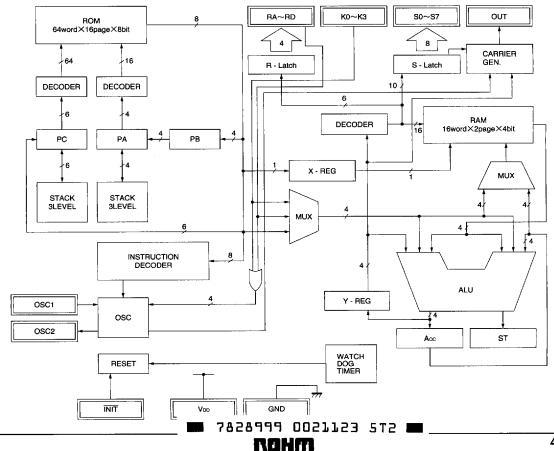

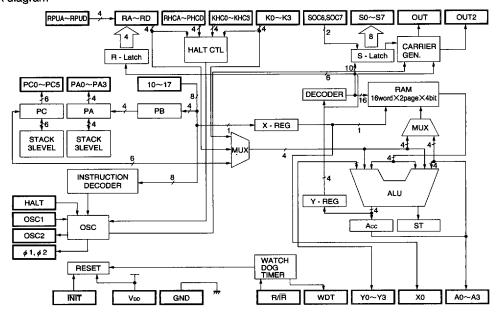

# Block diagram

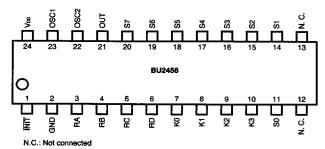

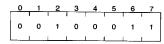

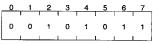

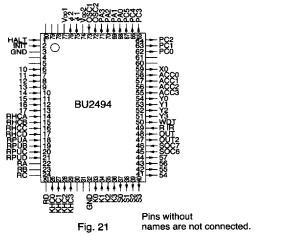

BU2456 pin layout

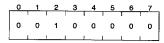

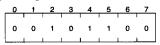

BU2458 pin layout

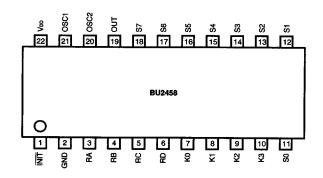

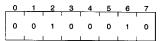

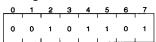

BU2459 pin layout

7828999 0021124 439

450

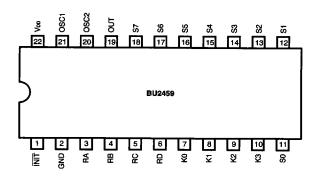

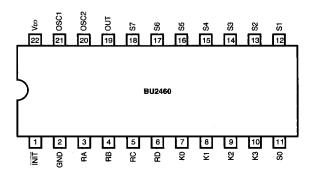

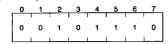

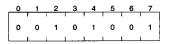

BU2460 pin layout

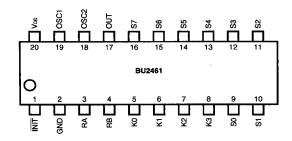

BU2461 pin layout

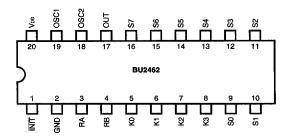

BU2462 pin layout

**■ 7828999 0021125 375 ■**

#### Pin description

| Pin Name        | I/O          | Function                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>DD</sub> | _            | Used to connect 2.0 V ~ 4.0 V power supply.                                                                                                                                                                                                                                                                                                                                               |

| GND             | _            | Reference voltage for all inputs and outputs (0 V).                                                                                                                                                                                                                                                                                                                                       |

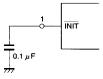

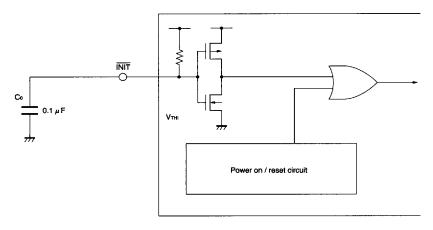

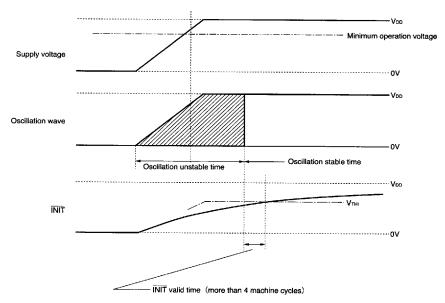

| INIT            | Input        | Manual reset input. Setting this pin to LOW initializes the S output ports and OUT output ports to LOW and sets the ROM address to 0 page, 0 address.                                                                                                                                                                                                                                     |

| К0∼К3           | Input        | 4-bit input ports. Internal pull-up resistance. A mask option can be used to select whether or not the HALT cancel function is to be effective for each individual bit (when the HALT function is effective, the HALT status is cancelled by setting this to LOW).                                                                                                                        |

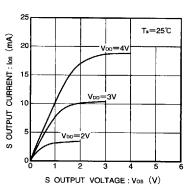

| S0~S7           | Output       | Each of these can be set and reset independently (or all at once). The output format is Nch open drain.                                                                                                                                                                                                                                                                                   |

| RA~RD           | Input/output | 4-bit input/output ports (however, these are set in input mode if a HIGH state is output for any respective pin). The outputs can be set and reset independently (or all at once). The output format is Nch open drain. A mask option can be used to selected whether or not the HALT cancel function is to be effective (by setting this to LOW) and whether pull-up resistance is used. |

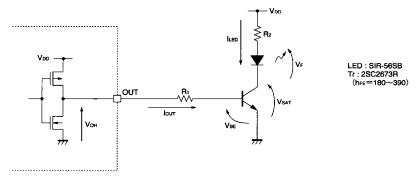

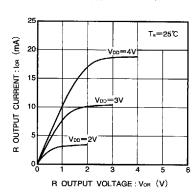

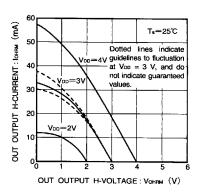

| OUT             | Output       | Remote control signal output port which can be used to drive large currents. The output format is CMOS output. The output HIGH current side can be used to drive large currents.                                                                                                                                                                                                          |

| OSC1            | Input        | A ceramic resonator is connected between this pin and OSC2. Built-in feedback resistor between this pin and OSC2.                                                                                                                                                                                                                                                                         |

| OSC2            | Output       | A ceramic resonator is connected between this pin and OSC1.                                                                                                                                                                                                                                                                                                                               |

Note: There are no RC or RD pins in the BU2461 and BU2462.

7828999 0021126 201 **...**

# ●Input/output circuit

| Pin Name | 1/0          | I/O Circuit | Notes                                                                                                    |

|----------|--------------|-------------|----------------------------------------------------------------------------------------------------------|

| INIT     | Input/output |             | Hysteresis input<br>Internal pull-up resistance<br>About. 400 kΩ                                         |

| RA~RD    | Input/output |             | Open drain output<br>HIGH on reset<br>(optional)<br>Internal MOS Tr for pull-up<br>About. 120 kΩ         |

| ко~кз    | Input        |             | Internal MOS<br>Tr for pull-up<br>About. 120 kΩ                                                          |

| S0~S7    | Output       | >           | Open drain output<br>LOW on reset                                                                        |

| OUT      | Output       |             | CMOS output<br>LOW on reset  Output HIGH current side ca<br>drive large currents                         |

| OSC2     | Output       | OSCSTB OSC2 | Internal MOS Tr for feedback Rf: About. 1 M $\Omega$ Internal damping resistance Rd: About. 6 k $\Omega$ |

| OSC1     | Input        | C1 # HR C2  | (optional) Internal capacitors can be provided for oscillation C1: About. 100 pF C2: About. 100 pF       |

Note: There are no RC or RD pins in the BU2461 and BU2462.

Circled items are mask options.

ROHM

453

●Electrical characteristics (Unless otherwise noted, Ta=25°C, VDD=3V)

| Parameter                       | Symbol             | Min. | Тур.             | Max. | Unit | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------------------------|--------------------|------|------------------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

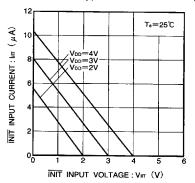

| INIT input current (HIGH)       | Інл                | _    | _                | 1    | μA   | $V_i = V_{DD}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| INIT input current (LOW)        | lilit              | -3   | <b>-7.5</b>      | -16  | μА   | V <sub>I</sub> =GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

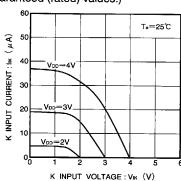

| K input current (HIGH)          | Інк                | _    | -                | 1    | μA   | V <sub>i</sub> =V <sub>DD</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| K input current (LOW)           | l <sub>ILK</sub>   | -9   | -25              | -50  | μΑ   | V <sub>I</sub> =GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| K input voltage (HIGH)          | V <sub>IHK</sub>   | 2.1  |                  | 3    | V    | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| K input voltage (LOW)           | VILK               | 0    |                  | 0.9  | V    | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

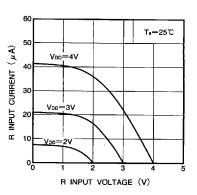

| R input current (HIGH)          | lihe               | _    | <b>—</b>         | 1    | μΑ   | V <sub>I</sub> =V <sub>DD</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| R input current 1 (LOW)         | liLR1              | -    | -0.1             | -1   | μA   | Vi = GND, output OFF, no pull-up resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| R input current 2 (LOW)         | l <sub>ILR2</sub>  | -9   | -25              | -50  | μA   | Vi = GND, output OFF, no pull-up resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| R input voltage (HIGH)          | VIHR               | 2.1  | † <del>-</del> - | 3    | v    | - Parity of the parity for the parit |

| R input voltage (LOW)           | VILR               | 0    | _                | 0.9  | ٧    | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| INIT input voltage (HIGH)       | VIHI               | 2.25 |                  | 3    | V    | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| INIT input voltage (LOW)        | VILI               | 0    | T -              | 0.75 | V    | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| R input voltage (LOW)           | Volr               | _    | 0.15             | 0.4  | v    | I <sub>DL</sub> =1mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| S input voltage (LOW)           | Vols               | _    | 0.15             | 0.4  | V    | lot=1mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| OUT output voltage (LOW)        | Volot              | _    | 0.15             | 0.4  | V    | I <sub>OL</sub> =100 μA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| OUT output voltage (HIGH)       | Vонот              | 2.1  | 2.5              | _    | V    | I <sub>OH</sub> = —8mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| OSC2 output voltage (LOW)       | Volos              |      | 0.4              | 0.9  | V    | I <sub>OL</sub> =70 μA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| OSC2 output voltage (HIGH)      | Vonos              | 2.1  | 2.5              |      | V    | I <sub>OH</sub> =-70 μA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| R output leakage current        | ILR                | _    | _                | 1    | μA   | Vo = Vpp, output OFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| S output leakage current        | lıs                | _    | _                | 1    | μA   | Vo = Vob, output OFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| OSC1 feedback current           | losc <sub>1</sub>  | 1    | 3                | 7    | μA   | When Vosc1 = GND, Vosc2 = VDD, in HALT mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Static current consumption      | I <sub>DDST</sub>  | _    |                  | 1    | μA   | In HALT mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Operating current consumption 1 | I <sub>DDOP1</sub> |      | 0.3              | 1.0  | mA   | When fosc = 455 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Operating current consumption 2 | IDDOP2             | _    | 0.25             |      | mA   | External clock of 1 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Operating frequency             | fosc               | 300  |                  | 1000 | kHz  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Oscillation capacitance 1       | C1                 |      | 100              | _    | pF   | When using internal capacitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Oscillation capacitance 2       | C2                 | _    | 100              | _    | pF   | When using internal capacitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 7828999 | 0051758 | 084 |  |

|---------|---------|-----|--|

|         |         |     |  |

454

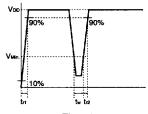

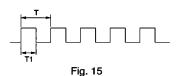

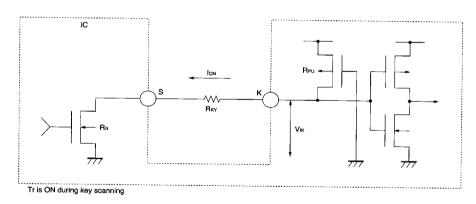

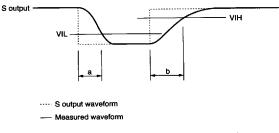

# Measurement circuits

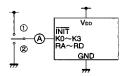

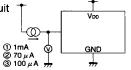

- ① Input current (HIGH) measurement circuit

- ② Input current (LOW) measurement circuit

Fig. 1

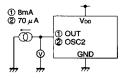

- 1 S output, R output voltage (LOW) measurement circuit

- 2 OSC2 output voltage (LOW) measurement circuit

- ③ OUT output voltage (LOW) measurement circuit (When testing, Nch transistor should be on.)

Fig. 2

- 1) OUT output voltage (HIGH) measurement circuit

- ② OSC2 output voltage (HIGH) measurement circuit (When testing, Pch transistor should be on.)

Fig. 3

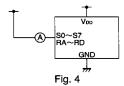

R output, S output leakage current measurement circuit (When testing, Nch transistor should be on.)

OSC1 feedback current measurement circuit

Static current consumption measurement circuit (Test in HALT mode, using HALT instruction to enter mode.)

■ 7828999 0021129 Tlo ■

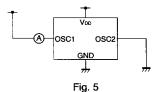

Operating current consumption measurement circuit

Note: There are no RC or RD pins in the BU2461 and BU2462.

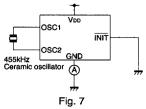

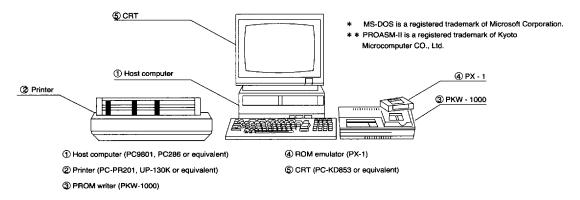

# Application example

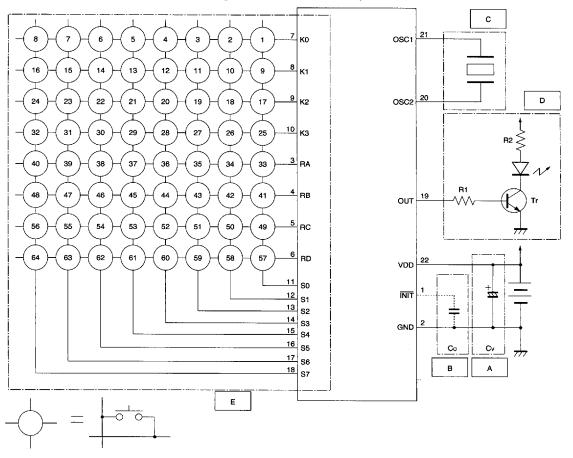

This typical application example shows the BU2458 as the base chip in the remote control encoder shown below.

Fig. 8 Application circuit example (64-key remote control unit)

The following is a guide to peripheral circuits (A to E in the above diagram).

A: Power supply circuit

B: Initial reset circuit C: Oscillation circuit

D: Infrared LED drive circuit

E: Key scan circuit

There are no RC or RD pins in the BU2461 and

BU2462.

**7828999 0021130 732**

456

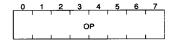

#### Mask options

With the BU2456, BU2458, BU2459, BU2460, BU2461, and BU2462, the following options can be selected:

- The watchdog timer can be reset (or not reset) using the OUT output signal.

- (2) The following input pins are equipped with a HALT cancel function: K0, K1, K2, K3, RA, RB, RC. RD.

- (3) The following input/output pins are equipped with pull-up resistance: RA, RB, RC, RD.

- (4) An internal capacitor can be provided (or not) for a ceramic oscillation circuit.

- (5) Output states in HALT mode

- S6: LOW state (values prior to HALT state are retained)

- S7: LOW state (values prior to HALT state are retained)

# ●HALT function

The HALT state can be initiated by executing the HALT instruction. In the HALT state, the following apply:

- Oscillation stops, enabling an extremely low current consumption.

- (2) The watchdog timer (WDT) is reset, and the S and OUT outputs go to LOW state.

(3) All values other than the WDT, S output and OUT output retain the values in effect prior to the HALT state.

However, the state of the S6 output and S7 output in the HALT mode can be selected using the mask options.

- (A): Sets LOW state.

- The values in effect prior to the HALT state are maintained.

The HALT cancel function can be specified independently for each bit of the K inputs and R inputs, using the mask options.

If even one of the K inputs or R inputs has been set to LOW, the HALT state is cancelled.

If the HALT state is cancelled, the following occur:

- The S output and OUT output values return to the values in effect prior to the HALT state.

- 2) In order to prevent operation before oscillation has stabilized, a wait timer is activated, and normal operation is then initiated after 1024  $\times$  6 effective clock pulses.

- 3) At the point where normal operation is resumed, the WDT begins to count again from 0.

For K inputs and R inputs equipped with the HALT cancel function, if a LOW state has been input, the HALT instruction has the same effect as the NOP instruction.

7828999 0021131 679

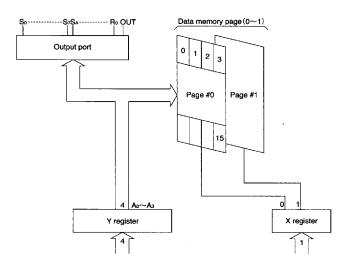

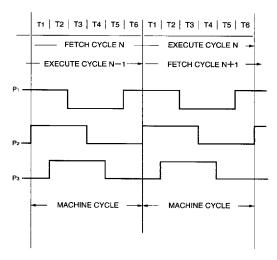

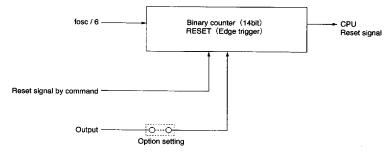

# Description of the block diagram

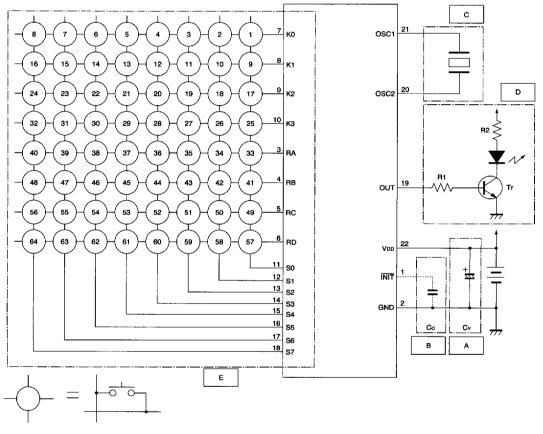

# (1) Program memory (ROM)

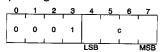

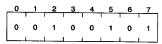

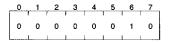

An internal ROM of 1024 words (64 words  $\times$  16 pages  $\times$  8 bits) for application software programs can be provided.

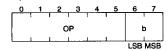

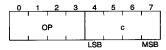

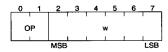

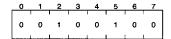

The scope of the program memory consists of the program counter PC ( $A_0 \sim A_5$ ) and the page address register PA ( $A_6 \sim A_9$ ), which are used to specify the address of the program register containing the next instruction (8 bits) to be executed.

The program memory is configured with one page consisting of 64 words, so that a maximum of 64 instructions can be stored on one page.

With evaluation chips, the ROM is attached externally, which makes it possible to carry out debugging and simulations of the pertinent system program. The program memory configuration is shown in Figure 9.

Fig. 9 Program memory configuration

| 7828999 00211<u>3</u>2 505

458

ROHIT

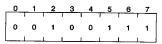

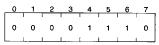

## (2) ROM address registers

The following registers are available to specify ROM addresses.

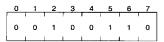

- 1) Page address register (PA)

- This contains the page numbers for the specified address in the ROM. The contents of the PA (4 bits) are decoded by a page decoder as one of 16 address lines.

- 2) Page buffer register (PB)

New addresses are loaded into the PB, and are then shifted to the PA when the correct branch (BR) and subroutine call (CAL) are executed. The LPC instruction is used to load the PB.

- 3) Program counter (PC)

- This is used for word addresses on ROM pages. One instruction is selected by the page decoder from among the contents of the PC (6 bits).

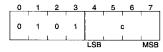

- 4) Stack register (SR)

- This stores return word addresses in the Call Sub-routine mode.

- 1. Page address register and page buffer register The range of  $0 \sim 15$  pages in the ROM is defined by latching the four bits specifying the ROM page address. The page address register differs from the program counter in that normally it does not change. As long as the Page Change instruction is not executed, the program continues to remain on the same page. To change the page address requires a two-step operation: ① write the page to which the program execution is to jump in the page buffer (execute the

LPC instruction), and ② execute the BR or CAL instruction.

This is necessary because the instruction code consists of 8 bits, and the page and word cannot be specified at the same time.

If the return instruction (RTN) from a subroutine in a subroutine called from another page is executed, the page address is changed at the same time.

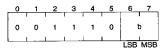

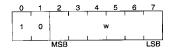

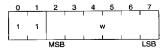

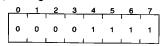

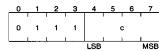

#### Program counter