# **HV255**

## **PRELIMINARY**

May 1991

## Half Bridge Complementary MOSFET Driver

#### Features

| • | Bipolar | or | Unipolar | Supply | Operation |

|---|---------|----|----------|--------|-----------|

|---|---------|----|----------|--------|-----------|

- Wide Supply Range ..... ±40V to ±225V

- Complete MOSFET Protection

- High Output to Logic Supply Isolation

- High Peak Output Current ......2A

- Frequency Range .................10kHz to 100kHz

## **Applications**

- High Switchmode Power Supplies

- PWM Servo Drives

- Stepper Motor Drives

- DC-DC Converters

- Uninterruptible Power Supplies

## Ordering Information

| PART<br>NUMBER | TEMPERATURE<br>RANGE           | DESCRIPTION        |  |

|----------------|--------------------------------|--------------------|--|

| HV255CP        | 0°C ≤T <sub>A</sub> ≤ +75°C    | 16 Pin Plastic DIP |  |

| HV255IP        | -40°C ≤ T <sub>A</sub> ≤ +85°C | 16 Pin Plastic DIP |  |

| HV255MJ*       | -55°C ≤ T <sub>A</sub> ≤+125°C | 16 Pin Ceramic DIP |  |

## Description

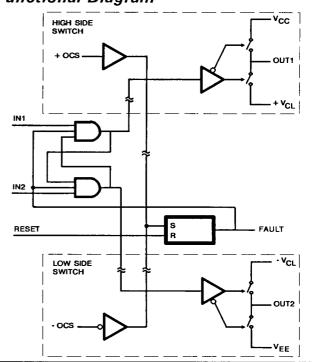

The HV255 is a monolithic dielectrically isolated high voltage integrated circuit. The circuit provides an interface from digital signals to the gates of complementary power MOSFETs or IGBTs. The circuit has wide supply voltage range, from 80VDC to 450VDC in unipolar connection or +40VDC to +225VDC. In addition the logic supply can float within the high voltage rails.

The inputs are TTL compatible when the logic supply is 5V, but will operate up to 15V logic supply.

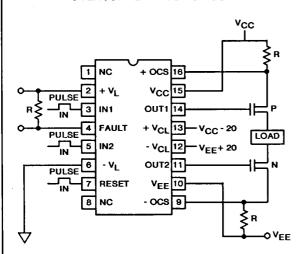

The outputs provide up to 2A current spikes to drive the gates of power MOSFETs or IGBTs. The actual voltage that the gates are driven to is set by the user, up to 20V for VGS.

Also on board the chip is an overcurrent sense circuit, which independently sense overcurrent on the high side and the low side. An overcurrent condition sets a latch that disables both outputs. In order to enable the output the reset input must be toggled.

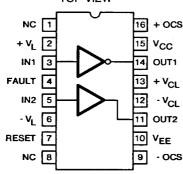

## **Pinout**

## HV255CP (16 PIN PLASTIC DIP) TOP VIEW

## Functional Diagram

CAUTION: These devices are sensitive to electrostatic discharge. Proper I.C. handling procedures should be followed. Copyright © Harris Corporation 1991 \* Offered at a later date.

File Number

2847

## Specifications HV255

| Absolute Maximum Ratings                            | Operating Temperature Range                             |

|-----------------------------------------------------|---------------------------------------------------------|

| Voltage Between +VS and -VS500V                     | HV255CP 0°C < T <sub>A</sub> < +75°C                    |

| Voltage Between +V <sub>1</sub> and -V <sub>1</sub> | HV255IP40°C < TA < +85°C                                |

| Voltage Between -VS and -VI                         | HV255MJ*55°C < T <sub>A</sub> < +125°C                  |

| Peak Output Current 2A                              | Storage Temperature Range65°C < T <sub>A</sub> < +150°C |

| Logic Input Voltage+Vi                              | Maximum Junction Temperature+175°C                      |

| Over Current Sense to VS                            | ,                                                       |

| Fault Output Current 1mA                            | * Offered at a Later Date                               |

Electrical Specifications  $V_{CC} = +40V$ ,  $V_{EE} = -40V$ ,  $C_L = 10$ nF,  $V_L = 5V$  Unless Otherwise Specified

|                                                          |                 | HV2                  | HV255CP, HV255IP |                      |       |

|----------------------------------------------------------|-----------------|----------------------|------------------|----------------------|-------|

| PARAMETER                                                | ТЕМР            | MIN                  | TYP              | MAX                  | UNITS |

| INPUT CHARACTERISTICS                                    |                 | <u> </u>             |                  | <del></del>          | •     |

| Input Voltage, High (VIH)                                | Full            | 2.4                  | _                | T -                  | l v   |

| Input Voltage, Low (VIL)                                 | Full            | _                    | _                | 0.8                  | v     |

| Input Current (I <sub>IH</sub> )                         | +25°C           | -                    | _                | 300                  | μΑ    |

|                                                          | Full            | _                    | _                | 300                  | μА    |

| Input Current, Low (I <sub>IL</sub> )                    | +25°C           | 150                  | _                | _                    | μА    |

|                                                          | Full            | 150                  | -                | _                    | ДA    |

| Overcurrent Input Threshold                              | +25°C           | 80                   | 100              | 120                  | mV    |

|                                                          | Fuli            | 75                   | 100              | 125                  | mV    |

| TRANSFER CHARACTERISTICS                                 |                 |                      |                  | •                    | *     |

| Turn-On Delay (T <sub>D1</sub> , T <sub>D3</sub> )       | +25°C           | -                    | -                | 1                    | μѕ    |

|                                                          | Full            | -                    | -                | 1                    | μs    |

| Turn-On Delay Skew (T <sub>D1</sub> , T <sub>D3</sub> )  | +25°C           | -                    | ±300             | _                    | ns    |

|                                                          | Full            | _                    | ±300             | -                    | ns    |

| Turn-Off Delay (T <sub>D2</sub> , T <sub>D4</sub> )      | +25°C           | _                    | -                | 1                    | μs    |

|                                                          | Full            | _                    | -                | 1                    | μs    |

| Turn-Off Delay Skew (T <sub>D2</sub> , T <sub>D4</sub> ) | +25°C           | _                    | ±100             | -                    | ns    |

|                                                          | Full            | _                    | ±100             | -                    | ns    |

| Current Limit Sense to Output Turn-Off Delay             | +25°C           | -                    | 500              | -                    | ns    |

|                                                          | Full            | _                    | 500              | _                    | ns    |

| Current Limit Sense to Fault Output Turn-Off Delay       | +25°C           | 50                   | -                | 150                  | ns    |

|                                                          | Full            | 50                   | -                | 150                  | ns    |

| Reset Delay (T <sub>D6</sub> )                           | +25°C           | -                    | 500              | _                    | ns    |

|                                                          | Full            | _                    | 500              | -                    | ns    |

| OUTPUT CHARACTERISTICS                                   |                 |                      |                  |                      |       |

| Output Rise Time                                         | Full            | -                    | 100              | 150                  | ns    |

| Output Fall Time                                         | Full            | -                    | 100              | 150                  | ns    |

| OUT1 Voltage (High)                                      | Full            | +V <sub>S</sub> -0.2 | -                | -                    | V     |

| OUT1 Voltage (Low)                                       | Full            | -                    | -                | +V <sub>S</sub> -19  | V     |

| OUT2 Voltage (High)                                      | Full            | -V <sub>S</sub> +19  | -                |                      | V     |

| OUT2 Voltage (Low)                                       | Full            | -                    | -                | -V <sub>S</sub> +0.2 | V     |

| Fault Output (VOH)                                       | Full            | 4.5                  | -                | -                    | V     |

| Fault Output (V <sub>OL</sub> )                          | Full            |                      | _                | 0.8                  | V     |

| POWER SUPPLY                                             | ··· <del></del> |                      |                  |                      |       |

| lcc                                                      | Full            | -                    | -                | 200                  | μА    |

| <sup>1</sup> EE                                          | Full            | -                    | -                | 200                  | μΑ    |

| IL.                                                      | Full            | -                    | -                | 4                    | mA    |

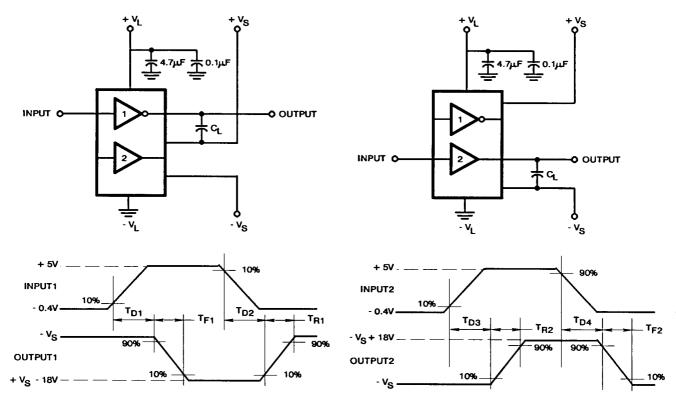

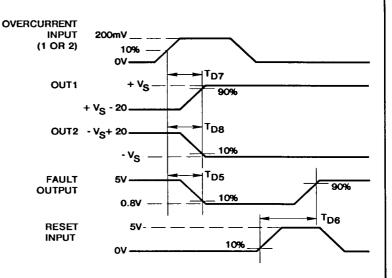

## Parameter Definitions (Refer to Switching Waveforms)

| SYMBOL          | DEFINITIONS                                                                                                                                                       |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>D2</sub> | Delay time as measured from the logic input high to low transition (1 to 0) at the 10% point, to the 10% point of the output transition for the high side switch. |

| T <sub>D1</sub> | Delay time as measured from the logic input low to high transition (0 to 1) at the 10% point, to the 10% point of the output transition for the high side switch. |

| T <sub>D4</sub> | Same as T <sub>DO-1</sub> for the ow side switch.                                                                                                                 |

| трз             | Same as T <sub>D1-1</sub> for the ow side switch.                                                                                                                 |

| T <sub>R1</sub> | Output rise time from the 10% – 90% points for the high side switch.                                                                                              |

| T <sub>R2</sub> | Output rise time from the 10% - 90% points for the low side switch.                                                                                               |

| T <sub>F1</sub> | Output fall time from the 10% - 90% points for the high side switch.                                                                                              |

| T <sub>F2</sub> | Output fall time from the 10% - 90% points for the low side switch.                                                                                               |

| T <sub>D5</sub> | Delay time as measured from the overcurrent input 10% point to the fault output high to low transition at the 10% point.                                          |

| T <sub>D6</sub> | Delay time as measured from the reset input 10% point to the fault output low to high transition at the 90% point.                                                |

| T <sub>D7</sub> | Delay time as measured from the overcurrent 1 input 10% point to output 1 low to high transition at the 90% point.                                                |

| T <sub>D8</sub> | Delay time as measured from the overcurrent 2 input 10% point to output 2 high to low transition at the 10% point.                                                |

## Switching Time Test Circuits

FIGURE 1. INVERTING DRIVE SWITCHING TIME (HIGH SIDE)

FIGURE 2. NON-INVERTING DRIVER SWITCHING TIME (LOW SIDE)

### Overcurrent Test Waveforms

#### **OVERCURRENT TEST CIRCUIT**

## Packaging

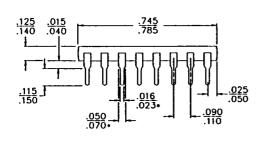

### 16 PIN PLASTIC DIP

ADD .003 INCHES TO DIM FOR SOLDER DIPPED LEADS.

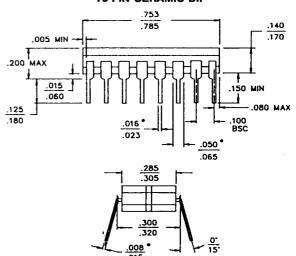

#### 16 PIN CERAMIC DIP

• INCREASE MAX LIMIT BY .003 INCHES MEASURED AT CENTER OF FLAT FOR

Harris Semiconductor products are sold by description only. Harris Semiconductor reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Harris is believed to be accurate and reliable. However, no responsibility is assumed by Harris or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Harris or its subsidiaries.

## Sales Office Headquarters

## **UNITED STATES**

Harris Semiconductor 1301 Woody Burke Road Melbourne, Florida 32902 TEL: (407) 724-3739

## **EUROPE**

Harris Semiconductor Mercure Centre Rue de la Fusee 100 1130 Brussels, Belgium TEL: (32) 2-246-21.11

#### **SOUTH ASIA**

Harris Semiconductor H.K. Ltd 13/F Fourseas Building 208-212 Nathan Road Tsimshatsui, Kowloon Hong Kong TEL: (852) 3-723-6339

**NORTH ASIA** Harris K.K. Shinjuku NS Bldg. Box 6153 2-4-1 Nishi-Shinjuku Shinjuku-Ku, Tokyo 163 Japan TEL: (81) 03-3345-8911

File Number 2847

024179 V R