# 16 bit D/A Converter

#### Description

The CX20133 is a 16 bit D/A converter IC for PCM audio using the integrating formula. Analog signal is reproduced from the 16 bit digital signal by combining an integrator, analog switch and low-pass filter to the IC exterior. Following circuits are also built-in so that it can be operated in sync with LSI for CD (compact disc) system.

- Integrating current output

- Two channels of discharge signal output

- Level shifting for interface direct with TTL/MOS LSIs.

- Analog switch drive.

#### **Features**

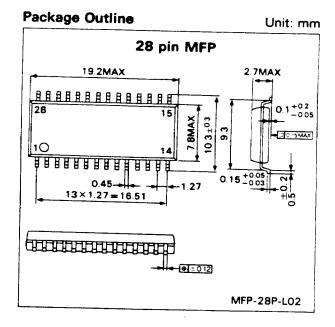

- Miniature flat package requires only small mounting area.

- Conversion frequency of 44.1 kHz.

- Serial data input.

- Low distortion factor typically at 0.003%.

#### Structure

Bipolar Silicon Monolithic IC

### Absolute Maximum Ratings (Ta = 25°C)

| Supply voltage                                  | VCC to VEE | 12            | V  |

|-------------------------------------------------|------------|---------------|----|

| <ul> <li>Operating temperature</li> </ul>       | Topr       | -10  to  +75  | °C |

| <ul> <li>Storage temperature</li> </ul>         | Tstg       | -50  to  +125 | °Č |

| <ul> <li>Allowable power dissination</li> </ul> | Po         | 1 1           | W  |

#### **Recommended Operating Conditions**

| <ul><li>Supply voltage</li></ul> | <b>Vc</b> c | $5 \pm 0.25$  | V |

|----------------------------------|-------------|---------------|---|

|                                  | VEE         | $-5 \pm 0.25$ | V |

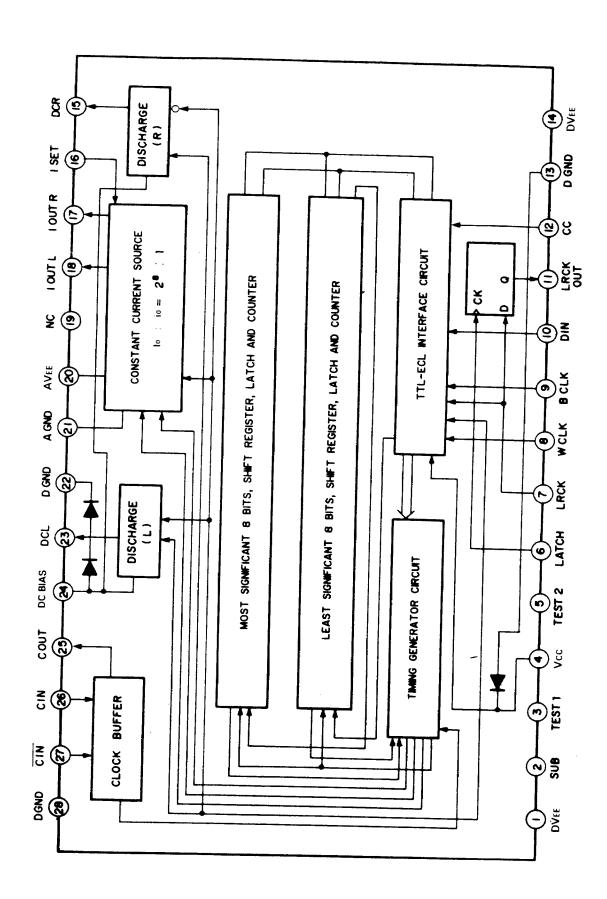

**Block Diagram**

Fig. 1

## **Pin Description**

| No. | Symbol   | Description                                                  |

|-----|----------|--------------------------------------------------------------|

| 1   | DVEE     | Power supply pin for the digital circuit. Applied with -5 V. |

| 2   | SUB      | IC substrate. Always connected to 1 pin.                     |

| 3   | TEST 1   | Test pin, normally open.                                     |

| 4   | Vcc      | Power supply pin for the digital circuit. Applied with +5 V. |

| 5   | TEST 2   | Test pin, normally open.                                     |

| 6   | LATCH    | Clock pin of D-type clutch.                                  |

| 7   | LRCK     | LRCK input pin.                                              |

| 8   | WCLK     | WCLK input pin.                                              |

| 9   | BCLK     | BCLK input pin.                                              |

| 10  | DIN      | DIN (data input pin).                                        |

| 11  | LRCK OUT | LRCK output pin.                                             |

| 12  | СС       | CC input pin.                                                |

| 13  | DGND     | Ground pin for the digital circuit.                          |

| 14  | DVEE     | Power supply pin for the digital circuit. Applied with -5 V. |

| 15  | DCR      | Output pin of R-channel discharge driving signal.            |

| 16  | ISET     | Pin for setting integration current.                         |

| 17  | IOUTR    | Output pin for R-channel current.                            |

| 18  | IOUTL    | Output pin for L-channel current.                            |

| 19  | NC       | No connection.                                               |

| 20  | AVEE     | Power supply pin for the analog circuit.                     |

| 21  | AGND     | Ground pin for the analog circuit.                           |

| 22  | DGND     | Ground pin for the digital circuit.                          |

| 23  | DCL      | Output pin for L-channel discharge driving signal.           |

| 24  | DCBIAS   | Bias pin for the discharge circuit.                          |

| 25  | COUT     | Output pin for the clock oscillator.                         |

| 26  | CIN      | Positive input pin for the clock oscillator:                 |

| 27  | CIN      | Negative input pin for the clock oscillator.                 |

| 28  | DGND     | Ground pin for the digital circuit.                          |

#### **Electrical Characteristics**

$(Ta = 25^{\circ}C, V_{EE} = -5 \text{ OV}, V_{CC} = 1 \text{ OV})$

| ltem                                              | Symbol                                         | Condition                                                                   | Min.  | Тур.  | Max.  | Unit | Note        |

|---------------------------------------------------|------------------------------------------------|-----------------------------------------------------------------------------|-------|-------|-------|------|-------------|

| Circuit current                                   | IEE                                            | 1, 2, 14, 20                                                                | - 112 | - 85  |       | mA   | 1           |

| Circuit current                                   | lcc                                            | 4                                                                           |       | 9.5   | 12.5  | mA   | 1           |

| Input threshold voltage                           | Vтн                                            | 6. 7, 8, 9, 10, 12                                                          |       | 2.1   |       | V    |             |

| High-level<br>input voltage                       | Vін                                            | 6, 7, 8, 9, 10, 12                                                          | 2.8   |       |       | ٧    |             |

| Low-level<br>input voltage                        | VIL                                            | 6, 7, 8, 9, 10, 12                                                          |       |       | 0.8   | V    |             |

| High-level input current                          | liH                                            | 6, 7, 8, 9, 10, 12 ViH = 4.5V                                               |       |       | 500   | μΑ   |             |

| Low-level input current                           | lıL                                            | 6, 7, 8, 9, 10, 12 VIL = 0V                                                 |       |       | 500   | μΑ   |             |

| High-level output voltage                         | VLRCKH                                         | 11 Pin 7 = 4.5V IOH = -100μA<br>Pin 6:1 clock input:0V - 5V - 0V            | 2.7   |       |       | V    |             |

| Low-level output voltage                          | VLRCKL                                         | 11 Pin 7 = 0V   IOL = 100μA<br>Pin 6:1 clock input: 0V - 5V - 0V            |       |       | - 2.7 | V    |             |

| Clock input<br>bias voltage                       | Vcin                                           | 26, 27                                                                      |       | -1.3  |       | V    |             |

| Clock high-level output voltage                   | VCCR                                           | 25                                                                          |       | - 0.8 |       | V    |             |

| Clock low-level output voltage                    | Vcor                                           | 25                                                                          |       | 1.6   |       | V    |             |

| Current output<br>pin leak                        | 10<br>LEAK                                     | 17, 18 Pins 17, 18: voltage = 0V when current output is off.                |       |       | 1.5   | μА   | <del></del> |

| IOUT output<br>current                            | lout                                           | Pins 17, 18: voltage = 0V<br>17, 18 Pin 16 Isετ = 500μA<br>(Ιουτ = Ιο - io) |       | 2.008 |       | mA   |             |

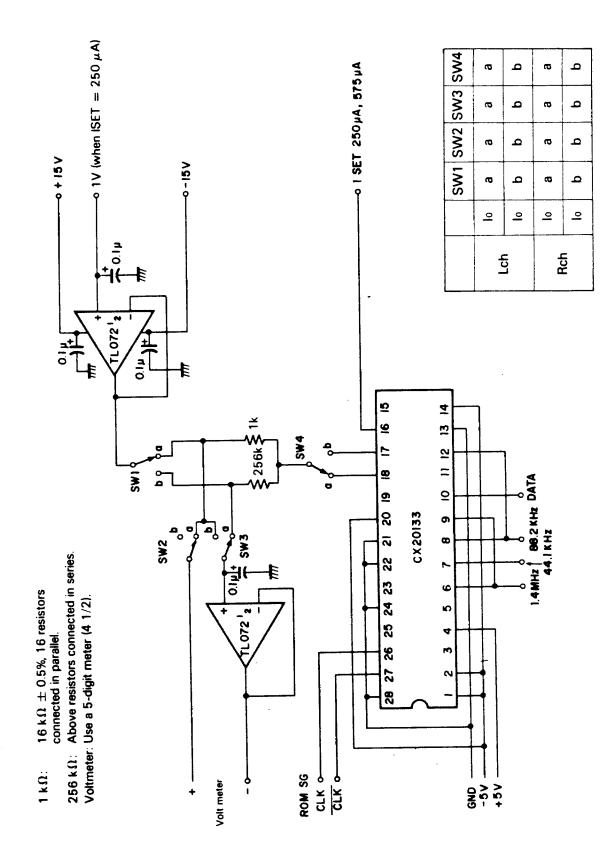

| Current ratio *1                                  | lo⁄io                                          | 17, 18 Pin 16 ISET = 250µA                                                  | 255.0 | 256.0 | 257.5 | _    | 2           |

| Discharge circuit current dissipation             | lpc                                            | 24 Set Pin 24 to 0V.                                                        | 1.35  | 1.9   | 2.5   | mA   |             |

| Discharge circuit<br>high-level output<br>voltage | VDCH                                           | 15, 23 Pin 24 voltage = 1.4V<br>Load current = -100μA                       | 0.27  | 0.45  | 0.77  | ٧    |             |

| Discharge circuit<br>low-level output<br>voltage  | VDCL                                           | 15, 23 Pin 24 voltage = 1.4V<br>Load current = -100μA                       |       | -4.2  | - 3.5 | ٧    |             |

| Maximum ISET current                              | ISET<br>MAX                                    | 16 In the range when the lou⊤L(R) current ratio satisfies 255 < lo/io < 257 |       |       | 575   | μА   |             |

| District                                          | 7115                                           | Both right and left, OdB (full scale) reproduction 680Hz                    |       | 0.003 | 0.005 | %    | 3           |

|                                                   | Both right and left, - 20dB reproduction 680Hz |                                                                             | -0.02 | 0.025 | %     | 3    |             |

| Operating clock frequency                         | fcLK                                           | Self-activating/Activated                                                   |       |       | 36    | MHz  |             |

Note 1) Ground Pins 13, 17, 18, 21, 22, 24 and 28. Connect Pin 16 via a resistor of 5.1 k $\Omega$  and keep other pins open.

2) Io and io must satisfy the relation below in the Current Ratio Test Circuit (Fig. 3):  $-3.9 \text{ (mV)} < 1 \text{ (k}\Omega) \times \text{Io } (\mu\text{A}) - 256 \text{ (k}\Omega) \times \text{io } (\mu\text{A}) < 5.9 \text{ (mV)}$

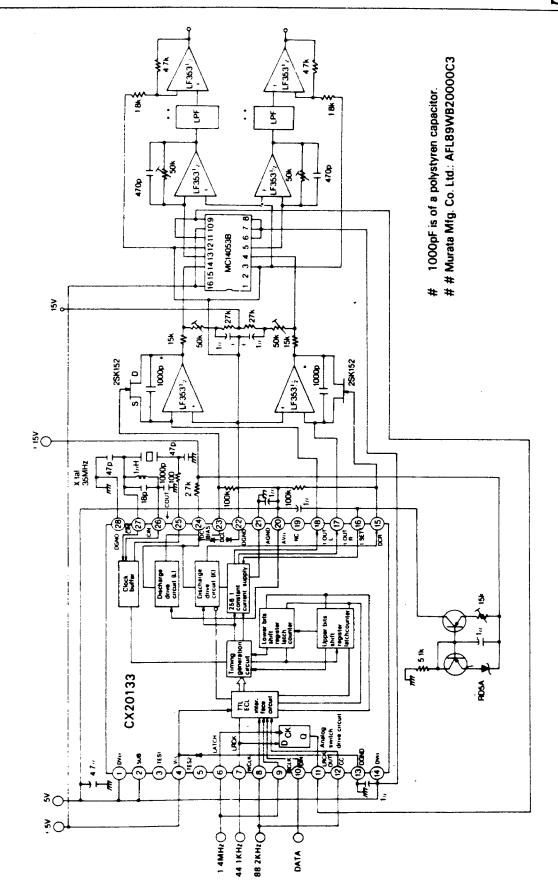

3) See the Test Circuit (Fig. 2).

Conversion frequency: 44.1 kHz

Input data: Use the 16 bit full-scale data (0 dB) generated by the data generator.

Distortion meter: Use the HP339A (with all filters on) or the like provided with 80 kHz LPF, 30 kHz LPF and 400 Hz HPF.

-3.9(mV) < 1(k $\Omega$ )  $\times$  lo( $\mu$ A) -256(k $\Omega$ )  $\times$  io( $\mu$ A) < 5.9(mV)

<sup>\*1</sup> In the Current Ratio Test Circuit (Fig. 3),

#### **Description of the Conversion Operation**

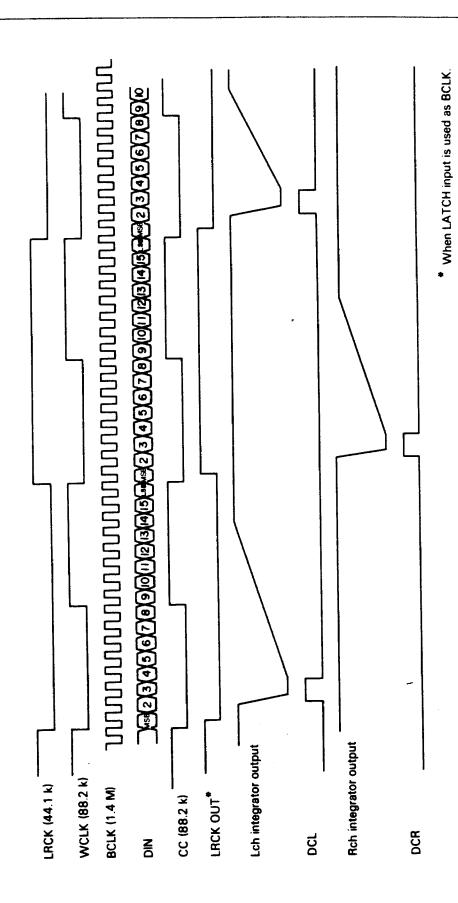

#### (1) Data call (BCLK, DIN, WCLK, LRCK). Refer to Fig. 6.

The data comes in 16 bit serial signal with 2's compliment. The data is sent sequencially into the IC beginning from MSB in sync with the rise of the bit clock (BCLK). (The data change represents the BCLK fall).

When the word clock (WCLK) is changed from the high-level to low-level at the 17th fall of BCLK, the 16 bit data is transferred from the shift register to the latch by the fall signal.

When the CX20133 is used in the stereo mode, data from other channels are sent in from the 17th BCLK.

In the stereo mode, Rch data is called when LRCK at the low level and Lch data is called in when the LRCK is at the high level. IOUTL and DCL operate only when LRCK is at the low level and IOUTR and DCR operate only when LRCK is at the high level.

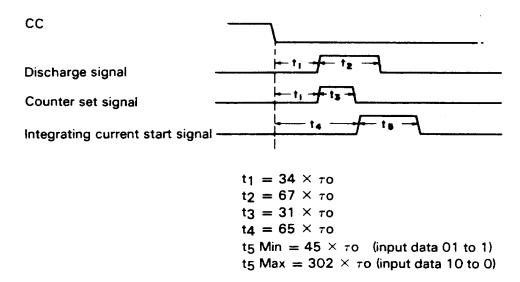

#### (2) Conversion operation (CC, LRCK, CIN, IOUTL, IOUTR, DCL, DCR)

When more than 3 clocks are input from the clock input (CIN) with conversion command at the high level, all inner timing circuits are reset.

After resetting, the inner timing circuit starts operation when a clock is input from CIN with CC at the low level. The three signal generated this way are the discharge signal, counter set signal and integrating signal. Time of these three signals is determined depending on the clock cycle and their number of quantity:

The counter set signal is to set the data input to the latch to the counter and it is not output externally.

The discharge signal is output from DCL and DCR and it is controlled by LRCK. It is output from DCL when LRCK is at the low level and from the DCR when LRCK is at the high level.

By the integrating current start signal, the upper current lo and lower current io start flowing. The counter starts counting from the preset value simultaneously when the discharge signal is off, measures the 11 offsets after completion of counting and outputs a signal to stop the integrating current.

The t5 value is varied between 0 and 255 by the preset input data in the counter.

Therefore, the conversion time from the start of low CC level to the completion of integrating requires t4 + t5 sec max.

The integrating current, like the discharge signal, is controlled by LRCK; IOUTL is output when LRCK is at the low level and IOUTR is output when LRCK is at the high level.

#### The Relation between Sampling Frequency fs and Clock

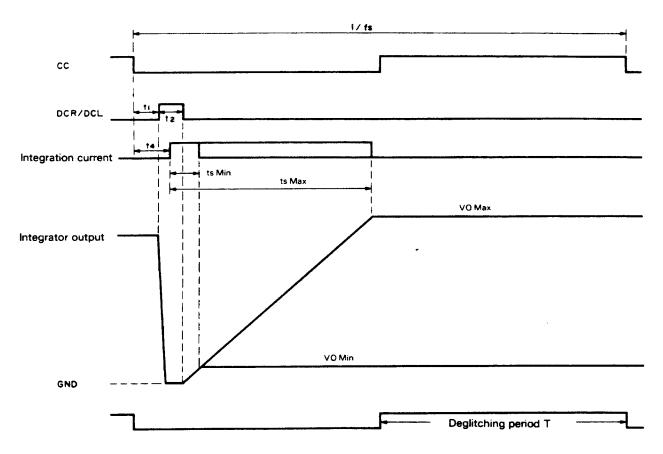

The maximum and minimum values of the integration voltage output, Vo Max and Vo Min, are expressed as follows:

Vo Max =

$$\frac{I_0}{C} * \tau_0 * 267 + \frac{i_0}{C} * \tau_0 * 266$$

(t<sub>4</sub> + t<sub>5</sub> Max)

Vo Min =

$$\frac{I_0}{C} * \tau_0 * 12 + \frac{i_0}{C} * \tau_0 * 11$$

(t<sub>4</sub> + t<sub>5</sub> Min)

where fCLK is a clock frequency and  $\tau$  is a period.

The integration voltage is held by the capacitor C in the integrator when the current is switched off. This voltage is used as D/A conversion output during the deglitching period T which is given according to the settling time of the deglitching circuit.

The relation between the conversion frequency fs and the clock frequency fCLK is given as below assuming that the conversion time and deglitching period are equivalent:

$$fs = \frac{fCLK}{2 \times (t_4 + t_5 Max)} = \frac{fCLK}{734}$$

where fs = 44.1 kHz results in 32.4 MHz of fCLK.

It is, however, recommendable to specify fs as the follow for the practical use because a settling time of 0.5 to 1.0  $\mu$ s is required for the integrator after the current for t<sub>5</sub> disappears:

$$fs = \frac{fCLK}{(t_4 + t_5 Max + 1.0 (\mu s)) + T}$$

#### (3) Integration current setting (ISET, IOUTL, LOUTR)

Integration current is determined by a constant current value input through the ISET pin, which is given as below:

IOUTL (R) =

$$10 + i0$$

=  $(4 + \frac{1}{64})$  ISET

where io and lo are integration currents corresponded to the ILSB and 28-LSB, respectively.

If Do and Dos are specified as MSB and LSB, respectively, integrator output voltage Vo is given by the following equation:

$$V_0 = \frac{I_0}{C} (D_0 * 2^7 + \overline{D}_1 * 2^7 + \cdots + \overline{D}_7 * 2^0 + 12) \tau_0 + \frac{I_0}{C} (\overline{D}_8 * 2^7 + \overline{D}_9 * 2^6 + \cdots + \overline{D}_{15} + 2^0 + 11) \tau_0$$

where ISET =  $500\mu$ A,  $\tau_0 = \frac{1}{35 \text{ (MHz)}} = 28.6 \text{ (ns)}$  and C = 2000 pF result in the maximum output voltage V<sub>0</sub> Max of the integrator when any of a value from 10 to 0 is given as an input data. Based on the relations below,

$$lo=4*ISET$$

$io=\frac{1}{64}*ISET$

Vo Max is calculated as the follow:

Vo Max =

$$\frac{2.0 \times 10^{-3}}{2000 \times 10^{-12}} * 267 * 28.6 \times 10^{-9}$$

+  $\frac{500 * 10^{-6}/64}{2000 \times 10^{-12}} * 266 * 28.6 \times 10^{-9}$

= 7.67 (V)

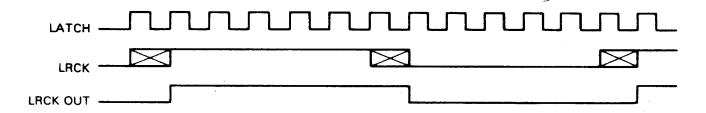

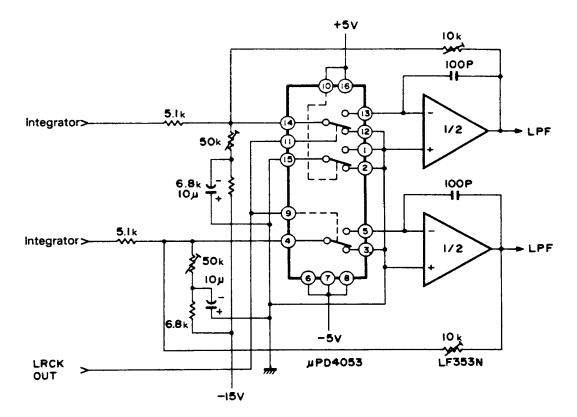

#### (4) Operation of LRCK OUT

The LRCK OUT is an output for the analog switch IC (equivalent to MC14053B) drive to clip the output converted by the CX20133 and integrator as a PAM wave.

A PAM wave jitter may cause a conversion error and a D-type flip-flop is incorporated to eliminate this jitter; the LATCH input is used as a clock for the flip-flop.

This D-type flip-flop changes the output status in sync with the clock rise. The LRCK OUT operates only when +5 V is applied to VCc. The output voltage level ranges from -2.7 V to +2.7 V enough to drive the CMOS analog switch effectively.

Timing of LATCH, LARCK and LRCKO

(5) Clock input/output pin (COUNT, CIN, CIN)

The clock buffer consists of a circuit equivalent to a general-purpose ECL logic circuit, with its input pin biased by the internal bias circuit. The ( $\approx -1.3$  V) output amplitude level is 0.8 V.

(6) Bias pin (DVEE, SUB, DGND, VCC, AVEE, AGND, DC BIAS)

SUB is used at the common potential with DVEE. A standard value for the DVEE and AVEE is -5.0 V. The CX20133 is devised so that it can operate when voltage at the digital input pin has a value between either 0 to -5 V or 0 to +5 V. When operated with an input between 0 and +5 V, +5 V must be applied to VCC. In this case, LRCK OUT is output as mentioned above.

When operated with an input between 0 to -5 V, Vcc must be set open.

DC BIAS is for the bias circuit of the discharge signal output circuit. Supply current of (2.5 mA  $+\alpha$ ) from a power supply of +5 V or above, because this pin requires approx. 2.5 mA current as a standard value. The potential at the pin is biased at 2 Vf.

A value  $\alpha$  can be determined according to the following procedures. Approx. 0.5 mA current is necessary to retain 2 Vf (approx. 1.4 V) at this pin. The maximum current that flows through the load resistor RL attached to DCR (15 Pin) and DCL (23 Pin) is calculated as the follow:

The above equation results in 1.15 V where RL=4.7 k $\Omega$ , VDCH=0.4 V and DVEE=-5 V are specified. Then  $\alpha$  is calculated as

$$\alpha = 0.5 + 1.15 = 1.65 \text{ (mA)},$$

and required current is then obtained as 4.15 mA. Recommended value is 5 mA for RL = 4.7 k $\Omega$ .

**Application Circuit and Test Circuit**

Fig. 2

# **Current Ratio Test Circuit**

Fig. 3

# Sample/Hold Circuit for Deglitching

Fig. 4

Timing Chart in the Stereo Mode

Fig. 5

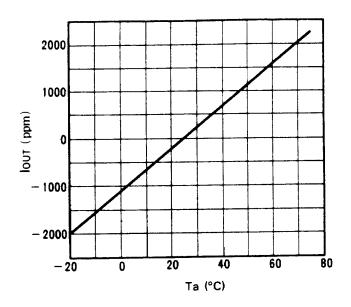

Temperature characteristics of lout (Io+id) (R, Lch common)

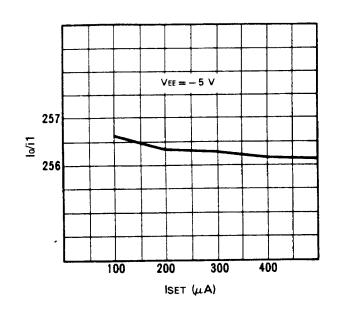

lo/io vs. ISET

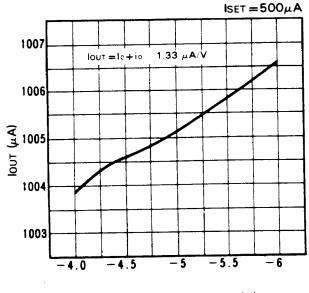

Output current vs. Supply voltage (VEE)

VEE - Supply voltage (V)

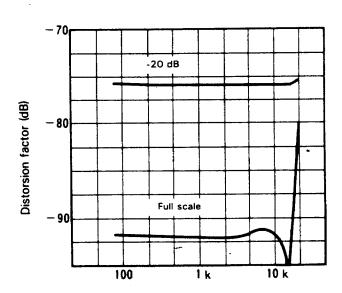

#### **Distortion factor**

Frequency (Hz)