# CSP1027 Voiceband Codec for Cellular Handset and Modem Applications

### 1 Features

- Δ-Σ (Delta-Sigma) A/D and D/A converters with standard 16-bit serial I/O interface.

- On-chip filters meet CCITT G.714 voiceband frequency response and signal to distortion plus noise specifications. Suitable for IS-54, GSM, and JDC digital cellular applications.

- Low-profile package (<1.5 mm) 48-pin thin quad flat pack (TQFP) available or 44-pin EIAJ quad flat pack (QFP).

- Operates in systems with a 3 V to 5 V digital power supply and a 5 V analog supply.

- Low-power 0.9 μm CMOS technology, fully static design, typical power of 68 mW when active and 0.05 mW in standby with a 3.3 V digital supply and a 5.0 V analog supply.

- A low-power inactive (standby) state without stopping clock or removing power supply.

- Sampling rates up to 24 kHz.

- On-chip programmable sampling clock generator allows input clock to be an integer multiple of 125 times the sampling rate or an integer multiple of the sampling rate.

- Programmable phase adjust of both codec sampling clock and baseband codec clock.

- Two on-chip clock dividers for generating the output clock for the baseband codec and the output clock for other processors.

- Regulated microphone power supply.

- Microphone preamplifier, with programmable input ranges of 0.16 Vpeak and 0.5 Vpeak.

- Output amplifier, with programmable gain settings,

0 dB to -45 dB in -3 dB steps.

- High-pass filters selectable via control registers.

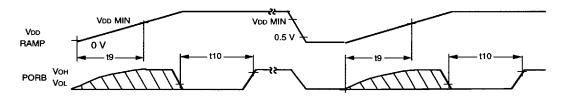

- Power-on reset pulse generator.

- Standard 16-bit serial I/O interface.

- Serial I/O multiprocessor mode compatible with the AT&T DSP16A and AT&T DSP1610/1616/1617/ 1618 Digital Signal Processors.

### 2 Description

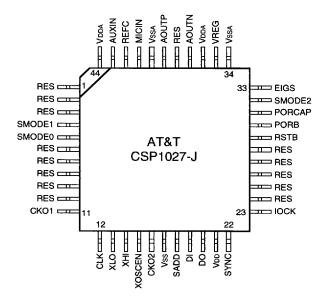

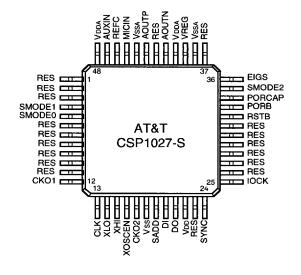

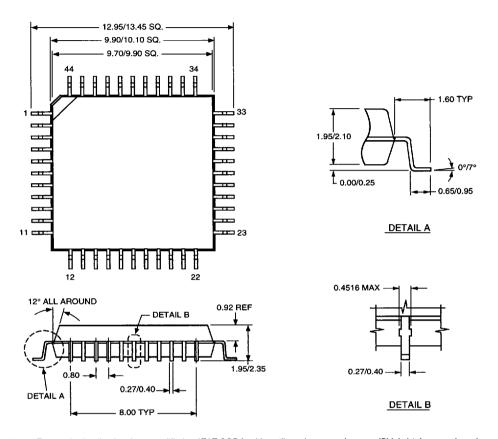

The AT&T CSP1027 is a high-precision linear voiceband  $\Delta$ - $\Sigma$  (delta-sigma) codec designed for cellular handset and modem applications. The device is fabricated in low-power CMOS technology and designed for low-voltage, 3 V to 5 V, digital systems. The CSP1027 is packaged in a 44-pin EIAJ quad flat pack (QFP) or a 48-pin EIAJ thin quad flat pack (TQFP). In the 48-pin TQFP, the CSP1027 occupies a total volume of 0.0784 cm<sup>3</sup>.

The CSP1027 has a variety of significant programmable features not found in standard voiceband codecs. The analog interface includes a microphone preamplifier with programmable gain settings, an output amplifier with gain programmable in 3 dB steps over a 45 dB range, and a regulated microphone power supply. An inactive mode allows a low-power standby state, and a mute function provides suppression of the analog output. On-chip antialiasing and anti-imaging filtering includes a selectable high-pass filter. The CSP1027 meets CCITT G.714 voiceband specifications.

The programmable features of the CSP1027 are set by writing four on-chip control registers through the serial I/O interface. The codec's digital input/output uses a linear 16-bit two's complement data format that is also transferred through the serial I/O interface. The CSP1027 interfaces easily to the 16-bit serial ports of digital signal processors and other devices. The serial interface supports the AT&T fixed-point DSP family serial multiprocessor mode. This allows up to eight compatible devices, including two CSP1027s, to interface to each other on a common 4-wire bus using a time-division-multiplexing scheme.

### **CSP1027**

### **Table of Contents**

| Contents                                            | Page  |

|-----------------------------------------------------|-------|

| 1 Features                                          | 11-1  |

| 2 Description                                       | 11-1  |

| 3 Pin Information                                   | 11-3  |

| 4 Architectural Information                         | 11-5  |

| 4.1 Overview                                        | 11-6  |

| 4.2 Description of Signal Paths                     | 11-6  |

| 4.3 Programmable Features                           | 11-13 |

| 4.4 Power-On Reset                                  |       |

| 4.5 Clock Generation                                | 11-16 |

| 4.6 Serial I/O Configurations                       | 11-19 |

| 5 Register Information                              | 11-25 |

| 5.1 Codec I/O Control 0 (cioc0) Register            |       |

| 5.2 Codec I/O Control 1 (cioc1) Register            | 11-26 |

| 5.3 Codec I/O Control 2 (cioc2) Register            | 11-27 |

| 5.4 Codec I/O Control 3 (cioc3) Register            | 11-27 |

| 6 Signal Descriptions                               | 11-28 |

| 6.1 Clock Interface                                 | 11-28 |

| 6.2 Reset Interface                                 | 11-20 |

| 6.3 Serial I/O Interface                            | 11 20 |

| 6.4 External Gain Control Interface                 | 11-23 |

| 6.4 External Gain Control Interace                  | 11-30 |

| 6.5 Digital Power and Ground                        | 11-30 |

| 6.6 Analog Interface                                | 11-30 |

| 6.7 Analog Power and Ground                         | 11-30 |

| 7 Application Information                           | 11-31 |

| 7.1 Analog Information                              | 11-31 |

| 7.2 Power Supply Configuration                      | 11-34 |

| 7.3 The Need for Fully Synchronous Operation        |       |

| 7.4 Crystal Oscillator                              | 11-36 |

| 7.5 Programmable Clock Generation                   | 11-43 |

| 8 Device Characteristics                            | 11-45 |

| 8.1 Absolute Maximum Ratings                        | 11-45 |

| 8.2 Handling Precautions                            | 11-45 |

| 8.3 Recommended Operating Conditions                | 11-45 |

| 9 Electrical Characteristics and Requirements       | 11-46 |

| 9.1 Power Dissipation                               | 11-48 |

| 10 Analog Characteristics and Requirements          | 11-49 |

| 10.1 Analog Input and Microphone Regulator          | 11-49 |

| 10.2 Analog-to-Digital Path                         | 11-50 |

| 10.3 Digital-to-Analog Path                         | 11-51 |

| 10.4 Miscellaneous                                  | 11-52 |

| 11 Timing Characteristics and Requirements          | 11-53 |

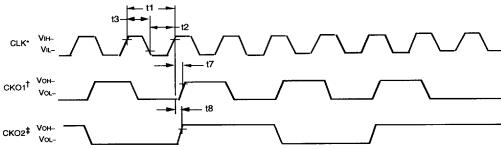

| 11.1 Clock Generation                               | 11-53 |

| 11.2 Power-On Reset                                 |       |

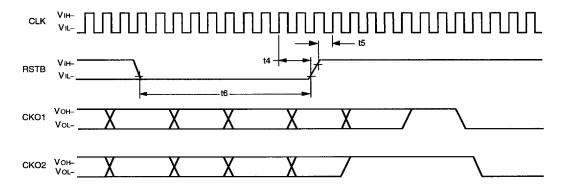

| 11.3 Reset                                          | 11-55 |

| 11.4 Serial I/O Communication                       | 11-56 |

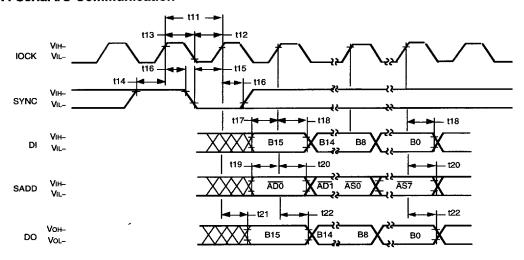

| 11.5 Serial Multiprocessor Communication            | 11-58 |

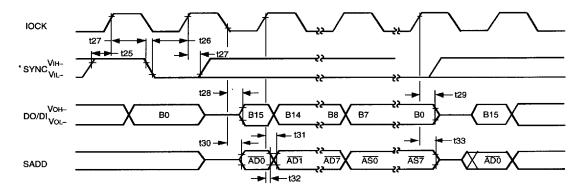

| 12 Outline Diagrams                                 | 11-59 |

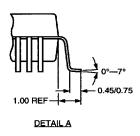

| 12.1 44-Pin EIAJ Quad Flat Pack (QFP)               | 11-59 |

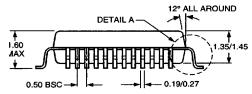

| 12.2 48-Pin EIAJ Thin Quad Flat Pack (TQFP)         | 11-60 |

| 121 10 1 11 El 10 1 IIII 0000 1 100 1 000 (1 01 1 ) |       |

### 3 Pin Information

Figure 1. 44-Pin EIAJ Quad Flat Pack (QFP) Pin Diagram

Figure 2. 48-Pin EIAJ Thin Quad Flat Pack (TQFP) Pin Diagram

### Pin Information (continued)

Functional descriptions of the pins are found in Section 6, Signal Descriptions.

**Table 1. Pin Descriptions**

| QFP Pin    | TQFP Pin    | Symbol | Туре           | Name/Function                                                 |

|------------|-------------|--------|----------------|---------------------------------------------------------------|

| 1, 2, 3    | 1, 2, 3     | RES    | NC*            | Reserved.                                                     |

| 4          | 4           | SMODE1 | ŀ              | Serial Mode Select 1.                                         |

| 5          | 5           | SMODE0 | ı              | Serial Mode Select 0.                                         |

| 6, 7, 8,   | 6, 7, 8,    | RES    | NC*            | Reserved.                                                     |

| 9, 10      | 9, 10, 11   |        |                |                                                               |

| 11         | 12          | CKO1   | 0              | Clock Output 1.                                               |

| 12         | 13          | CLK    |                | Clock input.                                                  |

| 13         | 14          | XLO    | -              | Crystal Input.                                                |

| 14         | 15          | XHI    | 0              | Crystal Output.                                               |

| 15         | 16          | XOSCEN | ı              | Crystal Oscillator Enable.                                    |

| 16         | 17          | CKO2   | 0              | Clock Output 2.                                               |

| 17         | 18          | Vss    | Ρ              | Digital Ground.                                               |

| 18         | 19          | SADD   | 1/0**          | Serial Address.                                               |

| 19         | 20          | DI     | ı              | Serial Input Data.                                            |

| 20         | 21          | DO     | O**            | Serial Output Data.                                           |

| 21         | 22          | VDD    | Ρ              | Digital Power Supply.                                         |

| _          | 23          | RES    | NC*            | Reserved.                                                     |

| 22         | 24          | SYNC   | I/O**          | Serial Input/Output Load Strobe and Synchronization.          |

| 23         | 25          | IOCK   | 1              | Serial Clock.                                                 |

| 24, 25,    | 26, 27, 28, | RES    | NC*            | Reserved.                                                     |

| 26, 27, 28 | 29, 30, 31  |        |                |                                                               |

| 29         | 32          | RSTB   | 1              | Reset.                                                        |

| 30         | 33          | PORB   | 0              | Power-On Reset Output.                                        |

| 31         | 34          | PORCAP | I <sup>‡</sup> | External Capacitor Connection for Power-On Reset.             |

| 32         | 35          | SMODE2 | l l            | Serial Mode Select 2.                                         |

| 33         | 36          | EIGS   | IŞ             | External Input Gain Select.                                   |

|            | 37          | RES    | NC*            | Reserved.                                                     |

| 34         | 38          | Vssa   | Р              | Analog Ground.                                                |

| 35         | 39          | VREG   | Α              | Regulated Output Voltage for Electret Condenser Microphone.   |

| 36         | 40          | VDDA   | Р              | Analog 5 V Power Supply.                                      |

| 37         | 41          | AOUTN  | Α              | Inverting Analog Output of Output Amplifier.                  |

| 38         | 42          | RES    | NC*            | Reserved.                                                     |

| 39         | 43          | AOUTP  | A              | Noninverting Analog Output of Output Amplifier.               |

| 40         | 44          | VSSA   | Р              | Analog Ground.                                                |

| 41         | 45          | MICIN  | Α              | Analog Input for Microphone.                                  |

| 42         | 46          | REFC   | Α              | External Capacitor Connection for Internal Voltage Regulator. |

| 43         | 47          | AUXIN  | Α              | Analog Input from Auxiliary                                   |

| 44         | 48          | VDDA   | Р              | Analog 5 V Power Supply.                                      |

<sup>\*</sup> Indicates no connection.

<sup>†</sup> Indicates pull-up device on input.

<sup>‡</sup> Indicates pull-up resistor on input.

<sup>§</sup> Indicates pull-down device on input.

\*\* Indicates 3-state output.

### **4 Architectural Information**

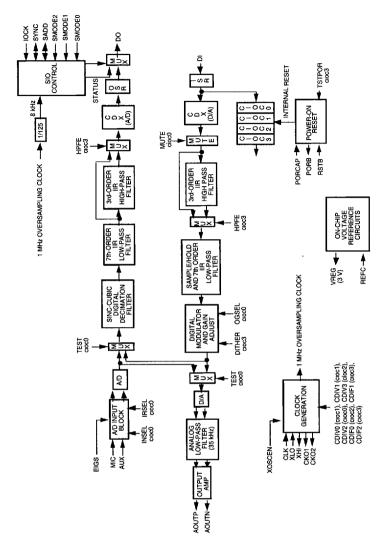

Figure 3. CSP1027 Block Diagram

### 4.1 Overview

The CSP1027 is a complete analog-to-digital and digital-to-analog acquisition and conversion system (see the block diagram in Figure 3). It band limits and encodes analog input signals into 16-bit PCM, and takes 16-bit PCM inputs and reconstructs and filters the resultant analog output signal. The selectable A/D input circuits, programmable sample rates, and digital filter options allow the user to optimize the codec configuration for either speech coding or voiceband data communications. The on-chip digital filters meet the CCITT G.714 voiceband frequency response and signal to distortion plus noise specifications and are suitable for IS-54, GSM, and JDC digital cellular applications. In addition, the small supply current drain when powered down extends battery life in mobile communication applications.

The CSP1027 is intended for both voiceband voice and data communication systems. As a result, this codec has a variety of features not found in standard voiceband codecs:

- 3 V regulated power supply for a condenser microphone

- Microphone preamplifier with programmable input ranges.

- Mute control of D/A output.

- Programmable output gain in 3 dB increments.

- Output speaker driver.

- Programmable master clock divider to set A/D and D/A conversion rate.

- Testability loopback mode.

- High-quality dither scheme to eliminate idle channel tones.

### 4.2 Description of Signal Paths

### Sampling Frequency

The oversampling ratio of the codec is 125:1; this is the ratio of the frequency of the oversampling clock to the frequency of the sampling clock. Most speech applications specify a sampling frequency of 8 kHz, yielding an oversampling frequency of 8 kHz x 125 = 1.0 MHz. The codec will operate at sampling frequencies up to 24 kHz, with the frequency response of the digital filters being changed proportionally. For this architectural description, the sampling frequency, fs, is assumed to be 8 kHz, with an oversampling frequency, fos, of 1 MHz, unless otherwise stated.

### **Analog-to-Digital Path**

The analog-to-digital (A/D) conversion signal path (see Figure 3) begins with the analog input driving the input block. The signal from the input block is then encoded by a second order  $\Delta$ - $\Sigma$  modulator A/D. The bulk of the antialiasing filtering is done in the digital domain in two

stages following the  $\Delta$ - $\Sigma$  modulator to give a 16-bit result. The blocks will next be covered in more detail.

### **Analog Input Block**

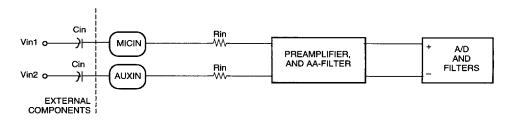

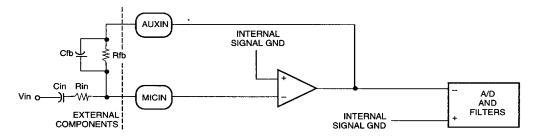

The A/D input block operates in two modes: when the external input gain select (EIGS) pin is low or left unconnected, the input goes through a preamplifier and is band limited by a second-order 30 kHz low-pass antialiasing filter (see Figure 4). When EIGS is high, external resistors, Rin and Rfb, are used to set the gain of an inverting amplifier (see Figure 5). These resistors, in combination with Cin and Cfb, create a bandpass antialiasing filter. Note that EIGS is a digital pin whose input levels are relative to digital power and ground (VDD and Vss).

### A/D Modulator and Digital Filters

A second-order  $\Delta$ - $\Sigma$  modulator quantizes the analog signal to 1 bit (see Figure 3). At the same time, the resulting quantization noise is shaped such that most of this noise lies outside of the baseband. The modulator output is then digitally low-pass filtered to remove the out-of-band quantization noise. After this filtering, the output samples are decimated down to the output sampling frequency. In the CSP1027, the filtering and decimation are completed in two stages. The first stage low-pass filter shapes the modulator output according to the sinc-cubic transfer function:

$$H(z) = \left[\frac{1}{25} \times \frac{(1-z^{-25})}{(1-z^{-1})}\right]^3$$

The output sampling frequency of the sinc-cubic filter is reduced by a factor of 25 from 1 MHz to 40 kHz. The sinc-cubic filter places nulls in the frequency response at multiples of 40 kHz, and removes most of the quantization noise above 20 kHz so that very little energy is aliased as a result of the decimation.

The sinc-cubic filter output is then processed by a seventh-order IIR digital low-pass filter. This filter removes the out-of-band quantization noise between 3.4 kHz and 20 kHz, compensates for the passband droop caused by the sinc-cubic decimator, and decimates the sampling frequency by a factor of five from 40 kHz to 8 kHz.

Following the low-pass filtering and decimation to 8 kHz, the 16-bit two's complement PCM can go directly to the output register, cdx(A/D), or go to a third-order IIR digital high-pass filter and then to the output register. The –3 dB corner frequency of the high-pass filter is approximately 270 Hz. This filter exceeds the VSELP preprocessing requirements of IS-54 for attenuation of 60 Hz and 120 Hz signals. The high-pass filter is selected by writing the HPFE field in the cioc3 register (see Table 10). The default value upon reset is the high-pass filter enabled (HPFE = 0).

Figure 4. CSP1027 A/D Path when in the Preamplifier Mode (EIGS = 0)

Figure 5. CSP1027 A/D Path in the External Gain Select Mode (EIGS = 1)

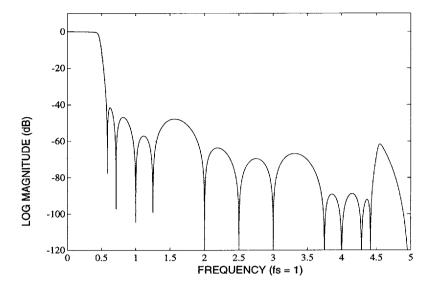

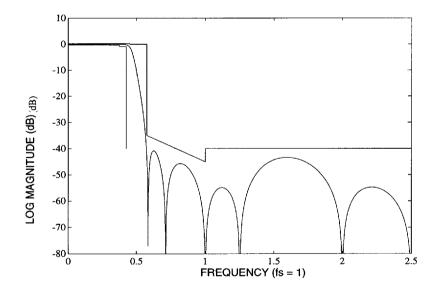

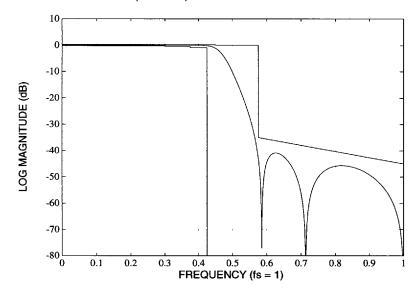

### A/D Path Frequency Response

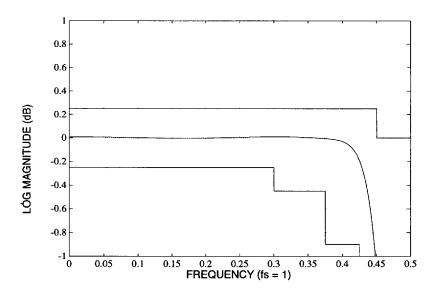

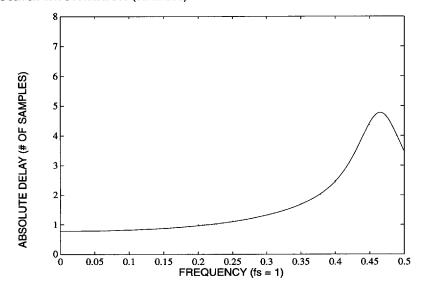

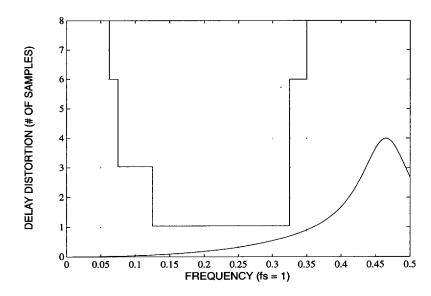

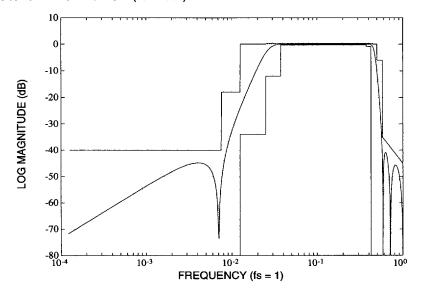

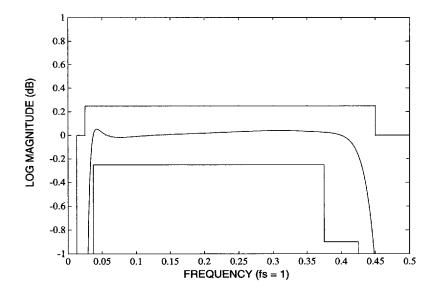

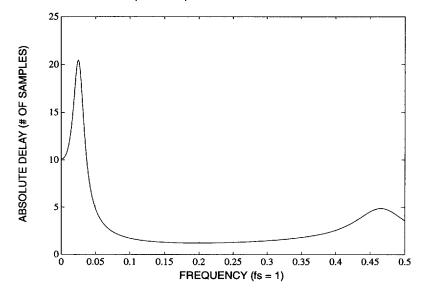

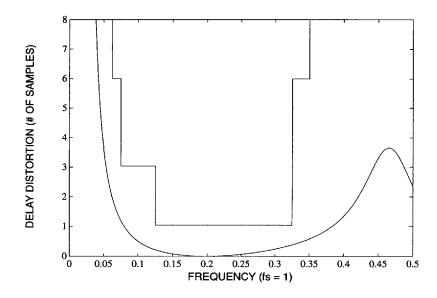

The composite digital filters (decimator, LPF, and HPF) meet the CCITT G.714 voiceband frequency response specifications and are suitable for IS-54, JDC, and GSM digital cellular applications. Figures 6, 7, 8, and 9 show the A/D and D/A frequency response without the optional high-pass filter (HPF). Figures 10 and 11 show the group delay characteristics of the A/D and D/A without the high-pass filter. Figures 12 and 13 show the frequency response of the high-pass filter. Figures 14 and 15 show the group delay characteristics of the highpass filter. In all figures, the frequency is normalized to the sampling frequency fs (i.e., frequency/fs). To get the actual frequency, multiply the normalized frequency by fs. The absolute delay and delay distortion have been normalized to the sampling period 1/fs (i.e., delay x fs). To obtain the actual delay, divide the normalized delay by fs. The templates shown in Figures 7, 8, 9, 11, 12, 13, and 15 correspond to the limits in the CCITT G.714 specification where  $f_s = 8.0 \text{ kHz}$ .

### **PCM Saturation Versus Analog Input Levels**

16-bit two's complement saturation is employed to prevent wraparound during input overload conditions. The saturation is hard-limiting:

0x7fff = Maximum positive level

0x8000 = Minimum negative level

The analog levels that correspond to the saturation levels for the three input modes are outlined in Table 14.

Figure 6. A/D or D/A Path Frequency Response over 5 fs Bandwidth (HPF Disabled)

Figure 7. A/D or D/A Path Frequency Response over 2.5 fs Bandwidth (HPF Disabled)

Figure 8. A/D or D/A Path Frequency Response over fs Bandwidth (HPF Disabled)

Figure 9. A/D or D/A Path Frequency Response over 0.5 fs Bandwidth (HPF Disabled)

Figure 10. A/D or D/A Path Absolute Group Delay (HPF Disabled)

Figure 11. A/D or D/A Path Group Delay Distortion (HPF Disabled)

Figure 12. A/D or D/A Path Frequency Response over fs Bandwidth (HPF Enabled)

Figure 13. A/D or D/A Path Frequency Response over 0.5 fs Bandwidth (HPF Enabled)

Figure 14. A/D or D/A Path Absolute Group Delay (HPF Enabled)

Figure 15. A/D or D/A Path Group Delay Distortion (HPF Enabled)

### Digital-to-Analog Path

Starting at the bottom right of Figure 3, the  $\Delta$ - $\Sigma$  D/A conversion process begins with a 16-bit two's complement PCM signal read from the DI serial input. The PCM is interpolated up to 1 MHz in two stages and low-pass filtered at each stage to attenuate 8 kHz images.

The PCM input is latched into the cdx(D/A) register at a nominal word rate of 8 kHz. The signal is then optionally high-pass filtered. This filter has the same transfer function as the A/D high-pass filter.

A digital sample-and-hold increases the word rate by a factor of 5 from 8 kHz to 40 kHz. The seventh-order IIR digital low-pass filter then removes the spectral images between 4 kHz and 20 kHz and predistorts the passband to compensate for the filtering done during the interpolation up to the 1 MHz word rate. The transfer function of this low-pass filter is the same as the one employed in the A/D converter.

The output of the low-pass filter feeds a programmable gain adjustment block that serves as a volume control. The gain can be changed in 3 dB increments from 0 dB to -45 dB. The attenuation level is set by writing the OGSEL field in the cioc0 register (see Table 7).

The digital modulator block further increases the word rate by a factor of 25 from 40 kHz to 1 MHz. Through quantization and noise shaping, the digital  $\Delta$ - $\Sigma$  modulator creates 1-bit output words at 1 MHz.

The modulator 1-bit output drives a structure combining a 1-bit D/A converter and a second-order switched-capacitor filter having a cutoff frequency of 8 kHz (based on a 1 MHz clock). This is all shown as the D/A block in Figure 3.

This is followed by a second-order active Chebychev filter having a cutoff frequency of 35 kHz.

The passband ripple of the analog filters is small enough such that they have virtually no effect on the passband response.

The output amplifier buffers the analog filter output.

The frequency responses of the A/D and D/A paths are essentially the same. See Figures 6 through 15 for the magnitude and delay responses vs. frequency.

### 4.3 Programmable Features

#### Active/Inactive Modes

The CSP1027 has active and inactive modes of operation which are selected by the ACTIVE field in the cioc0 register (see Table 7). The default value upon reset and powerup is ACTIVE = 0 (i.e., inactive). In the inactive mode, the codec clocks are disabled, data transfers by the codec are disabled, and analog bias currents are shut off. This state is useful in battery-powered applications when prolonged periods of inactivity are expected. It takes approximately 600 ms for the codec to reach full steady-state performance in going from inactive to active. This is primarily due to the charging of the large external capacitors, Cref and Creg. However, the codec is functionally useful after 100 ms.

#### Input Select

When the A/D preamplifier is selected (EIGS = 0), the INSEL field of cioc0 (Table 7) switches the preamp input between the MICIN and AUXIN inputs. When external gain select is used (EIGS = 1), the INSEL field has no effect.

### A/D Input Ranges

When the preamplifier is used (EIGS = 0), the IRSEL field of the cioc0 register (Table 7) selects the 500 mVpeak range when IRSEL = 0 and the 160 mVpeak range when IRSEL = 1. IRSEL has no effect when the external gain select mode is used (EIGS = 1).

When EIGS = 1, the inverting amplifier of Figure 5 replaces the preamplifier. The input range in this mode is the following:

VFULL-SCALE =

$$\frac{Rin}{RfB} \times 1.578 \text{ V}_{peak}$$

#### **Output Mute Function**

The D/A converter output can be selectively muted with the MUTE field in the cioc0 register (see Table 7). The default value upon reset is muted (MUTE = 0). The mute function is implemented (Figure 3) internally by a MUX following the D/A input. Placing the mute function here causes the signal at the analog output to gradually decay/rise over approximately 1 ms upon muting/unmuting. This effect is due to the impulse response and group delay of the digital filters. This implementation will reduce any potentially undesirable transient effects such as pops, when the D/A is muted.

### **Output Gains**

The D/A converter output can be programmed in 3 dB increments with the OGSEL field in the cioc0 register (Table 7) to serve as a volume control.

### **Loopback Mode**

The codec has a programmable loopback mode, represented by the TEST field in the cioc0 field, (see Table 7). As shown in Figure 3, when TEST = 0, the codec is in its normal mode of operation. When TEST = 1, the loopback mode is activated. In loopback mode, the 1-bit PDM output signal from the analog modulator is received by the analog demodulator. At the same time. the 1-bit signal output from the digital modulator is received by the sinc-cubic filter in the A/D. This results in the analog input being looped back to the analog output through the A/D and D/A, and the digital input being looped back to the digital output through the digital filters. The loopback mode can be useful for evaluating analog performance of the codec in the target system without going through the digital filters. This mode is also useful for evaluating the response of the digital filters or in evaluating the read/write functions of the codec and cdx registers without having to provide an analog input to the A/D.

### **High-Pass Filter Select**

The high-pass filter in the A/D and D/A can be enabled or disabled with the HPFE field in the cioc3 register (see Table 10).

#### Dither

A dithering scheme is employed in the CSP1027 which decorrelates the periodic quantization noise of the D/A modulator to make it white noise.

$\Delta\text{-}\Sigma$  converters are popular due to their high tolerance to component mismatch present in integrated circuit fabrication processes. However,  $\Delta\text{-}\Sigma$  converters may suffer from periodic noise and spurious tone generation (in-band and out-of-band) due to the coarse quantization and feedback of the  $\Delta\text{-}\Sigma$  modulator. Although this periodic noise may exist at very low levels (for example, at about –90 dBm), it may be very objectionable to the listener while having virtually no impact on the resolution of the converter. The CSP1027 D/A uses a robust dithering scheme which eliminates any potential problems due to this phenomenon.

The DITHER field in the cioc3 register (see Table 10) disables this feature. The default value upon reset is DITHER = 0 (i.e., enabled). When the DITHER is disabled, the signal-to-noise ratio will generally be about 2 dB higher. The DITHER should be enabled if the CSP1027 is used in an audio application, i.e., where this device interfaces to an audio transducer. If the CSP1027 is used in an application other than audio, such as data communications, the DITHER can be disabled if so desired.

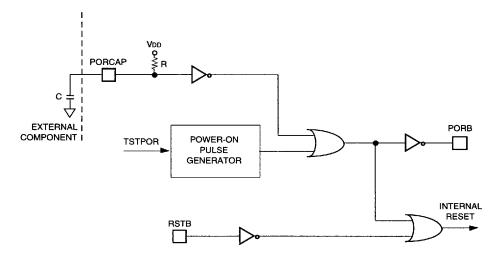

### 4.4 Power-On Reset

#### Internal

The CSP1027 has a power-on reset circuit that internally is OR'd with the inversion of the reset pin, RSTB, to form the internal reset (see Figure 16). The power-on reset circuit's inverted output is also itself an output pin, PORB. The PORB can be used to provide power-on reset to the system.

The power-on reset circuit is composed of two pulsegenerating elements, its output being the OR of the two. One element is entirely internal and generates a power-on pulse of 1.5 ms to 7.0 ms. The second element is composed of an input pin, PORCAP, a resistor connected between PORCAP and VDD, and an inverting input buffer. The user selects the capacitor value to connect between PORCAP and ground that will generate a power-on pulse of desired width. The pin POR-CAP allows the user to lengthen the power-on reset pulse to a width greater than the internal power-on element provides. The nominal value of the resistor is 155 k $\Omega$ , and the threshold of the inverting input buffer is 0.6 x VDD. The formula that relates the power-on reset pulse delay to the PORCAP capacitor is as follows:

$$T_D = -R \times C \times log_e (1 - 0.6)$$

$T_D = 0.9163 \times R \times C$

Hence, to generate a 14.2 ms power-on reset pulse, one would use a 0.1  $\mu$ F capacitor connected between PORCAP and Vss.

An internal power-on pulse can be initiated after poweron by writing a one to the TSTPOR field in the cioc3 register (see Table 10). This causes the internal poweron pulse of 1.5 ms to 7.0 ms to be generated. The pulse resets the device and appears on the PORB output pin.

Figure 16. Power-On Reset Diagram

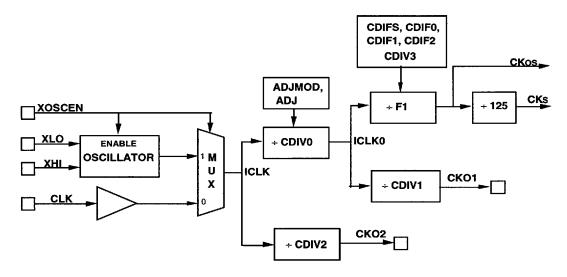

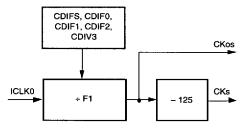

Figure 17. Clock Generation

### 4.5 Clock Generation

Figure 17 shows the clock generation and distribution for the CSP1027. The programmable dividers can customize the codec sample and master clock rates for a variety of applications in addition to standard 8 kHz sampling, while allowing a range of values for the crystal-controlled input clock. In Figure 17, XOSCEN is a chip input to enable the crystal oscillator circuit. XLO and XHI are the two leads for the crystal. CLK is the chip clock input if the crystal is not used. CKS is the internal codec sample clock, typically 8 kHz. CKos is the internal codec oversampled clock, typically 1 MHz. CKO1 and CKO2 are general-purpose clocks brought out to chip pins. CDIV1 and CDIV2 are programmable dividers with a range from 1 to 31. CDIV0 is programmed to be 1 or 2, but extra clock pulses can be added or subtracted at the output for one period of time following a write to the control register cioc1. This onetime increase or decrease in the number of clocks is programmed by ADJMOD and ADJ and causes a phase shift in the CKO1 and CKS output. F1 is an integral or a fractional divider controlled by the five programmable coefficients shown connected to it. With the fractional divide, the period of CKos will vary, but the period of CKS will be constant.

The following discussion begins with the crystal oscillator and is followed by a detailed description of each divisor block. Section 7.5 provides some examples of how to program the clocks.

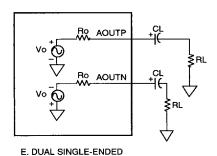

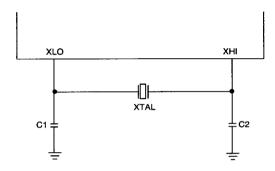

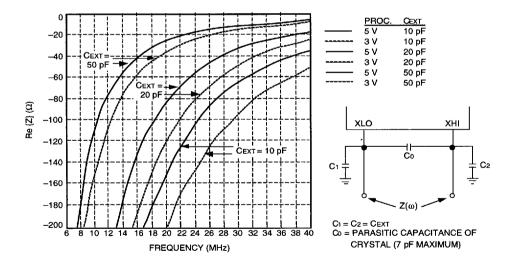

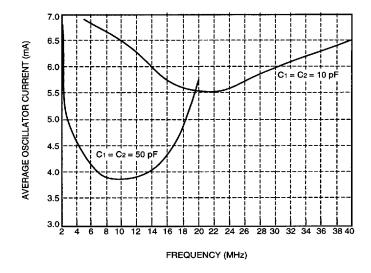

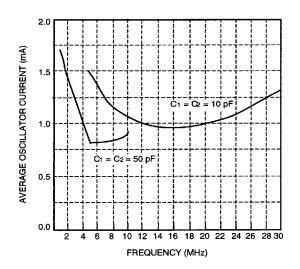

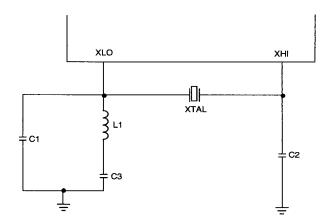

### **Crystal Oscillator**

The CSP1027 has a selectable on-chip clock oscillator. A logic 1 on the XOSCEN pin enables the crystal oscillator. A logic 0 disables the oscillator, powers it down, and selects the input buffer connected to the CLK pin.

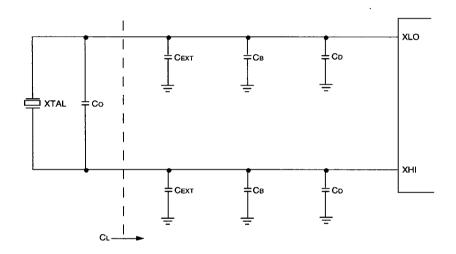

To use the oscillator, select a 20 MHz to 30 MHz fundamental-mode crystal with a series resistance less than 60  $\Omega$  and a mutual capacitance less than 7.0 pF. Connect the crystal between the XLO and XHI pins, and add 10 pF capacitors between XLO and ground, and XHI and ground. The XOSCEN pin enables and disables the crystal oscillator. See the application information on optimizing the oscillator performance.

### Clock Divider 2

The CDIV2 field in cioc0 (see Table 7) sets the clock divider that generates the output clock, CKO2. The clock output is a general-purpose clock that can be used to clock external logic or processors. CDIV2 ranges from 1 to 31, with 0 holding the output low. RSTB going low sets CDIV2 to +16. CKO2 is active while RSTB is low and synchronized by RSTB going high.

### **Clock Divider 0**

The CDIV0 field in cioc1 (see Table 8) sets the clock divider that generates the internal clock 0 (ICLK0) to either divide by one or divide by two. The ADJMOD and ADJ fields in cioc1 are used to adjust the phase of ICLK0 by increasing or decreasing the rate of ICLK0 for a burst of pulses, one time only. This event occurs each time control register cioc1 is written with nonzero values of ADJ. For example, let CDIV0 be set to +2, ADJ to seven, and ADJMOD to one (advance). After this word is written to the cioc1 register, seven ICLK0 pulses will occur at the same rate as ICLK, not divided by two. These seven clock pulses shift the phase of CKos, CKs, and CKO1 earlier, thus advancing these clocks. If ADJMOD is set to zero (retard), the +2 becomes a +3 for seven pulses of ICLK0. The CDIV0 clock divider is temporarily changed internally so that it divides by one greater, to retard the clocks, or one less, to advance the clocks, for the specified number of ICLK0 cycles. Note that the CDIV0 clock divider must be set to divide by two in order to advance and retard the clocks. If CDIV0 clock divider is set to divide by 1, one can only retard the clocks.

CDIVO has values of 1 or 2, ADJMOD is 0 or 1, and ADJMOD ranges from 1 to 127, with 0 selecting no clock adjust. RSTB going low sets CDIVO to ÷2. ICLKO is active while RSTB is low and synchronized by RSTB going high.

#### Clock Divider 1

The CDIV1 field in cioc1 (see Table 8) sets a clock divider that generates the CKO1 output clock. This general-purpose clock output can be used for clocking another codec in the system, such as the CSP1084. The ability to phase adjust the output clock and the codec sampling clock simultaneously is an important feature. CDIV1 ranges from 1 to 31, with 0 disabling the output. RSTB going low sets CDIV1 to ÷16. CKO1 is active while RSTB is low and synchronized by RSTB going high.

#### Sampling Clocks Generation

The oversampling codec clock CKos, typically 1 MHz, is used in the front sections of the A/D and the back sections of the D/A. The lower-frequency codec clock, CKs, typically 8 kHz, is the sample clock at the output of the A/D and the input to the D/A. The sampling clock frequency, fs, is the oversampling clock frequency, fos, divided by 125 (the fixed oversampling ratio). The divide by 125 must remain fixed, since it is constrained by the architecture of the codec digital filters. Many systems, however, have fixed high-frequency clocks and fixed sampling clocks, so it is necessary to have a great deal of flexibility in the creation of the codec clock CKs. The CSP1027 solves this problem in a unique way, by providing a programmable, fractional divider, F1.

F1 is the programmable ratio between ICLK0 and CKos. The equation for F1 is:

$$F1 = M + \left(S \times \frac{N}{125}\right)$$

where  $3 \le M \le 64$ ,  $0 \le N \le 62$ , and  $S = \{1, -1\}$ ;

or M = 2,  $0 \le N \le 62$ , and S = 1;

or M = 1, N = 0, and S = 1.

M is encoded by CDIV3 (Table 3), N is encoded by CDIF0, CDIF1, and CDIF2 (Table 5), and S is encoded by CDIFS (Table 4).

CKs is generated by dividing CKos by 125. The frequency of CKs can be described by:

$$fs = fos \div 125 = \left[ ficko \div \left( M + S \times \frac{N}{125} \right) \right] \div 125$$

Note that when N = 0, ICLK0 is simply divided by the integer M to create the oversampling clock, CKos. This is the preferred method for generating the sampling clock. If N  $\neq$  0, the fractional division results in an oversampling clock, CKos, whose period varies with time such that the average period is the desired fraction. This variation in the oversampling clock period is minimized by the clock generator but can cause distortion in the codec. Because the denominator of the fraction is fixed at 125, the period of the sampling clock, CKs, will be an integer multiple of the period of the internal clock, ICLK0, and will not vary. This is more clearly shown by the following equation:

$$\frac{\text{ficlk0}}{\text{fs}} = (125 \times \text{M}) + (\text{S} \times \text{N})$$

The expanded equation below explains what is happening in the time domain:

$$\frac{1}{fs} = \left[ (125 - N) \times \frac{M}{ficlk0} \right] + \left[ N \times \frac{(M+S)}{ficlk0} \right]$$

During each sampling period,  $\frac{1}{fs}$ , there are (125 – N)

oversampling clock cycles of period  $\frac{M}{\text{ficLK0}}$  and N

oversampling clock cycles of period  $\frac{(M+S)}{\text{ficLK0}}$ . The N

oversampling clock cycles are evenly distributed among the (125 – N) oversampling clock cycles to minimize the distortion due to oversampling clock cycles of differing period. The values for CDIF[0—2] in Table 5 have been selected to achieve the even distribution.

The procedure for selecting M, S, and N is illustrated in Section 7.5. The ranges for the programmable dividers are summarized in the Table 2.

**Table 2. Programmable Divider Summary**

| Clock Ratio        | ICLK/ICLK0 | ICLK0/CKOS         | ICLK0/CKS          | ICLK/CKO2    | ICLK0/CKO1   |

|--------------------|------------|--------------------|--------------------|--------------|--------------|

| Variable Name      | CDIV0      | M ± N<br>125       | 125M ± N           | CDIV2        | CDIV1        |

| Range of<br>Values | 1, 2       | 1, 2 to 64.496     | 125, 250 to 8062   | Off, 1 to 31 | Off, 1 to 31 |

| Encoding           | 0, 1       | See Table 3, 4, 5. | See Table 3, 4, 5. | 0 to 31      | 0 to 31      |

Table 3. CDIV3 Value for Each M

| M  | CDIV3   |

|----|---------|

| 1  | 00 0001 |

| 2  | 00 0010 |

|    |         |

|    |         |

| 62 | 11 1110 |

| 63 | 11 1111 |

| 64 | 00 0000 |

Table 4. CDIFS Value for Each S

| S  | CDIFS |

|----|-------|

| +1 | 0     |

| -1 | 1     |

Table 5. CDIF0, CDIF1, CDIF2 Values for Each N

| N  | CDIF0   | CDIF1   | CDIF2  |

|----|---------|---------|--------|

| 0  | 00 0000 | 00 0000 | 0 0000 |

| 1  | 11 1111 | 00 0000 | 0 0000 |

| 2  | 11 1101 | 00 0010 | 0 0000 |

| 3  | 10 1001 | 00 0010 | 0 0000 |

| 4  | 01 1111 | 00 0000 | 0 0000 |

| 5  | 01 1001 | 00 0000 | 0 0000 |

| 6  | 01 0101 | 10 0110 | 0 0000 |

| 7  | 01 0010 | 10 0100 | 0 0000 |

| 8  | 00 1111 | 00 0010 | 0 0000 |

| 9  | 00 1110 | 10 0101 | 0 0000 |

| 10 | 00 1100 | 00 0010 | 0 0000 |

| 11 | 00 1011 | 00 0010 | 0 0010 |

| 12 | 00 1010 | 00 0010 | 0 0010 |

| 13 | 00 1001 | 00 0010 | 1 0010 |

| 14 | 00 1001 | 10 0111 | 0 0010 |

| 15 | 00 1000 | 00 0011 | 0 0000 |

| 16 | 00 1000 | 10 0100 | 0 0010 |

| 17 | 00 0111 | 00 0011 | 0 0000 |

| 18 | 00 0111 | 10 1001 | 0 0010 |

| 19 | 00 0110 | 00 0010 | 1 0011 |

| 20 | 00 0110 | 00 0011 | 0 0010 |

| 21 | 00 0110 | 10 1011 | 0 0000 |

| 22 | 00 0101 | 00 0010 | 1 0010 |

| 23 | 00 0101 | 00 0010 | 0 0010 |

| 24 | 00 0101 | 00 0100 | 0 0010 |

| 25 | 00 0101 | 00 0000 | 0 0000 |

| 26 | 00 0101 | 10 0100 | 0 0010 |

| 27 | 00 0100 | 00 0010 | 1 0011 |

| 28 | 00 0100 | 00 0010 | 0 0011 |

| 29 | 00 0100 | 00 0011 | 0 0000 |

| 30 | 00 0100 | 00 0101 | 0 0010 |

| 31 | 00 0100 | 00 0000 | 0 0000 |

| N  | CDIF0   | CDIF1   | CDIF2  |

|----|---------|---------|--------|

| 32 | 00 0100 | 10 1000 | 0 0010 |

| 33 | 00 0100 | 10 0100 | 0 0010 |

| 34 | 00 0011 | 00 0010 | 1 0010 |

| 35 | 00 0011 | 00 0010 | 1 0100 |

| 36 | 00 0011 | 00 0010 | 0 0100 |

| 37 | 00 0011 | 00 0011 | 1 0010 |

| 38 | 00 0011 | 00 0011 | 0 0010 |

| 39 | 00 0011 | 00 0100 | 0 0010 |

| 40 | 00 0011 | 00 0111 | 0 0000 |

| 41 | 00 0011 | 00 1110 | 0 0000 |

| 42 | 00 0011 | 11 0110 | 0 0000 |

| 43 | 00 0011 | 10 1001 | 0 0000 |

| 44 | 00 0011 | 10 0110 | 0 0000 |

| 45 | 00 0011 | 10 0100 | 0 0010 |

| 46 | 00 0011 | 10 0011 | 0 0010 |

| 47 | 00 0010 | 00 0010 | 1 0010 |

| 48 | 00 0010 | 00 0010 | 1 0011 |

| 49 | 00 0010 | 00 0010 | 1 0101 |

| 50 | 00 0010 | 00 0010 | 0 0000 |

| 51 | 00 0010 | 00 0010 | 0 0011 |

| 52 | 00 0010 | 00 0010 | 0 0010 |

| 53 | 00 0010 | 00 0011 | 1 0011 |

| 54 | 00 0010 | 00 0011 | 0 0011 |

| 55 | 00 0010 | 00 0011 | 0 0010 |

| 56 | 00 0010 | 00 0100 | 0 0010 |

| 57 | 00 0010 | 00 0101 | 0 0000 |

| 58 | 00 0010 | 00 0110 | 0 0000 |

| 59 | 00 0010 | 00 0111 | 0 0010 |

| 60 | 00 0010 | 00 1010 | 0 0010 |

| 61 | 00 0010 | 00 1111 | 0 0010 |

| 62 | 00 0010 | 00 0000 | 0 0000 |

### 4.6 Serial I/O Configurations

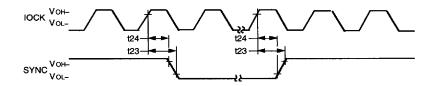

#### **Codec Data Transfer**

When the codec is active, ACTIVE = 1 (see cioc0, Table 7), it loads data into the cdx(A/D) and empties data from the cdx(D/A) register (see Figure 3) at the sampling frequency, fs (which is 8 kHz based on a 1 MHz oversampling frequency). The codec data transfers occur independent of the serial input/output data transfers described below. The data is double buffered, allowing the codec to transfer data to or from the cdx while the serial I/O is shifting data into or out of the shift registers (isr and osr). When the codec is set to inactive, ACTIVE = 0, there are no codec data transfers to the cdx(A/D) or from the cdx(D/A).

The internal STATUS flag is set high when cdx(A/D) is loaded and cdx(D/A) is emptied. Loading data from the cdx(A/D) into the output shift register, osr, or loading data from the input shift register, isr, into the cdx(D/A) due to a serial I/O transaction, clears the internal STATUS flag. The internal STATUS flag can be observed on the data output, DO, pin in the passive mode and causes data transfers in the active and multiprocessor modes.

#### **Codec Control Writes**

The four control registers are written through the serial port. The serial address, SADD, selects between control and data transfers. Bits 15 and 14 of the control word being transferred select which control register, cioc0, cioc1, cioc2, or cioc3, is written (i.e., cioc0: Bit[15:14] = 00, cioc1: Bit[15:14] = 01, etc.).

#### Serial I/O Port Overview

The CSP1027 serial I/O unit is an asynchronous, full-duplex, double-buffered channel operating at up to 20 Mbits/s that easily interfaces with other AT&T fixed-point DSPs (i.e., DSP16A and AT&T DSP1610/1616/1617/1618) in a single or multiple DSP environment. Commercially available codecs and time-division multiplexed (TDM) channels can be interfaced to the CSP1027 device with little, if any, external logic.

The serial interface is a subset of the standard AT&T DSP serial I/O and is comprised of eight pins:

- A single passive serial input/output clock (IOCK).

- A combined input load, output load, and synchronization (SYNC).

- Serial data input (DI).

- Serial data output (DO).

- Serial address (SADD).

- Three serial mode select pins (SMODE[2:0]).

The CSP1027's serial I/O is different from the standard AT&T serial I/O in a number of ways:

- The SMODE[1:0] pins configure the serial I/O port into one of four possible ways: a passive SIO configuration, an active SIO configuration, and two multiprocessor SIO configurations.

- A fixed most significant bit (MSB) first data format.

- A fixed 16-bit data mode.

- The serial address (SADD) is an input during the passive and active SIO configurations to select between data and control SIO transfers. It is intended to be connected to the DSP's SADD pin, which is an output during passive and active SIO. Note that the DSP's SADD output is inverted and is composed of two 8-bit fields that are shifted out least significant bit (LSB) first.

- The multiprocessor mode time slots and serial addresses are restricted to two sets, one of which is selected based on the state of SMODE0.

- The SMODE2 pin should always be tied low for the serial I/O port to operate as described.

- The frequency of the serial I/O interface clock input IOCK (Fiock) must be greater than the frequency of the internal oversampling clock (Fiock).

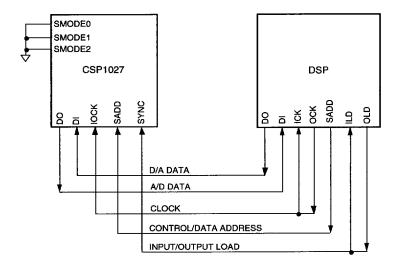

Figure 18. Passive Communication and Connections

#### Passive I/O Configuration (SMODE[1:0] = 00)

The passive SIO configuration allows the user maximum flexibility in interfacing the CSP1027 to a variety of system hardware configurations. It requires that the user supply a serial input/output clock, IOCK, and perform data transfers at the sampling rate, fs. Serial data transfers can be made to occur at the sampling rate by applying a clock that is synchronous with the codec clock, ICLK, to the SYNC pin or by polling the codec STATUS flag, which indicates that the cdx(A/D) register is full and the cdx(D/A) register is empty. The STATUS flag appears on DO when the SADD pin selects a control word.

Passive SIO is selected by setting both SMODE1 and SMODE0 low. The input/output clock, IOCK, is an input and the common input/output load, SYNC, (equivalent to a DSP16A's ILD and OLD tied together) is also an input. Serial data input, DI, is an input and serial data output, DO, is an output. The serial address, SADD, is an input, which determines if the transfer is to the control registers, cioc[0:3], or the data register, cdx(D/A).

A high-to-low transition of SYNC pin signal, latched by the next rising edge of IOCK, initiates the start of an input and output transaction. If the CSP1027's output buffer, cdx(A/D), is full, it will be loaded into the output shift register (osr) and shifted out on the DO pin. The CSP1027 shifts in the data from the DI pin into its input shift register (isr). A serial transmit address on the

SADD line is received simultaneously with data on the DI line. If SADD is high for the first 15 bits, corresponding to a zero serial transmit address, this causes the isr to be latched into cdx(D/A) after 16 bits have been shifted in. If SADD is low for any of the first 15 bits, corresponding to a nonzero transmit address, this causes the isr to be latched into cioc[0:3] and also changes the output data stream on DO to display the internal codec STATUS flag. If SADD is low for any clock cycle, while not involved in a serial transaction, the codec STATUS flag is displayed on the DO pin until the next data transfer

An example of the passive SIO configuration is shown in Figure 18. The DSP supplies both the serial clock, IOCK, and the sampling synchronization signal to SYNC, or polls the internal codec STATUS flag to determine when a data transmission is needed. This configuration allows the user maximum flexibility in interfacing the CSP1027 to a variety of other system hardware configurations.

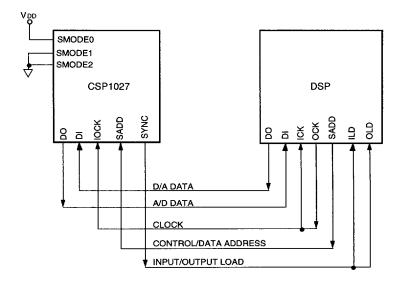

Figure 19. Active Communication and Connections

### Active I/O Configuration (SMODE[1:0] = 01)

The active SIO configuration causes the CSP1027 to generate an active input/output load (SYNC) to perform input/output transmissions when needed. The user supplies only a serial input/output clock, IOCK.

The active SIO is selected by setting SMODE1 low and SMODE0 high. The input/output clock, IOCK, is an input and the input/output load, SYNC, is an output. While the codec is inactive, ACTIVE = 0 (see Table 7, cioc0 register), SYNC generates serial I/O transfers at an IOCK + 16 rate to allow loading the codec control registers, cioc[0:3]. While the codec is active, ACTIVE = 1 (see Table 7, cioc0 register), SYNC generates serial I/O transfers at the sampling rate, synchronized to the codec's emptying of the cdx(D/A) and loading of the cdx(A/D). The serial address, SADD, functions as described previously for the passive SIO configuration, but with the SYNC pin being active and determining data transfers, the need for polling the codec STATUS flag is eliminated. The serial address during the data stream still is used to determine whether data in the input shift register is latched into cdx(D/A) or cioc[0:3] at the end of the transaction. Note that cioc0, with ACTIVE = 1, should be written last since this will change the rate of serial I/O transfers from IOCK + 16 to the sampling rate.

An example of the active SIO configuration is shown in Figure 19. The DSP supplies the serial clock, IOCK, while the CSP1027 supplies the input/output load, SYNC. The serial address, SADD, is connected so that writing the DSP's srta register addresses the cdx(D/A) when srta =0x0, or the cioc0, cioc1, cioc2, cioc3 when srta = 0x1. The DSP can activate the codec by writing the cioc0 register in the CSP1027, and then letting its input buffer full flag (IBF) indicate when the CSP1027 has transferred data. This is the preferred interface for a single DSP and a CSP1027.

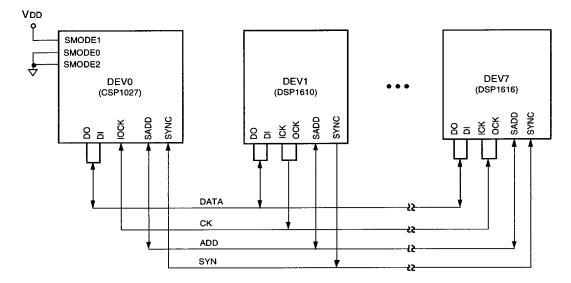

Figure 20. Multiprocessor Communication and Connections

### Multiprocessor Configuration (SMODE[1:0] = 1X)

The CSP1027 serial I/O supports a multiprocessor mode that allows multiple devices to be connected together to provide data transmission between any of the individual devices. This mode requires po external hardware and uses a time-division multiplex (TDM) interface with eight time slots per frame.

Figure 20 shows an example of a multiprocessor system with multiple DSPs and a CSP1027. The following pins are connected together to form a four-wire bus:

- DI and DO from the CSP1027s and DSPs form a data line referred to as DATA.

- IOCK from the CSP1027s and ICK and OCK from the DSPs form a clock line referred to as CK.

- SADD from the CSP1027s and DSPs form an address line referred to as ADD.

- SYNC from the CSP1027s and DSPs form a synchronization line referred to as SYN.

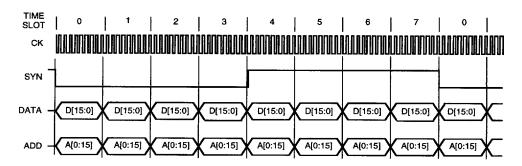

Figure 21 shows the time-slot allocation timing used in multiprocessor mode. One frame is defined as the time between SYN high-to-low transitions. Each frame is divided into eight time slots of 16 bits each. A high-to-low transition of SYN defines the beginning of time slot 0 and also resynchronizes any devices which are operating on the multiprocessor bus with SYN as an input.

Note that the DSP device which drives the multiprocessor bus during time slot 0 also drives the SYN line.

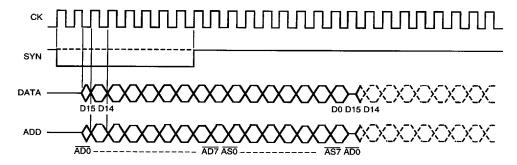

Each CSP1027 sends data in a time slot determined by its SMODE0 pin. Each DSP sends data in a time slot or time slots determined by its tdms register. Only one device can be assigned a particular time slot, and each of the eight time slots must be assigned to a device (note that one device can be assigned more than one time slot). These requirements must be met by the user's choice of CSP1027's SMODE0 connections and the DSP's tdms register contents. A CSP1027 is assigned to time slot 2 if SMODE0 is low or to time slot 5 if SMODE0 is high. This allows up to two CSP1027s to be placed on a multiprocessor bus.

The DSP input/output format can be configured to either most significant bit (MSB) first or least significant bit (LSB) first. The CSP1027 only supports MSB first format; hence, the DSPs connected on a multiprocessor bus must be using MSB first data format, configured in the sioc register, when transferring and receiving data and control words with the CSP1027.

11-22 Conversion Signal Processors

AT&T Wireless Products Data

During each time slot (see Figure 22), the device that is assigned to that time slot drives the ADD and DATA lines. If the assigned device's output buffer is full, it loads its output shift register and shifts the 16 bits of data, MSB first, out DO onto the DATA line. The 8-bit transmit address is inverted and shifted out, LSB first, onto the ADD line at the same time as the first 8 bits of data. The inverted 8-bit protocol information is then shifted out, LSB first, on the ADD line at the same time as the last 8 bits of data. The CSP1027's transmit address, AT[7:0], is determined by the SMODE0 pin (see Table 6). The DSP's transmit address is determined by the srta register. The CSP1027's protocol information is always all zeros, which is inverted to appear as all ones on the ADD line. The DSP's protocol information is determined by the saddx register. If during a time slot the assigned device's output buffer is empty, then zeros are shifted out on the DATA line and zeros are shifted and inverted to become ones on the ADD line.

During each time slot, each device receives the data on the DATA line and inverts and receives the address and protocol information on the ADD line. Each device compares the transmitted 8-bit address with its receive address. If the transmitted address and the device's receive address have at least one occurrence of a one in the same bit location, the address matches and the device transfers the data from the input shift register to its input buffer. If the transmitted address and the receive address do not match, the data remains in the input shift register and is overwritten during the next time slot. The DSP's receive address is determined by its srta register. Each CSP1027 has two receive addresses, one for data and another for control, the values of these two addresses are determined by the SMODE0 pin (see Table 7). When the data receive address matches, the input shift register is loaded into the cdx(D/A) register. When the control receive address matches, the input shift register is loaded into one of the four cioc registers, based upon the two most significant bits of the 16-bit word. The CSP1027 ignores the protocol information.

Multiprocessor communication with a CSP1027 is intended to follow the sequence:

- The DSP writes the control registers, cioc[0:3], in the CSP1027 to configure the clock dividers and codec. The codec is also activated.

- The CSP1027's A/D fills the output buffer, cdx(A/D), and empties the input buffer, cdx(D/A), at the same time. This causes the A/D data to be transmitted by the CSP1027 to the DSP during the next CSP1027 time slot. The DSP's receive address is set to match the CSP1027's transmit address.

- 3. When the DSP receives A/D data from the CSP1027, it responds by sending D/A data to the CSP1027 during the DSP's next time slot. The DSP's transmit address is set to match the CSP1027's data receive address. The new data is loaded into the CSP1027's cdx(D/A) register to be used as the next D/A sample.

- If the DSP wants to send a control word to the CSP1027 to change the configuration or inactivate the codec, this can be done by setting the DSP's transmit address to match the codec's control receive address.

Note that since the CSP1027 sends all zeros for the protocol information, this will have to be used to identify the A/D data from the CSP1027. If two CSP1027s are connected to the multiprocessor bus and the DSP's receive address is set to match both CSP1027's transmit addresses, the DSP will have to identify which A/D data came from which CSP1027 by the order in which the data arrives, since both CSP1027s will be sending the same protocol information.

Figure 21. Multiprocessor Frame Timing

Table 6. Hardwired CSP1027 Multiprocessor Time Slot and Addresses

|                                           | SMODE0 = 0 | SMODE0 = 1 |

|-------------------------------------------|------------|------------|

| Transmit Time Slot                        | 2          | 5          |

| Data, cdx(A/D), Transmit Address [7:0]    | 0000 0100  | 0010 0000  |

| Data, cdx(D/A), Receive Address [7:0]     | 0000 1000  | 0100 0000  |

| Control, cioc[0:3], Receive Address [7:0] | 0001 0000  | 1000 0000  |

Figure 22. Multiprocessor Time-Slot Timing

### **5 Register Information**

Tables 7 through 10 describe the programmable registers of the CSP1027 device.

### 5.1 Codec I/O Control 0 (cioc0) Register

Table 7. Codec I/O Control 0 (cioc0) Register

| Bit   | 15—14 | 13   | 12     | 11—8  | 7    | 6     | 5     | 4—0   |

|-------|-------|------|--------|-------|------|-------|-------|-------|

| Field | Reg   | TEST | ACTIVE | OGSEL | MUTE | IRSEL | INSEL | CDIV2 |

| Field  | Value   | Description                                      |

|--------|---------|--------------------------------------------------|

| Reg    | 00      | Indicates control register 0.                    |

| TEST   | 0*      | Normal operation.                                |

|        | 1       | Testability mode—analog and digital loopback.    |

| ACTIVE | 0*      | Codec set to inactive mode (i.e., powerdown).    |

| ļ      | 1       | Codec set to active mode.                        |

| OGSEL  | 1111    | Output gain adjustment of 0 dB.                  |

| ļ      | 1110    | Output gain adjustment of -3 dB.                 |

|        | 1101    | Output gain adjustment of -6 dB.                 |

|        |         | •                                                |

|        |         |                                                  |

|        | •       |                                                  |

|        | 0001    | Output gain adjustment of -42 dB.                |

|        | 0000*   | Output gain adjustment of -45 dB.                |

| MUTE   | 0*      | Output signal muted.                             |

|        | _1      | Output signal not muted.                         |

| IRSEL  | 0*      | Microphone preamplifier input range: 500 mVpeak. |

|        | 1       | Microphone preamplifier input range: 160 mVpeak. |

| INSEL  | 0*      | Select microphone input, MICIN.                  |

|        | 1       | Select auxiliary input, AUXIN.                   |

| CDIV2  | 0 0000  | Output clock 2, CKO2, disabled.                  |

|        | 0 0001  | Output clock 2, CKO2 = ICLK ÷ 1.                 |

|        | 0 0010  | Output clock 2, CKO2 = ICLK ÷ 2.                 |

|        |         |                                                  |

|        |         |                                                  |

|        | •       |                                                  |

|        | 1 0000* | Output clock 2, CKO2 = ICLK ÷ 16.                |

|        |         |                                                  |

|        |         |                                                  |

|        |         |                                                  |

|        | 1 1110  | Output clock 2, CKO2 = ICLK ÷ 30.                |

|        | 1 1111  | Output clock 2, CKO2 = ICLK ÷ 31.                |

<sup>\*</sup> Value upon reset.

### Register Information (continued)

### 5.2 Codec I/O Control 1 (cioc1) Register

Table 8. Codec I/O Control 1 (cioc1) Register

| Bit   | 15—14 | 13     | 126      | 5     | 40    |

|-------|-------|--------|----------|-------|-------|

| Field | Reg   | ADJMOD | ADJ[6:0] | CDIV0 | CDIV1 |

| Field  | Value     | Description                                                             |

|--------|-----------|-------------------------------------------------------------------------|

| Reg    | 01        | Indicates control register 0.                                           |

| ADJMOD | 0*        | Select retard mode for internal clock, ICLK0, adjustment.               |

| :      | 1         | Select advance mode for internal clock, ICLK0, adjustment.              |

| ADJ    | 000 0000* | Internal clock, ICLK0, not adjusted.                                    |

|        | 000 0001  | Internal clock, ICLK0, adjusted by one ICLK cycle for one ICLK0 cycle.  |

|        | 000 0010  | Internal clock, ICLK0, adjusted by one ICLK cycle for two ICLK0 cycles. |

|        | •         |                                                                         |

|        | •         | •                                                                       |

| ļ      | •         |                                                                         |

|        | 111 1110  | Internal clock, ICLK0, adjusted by one ICLK cycle for 126 ICLK0 cycles. |

|        | 111 1111  | Internal clock, ICLK0, adjusted by one ICLK cycle for 127 ICLK0 cycles. |

| CDIV0  | 0         | Internal clock, ICLK0 = ICLK + 1.                                       |

|        | 1*        | Internal clock, ICLK0 = ICLK + 2.                                       |

| CDIV1  | 0 0000    | Output clock 1, CKO1, disabled.                                         |

|        | 0 0001    | Output clock 1, CKO1 = ICLK0 ÷ 1.                                       |

|        | 0 0010    | Output clock 1, CKO1 = ICLK0 ÷ 2.                                       |

|        | •         |                                                                         |

|        | •         |                                                                         |

|        | •         |                                                                         |

|        | 1 0000*   | Output clock 1, CKO1 = ICLK0 ÷ 16.                                      |

|        | •         |                                                                         |

|        |           |                                                                         |

|        |           |                                                                         |

|        | 1 1110    | Output clock 1, CKO1 = ICLK0 ÷ 30.                                      |

| * \/-1 | 1 1111    | Output clock 1, CKO1 = ICLK0 ÷ 31.                                      |

<sup>\*</sup> Value upon reset.

### Register Information (continued)

### 5.3 Codec I/O Control 2 (cioc2) Register

Table 9. Codec I/O Control 2 (cioc2) Register

| Bit   | 15—14 | 13       | 12    | 11—6  | 5—0   |

|-------|-------|----------|-------|-------|-------|

| Field | Reg   | Reserved | CDIFS | CDIF0 | CDIV3 |

| Field    | Value    | Description                                                         |  |  |

|----------|----------|---------------------------------------------------------------------|--|--|

| Reg      | 10       | Indicates control register 0.                                       |  |  |

| Reserved | 0*       | Reserved, always write 0.                                           |  |  |

| CDIFS    | 0*       | Sampling rate, CKs = ICLK0 + (CDIV3 x 125).                         |  |  |

|          |          | Sampling rate, CKs = ICLK0 ÷ 256. (Note: CDIV3 must be set to 2.)   |  |  |

|          | 1        | Sampling rate, CKs = ICLK0 ÷ 1458. (Note: CDIV3 must be set to 12.) |  |  |

|          | W        | Sampling rate, CKs = ICLK0 ÷ (125 x M + S x N). See Section 4.5.    |  |  |

| CDIF0    | 00 0000* | Sampling rate, CKs = ICLK0 ÷ (CDIV3 x 125).                         |  |  |

|          | 01 0101  | Sampling rate, CKs = ICLK0 ÷ 256. (Note: CDIV3 must be set to 2.)   |  |  |

|          | 00 0011  | Sampling rate, CKs = ICLK0 ÷ 1458. (Note: CDIV3 must be set to 12.) |  |  |

|          | wwwwwww  | Sampling rate, CKs = ICLK0 ÷ (125 x M + S x N). See Section 4.5.    |  |  |

| CDIV3    | 00 0001  | Oversampling clock, CKos = ICLK0 + 1.                               |  |  |

|          | 00 0010  | Oversampling clock, CKos = ICLK0 + 2.                               |  |  |

|          |          |                                                                     |  |  |

|          | :        |                                                                     |  |  |

|          | 11 1111  | Oversampling clock, CKos = ICLK0 ÷ 63.                              |  |  |

|          | 00 0000* | Oversampling clock, CKos = ICLK0 + 64.                              |  |  |

|          | WW WWWW  | Sampling rate, CKs = ICLK0 ÷ (125 x M + S x N). See Section 4.5.    |  |  |

<sup>\*</sup> Value upon reset.

### 5.4 Codec I/O Control 3 (cioc3) Register

Table 10. Codec I/O Control 3 (cioc3) Register

| Bit   | 15—14 | 13     | 12   | 11     | 10—6  | 5—0   |

|-------|-------|--------|------|--------|-------|-------|

| Field | Reg   | TSTPOR | HPFE | DITHER | CDIF2 | CDIF1 |

| Field                                     | Value    | Description                                                         |  |  |

|-------------------------------------------|----------|---------------------------------------------------------------------|--|--|

| Reg                                       | 11       | Indicates control register 0.                                       |  |  |

| TSTPOR                                    | 0*       | Normal operation.                                                   |  |  |

|                                           | 1        | Test on-chip power-on reset pulse generator.                        |  |  |

| HPFE 0* Enable high-pass fill             |          | Enable high-pass filter in A/D and D/A.                             |  |  |

|                                           | 1        | Disable high-pass filter in A/D and D/A.                            |  |  |

| DITHER 0* Enable dither on D/A converter. |          | Enable dither on D/A converter.                                     |  |  |

|                                           | 1        | Disable dither on D/A converter.                                    |  |  |

| CDIF2 0 0000* Sampling ra                 |          | Sampling rate, CKS = ICLK0 ÷ (CDIV3 x 125).                         |  |  |

|                                           | 0 0000   | Sampling rate, CKS = ICLK0 ÷ 256. (Note: CDIV3 must be set to 2.)   |  |  |

|                                           | 0 0000   | Sampling rate, CKS = ICLK0 ÷ 1458. (Note: CDIV3 must be set to 12.) |  |  |

|                                           | w wwww   | Sampling rate, CKS = ICLK0 + (125 x M + S x N). See Section 4.5.    |  |  |

| CDIF1                                     | 00 0000* | Sampling rate, CKS = ICLK0 ÷ (CDIV3 x 125).                         |  |  |

|                                           | 10 0110  | Sampling rate, CKS = ICLK0 ÷ 256. (Note: CDIV3 must be set to 2.)   |  |  |

|                                           | 11 0110  | Sampling rate, CKS = ICLK0 ÷ 1458. (Note: CDIV3 must be set to 12.) |  |  |

|                                           | wwwwwww  | Sampling rate, CKS = ICLK0 + (125 x M + S x N). See Section 4.5.    |  |  |

<sup>\*</sup> Value upon reset.

🔳 0050026 0017548 6T6 🖩

### **6 Signal Descriptions**

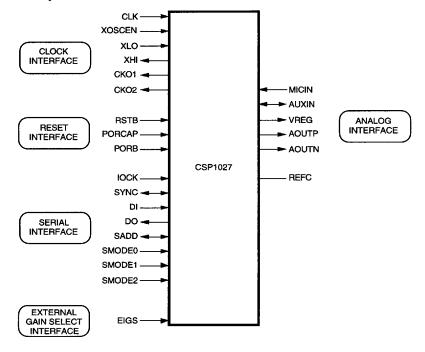

Figure 23. CSP1027 Pinout by Interface

Figure 23 shows the pinout by interface for the CSP1027. The signals can be separated into five interfaces as shown. These interfaces and the signals that comprise them are described below.

### 6.1 Clock Interface

The clock interface consists of the clock input, crystal oscillator, and clock outputs for the codec.

#### CLK

Clock Input: The input clock for the CSP1027 when the XOSCEN is a logic low. Codec operation restricts CLK to integer frequencies from 1 MHz to 40 MHz or specific multiples of 8 kHz. When XOSCEN is tied to logic high, the CLK input is not selected but should be tied low or high to minimize input buffer power.

### **XLO**

**Crystal Input:** The crystal for CSP1027 voiceband codec is connected between XLO and XHI. When the crystal is not being used, this pin is to be left floating and the CMOS clock applied to CLK.

#### XHI

**Crystal Output:** The crystal for CSP1027 handset codec is connected between XLO and XHI. When the crystal is not being used, this pin is to be left floating and the CMOS clock applied to CLK.

#### XOSCEN

**Crystal Oscillator Enable:** When a logic high, the crystal oscillator is selected for XLO and XHI pins. When a logic low, the input buffer is selected for CLK pin and the crystal oscillator is powered down.

Note: The XOSCEN pin does not have a pull-up or pull-down device. Make sure that it is tied to VDD, tied to Vss, or driven by valid logic levels.

11-28 Conversion Signal Processors

AT&T Wireless Products Data

### Signal Descriptions (continued)

#### CKO<sub>1</sub>

Clock Out 1: ICLK + CDIV1 (see Table 8, cioc1 register). General-purpose output clock that can be used by a baseband codec, such as the CSP1084.

#### CK<sub>02</sub>

Clock Out 2:. CLK + CDIV2 (see Table 7, cioc0 register). General-purpose output clock that can be used by a processor, such as the DSP1616.

#### 6.2 Reset Interface

The reset interface consists of the reset input, poweron reset input, and power-on reset output for the codec.

#### **RSTB**

Reset: A high-to-low transition causes entry into the reset state. The cioc[0:3] register bits are set to their default states.

#### PORB

**Power-On Reset:** A high-to-low transition indicates entry into the power-on reset state.

#### PORCAP

Power-On Reset Capacitor: A capacitor is to be attached to this pin for the power-on reset circuit. POR-CAP has an internal resistor (nominal value of 155  $k\Omega$ ) connected to digital power, VDD.

#### 6.3 Serial I/O Interface

The serial I/O interface consists of the serial clock input, synchronizing signal, data input, data output, serial address, and serial modes for the codec.

### SMODE 0

Serial Mode 0: Configures the CSP1027 serial I/O interface. When in active/passive mode (SMODE1 low), SYNC is an output when SMODE0 is high, and SYNC is an input when SMODE0 is low. In multiprocessor mode (SMODE1 high), SMODE0 selects between two possible time slots, and between two possible transmit and receive address combinations. See Table 6 in the architectural information for the addresses.

#### SMODE1

**Serial Mode 1:** Configures the CSP1027 serial I/O interface to multiprocessor mode when active-high; otherwise, active/passive mode is selected when low.

#### SMODE2

**Serial Mode 2:** Must be tied low to configure the CSP1027 serial I/O interface as described.

#### DI

**Serial Data Input:** Serial data input is latched on rising edge of IOCK, MSB first. DI and DO should be connected together when in multiprocessor mode.

#### DO

Serial Data Output: Serial data output from the output shift register (osr), MSB first, when the data register, cdx(A/D), is selected or codec status flag when the control registers, cioc[0:3], are selected. When an output, DO changes on the rising edges of IOCK. DI and DO should be connected together when in multiprocessor mode, SMODE1 high.

#### IOCK

**Serial Input/Output Clock:** Input clock for serial PCM input and output data.

Note: The frequency of the serial I/O interface clock input IOCK (FIOCK) must be greater than the frequency of the internal oversampling clock CKos (FCKOS).

### SYNC

Serial Input/Output Load Strobe and Sync: When not in multiprocessor mode, the falling edge of SYNC indicates the beginning of a serial input and a serial output word. The falling edge of SYNC loads the output shift register (osr) from the codec data register (cdx(A/D)). Sixteen IOCK clock cycles after the falling edge of SYNC, the codec data (cdx(D/A)) or control register (cioc) is loaded from the input shift register (isr). SYNC is an input when the SMODEO pin is low and an output when the SMODEO pin is high.

In multiprocessor mode, SYNC is the multiprocessor synchronization input signal. A falling edge of SYNC indicates the first word of a TDM I/O stream and causes the resynchronization of the internal input and output load generators.

0050026 0017550 254

### Signal Descriptions (continued)

#### SADD

Serial Address: When not in multiprocessor mode, SADD is an input that selects between the codec data registers, cdx(D/A) and cdx(A/D), and codec control registers, cioc[0:3]. SADD is inverted and latched on the rising edge of IOCK and compared against a zero for data and a one for control, to determine if input data on DI is loaded from the input shift register, isr, into cdx(D/A) or one of cioc[0:3]. Once SADD indicates a control word, the internal codec status flag appears on DO, replacing cdx(A/D). While not performing a serial transmission, SADD low causes the internal codec status flag to be output on DO.

In multiprocessor mode, SADD is an output when the tdms time slot dictates a serial output transmission; otherwise, it is an input. While an output, SADD is the inverted 8-bit serial transmit address output, LSB first. SADD changes on the rising edges of IOCK. While an input, SADD is inverted and latched on the rising edge of IOCK and compared against the cdx(D/A) and cioc[0:3] serial receive addresses to determine if input data on DI is loaded from the input shift register, isr, into cdx(D/A) or cioc.

### 6.4 External Gain Control Interface

The external gain control interface consists of one input.

#### **EIGS**

**External Input Gain Select:** A logic low or no connect selects the microphone preamplifier. A logic high selects the single op amp input mode where external resistors set the A/D input range. Note that EIGS is a digital pin whose input levels are relative to digital power and ground (VDD and Vss).

### 6.5 Digital Power and Ground

**V**<sub>DD</sub>

Digital Power Supply: 3 V to 5 V supply.

Vss

Digital Ground: 0 V.

### 6.6 Analog Interface

The analog interface consists of the two inputs, two outputs, a regulated output voltage reference, and a capacitor connection for the codec.

#### MICIN

Analog Input from Microphone: Low-level analog signal from electret condenser microphone selected by INSEL bit in codec control register, cioc0 (see Table 7).

#### **AUXIN**

Analog Input from Auxiliary: When used in preamplifier mode (EIGS = 0), AUXIN is a low-level analog signal selected by INSEL bit in codec control register, cioc0 (see Table 7). The characteristics of AUXIN are identical to MICIN.

When used in external gain select mode (EIGS = 1), AUXIN is the output of the inverting amplifier. The INSEL bit has no effect in this mode.

### AOUTP

Noninverting Analog Output: In conjunction with AOUTN, this output can drive a 2  $k\Omega$  load in differential mode or a 1  $k\Omega$  load ac-coupled to analog ground.

#### **AOUTN**

Inverting Analog Output: In conjunction with AOUTP, this output can drive a 2  $k\Omega$  load in differential mode or a 1  $k\Omega$  load ac-coupled to ground.

### **VREG**

**Regulated Output Voltage:** For electret condenser microphone. Vout =  $3 \text{ V} \pm 10\%$ , lout =  $250 \ \mu\text{A}$  max. A  $1 \ \mu\text{F}$  and  $0.1 \ \mu\text{F}$  ceramic type X7R capacitor to ground must be provided at this pin (see Figure 24).

#### REFC

External Capacitor Connection: Internal voltage regulator bypassing. A 0.22 μF ceramic type X7R capacitor to ground must be provided at this pin.

### 6:7 Analog Power and Ground

VDDA

Analog Power Supply: 5 V supply.

VSSA

Analog Ground: 0 V.

### 7 Application Information

This section begins with application information for the analog section, followed by power distribution, crystal oscillator, and codec clock generation programming examples.

### 7.1 Analog Information

The A/D input block is covered first, followed by the D/A, and the microphone voltage regulator.

### A/D in the Preamplifier Mode

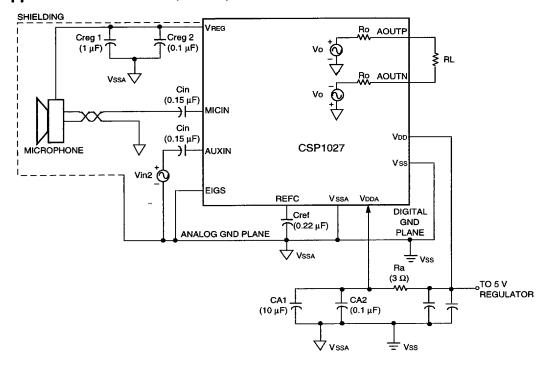

Figure 24 shows a typical telephone handset application. The codec is shown with the preamp mode (EIGS = Vss) selected and connected to a microphone. The analog-to-digital conversion path begins with an on-chip preamplifier front end having two single-ended inputs. The preamp inputs are MICIN and AUXIN. Selection of MICIN or AUXIN is made via the INSEL field in the cioc0 register (Table 7) and can be dynamically changed, as desired. The electrical specifications for both inputs are the same.

An off-chip ac-coupling capacitor, Cin, is required before each input. However, if either input is unused, it may be left unconnected (floating). The input resistance (Rin) to either MICIN or AUXIN is approximately 40 k $\Omega$ . The recommended value of Cin is 0.15  $\mu$ F. This creates a high-pass filter pole at approximately 26 Hz. A larger capacitor value may be used if desired, in order to allow lower frequencies to pass to the A/D converter, but smaller capacitor values are not recommended.

### A/D in the External Input Gain Select Mode

The external input gain select (EIGS = VDD) is used when the input range is set by the user (see Section 4.3 for setting input gain). The A/D input circuitry of Figure 24 is modified as shown in Figure 5. When EIGS = VDD, the following notes apply.

- The recommended range of values for the feedback resistor and capacitor are the following: 10 kΩ ≤ Rtb ≤ 45 kΩ and 150 pF ≤ Ctb ≤ 680 pF.

- 2. The  $\frac{R_{\text{th}}}{R_{\text{in}}}$  external resistor ratio accuracy directly impacts the absolute accuracy of the A/D path. A 1% ratio error adds 86 mdB of absolute gain error.

- 3. The A/D input sampling switches have an effective bandwidth on the order of 15 MHz. The amplifier unity gain frequency is on the order of 3 MHz. Highfrequency noise in the 1 MHz to 50 MHz range that couples to the AUXIN pin will be somewhat attenuated by the amplifier output impedance, but a significant portion will be sampled by the A/D and aliased down to the baseband. Special care in circuit board

layout is required to keep noise sources from coupling into the AUXIN or MICIN pins so that the noise and distortion performance shown in Table 16 can be achieved.

The codec is not as sensitive to wideband noise when the preamplifier is used (EIGS = Vss) because the A/D inputs are driven from an on-chip low-pass filter.

4. The external gain mode input circuitry of Figure 5 is a lossy integrator. The frequency response of Table 18 assumes that the Rfb · Cfb corner frequency is 25 kHz so the 3 kHz droop is less than 65 mdB. Similarly, the Cin · Rin corner frequency is set to 7 Hz. These RC combinations create a bandpass antialiasing filter with corner frequencies given by

$$fLO = \frac{1}{2\pi \times Rin \times Cin}$$

$fHI = \frac{1}{2\pi \times Rib \times Cib}$

When selecting component values, verify that the A/D frequency response will still meet the application requirements.

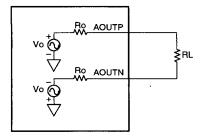

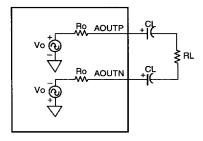

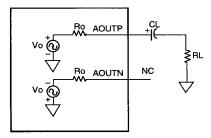

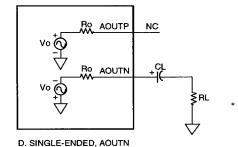

### D/A Analog Output

The CSP1027 D/A has two analog outputs, AOUTP and AOUTN, capable of operating as two single-ended drivers, or a single fully differential driver. The output impedance of each is no more than 6  $\Omega$  (12  $\Omega$  if configured as fully differential) over the dc to 4 kHz frequency range.

The maximum open-circuit output levels are 2.1 V peak (4.2 V peak-to-peak) if fully differential, and one-half these levels if single-ended. These levels correspond to a full-scale 16-bit two's complement PCM input into the D/A converter, with the output gain setting (OGSEL) at 0 dB. For any given PCM input, the output levels will be reduced by a voltage division of the D/A output and the load impedance:

$$V$$

OUT =  $V$ O  $\times \frac{RL}{RO + RL}$

The driver linearity is only guaranteed for the single-ended output load resistance (RL) of at least 1000  $\Omega$  and the differential output load resistance (RL) of at least 2000  $\Omega$ .