1063

262,144-WORD by 4-BIT HIGH SPEED CMOS SYNCHRONOUS STATIC RAM

## **PRELIMINARY**

### Description

The CXK77410J is a high speed CMOS synchronous static RAM with separate I/O pins, organized as 262,144-words by 4-bits. This synchronous SRAM integrates input registers. high speed SRAM and output registers onto a single monolithic IC. All input signals are latched at the positive edge of an external clock (CLK). The RAM data from the previous cycle is presented at the positive edge of the subsequent clock cycle. Write operation is initiated by the positive edge of CLK and is internally selftimed. This feature eliminates complex off-chip write pulse generation and provides increased flexibility for incoming signals. Pass-thru capability is also provided. 100MHz operation is obtained from a single 5V power supply.

**Structure** Silicon gate CMOS IC

#### **Features**

- High speed, low power consumption.

- Single +5V power supply :  $5V \pm 5\%$

- Inputs and outputs are TTL compatible.

- Write-through capability.

- Separate data input and output.

- 10 ns cycle time (100 MHz).

- All inputs and outputs are registered on a single clock edge.

- Self-timed write cycle.

- Arbitrary consecutive read/write cycles with no write recovery cycles.

- Available in a 36 pin 50 mil lead pitch 400 mil SOJ package.

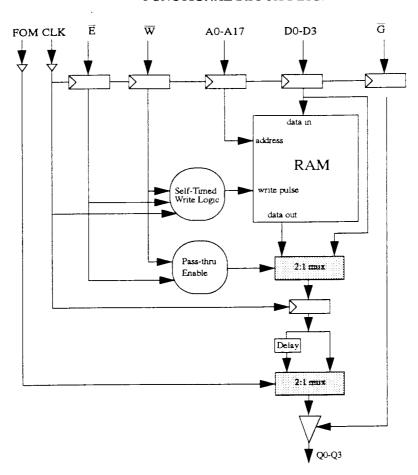

#### FUNCTIONAL BLOCK DIAGRAM

#### FUNTIONAL DESCRIPTION

There are three possible user capabilities with this chip: Read operation, Write operation, and Pass-through operation.

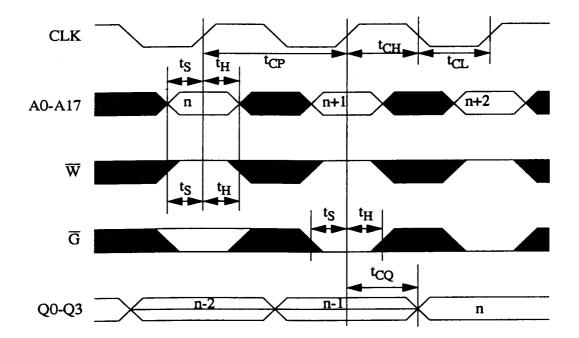

The read operation requires  $\overline{W}$  = "HIGH" at the rising edge of CLK. The memory location specified by the address inputs is latched and read internally. At the subsequent rising edge of CLK, if  $\overline{G}$  = "LOW", the contents of the previous cycle are captured by the Data-out registers. The state of the output terminals reflect the contents of the Data-out registers.

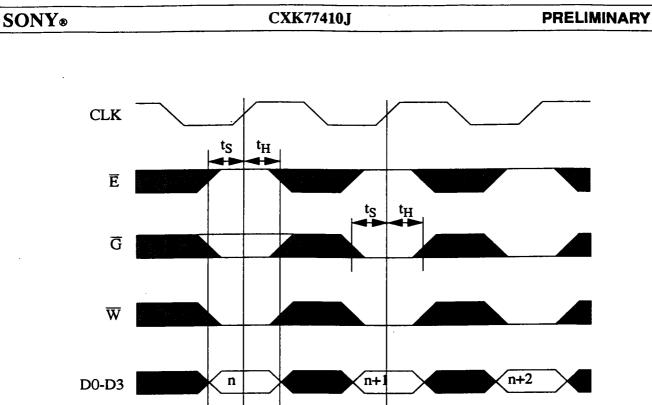

The write and pass-through operations require  $\overline{W}$  and  $\overline{E}$  to be "LOW" at the rising edge of CLK. The contents of the Data-in registers are written into the memory locations specified by the address inputs. The write operation is entirely self-timed. The contents of the Data-in registers are also captured by the Data-out registers when  $\overline{G}$  goes "LOW" at the subsequent rising edge of CLK and are also passed to the output terminals for write through operation.

The pass through operation requires  $\overline{W}$  = "LOW" and  $\overline{E}$  = "HIGH" at the rising edge of CLK. The data is not written to memory, however the contents of Data-in registers are captured by the Data-out registers when  $\overline{G}$  = "LOW" at the subsequent rising edge of CLK. It is also presented to the output terminals.

Wait states are not required between read and write cycles.

The FOM pin is used to control output timing, allowing the user to skew CLK to output and hold times.

2 Revision 2.0

# Pin Configuration (Top View)

## Pin Description

| Symbol                  | Description                 |

|-------------------------|-----------------------------|

| A0 to A17               | Address input               |

| D0 to D3                | Data input                  |

| Q0 to Q3                | Data output                 |

| CLK                     | Clock                       |

| Ē                       | Internal write enable input |

| $\overline{\mathbf{W}}$ | Write enable input          |

| G                       | Output enable input         |

| FOM                     | Fast Output Mode option pin |

| Vcc                     | +5V power supply            |

| GND                     | Ground                      |

## **Pin Description**

## CLK (Clock, positive edge triggered)

All timing is controlled by the rising or positive edge of CLK. All synchronous input and output signals are registered on the rising edge of CLK with set-up and hold times referenced to that edge. Since only one edge of CLK is referenced, the duty cycle of CLK is not critical.

## A0 to A17 (Address)

The Address inputs are decoded on-chip to select one of 262,144 words. The state of the Address inputs is registered into the Address register on the positive edge of CLK. The Address inputs must be valid during every positive edge with all set-up and hold times referenced to that edge.

## D0 to D3 (Data input)

The state of the Data inputs is registered into the Data-in registers on the positive edge of CLK for the write operation. The data inputs must be valid during every positive edge with all set-up and hold times referenced to that edge.

## Q0 to Q3 ( Data input )

Output terminals are three-state. The state is defined by the Control block( refer the truth table ). The Data outputs are triggered by the edge of CLK and the contents of the Output-Registers are presented.

3

# $\overline{\mathbf{W}}$ ( Synchronous Write Enable, active low )

$\overline{W}$  is used to indicate whether a read or write operation is to be performed.  $\overline{W}$  is "LOW" to perform a write operation.  $\overline{W}$  is registered on every positive edge of CLK with set-up and hold times referenced to that edge. The internal timing required to store data into the memory array is self-timed.

## **E** (Synchronous Internal Write Enable, active low)

$\overline{E}$  is used to control the write operation along with  $\overline{W}$  (refer the truth table ). The state of  $\overline{E}$  is registered on every positive edge of CLK with set-up and hold times referenced to that edge.

# $\overline{\mathbf{G}}$ ( Synchronous Output Enable, active low )

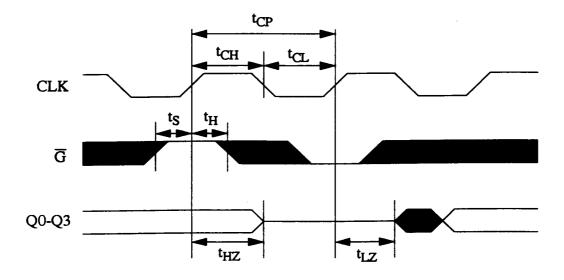

$\overline{G}$  is used to control output registers and enable the output terminals. When  $\overline{G}$  is "LOW", the data from the previous cycle will be captured into the output registers and also presented to the output terminals. When  $\overline{G}$  is "HIGH", output registers will contain tri-stated information and the output terminals are tri-stated. The state of G is registered on every positive edge of CLK with set-up and hold times referenced to that edge.

## FOM (Fast Output Mode, active high)

FOM is an option pin, which controls clock to output timing. When FOM is tied high, a built-in delay circuit is bypassed, allowing a faster output access time. Conversely, when FOM is tied low, the output data is routed through the delay circuit, giving better output hold time. FOM, if left unconnected (floating), defaults to an active high. This is accomplished by an internal pull-up device strobed by CLK and a unidirectional latch.

Revision 2.0

# **Absolute Maximum Ratings**

| (Ta | = | 25° | C, | <b>GND</b> | = | <b>0</b> V | 7   |

|-----|---|-----|----|------------|---|------------|-----|

| ν-я |   |     | ~, |            |   | • ,        | - 4 |

| Item _                       | Symbol              | Rating                        | Unit     |

|------------------------------|---------------------|-------------------------------|----------|

| Supply voltage               | V <sub>CC</sub>     | -0.5 to +7.0                  | V        |

| Input voltage                | V <sub>IN</sub>     | $-0.5^*$ to $V_{CC} + 0.5$    | V        |

| Output voltage               | v <sub>o</sub>      | -0.5 to V <sub>CC</sub> + 0.5 | V        |

| Allowable power dissipation  | P <sub>D</sub>      | 1.0                           | W        |

| Operating temperature        | T <sub>opr</sub>    | 0 to 70                       | °C       |

| Storage temperature          | T <sub>stg</sub>    | -55 to 150                    | °C       |

| Soldering temperature • time | T <sub>solder</sub> | 260 • 10                      | °C • sec |

## **Truth Table**

| $\overline{\overline{E}}(t_n)$ | $\overline{W}(t_n)$ | $\overline{G}(t_{n+1})$ | Mode                | $D_{0-3}(t_n)$ | $Q_{0-3}(t_{n+1})$ | V <sub>CC</sub><br>Current |

|--------------------------------|---------------------|-------------------------|---------------------|----------------|--------------------|----------------------------|

| _                              |                     | L                       | Write and Pass-thru | Valid          | $D_{0-3}(t_n)$     | I <sub>CC</sub>            |

| L                              | L                   | Н                       | Write               | Valid          | Hi - Z             | I <sub>CC</sub>            |

| _                              |                     | L                       | Read                | Don't care     | $D_{OUT}(t_n)$     | I <sub>CC</sub>            |

| L                              | H                   | Н                       | Aborted read        | Don't care     | Hi - Z             | I <sub>CC</sub>            |

|                                | -                   | L                       | Pass-thru           | Valid          | $D_{0-3}(t_n)$     | I <sub>CC</sub>            |

| Н                              | L                   | Н                       | Aborted pass-thru   | Valid          | Hi - Z             | I <sub>CC</sub>            |

|                                |                     | L                       | Read                | Don't care     | $D_{OUT}(t_n)$     | I <sub>CC</sub>            |

| Н                              | Н                   | Н                       | Aborted read        | Don't care     | Hi - Z             | I <sub>CC</sub>            |

## DC Recommended Operating Conditions

$$(T_a = 25^{\circ}C, GND = 0V)$$

| Item               | Symbol          | Min   | Тур | Max                   | Unit |

|--------------------|-----------------|-------|-----|-----------------------|------|

| Supply voltage     | V <sub>CC</sub> | 4.75  | 5.0 | 5.25                  | V    |

| Input high voltage | V <sub>IH</sub> | 2.2   |     | V <sub>CC</sub> + 0.3 | V    |

| Input low voltage  | V <sub>IL</sub> | -0.3* |     | 0.8                   | V    |

<sup>\*</sup> $V_{IL}$  = -3.0 V Min. for pulse width less than 20 ns.

Revision 2.0

# **Electrical Characteristics**

## •DC and operating characteristics

$(Vcc = 5V \pm 5\%, GND = 0V, T_a = 0 \text{ to } 70^{\circ}\text{C})$

| Item                                | Symbol             | Test conditions                                                  | Min   | Typ* | Max | Unit |

|-------------------------------------|--------------------|------------------------------------------------------------------|-------|------|-----|------|

| Input leakage current except pin 18 | I <sub>LI</sub>    | Vin = GND to<br>Vcc                                              | -1    |      | 1   | uA   |

| Input leakage current<br>Pin 18     | I <sub>LI,18</sub> | Vin = GND to<br>Vcc, V <sub>CLK</sub> =V <sub>IH</sub>           | -2000 |      | 1   | uA   |

|                                     |                    | Vin = GND to<br>Vcc, V <sub>CLK</sub> =V <sub>IL</sub>           | -1    |      | 1   | uA   |

| Output leakage current              | $I_{LO}$           | $\frac{V_O}{G} = GND \text{ to Vcc}$<br>$\frac{V_O}{G} = V_{IH}$ | -1    |      | 1   | uA   |

| Operating power supply current      | I <sub>CC</sub>    | Cycle = 66.7 MHz<br>Vin = V <sub>IH</sub> or V <sub>IL</sub>     |       |      | 170 | mA   |

|                                     |                    | Cycle = 80 MHz                                                   |       |      | 190 | mA   |

|                                     |                    | Cycle = 100 MHz                                                  |       |      | 200 | mA   |

| Output high voltage                 | V <sub>OH</sub>    | $I_{OH} = -4.0 \text{ mA}$                                       | 2.4   |      |     | V    |

| Output low voltage                  | $V_{OL}$           | $I_{OL} = 8.0 \text{ mA}$                                        |       |      | 0.4 | V    |

<sup>\*</sup>  $Vcc = 5V, T_a = 25^{\circ}C$

## •I/O capacitance

$(T_a = 25^{\circ}C, f = 1 \text{ MHz})$

| Item                         | Symbol           | Test conditions       | Min | Max | Unit |

|------------------------------|------------------|-----------------------|-----|-----|------|

| Input capacitance            | C <sub>IN</sub>  | $V_{IN} = 0V$         |     | 5   | pF   |

| Output capacitance           | C <sub>OUT</sub> | V <sub>OUT</sub> = 0V |     | 8   | pF   |

| Clock input capaci-<br>tance | C <sub>CLK</sub> | $V_{CLK} = 0V$        |     | 8   | pF   |

Note: These parameters are sampled and are not 100% tested.

#### •AC ELECTRICAL CHARACTERISTICS

|                     | Item                           |                    | -10<br>(100 MHZ) |     | -12<br>(80 MHZ) |     | -15<br>(66.7 MHz) |     | Unit |

|---------------------|--------------------------------|--------------------|------------------|-----|-----------------|-----|-------------------|-----|------|

|                     |                                |                    | Min              | Max | Min             | Max | Min               | Max |      |

|                     | Clock period                   | t <sub>CP</sub>    | 10               | ∞   | 12.5            | ∞   | 15                | ∞   | ns   |

|                     | Clock pulse high               | t <sub>CH</sub>    | 3                |     | 4               |     | 5                 |     | ns   |

|                     | Clock pulse low                | t <sub>CL</sub>    | 3                |     | 4               |     | 5                 |     | ns   |

|                     | Setup time                     | ts                 | 2                |     | 2               |     | 2.5               |     | ns   |

|                     | Hold time                      | t <sub>H</sub>     | 1                |     | 1               |     | 1.5               |     | ns   |

| FOM                 | Clock to output                | t <sub>CQ</sub>    | 2                | 6.5 | 2               | 7   | 2                 | 8.5 | ns   |

| =                   | Clock to output high impedance | t <sub>HZ</sub> *2 | 2                | 5   | 2               | 6   | 2                 | 7.5 | ns   |

| $\Lambda^{I\Gamma}$ | Clock to output low impedance  | t <sub>LZ</sub> *2 | 2                |     | 2               |     | 2                 |     | ns   |

| FOM                 | Clock to output                | tcQ                | 1                | 5.5 | 1               | 6   | 1                 | 7.5 | ns   |

| =                   | Clock to output high impedance | t <sub>HZ</sub> *2 | 1                | 4.5 | 1               | 5   | 1                 | 6.5 | ns   |

| VIH                 | Clock to output low impedance  | t <sub>LZ</sub> *2 | 1                |     | 1               |     | 1                 |     | ns   |

- 1. All parameters are specified over the range 0-70°C.

- 2. These parameters are sampled and are not 100% tested.

#### **AC** characteristics

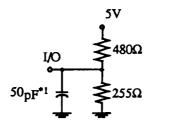

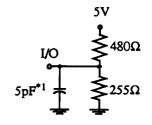

AC test conditions

$(Vcc = 5V \pm 5\%, Ta = 0 \text{ to } 70^{\circ}C)$

| Item                   | Conditions           |

|------------------------|----------------------|

| Input pulse high level | $V_{IH} = 3.0V$      |

| Input pulse low level  | $V_{OL} = 0V$        |

| Input rise time        | $t_r = 3 \text{ ns}$ |

| Input fall time        | $t_f = 3 \text{ ns}$ |

| Input reference level  | 1.5V                 |

| Output reference level | 0.8 V/2.0 V          |

| Output load conditions | Fig.1                |

#### FIG.1

Output Load (1)

Output Load\*2 (2)

- 1. Including scope and jig capacitance.

- 2. For  $t_{LZ}$ ,  $t_{HZ}$ .

TIMING WAVEFORM OF READ CYCLE (E Don't care)

**SONY**®

Q0-Q3

TIMING WAVEFORM OF WRITE CYCLE (\* pass-thru option)

n\*

TIMING WAVEFORM OF PASS THROUGH CYCLE

Q0-Q3

TIMING WAVEFORM OF TRI-STATE OUTPUTS

n