# **Image Sensor Signal Processing LSI**

# **Preliminary**

### **Overview**

The LC99062-W50 is an external digital signal processor (DSP) that includes digital NTSC and PAL encoders on chip, and that supports color video. The LC99062-W50 is implemented in a single chip using standard cells.

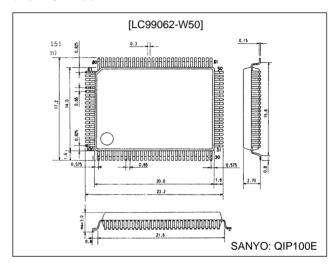

# **Package Dimensions**

unit: mm

#### 3151-QFP100E

# **Specifications**

# Absolute Maximum Ratings at $Ta = 25^{\circ}C$ , $V_{SS} = 0~V$

| Parameter                   | Symbol                          | Conditions                        | Ratings                       | Unit |

|-----------------------------|---------------------------------|-----------------------------------|-------------------------------|------|

| Maximum supply voltage      | V <sub>DD</sub> max             |                                   | -0.3 to +7.0                  | V    |

| I/O voltages                | V <sub>I</sub> , V <sub>O</sub> |                                   | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Allowable power dissipation | Pd max                          |                                   | 850                           | mW   |

| Operating temperature       | Topr                            |                                   | -15 to +65                    | °C   |

| Storage temperature         | Tstg                            |                                   | -55 to +125                   | °C   |

| Caldavina conditions        |                                 | Hand soldering: 3 seconds         | 350                           | °C   |

| Soldering conditions        |                                 | Reflow: 10 seconds                | 235                           | °C   |

| I/O currents                | I <sub>I</sub> , I <sub>O</sub> | Per individual I/O reference cell | ±20                           | mA   |

### Allowable Operating Ranges at Ta = -15 to $+65^{\circ}C$ , $V_{SS} = 0$ V

| Parameter           | Symbol          | Conditions | min  | typ | max      | Unit |

|---------------------|-----------------|------------|------|-----|----------|------|

| Supply voltage      | $V_{DD}$        |            | 4.75 | 5.0 | 5.25     | V    |

| Input voltage range | V <sub>IN</sub> |            | 0    |     | $V_{DD}$ | V    |

# Electrical Characteristics at Ta = -15 to +65°C, $V_{DD}$ = 4.75 to 5.25 V, $V_{SS}$ = 0 V

| Parameter                 | Symbol          | Conditions                                                                       | min                   | typ | max                 | Unit |

|---------------------------|-----------------|----------------------------------------------------------------------------------|-----------------------|-----|---------------------|------|

| Input high level voltage  | V <sub>IH</sub> | CMOS compatible: applicable pin (1)                                              | 0.7 V <sub>DD</sub>   |     |                     | V    |

| Input low level voltage   | V <sub>IL</sub> | CMOS compatible: applicable pin (1)                                              |                       |     | 0.3 V <sub>DD</sub> | V    |

| Input high level voltage  | V <sub>IH</sub> | TTL compatible Schmitt: applicable pin (2)                                       | 2.5                   |     |                     | V    |

| Input low level voltage   | V <sub>IL</sub> | TTL compatible Schmitt: applicable pin (2)                                       |                       |     | 0.6                 | V    |

| Output high level voltage | V <sub>OH</sub> | I <sub>OH</sub> = -4 mA: applicable pin (3)                                      | V <sub>DD</sub> – 2.1 |     |                     | V    |

| Output low level voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 4 mA: applicable pin (3)                                       |                       |     | 0.4                 | V    |

| Output high level voltage | V <sub>OH</sub> | I <sub>OH</sub> = -4 mA: applicable pin (4)                                      | V <sub>DD</sub> – 2.1 |     |                     | V    |

| Output low level voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 4 mA: applicable pin (4)                                       |                       |     | 0.4                 | V    |

| Input leakage current     | IL              | V <sub>I</sub> = V <sub>SS</sub> , V <sub>DD</sub> : applicable pins (1) and (2) | -10                   |     | +10                 | μA   |

| Output leakage current    | loz             | In high-impedance output mode: applicable pin (3)                                | -10                   |     | +10                 | μA   |

Note: The applicable pin sets are defined as follows:

Input

- (1) .....All input pins except REGSEL1 and REGSEL2

- (2) .....REGSEL1, REGSEL2

Output

- (3) .....OT1 to OT24

- (4) .....CRKEYH

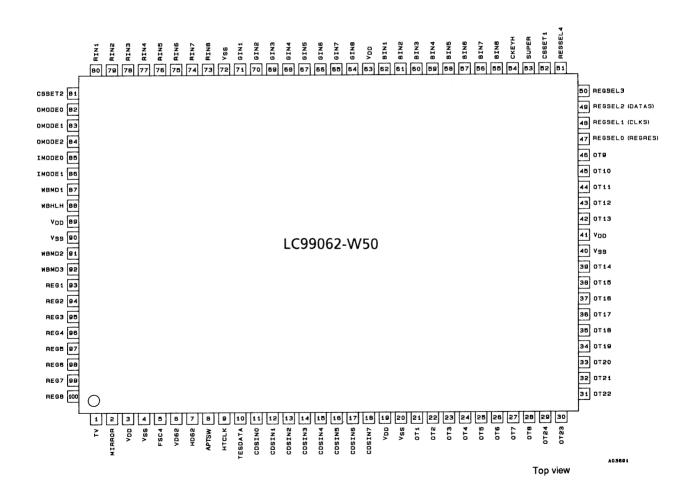

### **Pin Assignment**

### **Pin Functions**

$\text{I/O} \rightarrow \text{I: Input pin, O: Output pin, B: Bidirectional pin, P: Power supply pin, NC: Unconnected pin}$

|          |                         |     | I/O → I: Input pin, O: Output pin, B: Bidirectional pin, P: Power supply pin, NC: Unconnected pin                                                                           |

|----------|-------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No.  | Symbol                  | I/O | Function                                                                                                                                                                    |

| 1        | TV                      |     | 0: NTSC, 1: PAL                                                                                                                                                             |

| 2        | MIRROR                  |     | 0: Normal, 1: Mirror                                                                                                                                                        |

| 3        | V <sub>DD</sub>         | P   |                                                                                                                                                                             |

| 4        | V <sub>SS</sub>         | P . |                                                                                                                                                                             |

| 5        | FSC4                    | I   | CLK (from LC99052) NTSC: 14.31818 MHz, PAL: 14.1875 MHz                                                                                                                     |

| 6        | VD62                    | I   | VD (from LC99052)                                                                                                                                                           |

| 7        | HD62                    | I   | HD (from LC99052)                                                                                                                                                           |

| 8        | APTSW                   | I   | Aperture switch 0: Off, 1: On                                                                                                                                               |

| 9        | HTCLK                   | I   | CLK = 8/3fsc (from LC99052)                                                                                                                                                 |

| 10       | TESDATA                 | I   | 0: Run                                                                                                                                                                      |

| 11       | CDSIN0                  | I   | 8-bit data input (from LC99052) (LSB)                                                                                                                                       |

| 12       | CDSIN1                  | I   | 8-bit data input (from LC99052)                                                                                                                                             |

| 13       | CDSIN2                  | I   | 8-bit data input (from LC99052)                                                                                                                                             |

| 14       | CDSIN3                  | I   | 8-bit data input (from LC99052)                                                                                                                                             |

| 15       | CDSIN4                  | I   | 8-bit data input (from LC99052)                                                                                                                                             |

| 16       | CDSIN5                  | I   | 8-bit data input (from LC99052)                                                                                                                                             |

| 17       | CDSIN6                  | I   | 8-bit data input (from LC99052)                                                                                                                                             |

| 18       | CDSIN7                  | I   | 8-bit data input (from LC99052) (MSB)                                                                                                                                       |

| 19       | V <sub>DD</sub>         | P   |                                                                                                                                                                             |

| 20       | V <sub>SS</sub>         | P   | 0                                                                                                                                                                           |

| 21       | OT1                     | 0   | Output channel1 = CH1 (LSB)                                                                                                                                                 |

| 22       | OT2                     | 0   | Output channel1 = CH1                                                                                                                                                       |

| 23       | OT3                     | 0   | Output channel1 = CH1                                                                                                                                                       |

| 24       | OT4                     | 0   | Output channel1 = CH1                                                                                                                                                       |

| 25       | OT5                     | 0   | Output channel1 = CH1                                                                                                                                                       |

| 26       | OT6                     | 0   | Output channel1 = CH1                                                                                                                                                       |

| 27       | OT7                     | 0   | Output channel1 = CH1                                                                                                                                                       |

| 28       | OT8                     | 0   | Output channel1 = CH1 (MSB)                                                                                                                                                 |

| 29       | OT24                    | 0   | Output channel3 = CH3 (MSB)                                                                                                                                                 |

| 30       | OT23                    | 0   | Output channel3 = CH3                                                                                                                                                       |

| 31       | OT22                    | 0   | Output channel3 = CH3                                                                                                                                                       |

| 32       | OT21                    | 0   | Output channel3 = CH3                                                                                                                                                       |

| 34       | OT20                    | 0   | Output channel3 = CH3                                                                                                                                                       |

|          | OT19                    | 0   | Output channel3 = CH3                                                                                                                                                       |

| 35       | OT18                    | 0   | Output channel3 = CH3                                                                                                                                                       |

| 36       | OT17                    | -   | Output channel3 = CH3 (LSB)                                                                                                                                                 |

| 37       | OT16                    | 0   | Output channel2 = CH2 (MSB)                                                                                                                                                 |

| 38       | OT15                    | 0   | Output channel2 = CH2 Output channel2 = CH2                                                                                                                                 |

| 39       | OT14                    | P   | Output Grannetz = Onz                                                                                                                                                       |

| 40       | V <sub>SS</sub>         | P   |                                                                                                                                                                             |

| 41       | V <sub>DD</sub><br>OT13 | 0   | Output channel2 – CH2                                                                                                                                                       |

| 43       | OT12                    | 0   | Output channel2 = CH2 Output channel2 = CH2                                                                                                                                 |

| 43       | OT12                    | 0   | Output channel2 = CH2 Output channel2 = CH2                                                                                                                                 |

| 44       | OT10                    | 0   | Output channel2 = CH2 Output channel2 = CH2                                                                                                                                 |

| 46       | OT10                    | 0   | Output channel2 = CH2 (LSB)                                                                                                                                                 |

| 47       | REGSEL0                 | 1   | (REGRES) 0: Register initialization 1: Register modification allowed                                                                                                        |

| 48       | REGSEL1                 |     | (CLKS) Serial clock input                                                                                                                                                   |

| 49       | REGSEL2                 | 1   | (DATAS) Serial data input                                                                                                                                                   |

| 50<br>51 | REGSEL3                 | I   | PEGSEL [4:0] = (41410) or (41**4): OT (24 to 1) \ High impodence                                                                                                            |

| 31       | REGSEL4                 | '   | REGSEL [4:0] = (11110) or (11**1); OT (24 to 1) → High impedance  Must be set according to the phase of the LC99052 A/D converter clock. (This is true for pin 81 as well.) |

| 52       | CSSET1                  | 1   | Recommended value for current conditions: 1                                                                                                                                 |

| 53       | SUPER                   | I   | Superimpose pulse input 1; superimpose 0; camera through                                                                                                                    |

| 54       | CKEYH                   | 0   | Chrominance key out H; chrominance key The delay time is changed by the settings of pins 85 and 86. See pins 85 and 86.                                                     |

Continued on next page.

Continued from preceding page.

$I/O \rightarrow I$ : Input pin, O: Output pin, B: Bidirectional pin, P: Power supply pin, NC: Unconnected pin

| Pin No.        | Symbol                     | I/O         | I/O → I: Input pin, O: Output pin, B: Bidirectional pin, P: Power supply pin, NC: Unconnected pin  Function                                                                                                                                                                                                                                                                                                                                            |

|----------------|----------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 55             | BIN8                       | 1/0         | 8-bit data input (MSB)                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 56             | BIN7                       | <u>'</u>    | 8-bit data input                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 57             | BIN6                       | <u>'</u>    | 8-bit data input                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 58             | BIN5                       | i           | 8-bit data input                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 59             | BIN4                       | i           | 8-bit data input                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 60             | BIN3                       | i           | 8-bit data input or register setting pin                                                                                                                                                                                                                                                                                                                                                                                                               |

| 61             | BIN2                       | <u> </u>    | 8-bit data input or register setting pin                                                                                                                                                                                                                                                                                                                                                                                                               |

| 62             | BIN1                       | i           | 8-bit data input (LSB) or register setting pin                                                                                                                                                                                                                                                                                                                                                                                                         |

| 63             | V <sub>DD</sub>            | P           | o sh data mpat (200) of regions conting pin                                                                                                                                                                                                                                                                                                                                                                                                            |

| 64             | GIN8                       | i           | 8-bit data input (MSB)                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 65             | GIN7                       | i           | 8-bit data input                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 66             | GIN6                       | i           | 8-bit data input                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 67             | GIN5                       | i           | 8-bit data input                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 68             | GIN4                       | i           | 8-bit data input                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 69             | GIN3                       | i           | 8-bit data input or register setting pin                                                                                                                                                                                                                                                                                                                                                                                                               |

| 70             | GIN2                       | i           | 8-bit data input or register setting pin                                                                                                                                                                                                                                                                                                                                                                                                               |

| 71             | GIN1                       | i           | 8-bit data input (LSB) or register setting pin                                                                                                                                                                                                                                                                                                                                                                                                         |

| 72             | V <sub>SS</sub>            | P           | ,, . ,                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 73             | RIN8                       | 1           | 8-bit data input (MSB)                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 74             | RIN7                       | i           | 8-bit data input                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 75             | RIN6                       | 1           | 8-bit data input                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 76             | RIN5                       | 1           | 8-bit data input                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 77             | RIN4                       | 1           | 8-bit data input                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 78             | RIN3                       | 1           | 8-bit data input or register setting pin                                                                                                                                                                                                                                                                                                                                                                                                               |

| 79             | RIN2                       | 1           | 8-bit data input or register setting pin                                                                                                                                                                                                                                                                                                                                                                                                               |

| 80             | RIN1                       | 1           | 8-bit data input (LSB) or register setting pin                                                                                                                                                                                                                                                                                                                                                                                                         |

| 81             | CSSET2                     | 1           | Must be set according to the phase of the LC99052 A/D converter clock. (This is true for pin 52 as well.)  Recommended value for current conditions: 1                                                                                                                                                                                                                                                                                                 |

| 82<br>83<br>84 | OMODE0<br>OMODE1<br>OMODE2 | 1<br>1<br>1 | Output mode select 000: Video (OT1 to OT8), ICON (OT24) 001: R (OT1 to OT8), G (OT9 to OT16), B (OT17 to OT24) 010: R-Y (OT1 to OT8), Y (OT9 to OT16), B-Y (OT17 to OT24) 011: Y (OT1 to OT8), C (OT9 to OT16), CSYNC (OT24) 100: Y (OT1 to OT8), U/V (OT9 to OT16), U/CONT (OT24) 101: VBS (OT1 to OT8), Y (OT12 to OT9), R-Y (OT16, OT15), B-Y (OT14, OT13) 110: VBS (OT1 to OT8), Y + CSYNC (OT9 to OT16), C (OT17 to OT24) 111: Y/U/V (OT1 to OT8) |

| 85<br>86       | IMODE0<br>IMODE1           | I<br>I      | Input mode select  00: R (RIN4 to RIN8), G (GIN4 to GIN8), B (BIN4 to BIN8)*1  01: R (RIN4 to RIN8), G (GIN4 to GIN8), B (BIN4 to BIN8)*2  10: R (RIN1 to RIN8), G (GIN1 to GIN8), B (BIN1 to BIN8)*1  11: Y (RIN1 to RIN8), V (GIN1 to GIN8), U (BIN1 to BIN8)*1  Note: 1. The output is synchronized with the chrominance key out.  2. The chrominance key out is output 16 clock cycles in advance of this output.                                  |

| 87             | WBMD1                      | I           | White balance mode SW1                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 88             | WBHLH                      | I           | Auto white balance hold; 1: Hold, 0: Auto Note: * Hold this pin low when the internal register is used.                                                                                                                                                                                                                                                                                                                                                |

| 89             | $V_{DD}$                   | Р           |                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 90             | V <sub>SS</sub>            | Р           |                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 91             | WBMD2                      | I           | White balance mode SW2                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 92             | WBMD3                      | I           | White balance mode SW3                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 93             | REG1                       | - 1         | Register setting pin                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 94             | REG2                       | - 1         | Register setting pin                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 95             | REG3                       | I           | Register setting pin                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 96             | REG4                       | I           | Register setting pin                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 97             | REG5                       | I           | Register setting pin                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 98             | REG6                       | 1           | Register setting pin                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 99             | REG7                       | ı           | Register setting pin                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 100            | REG8                       | I           | Register setting pin                                                                                                                                                                                                                                                                                                                                                                                                                                   |

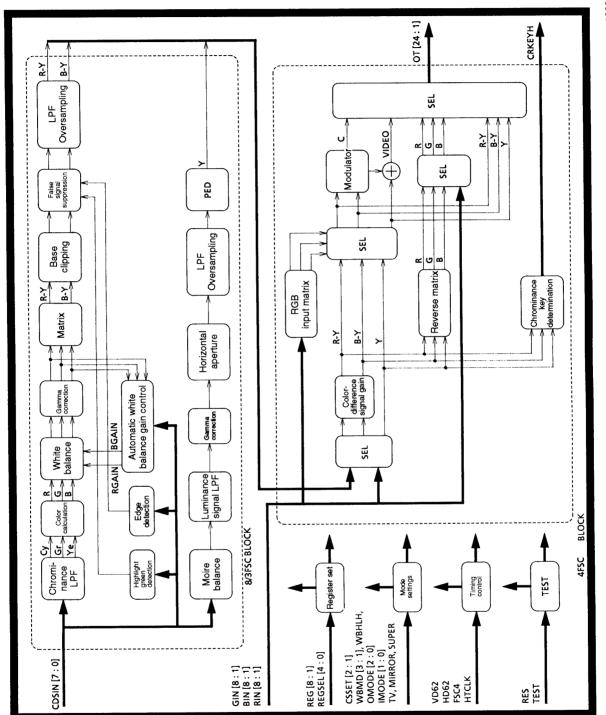

### **Block Diagram**

No. 5073-5/7

# Main Functions Provided by the LC99062-W50

DSP Functions for Sanyo Color CCD devices (LC9997G/LC9998G)

- 1. Luminance signal system processing

- Includes a luminance matrix to reduce reflected noise (moire).

- Includes a knee-processing circuit using complementary color filters.

- Includes a seven-tap low-pass filter.

- Gamma correction circuit using a five-line approximation technique. The intersection points for each line can be adjusted.

- Provides second-order horizontal outline correction. The gain and coring are adjustable.

- Forms a 1.5× sampling frequency conversion circuit.

#### 2. Chrominance system signal processing

- Includes a digital clamping circuit that prevents black balance slippage.

- Forms the RGB signal using an 11-tap low-pass filter and a color calculation matrix.

- · Automatic white balance circuit

- Includes all circuits and functions required for automatic white balance.

- Allows switching between automatic and manual modes.

- Allows holding from automatic mode.

- Supports fine-grained gain settings using 7-bit gain data and a technique that takes valid bits into account. The R gain can be set from  $\times 0.25$  to  $\times 4.0$ , and the B gain from  $\times 0.5$  to  $\times 8.0$ .

- Provides modes with seven patterns, including flesh correction.

- Reduces incorrect operation by applying a response with hysteresis according to the degree of the discrepancy.

- Gamma correction circuit using a three-line approximation technique

- Includes a linear matrix for color difference signals. Allows color tone adjustment.

- Includes a color noise suppression circuit that operates for low chrominance level signals. The suppression level is adjustable.

- Includes a suppression circuit for false color signals that occur at edges and in high-luminance areas.

- All of the above functions are formed with baseband signals.

- Includes a 1.5x sampling frequency conversion circuit.

#### NTSC/PAL Encoder

- NTSC and PAL encoding is possible with only HD, VD, and CLK inputs (NTSC = 14.31818 MHz, PAL = 14.1875 MHz). In PAL mode, internal operations are used to generate the Fsc signal, and normally there is no need for a Fsc signal generated by a PLL or other circuit.

- The CSYNC, CBLK, and BF signals are formed internally.

- Allows burst phase adjustment (hue adjustment). (NTSC only)

- Allows pedestal and burst level adjustment.

- Includes a seven-tap low-pass filter for the color difference signals relative to the external RGB inputs. The luminance system 3.58 MHz trap can be turned on or off.

#### Input and Output Modes

- 1. Input modes

- In addition to signal input from an LC99052-V64A, the LC99062-W50 also supports <R, G, B> and <Y, R-Y, B-Y> input modes.

- Two of the above input systems can be superimposed.

### 2. Output modes

- The LC99062-W50 supports eight output modes.

- Composite video, 8-bit RGB, <Y, R-Y, B-Y>, <Y, C>, <Y, U/V>, and <4-bit Y, 2-bit R-Y, B-Y>

- --- < Y + CSYNC, C > and < Y/U/V >

#### Other Functions

- Simplified chrominance key function

- An arbitrary color can be detected by setting R-Y and B-Y data.

- A 2-pin serial interface is used for setting registers.

- Stand-alone operation is possible. The adjustments and settings are supported from external pins even in stand-alone mode.

- Support for mirror (left-right reversal) processing.

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of June, 1995. Specifications and information herein are subject to change without notice.