# AMDA

# Am79C901A

### HomePHY™ Single-Chip 1/10 Mbps Home Networking PHY

### DISTINCTIVE CHARACTERISTICS

- Fully integrated 1 Mbps HomePNA Physical Layer (PHY) as defined by Home Phoneline Networking Alliance (HomePNA) specification 1.1

- Optimized for home networking applications over existing telephone wire

- Media Independent Interface (MII)-compatible for connecting external Media Access Controller (MAC)

- In-band control features:

- Adjustable power and speed levels 32 bits of reserved in-band messaging piggybacked on Ethernet packet

- Register programmable features:

**Power control**

Speed control

Performance registers

Optional control of Squelch algorithm

Major frame timing parameters programmable: ISBI, AID ISBI, pulse width, inter-symbol time

- any1Home™ link detection:

- Indicates to the MAC that a valid home networking node has been detected

- Detects a network failure and allows the upper layer protocol to take corrective action

- Fully integrated 10 Mbps Ethernet transceiver

- Comprehensive Auto-Negotiation implementation

- IEEE 802.3u-compliant MII

- Full-duplex operation supported on the MII port with independent Transmit (TX) and Receive (RX) channels

- Optimized for 10BASE-T applications

- Compliant with HomePNA specification 1.1

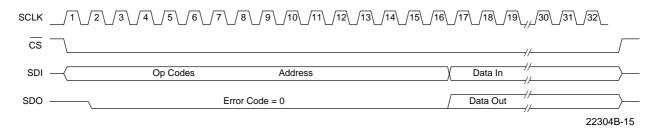

- General Purpose Serial Interface (GPSI)/Serial Peripheral Interface (SPI)

- Extensive programmable internal/external loopback capabilities

- Extensive LED status support

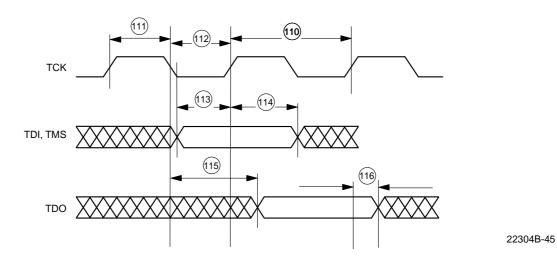

- IEEE 1149.1-compliant JTAG Boundary Scan test access port interface

- Very low power consumption

- +3.3 V power supply along with 5 V tolerant I/Os enable broad system compatibility

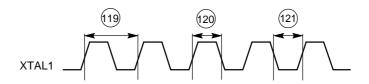

- XTAL1 supports 3.3 V I/O only

- XTAL2 supports 1.0 V I/O only

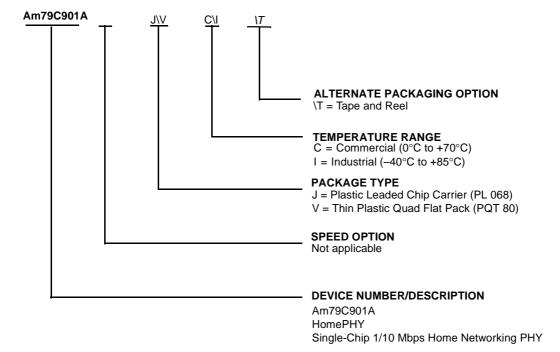

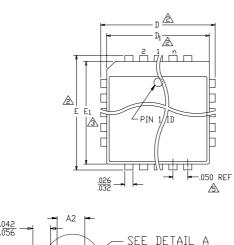

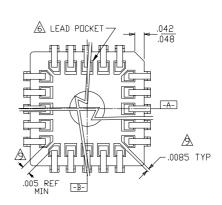

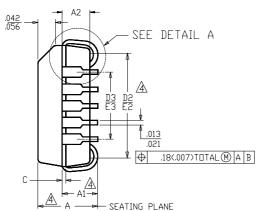

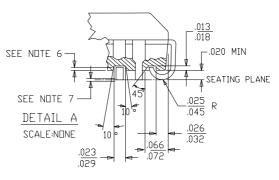

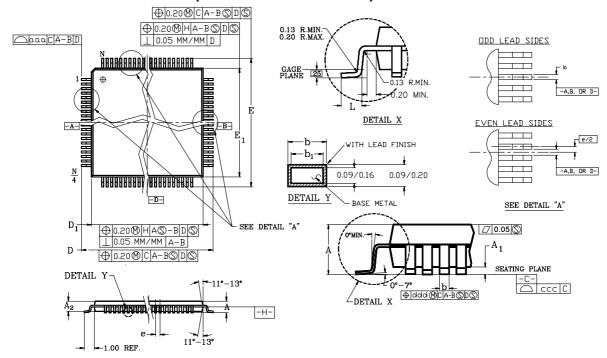

- Available in 68-pin PLCC and 80-pin TQFP packages

- Industrial Temperature Support (-40°C to +85°C)

### **GENERAL DESCRIPTION**

The Am79C901A HomePHY is a single-chip device that contains both a physical layer (PHY) for 1 Mbps data networking over existing residential telephone wiring based on the specification published by HomePNA and a physical layer for supporting the IEEE 802.3 standard for 10BASE-T. The HomePHY is targeted at embedded applications and has both GPSI and MII-compatible interfaces.

The integrated HomePNA transceiver is a physical layer device that enables data networking at speeds up to 1 Mbps over existing residential phone wiring regardless of topology and without disrupting telephone (POTS) service.

The integrated Ethernet transceiver is a physical layer device supporting the IEEE 802.3 standard for 10BASE-T. It provides all of the PHY layer functions

required to support 10 Mbps data transfer speeds. A compliant IEEE 1149.1 JTAG test interface for board level testing is provided. The Am79C901A PHY also provides on-chip LED drivers for collision, link integrity, speed, activity, and power output.

The Am79C901A PHY is fabricated in an advanced low power 3.3 V CMOS process to provide low operating current for power sensitive applications.

The Am79C901A PHY is available in the commercial temperature range (0°C to +70°C) in 68-pin PLCC and 80-pin TQFP packages. The Am79C901A also supports the industrial temperature range (-40°C to +85°C) in the 80-pin TQFP package. The industrial temperature range is well suited to environments with enclosures with restricted air flow or outdoor equipment.

Publication# 22304 Rev: C Amendment/0 Issue Date: July 2000

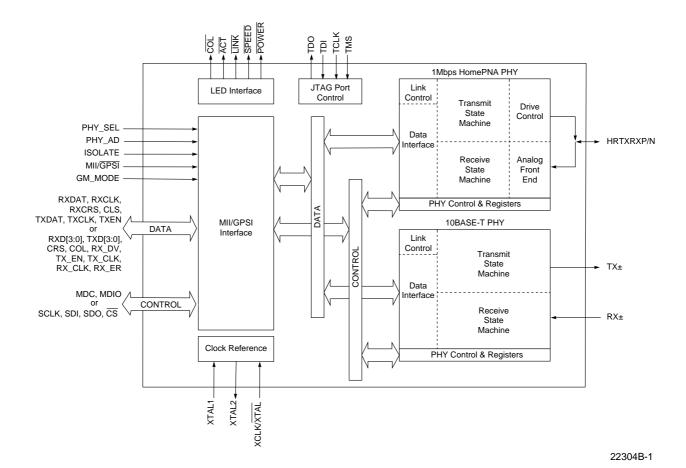

### **BLOCK DIAGRAM**

### **TABLE OF CONTENTS**

| DISTINCTIVE CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GENERAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| BLOCK DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| TABLE OF CONTENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| LIST OF FIGURESLIST OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

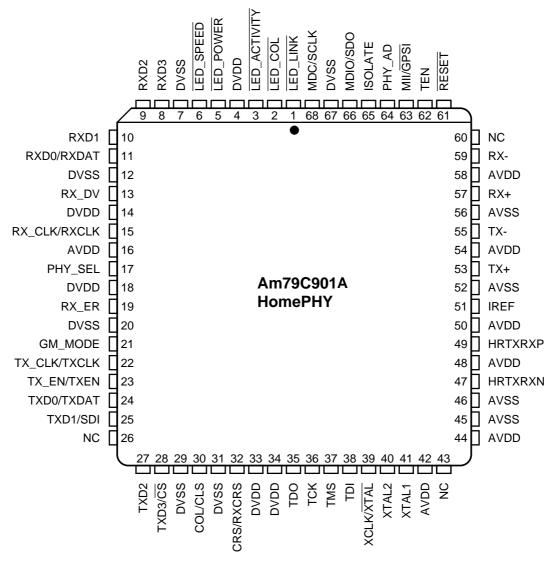

| CONNECTION DIAGRAM (PL 068)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

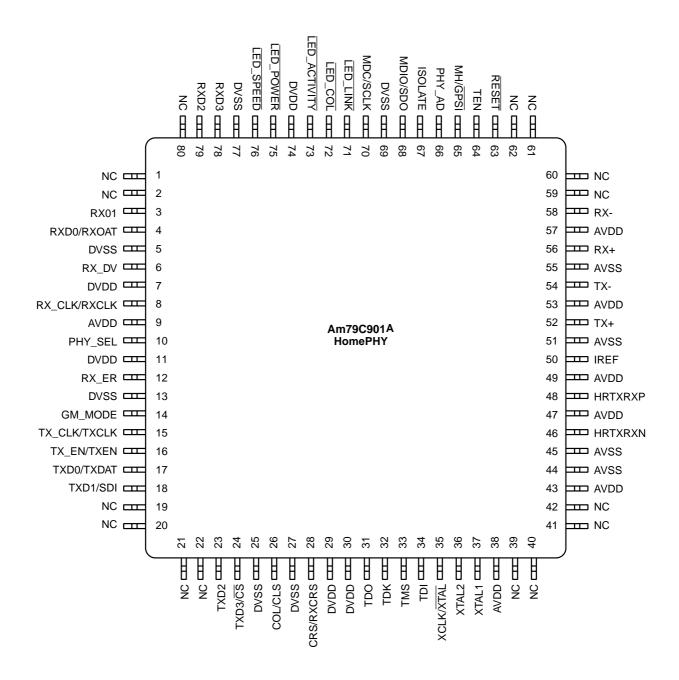

| CONNECTION DIAGRAM (PQT 80)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| PIN DESIGNATIONS (PL 068)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Listed By Pin Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PIN DESIGNATIONS (PQT 80)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Listed By Pin Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PIN DESIGNATIONS (PL 068)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Listed By Group                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| PIN DESIGNATIONS (PQT 80) 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Listed By Group                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| PIN DESIGNATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Listed By Driver Type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ORDERING INFORMATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Standard Products                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| PIN DESCRIPTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Configuration Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Board Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| GPSI Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SPI Interface (Slave Mode Only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| MII Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| IEEE 1149.1 (JTAG) Test Access Port Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Ethernet Network Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| HomePNA PHY Network Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Clock Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Scan Test Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Scan Test Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Scan Test Interface 2  BASIC FUNCTIONS 2  Network Interfaces 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Scan Test Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Scan Test Interface 2  BASIC FUNCTIONS 2  Network Interfaces 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Scan Test Interface         2           BASIC FUNCTIONS         2           Network Interfaces         2           PHY Data Interfaces         2           Reset         2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Scan Test Interface       2         BASIC FUNCTIONS       2         Network Interfaces       2         PHY Data Interfaces       2         Reset       2         H_RESET       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Scan Test Interface       2         BASIC FUNCTIONS       2         Network Interfaces       2         PHY Data Interfaces       2         Reset       2         H_RESET       2         S_RESET       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Scan Test Interface       2         BASIC FUNCTIONS       2         Network Interfaces       2         PHY Data Interfaces       2         Reset       2         H_RESET       2         S_RESET       2         DETAILED FUNCTIONS       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Scan Test Interface       2         BASIC FUNCTIONS       2         Network Interfaces       2         PHY Data Interfaces       2         Reset       2         H_RESET       2         S_RESET       2         DETAILED FUNCTIONS       2         GPSI Interface       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

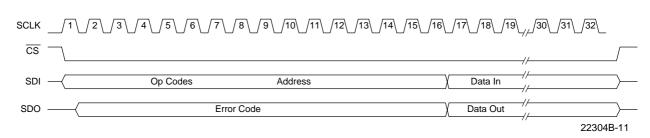

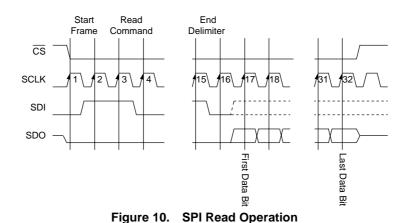

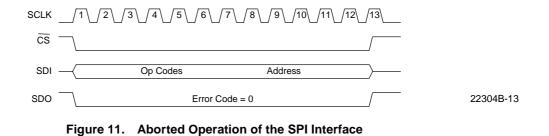

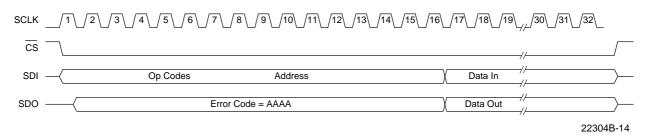

| Scan Test Interface       2         BASIC FUNCTIONS       2         Network Interfaces       2         PHY Data Interfaces       2         Reset       2         H_RESET       2         S_RESET       2         DETAILED FUNCTIONS       2         GPSI Interface       2         Serial Peripheral Interface (SPI-Slave) Mode       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Scan Test Interface       2         BASIC FUNCTIONS       2         Network Interfaces       2         PHY Data Interfaces       2         Reset       2         H_RESET       2         S_RESET       2         DETAILED FUNCTIONS       2         GPSI Interface       2         Serial Peripheral Interface (SPI-Slave) Mode       2         MII-Compatible Interface for HomePNA PHY       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Scan Test Interface       2         BASIC FUNCTIONS       2         Network Interfaces       2         PHY Data Interfaces       2         Reset       2         H_RESET       2         S_RESET       2         DETAILED FUNCTIONS       2         GPSI Interface       2         Serial Peripheral Interface (SPI-Slave) Mode       2         MII-Compatible Interface for HomePNA PHY       2         MII-Compliant Interface for 10BASE-T PHY       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

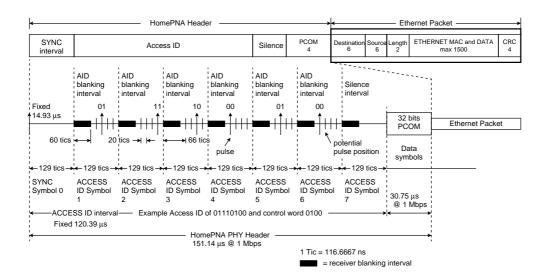

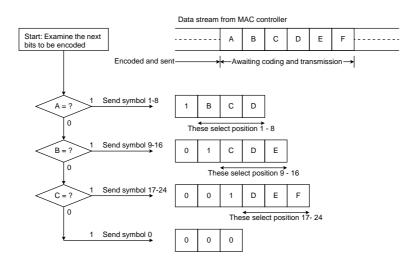

| Scan Test Interface       2         BASIC FUNCTIONS       2         Network Interfaces       2         PHY Data Interfaces       2         Reset       2         H_RESET       2         S_RESET       2         DETAILED FUNCTIONS       2         GPSI Interface       2         Serial Peripheral Interface (SPI-Slave) Mode       2         MII-Compatible Interface for HomePNA PHY       2         MII-Compliant Interface for 10BASE-T PHY       2         1 Mbps HomePNA PHY       3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Scan Test Interface       2         BASIC FUNCTIONS       2         Network Interfaces       2         PHY Data Interfaces       2         Reset       2         H_RESET       2         S_RESET       2         DETAILED FUNCTIONS       2         GPSI Interface       2         Serial Peripheral Interface (SPI-Slave) Mode       2         MII-Compatible Interface for HomePNA PHY       2         MII-Compliant Interface for 10BASE-T PHY       2         1 Mbps HomePNA PHY       3         HomePNA PHY Medium Interface       3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

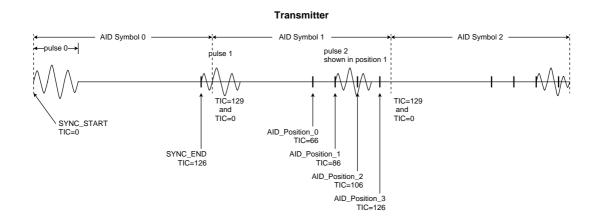

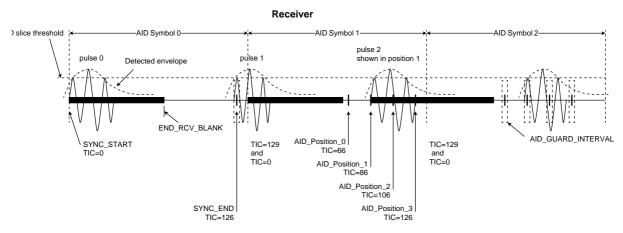

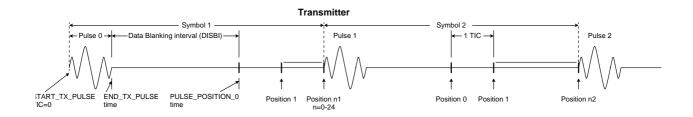

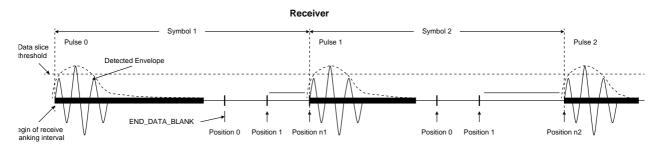

| Scan Test Interface       2         BASIC FUNCTIONS       2         Network Interfaces       2         PHY Data Interfaces       2         Reset       2         H_RESET       2         S_RESET       2         DETAILED FUNCTIONS       2         GPSI Interface       2         Serial Peripheral Interface (SPI-Slave) Mode       2         MII-Compatible Interface for HomePNA PHY       2         MII-Compliant Interface for 10BASE-T PHY       2         1 Mbps HomePNA PHY       3         HomePNA PHY Medium Interface       3         HomePNA PHY Symbol Waveform       3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Scan Test Interface       2         BASIC FUNCTIONS       2         Network Interfaces       2         PHY Data Interfaces       2         Reset       2         H_RESET       2         S_RESET       2         DETAILED FUNCTIONS       2         GPSI Interface       2         Serial Peripheral Interface (SPI-Slave) Mode       2         MII-Compatible Interface for HomePNA PHY       2         MII-Compliant Interface for 10BASE-T PHY       2         1 Mbps HomePNA PHY       3         HomePNA PHY Medium Interface       3         HomePNA PHY Symbol Waveform       3         Time Interval Unit       3                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Scan Test Interface       2         BASIC FUNCTIONS       2         Network Interfaces       2         PHY Data Interfaces       2         Reset       2         H_RESET       2         S_RESET       2         DETAILED FUNCTIONS       2         GPSI Interface       2         Serial Peripheral Interface (SPI-Slave) Mode       2         MII-Compatible Interface for HomePNA PHY       2         MII-Compliant Interface for 10BASE-T PHY       2         1 Mbps HomePNA PHY       3         HomePNA PHY Medium Interface       3         HomePNA PHY Symbol Waveform       3         Time Interval Unit       3         Collisions       3                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Scan Test Interface       2         BASIC FUNCTIONS       2         Network Interfaces       2         PHY Data Interfaces       2         Reset       2         H_RESET       2         S_RESET       2         DETAILED FUNCTIONS       2         GPSI Interface       2         Serial Peripheral Interface (SPI-Slave) Mode       2         MII-Compatible Interface for HomePNA PHY       2         MII-Compliant Interface for 10BASE-T PHY       2         1 Mbps HomePNA PHY       3         HomePNA PHY Medium Interface       3         HomePNA PHY Symbol Waveform       3         Time Interval Unit       3         Collisions       3         JAM Signal       3                                                                                                                                                                                                                                                                                                                                                                                                           |

| Scan Test Interface       2         BASIC FUNCTIONS       2         Network Interfaces       2         PHY Data Interfaces       2         Reset       2         H_RESET       2         S_RESET       2         DETAILED FUNCTIONS       2         GPSI Interface       2         Serial Peripheral Interface (SPI-Slave) Mode       2         MII-Compatible Interface for HomePNA PHY       2         MIII-Compliant Interface for 10BASE-T PHY       2         1 Mbps HomePNA PHY       3         HomePNA PHY Medium Interface       3         HomePNA PHY Symbol Waveform       3         Time Interval Unit       3         Collisions       3         JAM Signal       3         Access ID Values       3                                                                                                                                                                                                                                                                                                                                                                         |

| Scan Test Interface       2         BASIC FUNCTIONS       2         Network Interfaces       2         PHY Data Interfaces       2         Reset       2         H_RESET       2         S_RESET       2         DETAILED FUNCTIONS       2         GPSI Interface       2         Serial Peripheral Interface (SPI-Slave) Mode       2         MII-Compatible Interface for HomePNA PHY       2         MII-Compliant Interface for 10BASE-T PHY       2         1 Mbps HomePNA PHY       2         1 Mbps HomePNA PHY Medium Interface       3         HomePNA PHY Symbol Waveform       3         Time Interval Unit       3         Collisions       3         JAM Signal       3         Access ID Values       3         Silence Interval (AID symbol 7)       3                                                                                                                                                                                                                                                                                                                   |

| Scan Test Interface       2         BASIC FUNCTIONS       2         Network Interfaces       2         PHY Data Interfaces       2         Reset       2         H_RESET       2         S_RESET       2         DETAILED FUNCTIONS       2         GPSI Interface       2         Serial Peripheral Interface (SPI-Slave) Mode       2         MII-Compatible Interface for HomePNA PHY       2         MIII-Compliant Interface for 10BASE-T PHY       2         1 Mbps HomePNA PHY       2         HomePNA PHY Medium Interface       3         HomePNA PHY Symbol Waveform       3         Time Interval Unit       3         Collisions       3         JAM Signal       3         Access ID Values       3         Silence Interval (AID symbol 7)       3         Data Symbols       3                                                                                                                                                                                                                                                                                            |

| Scan Test Interface       2         BASIC FUNCTIONS       2         Network Interfaces       2         PHY Data Interfaces       2         PHY Data Interfaces       2         Reset       2         H_RESET       2         S_RESET       2         DETAILED FUNCTIONS       2         GPSI Interface       2         Serial Peripheral Interface (SPI-Slave) Mode       2         MII-Compatible Interface for HomePNA PHY       2         MII-Compliant Interface for 10BASE-T PHY       2         1 Mbps HomePNA PHY       3         HomePNA PHY Medium Interface       3         HomePNA PHY Symbol Waveform       3         Time Interval Unit       3         Collisions       3         JAM Signal       3         Access ID Values       3         Silence Interval (AID symbol 7)       3         Data Symbols       3         Mode Interface       3                                                                                                                                                                                                                          |

| Scan Test Interface       2         BASIC FUNCTIONS       2         Network Interfaces       2         PHY Data Interfaces       2         Reset       2         H_RESET       2         S_RESET       2         DETAILED FUNCTIONS       2         GPSI Interface       2         Serial Peripheral Interface (SPI-Slave) Mode       2         MII-Compatible Interface for HomePNA PHY       2         MIII-Compliant Interface for 10BASE-T PHY       2         1 Mbps HomePNA PHY       2         HomePNA PHY Medium Interface       3         HomePNA PHY Symbol Waveform       3         Time Interval Unit       3         Collisions       3         JAM Signal       3         Access ID Values       3         Silence Interval (AID symbol 7)       3         Data Symbols       3                                                                                                                                                                                                                                                                                            |

| Scan Test Interface       2         BASIC FUNCTIONS       2         Network Interfaces       2         PHY Data Interfaces       2         PHY Data Interfaces       2         Reset       2         H_RESET       2         S_RESET       2         DETAILED FUNCTIONS       2         GPSI Interface       2         Serial Peripheral Interface (SPI-Slave) Mode       2         MII-Compatible Interface for HomePNA PHY       2         MII-Compliant Interface for 10BASE-T PHY       2         1 Mbps HomePNA PHY       3         HomePNA PHY Medium Interface       3         HomePNA PHY Symbol Waveform       3         Time Interval Unit       3         Collisions       3         JAM Signal       3         Access ID Values       3         Silence Interval (AID symbol 7)       3         Data Symbols       3         Mode Interface       3                                                                                                                                                                                                                          |

| Scan Test Interface       2         BASIC FUNCTIONS       2         Network Interfaces       2         PHY Data Interfaces       2         Reset       2         H_RESET       2         S_RESET       2         DETAILED FUNCTIONS       2         GPSI Interface       2         Serial Peripheral Interface (SPI-Slave) Mode       2         MII-Compatible Interface for HomePNA PHY       2         MII-Compliant Interface for 10BASE-T PHY       2         1 Mbps HomePNA PHY Medium Interface       3         HomePNA PHY Medium Interface       3         HomePNA PHY Symbol Waveform       3         Time Interval Unit       3         Collisions       3         JAM Signal       3         Access ID Values       3         Silence Interval (AID symbol 7)       3         Data Symbols       3         Mode Interface       3         1 Mbps HomePNA PHY Loopback       3                                                                                                                                                                                                 |

| Scan Test Interface       2         BASIC FUNCTIONS       2         Network Interfaces       2         PHY Data Interfaces       2         Reset       2         H_RESET       2         S_RESET       2         DETAILED FUNCTIONS       2         GPSI Interface       2         Serial Peripheral Interface (SPI-Slave) Mode       2         MII-Compatible Interface for HomePNA PHY       2         MII-Compliant Interface for 10BASE-T PHY       2         1 Mbps HomePNA PHY       3         HomePNA PHY Medium Interface       3         HomePNA PHY Symbol Waveform       3         Time Interval Unit       3         Collisions       3         JAM Signal       3         Access ID Values       3         Silence Interval (AID symbol 7)       3         Data Symbols       3         Mode Interface       3         1 Mbps HomePNA PHY Loopback       3         any1Home Link Detection       3                                                                                                                                                                          |

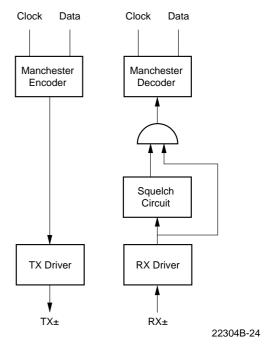

| Scan Test Interface       2         BASIC FUNCTIONS       2         Network Interfaces       2         PHY Data Interfaces       2         Reset       2         H_RESET       2         S_RESET       2         DETAILED FUNCTIONS       2         GPSI Interface       2         Serial Peripheral Interface (SPI-Slave) Mode       2         MII-Compatible Interface for HomePNA PHY       2         MII-Compliant Interface for 10BASE-T PHY       2         1 Mbps HomePNA PHY       3         HomePNA PHY Medium Interface       3         HomePNA PHY Symbol Waveform       3         Time Interval Unit       3         Collisions       3         JAM Signal       3         Access ID Values       3         Silence Interval (AID symbol 7)       3         Data Symbols       3         Mode Interface       3         1 Mbps HomePNA PHY Loopback       3         any1Home Link Detection       3         10BASE-T PHY       3                                                                                                                                             |

| Scan Test Interface       2         BASIC FUNCTIONS.       2         Network Interfaces       2         PHY Data Interfaces       2         Reset       2         H_RESET       2         S_RESET       2         DETAILED FUNCTIONS       2         GPSI Interface       2         Serial Peripheral Interface (SPI-Slave) Mode       2         MII-Compatible Interface for HomePNA PHY       2         MII-Compliant Interface for 10BASE-T PHY       2         1 Mbps HomePNA PHY Medium Interface       3         HomePNA PHY Symbol Waveform       3         Time Interval Unit       3         Collisions       3         JAM Signal       3         Access ID Values       3         Silence Interval (AID symbol 7)       3         Data Symbols       3         Mode Interface       3         1 Mbps HomePNA PHY Loopback       3         any1Home Link Detection       3         10BASE-T PHY       3         Twisted Pair Transmit Function       3         Twisted Pair Receive Function       3                                                                           |

| Scan Test Interface         2           BASIC FUNCTIONS         2           Network Interfaces         2           PHY Data Interfaces         2           Reset         2           H_RESET         2           S_RESET         2           DETAILED FUNCTIONS         2           GPSI Interface         2           Serial Peripheral Interface (SPI-Slave) Mode         2           MII-Compatible Interface for HomePNA PHY         2           MII-Compatible Interface for 10BASE-T PHY         2           1 Mbps HomePNA PHY         2           1 Mbps HomePNA PHY         3           HomePNA PHY Symbol Waveform         3           Time Interval Unit         3           Collisions         3           JAM Signal         3           Access ID Values         3           Silence Interval (AID symbol 7)         3           Data Symbols         3           Mode Interface         3           1 Mbps HomePNA PHY Loopback         3           any1Home Link Detection         3           10BASE-T PHY         3           Twisted Pair Transmit Function         3 |

### PRELIMINARY

| Reverse Polarity Detect                                                       | . 39 |

|-------------------------------------------------------------------------------|------|

| Auto-Negotiation                                                              | . 39 |

| Soft Reset Function                                                           |      |

| 10BASE-T Loopback                                                             |      |

|                                                                               |      |

| LED Support                                                                   |      |

| IEEE 1149.1 (JTAG) Test Access Port Interface                                 | . 40 |

| Boundary Scan Circuit                                                         | . 40 |

| TAP Finite State Machine                                                      |      |

| Supported Instructions.                                                       |      |

|                                                                               |      |

| Instruction Register and Decoding Logic                                       |      |

| Boundary Scan Register                                                        | . 41 |

| Other Data Registers                                                          | . 41 |

| Boundary Scan Cells                                                           |      |

|                                                                               |      |

| USER ACCESSIBLE REGISTERS                                                     |      |

| 1 Mbps HomePNA PHY Management Registers (HPRs)                                |      |

| HPR0: HomePNA PHY Control Register (Register 0)                               | . 44 |

| HPR1: HomePNA PHY Status Register (Register 1)                                |      |

| HPR2 and HPR3: HomePNA PHY ID Registers (Registers 2 and 3)                   |      |

|                                                                               |      |

| HPR4: HomePNA PHY Auto-Negotiation Advertisement Register (Register 4)        |      |

| HPR5: HomePNA PHY Auto-Negotiation Link Partner Ability Register (Register 5) |      |

| HPR6: HomePNA PHY Auto-Negotiation Expansion Register (Register 6)            | . 49 |

| HPR7: HomePNA PHY Auto-Negotiation Next Page Register (Register 7)            |      |

|                                                                               |      |

| Reserved Registers: HPR8 - HPR15                                              | . 49 |

| HPR16: HomePNA PHY Control Register (Register 16)                             |      |

| HPR17: HomePNA PHY Status/Control Register (Register 17)                      | . 51 |

| HPR18 and HPR19: HomePNA PHY TxCOMM Registers (Registers 18 and 19)           |      |

| HPR20 and HPR21: HomePNA PHY RxCOMM Registers (Registers 20 and 21)           |      |

|                                                                               |      |

| HPR22: HomePNA PHY AID Register (Register 22)                                 |      |

| HPR23: HomePNA PHY Noise Control Register (Register 23)                       |      |

| HPR24: HomePNA PHY Noise Control 2 Register (Register 24)                     | . 53 |

| HPR25: HomePNA PHY Noise Statistics Register (Register 25)                    |      |

| HPR26: HomePNA PHY Event Status Register (Register 26)                        |      |

|                                                                               |      |

| HPR27: HomePNA PHY AID Control Register (Register 27)                         |      |

| HPR28: HomePNA PHY ISBI Control Register (Register 28)                        | . 55 |

| HPR29: HomePNA PHY TX Control Register (Register 29)                          | . 55 |

| HPR30: HomePNA PHY Drive Level Control Register (Register 30)                 |      |

|                                                                               |      |

| HPR31: HomePNA PHY Analog Control Register (Register 31)                      |      |

| 10BASE-T PHY Management Registers (TBRs)                                      |      |

| TBR0: 10BASE-T PHY Control Register (Register 0)                              | . 57 |

| TBR1: 10BASE-T Status Register (Register 1)                                   |      |

| TBR2 and TBR3: 10BASE-T PHY Identifier Register (Registers 2 and 3)           |      |

|                                                                               |      |

| TBR4: 10BASE-T Auto-Negotiation Advertisement Register (Register 4)           |      |

| TBR5: 10BASE-T Auto-Negotiation Link Partner Ability Register (Register 5)    |      |

| TBR6: 10BASE-T Auto-Negotiation Expansion Register (Register 6)               | . 62 |

| TBR7: 10BASE-T Auto-Negotiation Next Page Register (Register 7)               | . 62 |

| Reserved Registers (Registers 8-15, 18, 20-23, and 25-31)                     |      |

|                                                                               |      |

| TBR16: 10BASE-T Status and Enable Register (Register 16)                      |      |

| TBR17: 10BASE-T PHY Control/Status Register (Register 17)                     |      |

| TBR19: 10BASE-T PHY Management Extension Register (Register 19)               | . 65 |

| TBR24: 10BASE-T Summary Status Register (Register 24)                         |      |

| ABSOLUTE MAXIMUM RATINGS.                                                     |      |

| OPERATING RANGES                                                              |      |

|                                                                               |      |

| DC CHARACTERISTICS                                                            | -    |

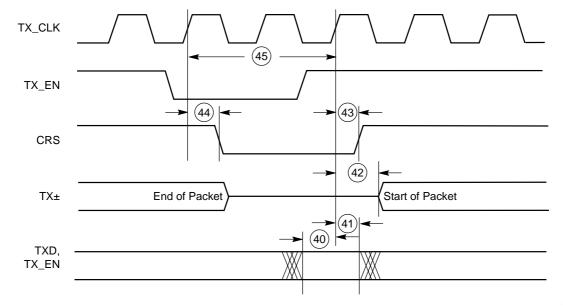

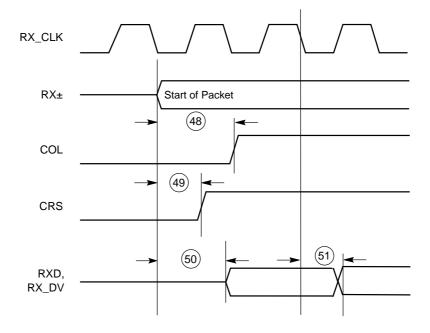

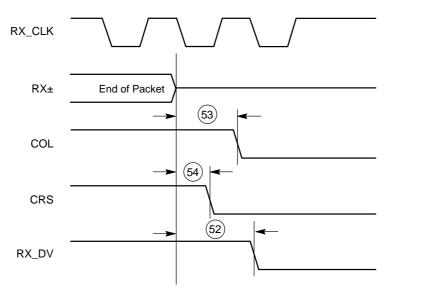

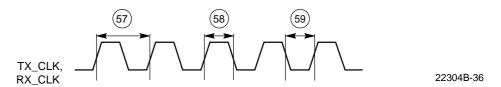

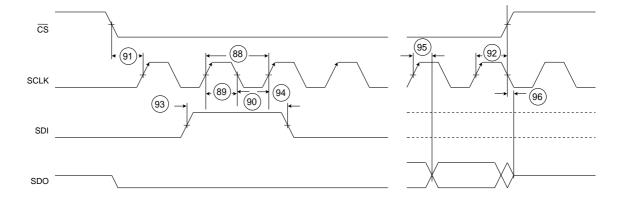

| SWITCHING WAVEFORMS                                                           | . 68 |

| Key to Switching Waveforms                                                    | . 68 |

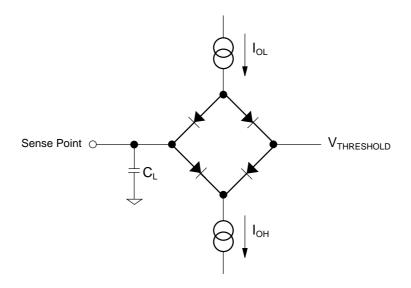

| SWITCHING TEST CIRCUITS                                                       |      |

| AC CHARACTERISTICS                                                            |      |

|                                                                               |      |

| GPSI                                                                          |      |

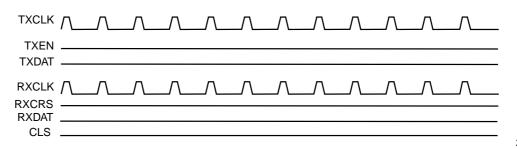

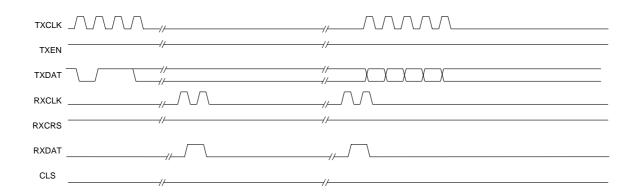

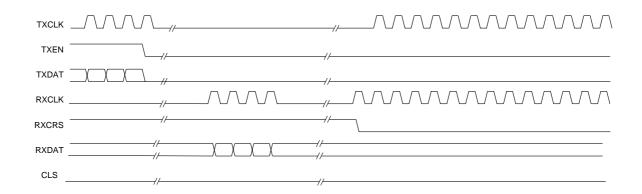

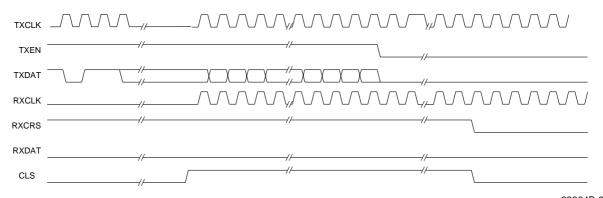

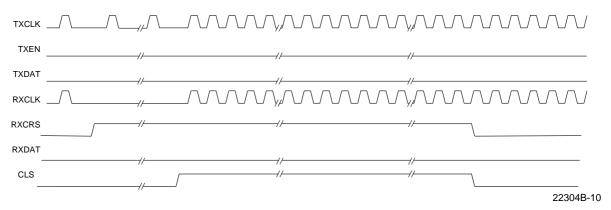

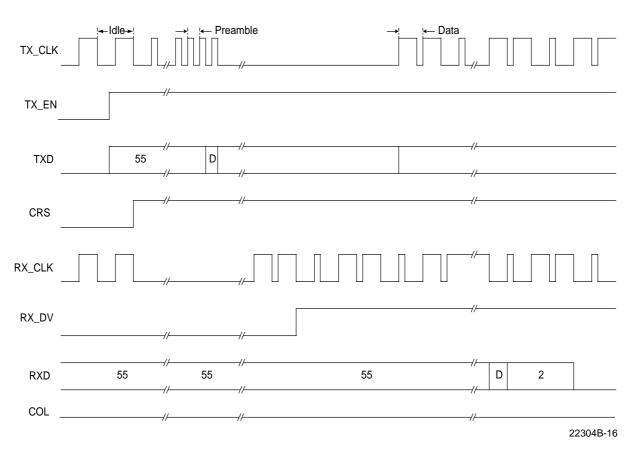

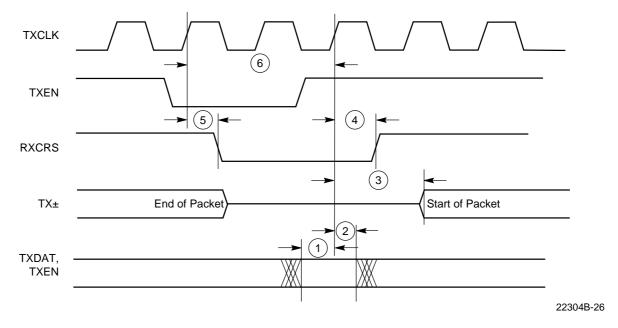

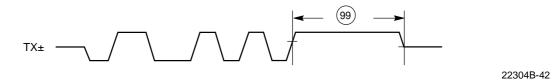

| 10BASE-T Transmit Timing (GPSI)                                               | . 69 |

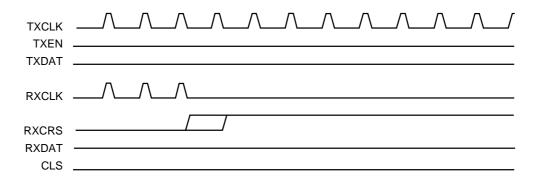

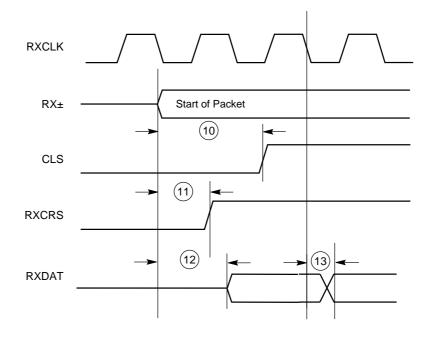

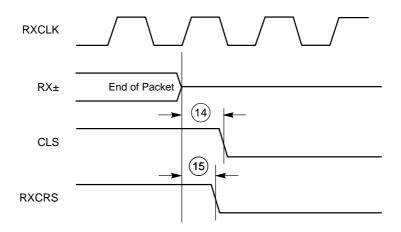

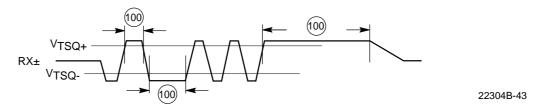

| 10BASE-T Receive Timing (GPSI)                                                | . 70 |

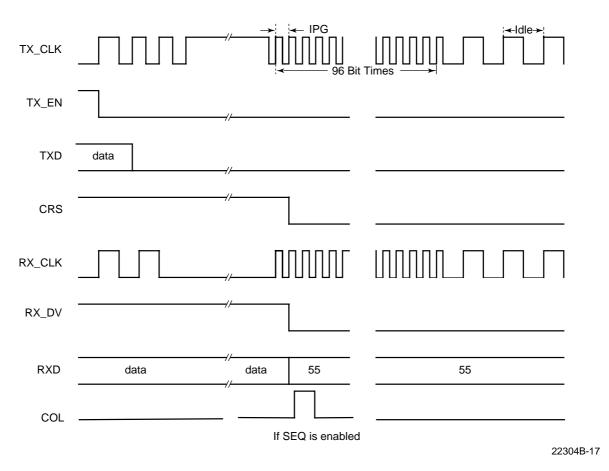

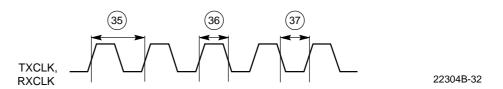

| 10BASE-T Transmit Clock Timing (GPSI)                                         |      |

| 10BASE-T Receive Clock Timing (GPSI)                                          |      |

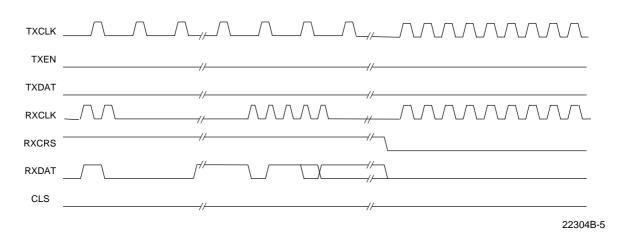

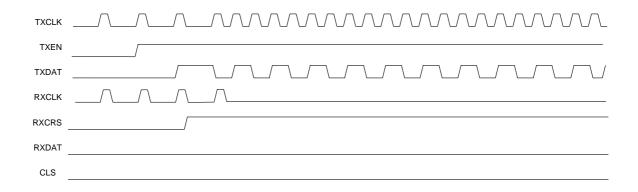

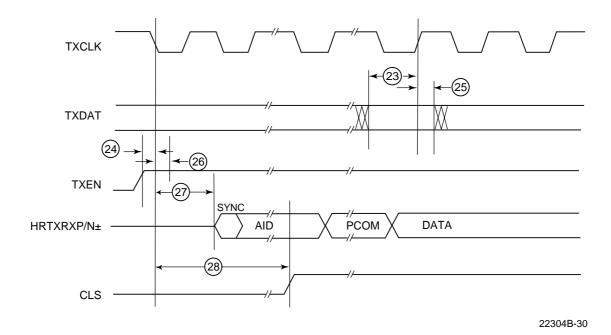

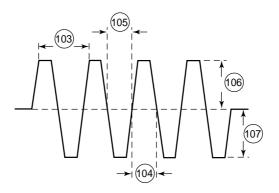

| 1 Mbps HomePNA Transmit Timing (GPSI)                                         |      |

| LIVIDUS HOMAPINA Transmit Limina (L-PS)                                       | . 72 |

### PRELIMINARY

| 1 Mbps HomePNA Receive Timing  | (GPSI) |    |

|--------------------------------|--------|----|

|                                |        |    |

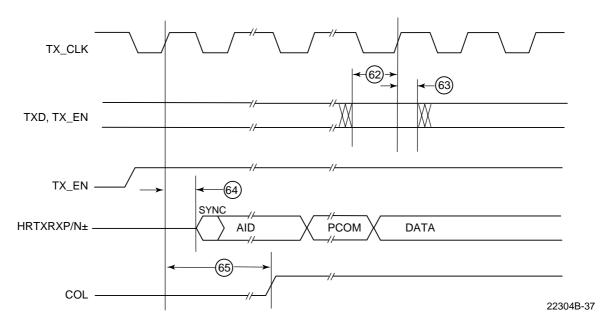

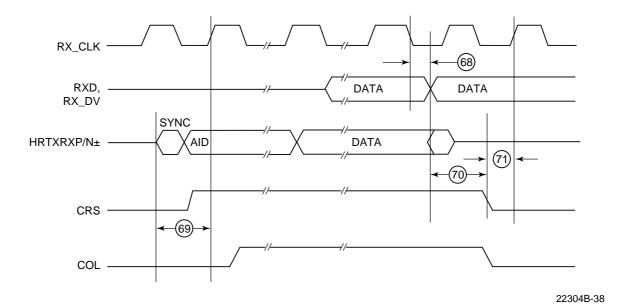

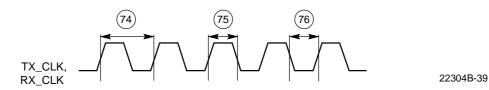

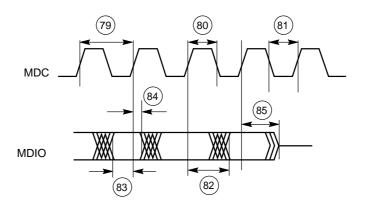

| MII                            |        |    |