# Hitachi Single-Chip Microcomputer H8/3644 Series, H8/3644R Series

H8/3644, H8/3644R

HD6473644, HD6433644, HD6473644R, HD6433644R

H8/3643, H8/3643R

HD6433643, HD6433643R

H8/3642, H8/3642R

HD6433642, HD6433642R

H8/3641, H8/3641R

HD6433641, HD6433641R

H8/3640, H8/3640R

HD6433640, HD6433640R

$H8/3644F-ZTAT^{TM}$

HD64F3644

$H8/3643F-ZTAT^{TM}$

HD64F3643

$H8/3642AF-ZTAT^{TM}$

HD64F3642A

Hardware Manual

**HITACHI**

ADE-602-087D Rev. 5.0 March 23, 1999 Hitachi, Ltd. MC-Setsu

### Cautions

- 1. Hitachi neither warrants nor grants licenses of any rights of Hitachi's or any third party's patent, copyright, trademark, or other intellectual property rights for information contained in this document. Hitachi bears no responsibility for problems that may arise with third party's rights, including intellectual property rights, in connection with use of the information contained in this document.

- 2. Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.

- 3. Hitachi makes every attempt to ensure that its products are of high quality and reliability. However, contact Hitachi's sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation, traffic, safety equipment or medical equipment for life support.

- 4. Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installation conditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.

- 5. This product is not designed to be radiation resistant.

- 6. No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.

- 7. Contact Hitachi's sales office for any questions regarding this document or Hitachi semiconductor products.

# Preface

The H8/300L Series of single-chip microcomputers has the high-speed H8/300L CPU at its core, with many necessary peripheral functions on-chip. The H8/300L CPU instruction set is compatible with the H8/300 CPU.

The H8/3644 Series has a system-on-a-chip architecture that includes such peripheral functions as a D/A converter, five timers, a 14-bit PWM, a two-channel serial communication interface, and an A/D converter. This makes it ideal for use in advanced control systems.

This manual describes the hardware of the H8/3644 Series. For details on the H8/3644 Series instruction set, refer to the H8/300L Series Programming Manual.

# Contents

| Secti | on 1     | Overview                             | 1  |

|-------|----------|--------------------------------------|----|

| 1.1   | Overvio  | ew                                   | 1  |

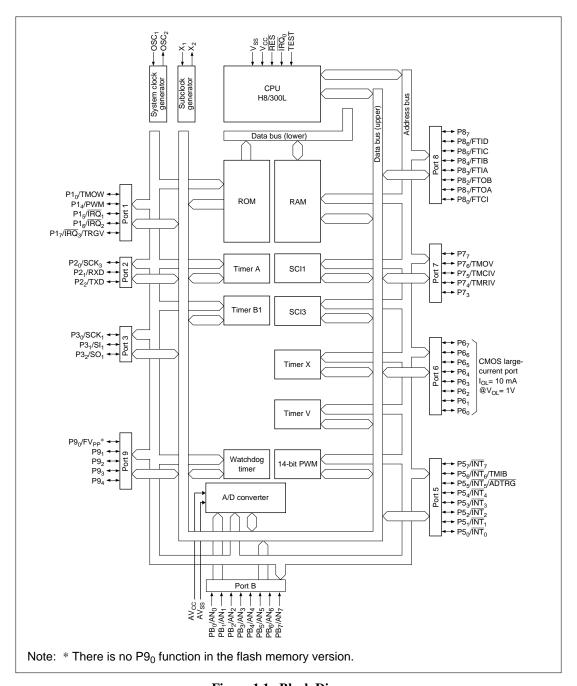

| 1.2   | Interna  | Block Diagram                        | 6  |

| 1.3   | Pin Arr  | angement and Functions               | 7  |

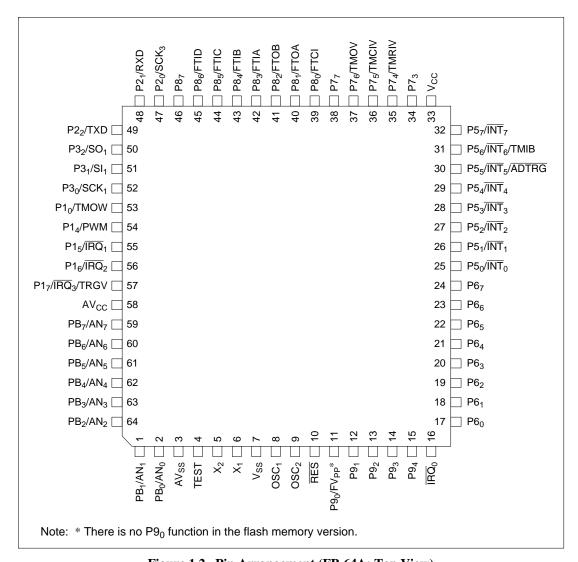

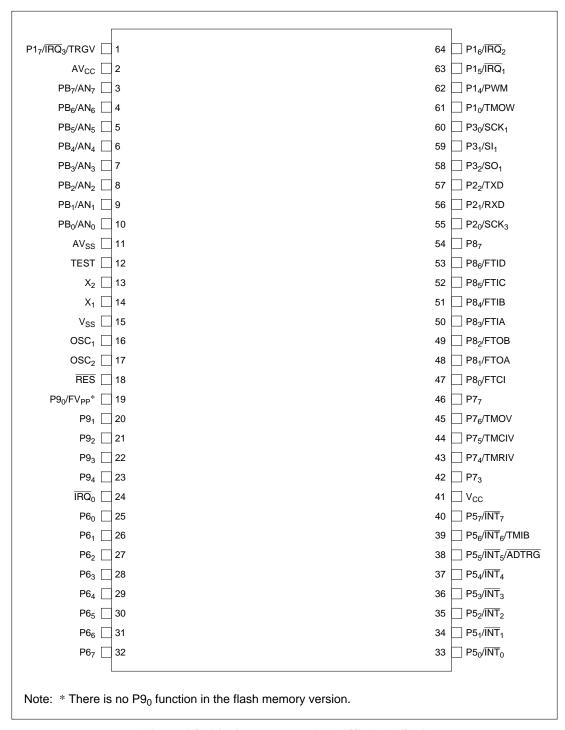

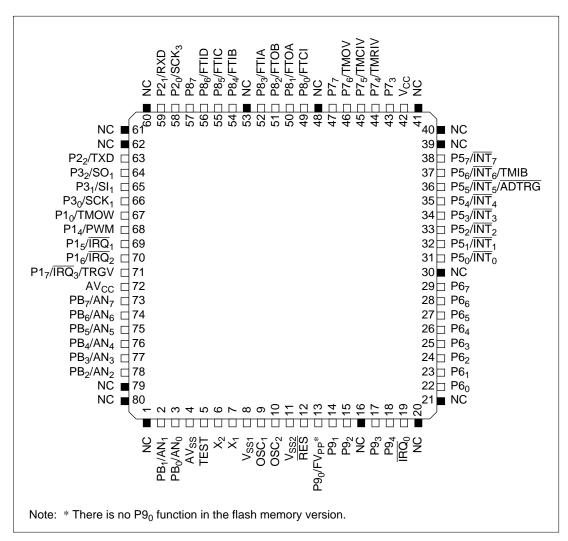

|       | 1.3.1    | Pin Arrangement                      | 7  |

|       | 1.3.2    | Pin Functions                        | 10 |

| Secti | on 2     | CPU                                  | 15 |

| 2.1   | Overvio  | ew                                   | 15 |

|       | 2.1.1    | Features                             | 15 |

|       | 2.1.2    | Address Space                        | 16 |

|       | 2.1.3    | Register Configuration               | 16 |

| 2.2   | Registe  | r Descriptions                       | 17 |

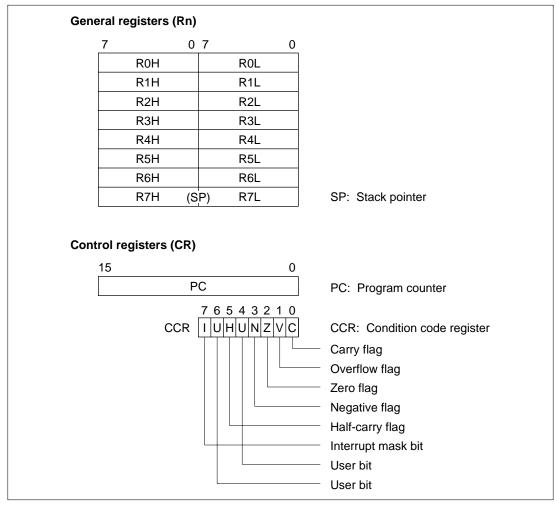

|       | 2.2.1    | General Registers                    | 17 |

|       | 2.2.2    | Control Registers                    | 17 |

|       | 2.2.3    | Initial Register Values              | 19 |

| 2.3   | Data Fo  | ormats                               | 19 |

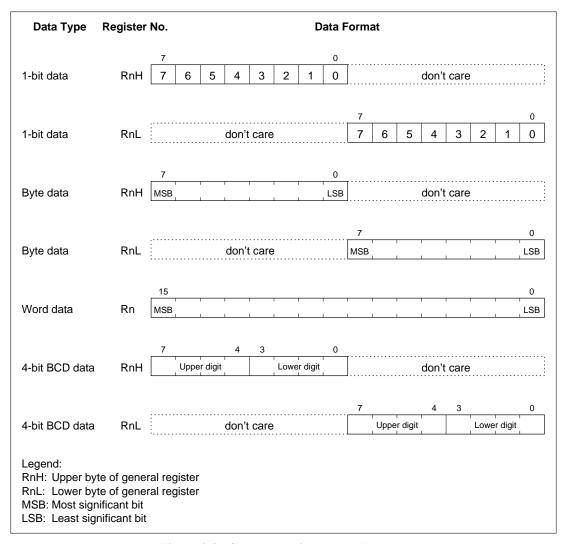

|       | 2.3.1    | Data Formats in General Registers    | 20 |

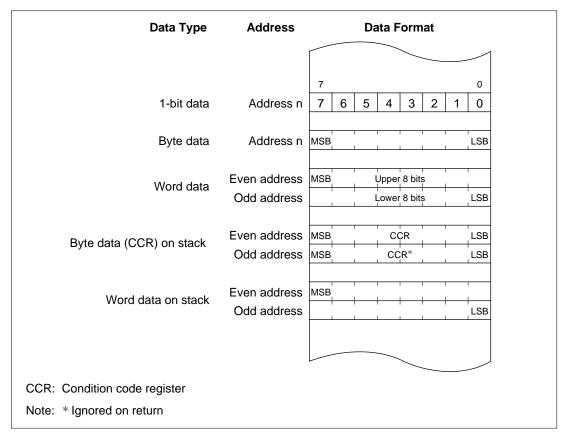

|       | 2.3.2    | Memory Data Formats                  | 21 |

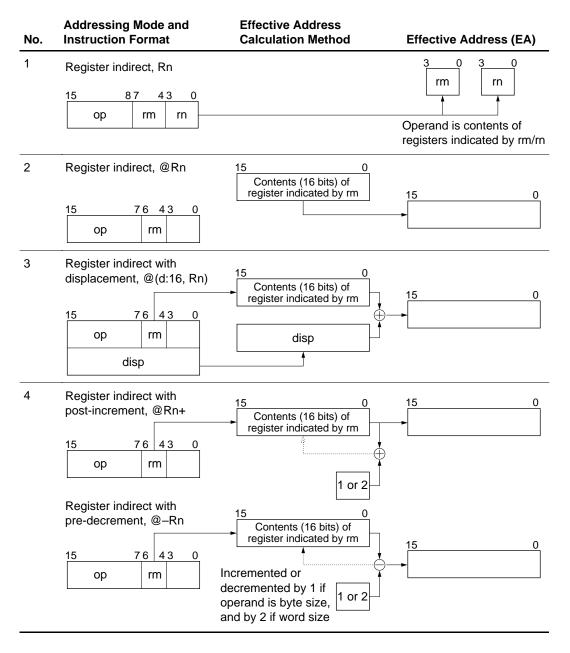

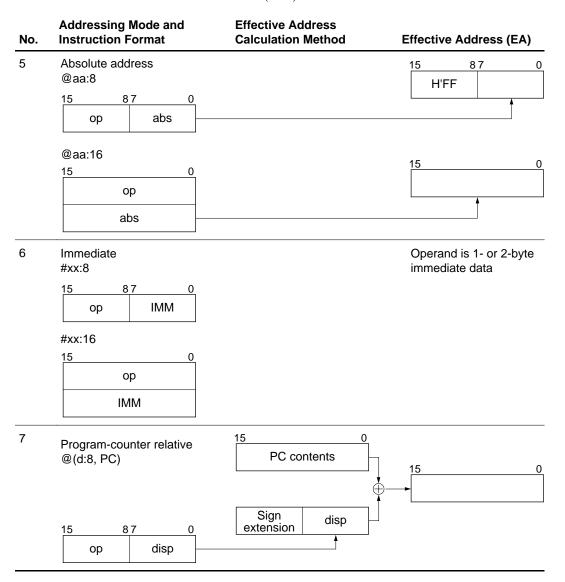

| 2.4   | Addres   | sing Modes                           | 22 |

|       | 2.4.1    | Addressing Modes                     | 22 |

|       | 2.4.2    | Effective Address Calculation        | 24 |

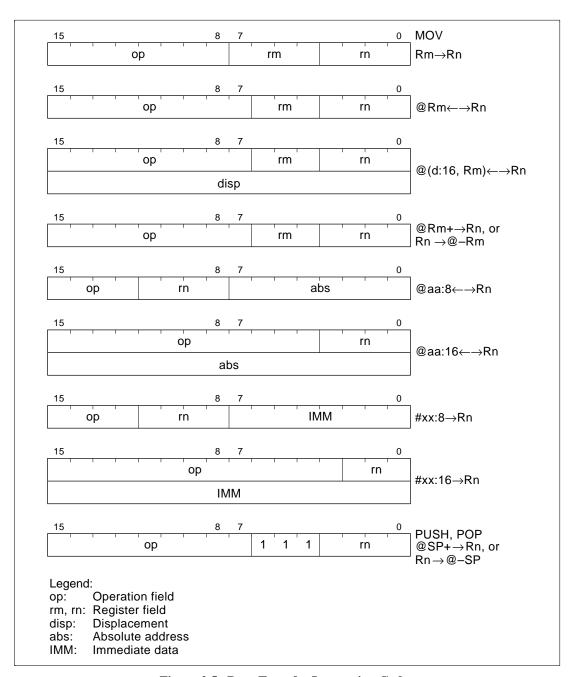

| 2.5   | Instruct | tion Set                             | 28 |

|       | 2.5.1    | Data Transfer Instructions           | 30 |

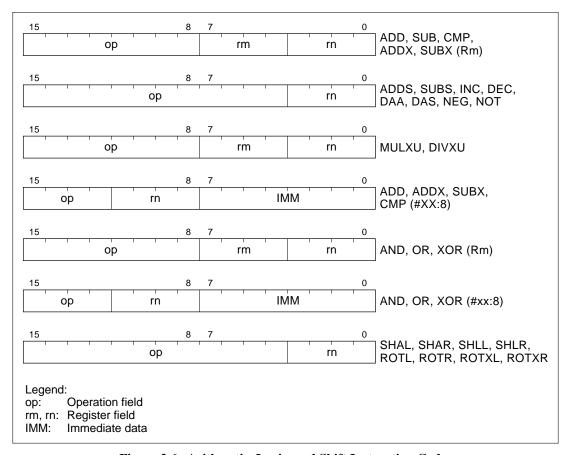

|       | 2.5.2    | Arithmetic Operations                | 32 |

|       | 2.5.3    | Logic Operations                     | 33 |

|       | 2.5.4    | Shift Operations                     | 33 |

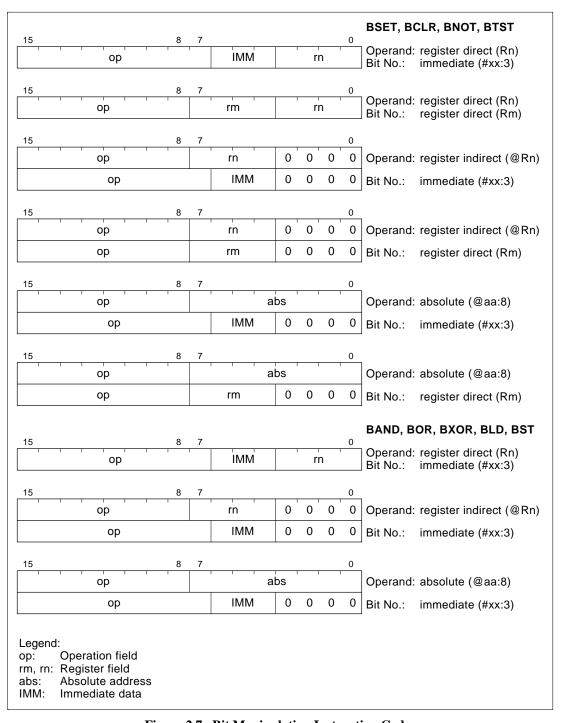

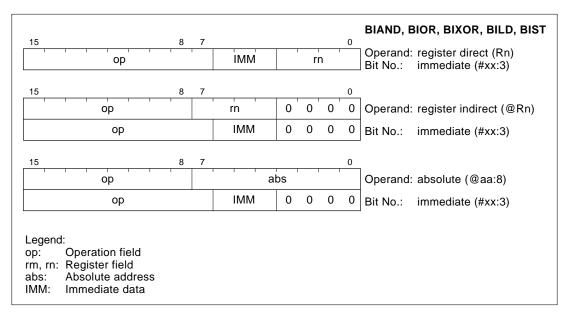

|       | 2.5.5    | Bit Manipulations                    | 35 |

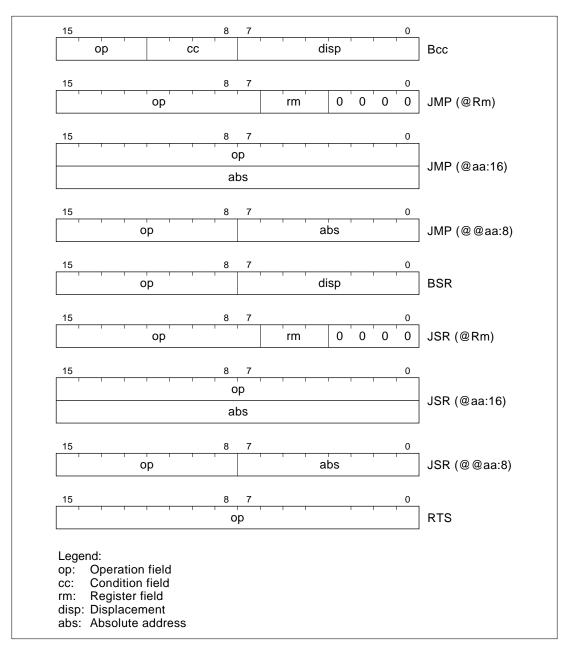

|       | 2.5.6    | Branching Instructions               | 39 |

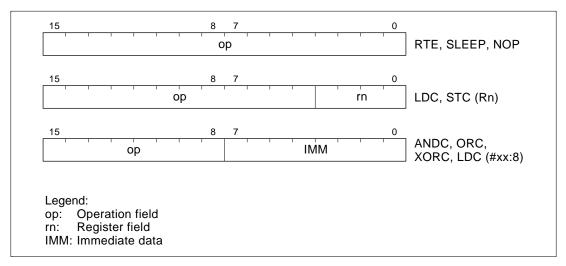

|       | 2.5.7    | System Control Instructions          | 41 |

|       | 2.5.8    | Block Data Transfer Instruction      | 42 |

| 2.6   | Basic C  | Operational Timing                   | 44 |

|       | 2.6.1    | Access to On-Chip Memory (RAM, ROM)  | 44 |

|       | 2.6.2    | Access to On-Chip Peripheral Modules | 45 |

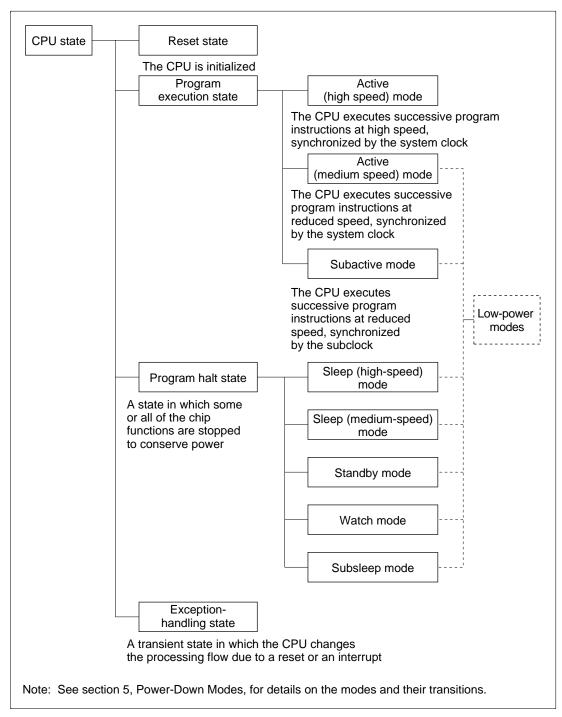

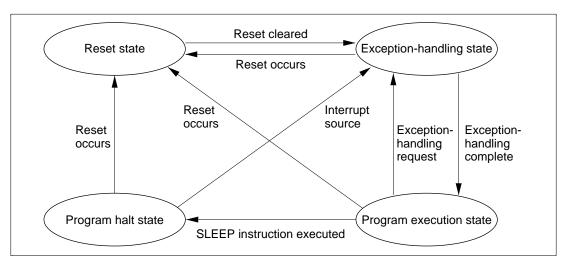

| 2.7   | CPU St   | ates                                 | 46 |

|       | 2.7.1    | Overview                             | 46 |

|       | 2.7.2    | Program Execution State              | 48 |

|       | 2.7.3    | Program Halt State                   | 48 |

|       | 2.7.4    | Exception-Handling State             | 48 |

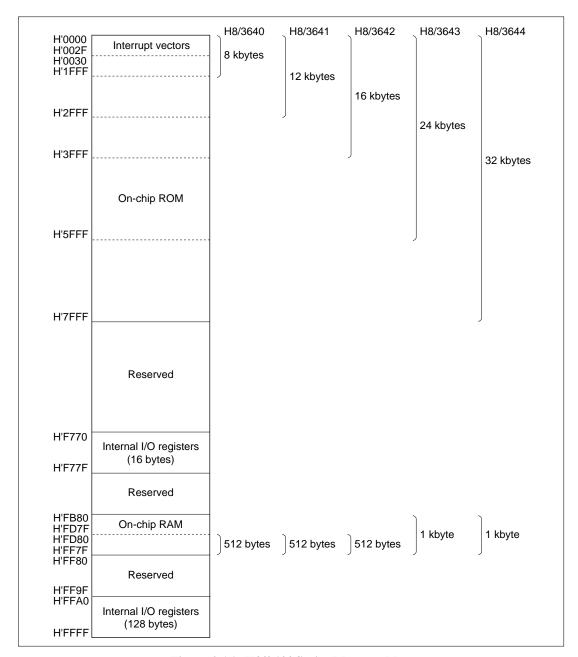

| 2.8  | .8 Memory Map |                                                        | 49       |  |  |

|------|---------------|--------------------------------------------------------|----------|--|--|

| 2.9  | Applic        | eation Notes                                           | 50       |  |  |

|      | 2.9.1         | Notes on Data Access                                   | 50       |  |  |

|      | 2.9.2         | Notes on Bit Manipulation                              | 52       |  |  |

|      | 2.9.3         | Notes on Use of the EEPMOV Instruction                 | 58       |  |  |

| Sect | tion 3        | Exception Handling                                     | 59       |  |  |

| 3.1  | Overv         | iew                                                    | 59       |  |  |

| 3.2  | Reset.        |                                                        | 59       |  |  |

|      | 3.2.1         | Overview                                               | 59       |  |  |

|      | 3.2.2         | Reset Sequence                                         | 59       |  |  |

|      | 3.2.3         | Interrupt Immediately after Reset                      | 61       |  |  |

| 3.3  | Interru       | ipts                                                   | 61       |  |  |

|      | 3.3.1         | Overview                                               | 61       |  |  |

|      | 3.3.2         | Interrupt Control Registers                            | 63       |  |  |

|      | 3.3.3         | External Interrupts                                    | 72       |  |  |

|      | 3.3.4         | Internal Interrupts                                    | 72       |  |  |

|      | 3.3.5         | Interrupt Operations                                   | 73       |  |  |

|      | 3.3.6         | Interrupt Response Time                                | 78       |  |  |

| 3.4  | Applic        | Application Notes 79                                   |          |  |  |

|      | 3.4.1         | Notes on Stack Area Use                                | 79       |  |  |

|      | 3.4.2         | Notes on Rewriting Port Mode Registers                 | 80       |  |  |

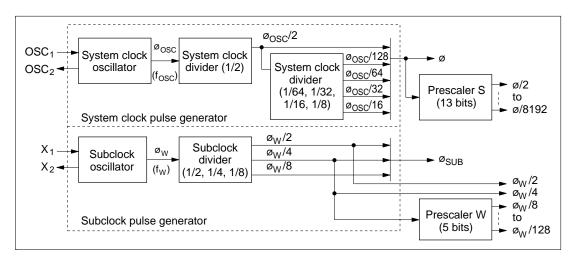

| Sect | tion 4        | Clock Pulse Generators                                 | 83       |  |  |

| 4.1  |               | iew                                                    | 83       |  |  |

|      | 4.1.1         | Block Diagram                                          | 83       |  |  |

|      | 4.1.2         | System Clock and Subclock                              | 83       |  |  |

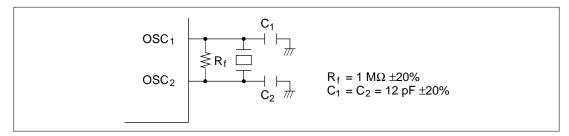

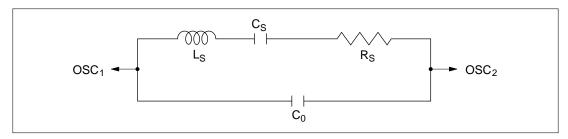

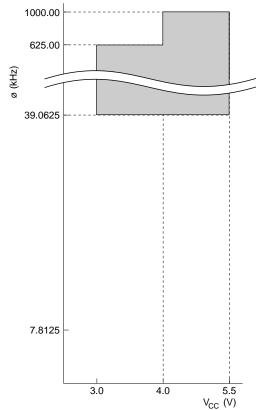

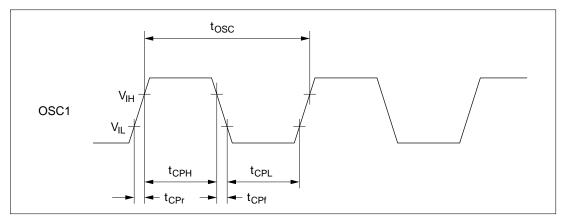

| 4.2  |               | n Clock Generator                                      | 84       |  |  |

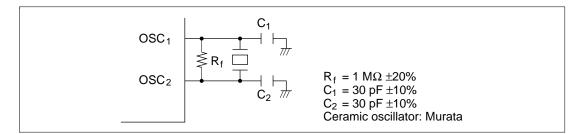

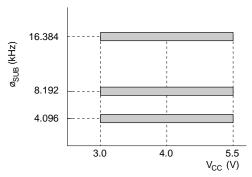

| 4.3  | -             | ock Generator                                          | 87       |  |  |

| 4.4  |               | lers                                                   | 88       |  |  |

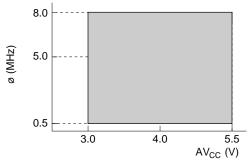

| 4.5  |               | on Oscillators                                         | 88       |  |  |

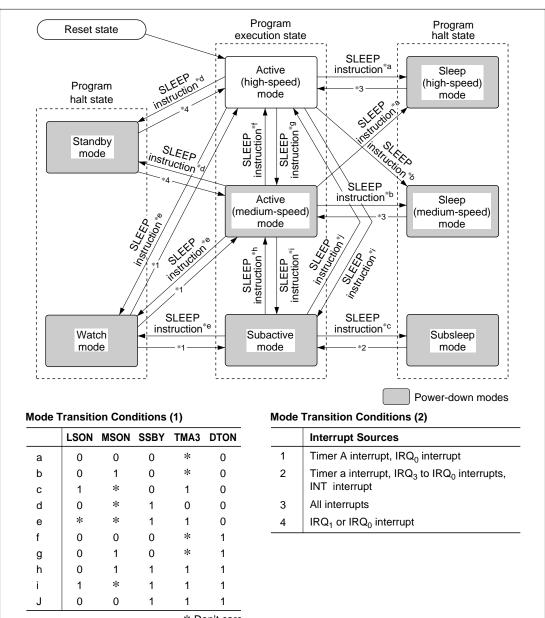

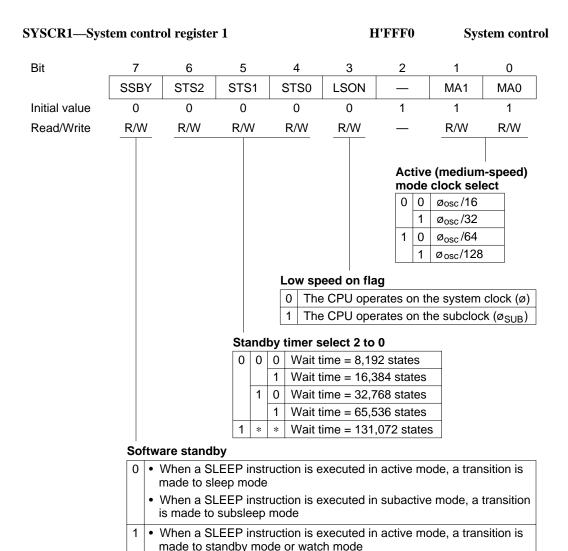

| Sect | tion 5        | Power-Down Modes                                       | 89       |  |  |

| 5.1  |               | iew                                                    | 89       |  |  |

| 3.1  |               | System Control Registers                               | 92       |  |  |

| 5.2  |               | Mode                                                   | 96       |  |  |

| 3.2  | 5.2.1         | Transition to Sleep Mode                               | 96       |  |  |

|      | 5.2.1         |                                                        | 96       |  |  |

|      | 5.2.3         | Clearing Sleep Mode                                    | 96       |  |  |

| 5.3  |               | by Mode                                                | 97       |  |  |

| ر.ى  | 5.3.1         | Transition to Standby Mode                             | 97       |  |  |

|      | 5.3.1         | Clearing Standby Mode                                  |          |  |  |

|      | 5.3.3         | Oscillator Settling Time after Standby Mode is Cleared | 97<br>98 |  |  |

|      | ر.د.د         | Oscinator betting time arter brancoy widge is cleared  | 2C       |  |  |

| 5.4   | Watch   | Mode                                                 | 99  |

|-------|---------|------------------------------------------------------|-----|

|       | 5.4.1   | Transition to Watch Mode                             | 99  |

|       | 5.4.2   | Clearing Watch Mode                                  | 99  |

|       | 5.4.3   | Oscillator Settling Time after Watch Mode is Cleared | 99  |

| 5.5   | Subsle  | ep Mode                                              | 100 |

|       | 5.5.1   | Transition to Subsleep Mode                          | 100 |

|       | 5.5.2   | Clearing Subsleep Mode                               | 100 |

| 5.6   | Subact  | ive Mode                                             | 101 |

|       | 5.6.1   | Transition to Subactive Mode                         | 101 |

|       | 5.6.2   | Clearing Subactive Mode                              | 101 |

|       | 5.6.3   | Operating Frequency in Subactive Mode                | 101 |

| 5.7   | Active  | (Medium-Speed) Mode                                  | 102 |

|       | 5.7.1   | Transition to Active (Medium-Speed) Mode             | 102 |

|       | 5.7.2   | Clearing Active (Medium-Speed) Mode                  | 102 |

|       | 5.7.3   | Operating Frequency in Active (Medium-Speed) Mode    | 102 |

| 5.8   | Direct  | Transfer                                             | 103 |

|       |         |                                                      |     |

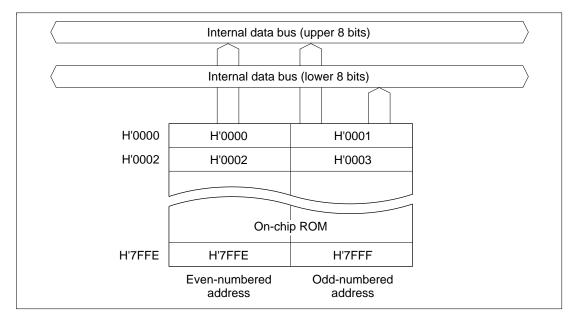

| Secti | ion 6   | ROM                                                  | 105 |

| 6.1   | Overvi  | ew                                                   | 105 |

|       | 6.1.1   | Block Diagram                                        | 105 |

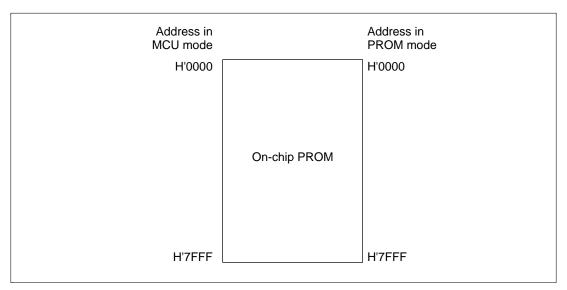

| 6.2   | PROM    | Mode                                                 | 106 |

|       | 6.2.1   | Setting to PROM Mode                                 | 106 |

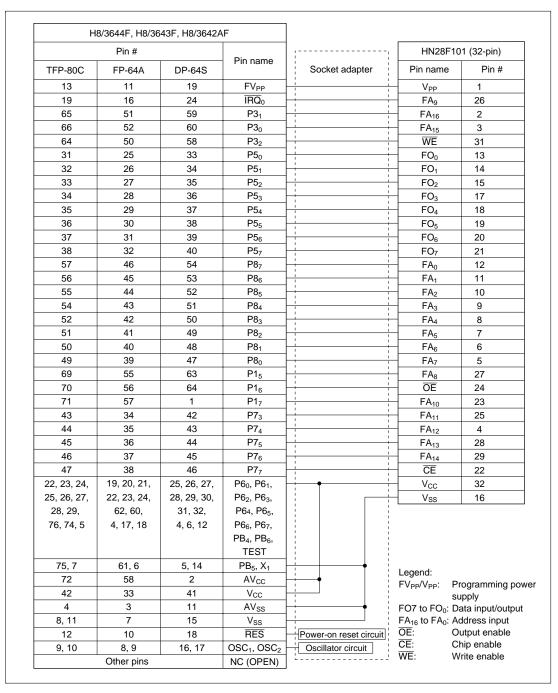

|       | 6.2.2   | Socket Adapter Pin Arrangement and Memory Map        | 106 |

| 6.3   | Progra  | mming                                                | 108 |

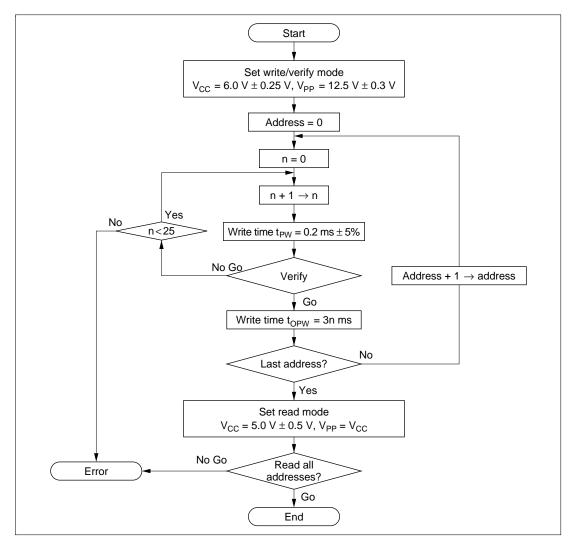

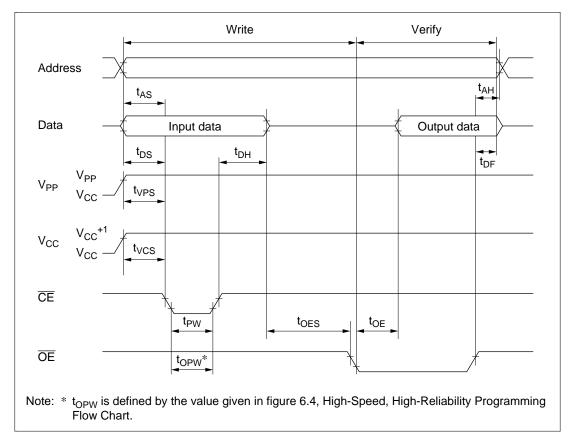

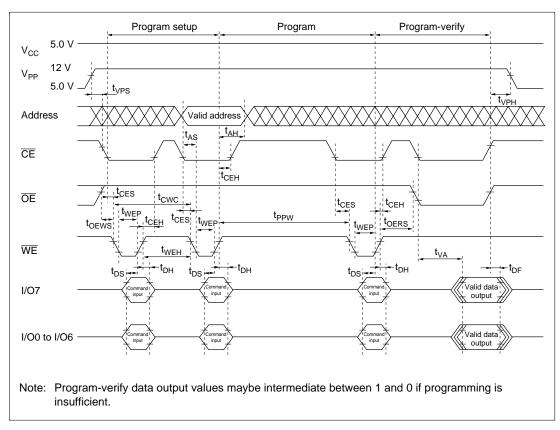

|       | 6.3.1   | Writing and Verifying                                | 109 |

|       | 6.3.2   | Programming Precautions                              | 112 |

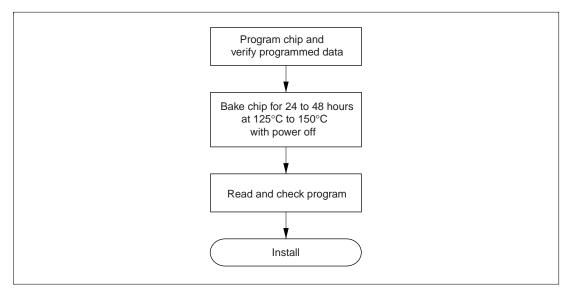

|       | 6.3.3   | Reliability of Programmed Data                       | 113 |

| 6.4   | Flash I | Memory Overview                                      | 113 |

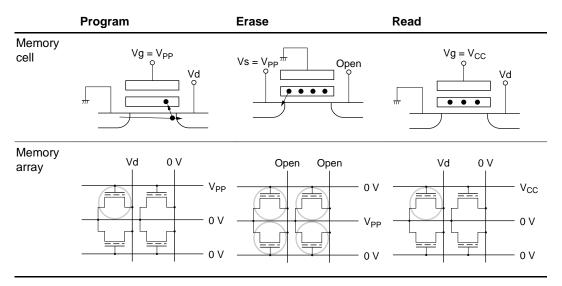

|       | 6.4.1   | Principle of Flash Memory Operation                  | 113 |

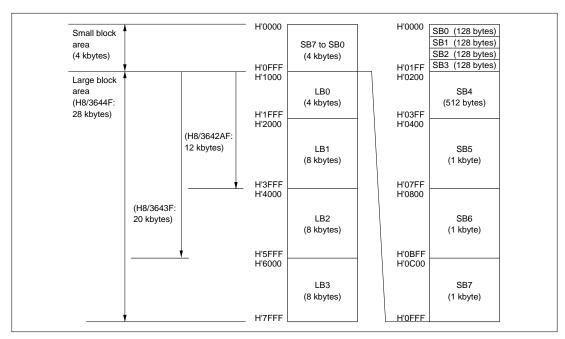

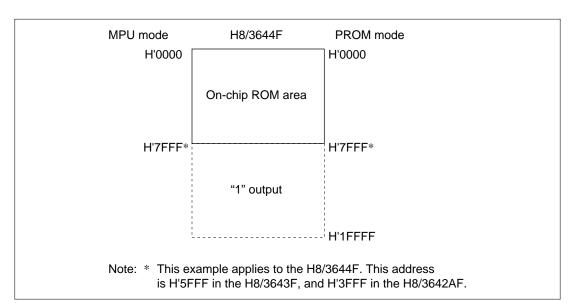

|       | 6.4.2   | Mode Pin Settings and ROM Space                      | 114 |

|       | 6.4.3   | Features                                             | 115 |

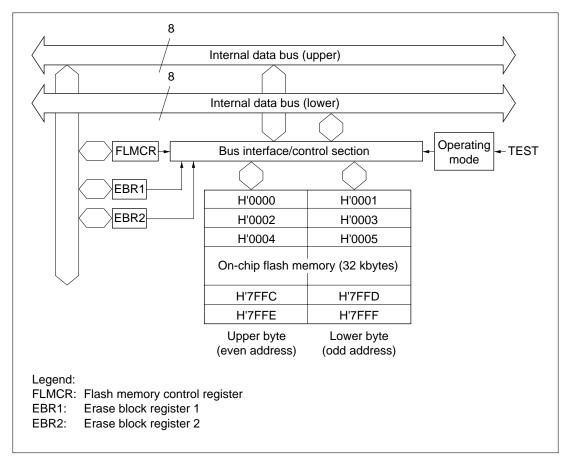

|       | 6.4.4   | Block Diagram                                        | 116 |

|       | 6.4.5   | Pin Configuration                                    | 117 |

|       | 6.4.6   | Register Configuration                               | 117 |

| 6.5   | Flash l | Memory Register Descriptions                         | 118 |

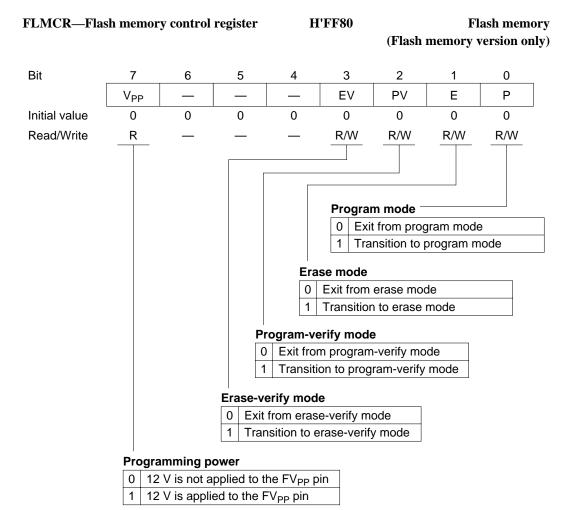

|       | 6.5.1   | Flash Memory Control Register (FLMCR)                | 118 |

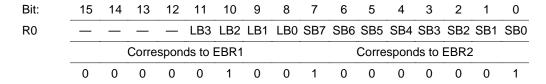

|       | 6.5.2   | Erase Block Register 1 (EBR1)                        | 120 |

|       | 6.5.3   | Erase Block Register 2 (EBR2)                        | 121 |

| 6.6   | On-Bo   | ard Programming Modes                                | 123 |

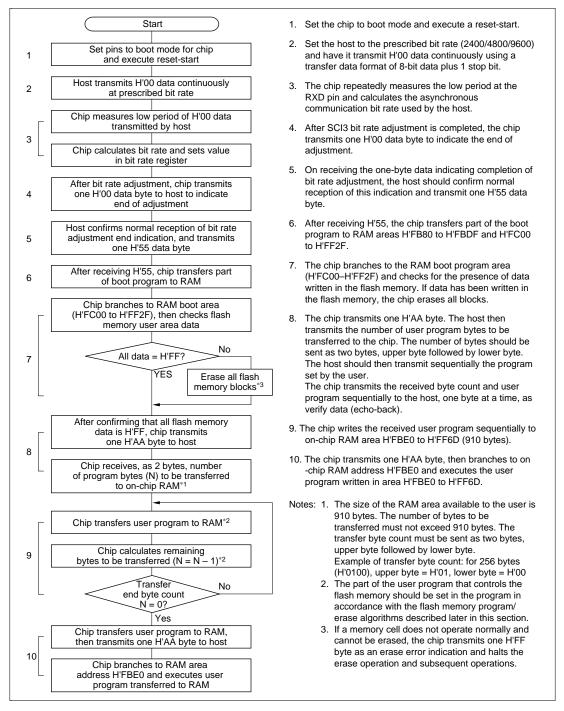

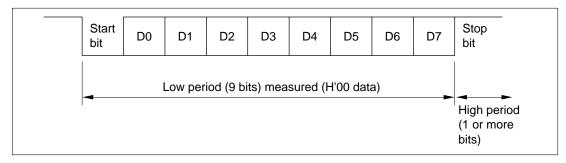

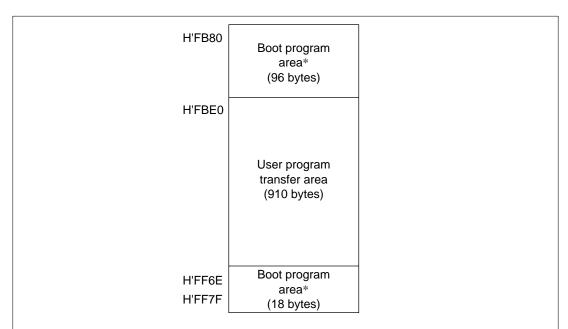

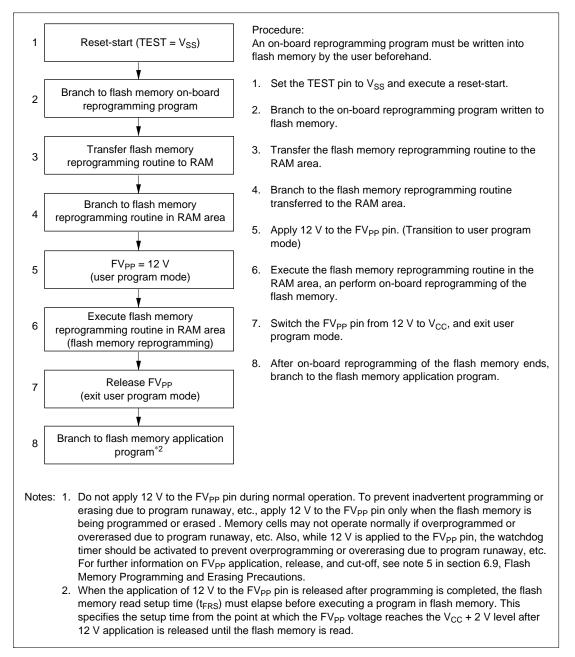

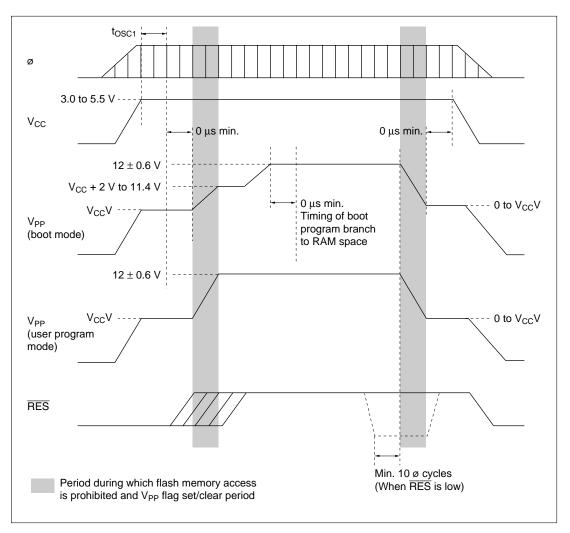

|       | 6.6.1   | Boot Mode                                            | 123 |

|       | 6.6.2   | User Program Mode                                    | 128 |

| 6.7   | Progra  | mming and Erasing Flash Memory                       | 130 |

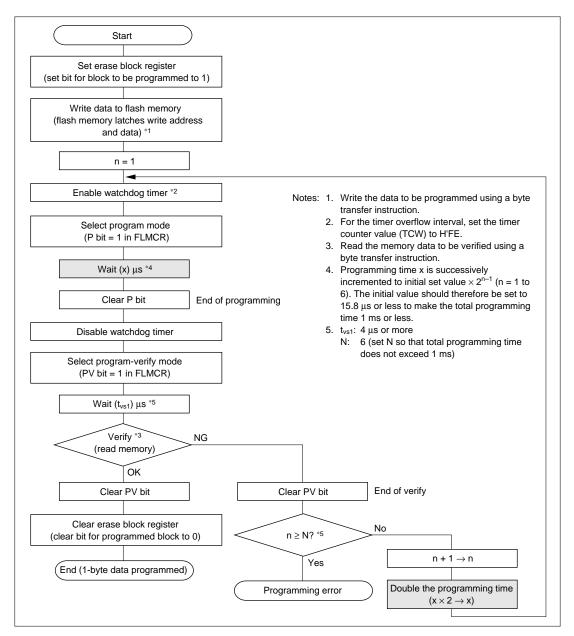

|       | 6.7.1   | Program Mode                                         | 130 |

iii

|      | 6.7.2   | Program-Verify Mode                                        | 131 |

|------|---------|------------------------------------------------------------|-----|

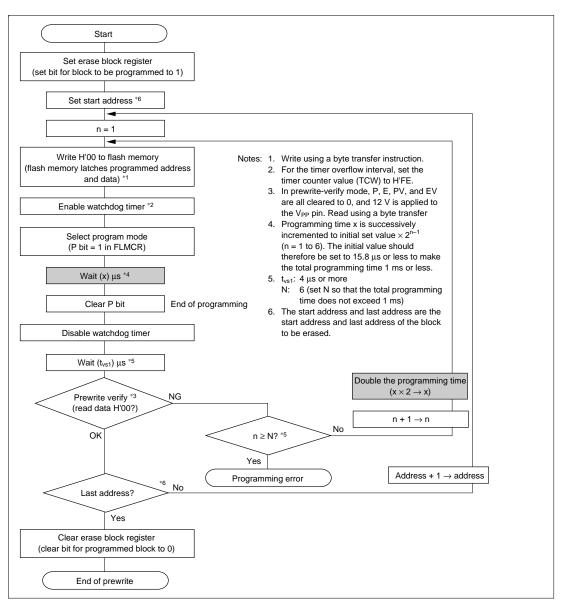

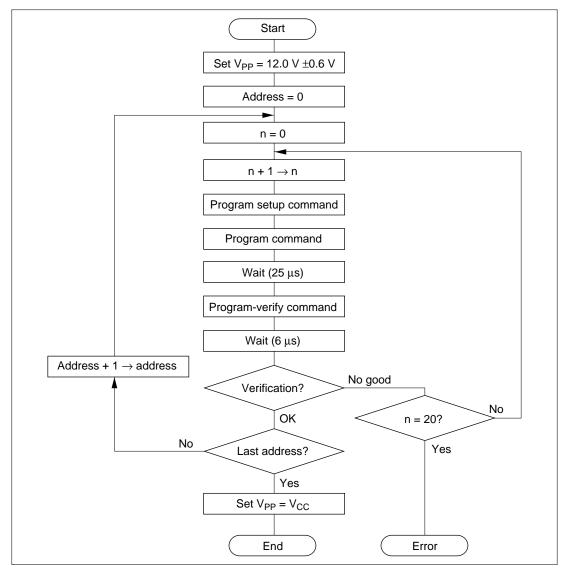

|      | 6.7.3   | Programming Flowchart and Sample Program                   | 132 |

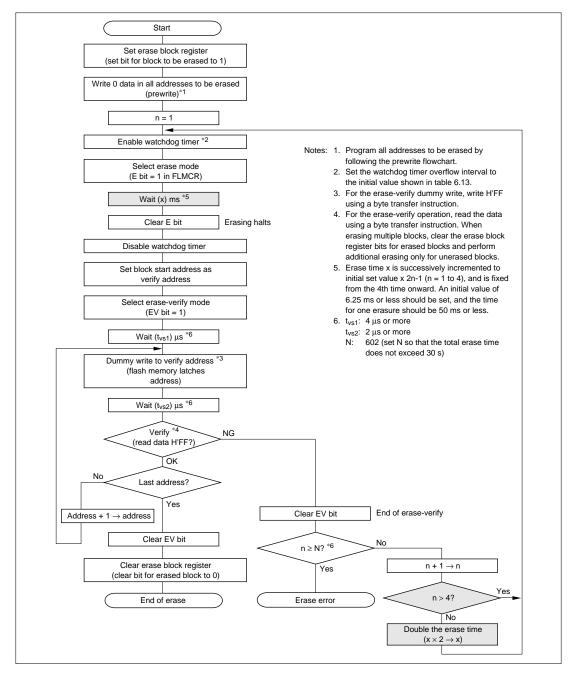

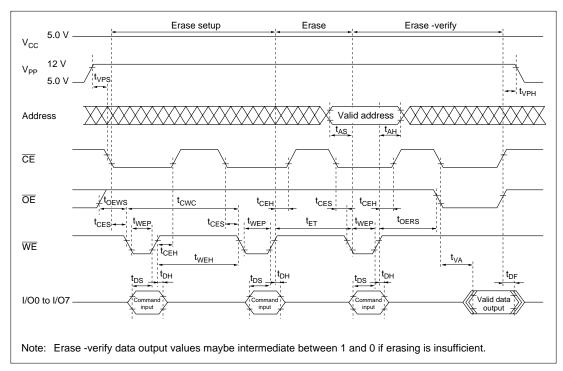

|      | 6.7.4   | Erase Mode                                                 | 135 |

|      | 6.7.5   | Erase-Verify Mode                                          | 135 |

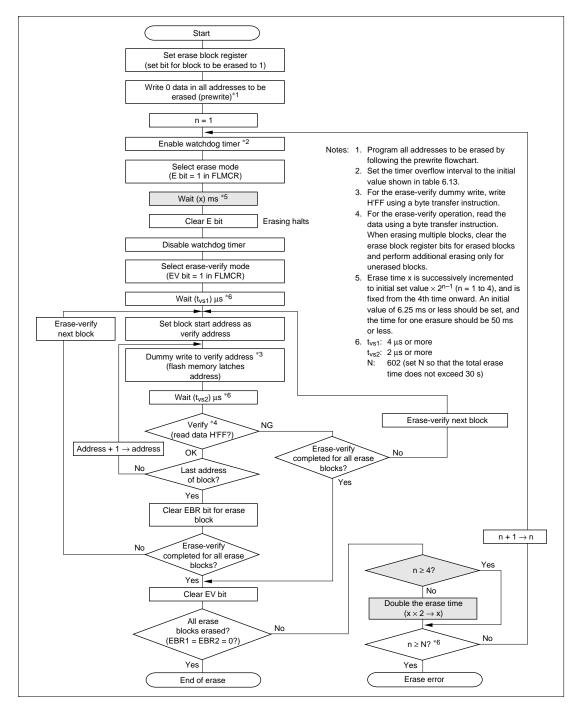

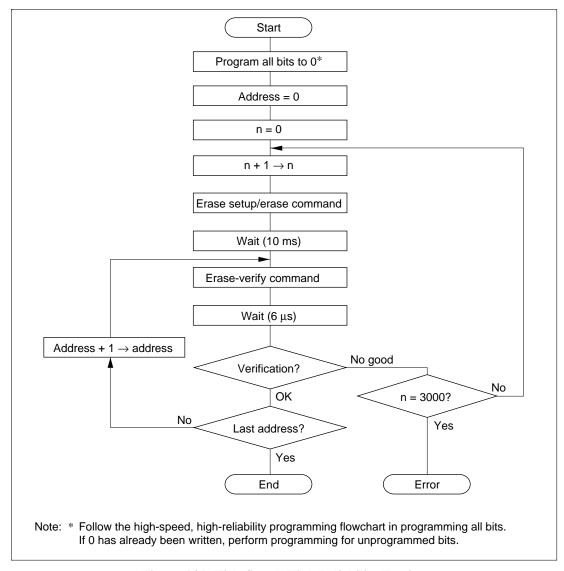

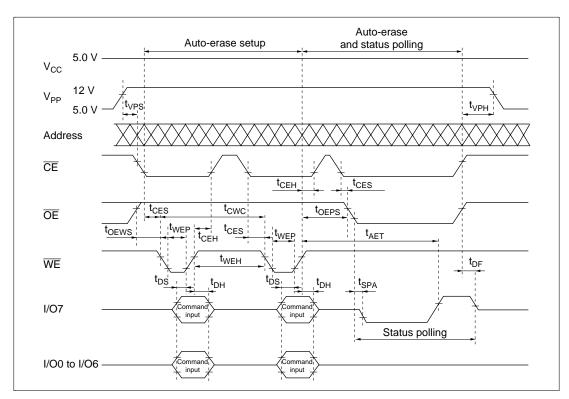

|      | 6.7.6   | Erase Flowcharts and Sample Programs                       | 136 |

|      | 6.7.7   | Prewrite-Verify Mode                                       | 149 |

|      | 6.7.8   | Protect Modes                                              | 149 |

|      | 6.7.9   | Interrupt Handling during Flash Memory Programming/Erasing | 150 |

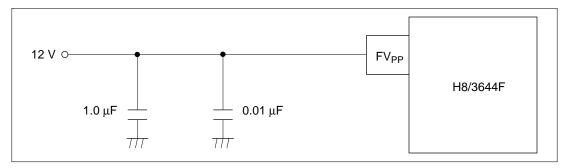

| 6.8  | Flash l | Memory PROM Mode (H8/3644F, H8/3643F, and H8/3642AF)       |     |

|      | 6.8.1   | PROM Mode Setting                                          |     |

|      | 6.8.2   | Socket Adapter and Memory Map                              |     |

|      | 6.8.3   | Operation in PROM Mode                                     |     |

| 6.9  | Flash l | Memory Programming and Erasing Precautions                 |     |

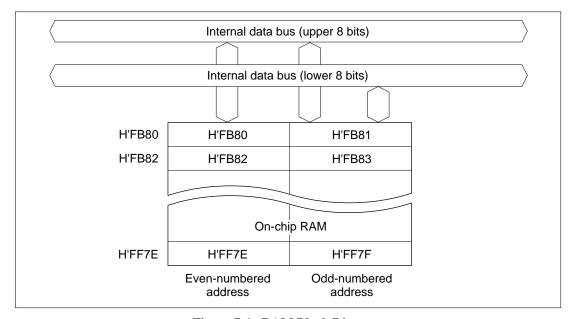

| Sect | tion 7  | RAM                                                        | 169 |

| 7.1  |         | iew                                                        |     |

| 7.1  | 7.1.1   | Block Diagram.                                             |     |

|      | 7.1.1   | DIOCK Diagram.                                             | 109 |

| Sect | tion 8  | I/O Ports                                                  | 171 |

| 8.1  | Overv   | iew                                                        | 171 |

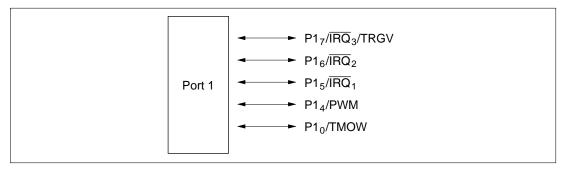

| 8.2  | Port 1. |                                                            | 173 |

|      | 8.2.1   | Overview                                                   | 173 |

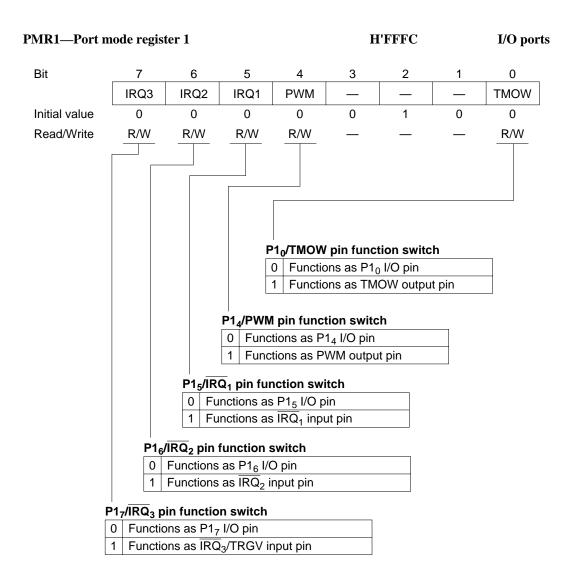

|      | 8.2.2   | Register Configuration and Description                     | 173 |

|      | 8.2.3   | Pin Functions                                              | 177 |

|      | 8.2.4   | Pin States                                                 | 178 |

|      | 8.2.5   | MOS Input Pull-Up                                          | 178 |

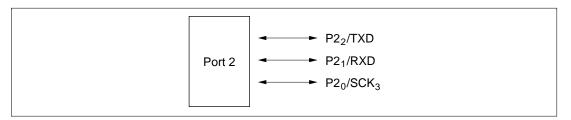

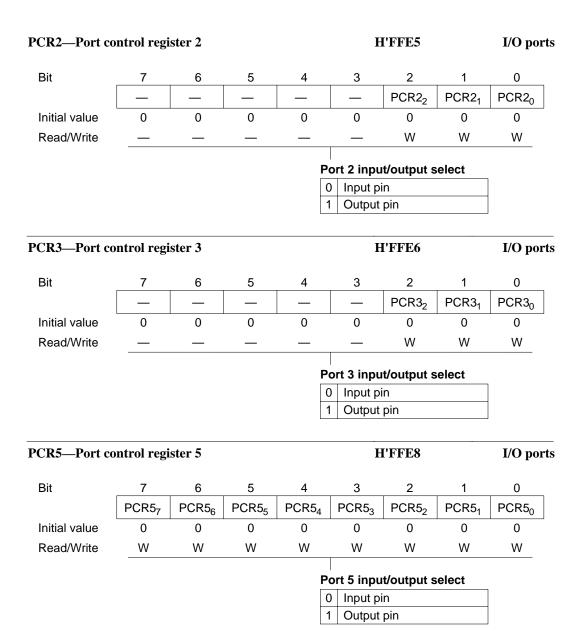

| 8.3  | Port 2. |                                                            | 179 |

|      | 8.3.1   | Overview                                                   | 179 |

|      | 8.3.2   | Register Configuration and Description                     | 179 |

|      | 8.3.3   | Pin Functions                                              | 181 |

|      | 8.3.4   | Pin States                                                 | 181 |

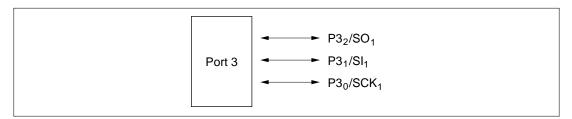

| 8.4  | Port 3. |                                                            | 182 |

|      | 8.4.1   | Overview                                                   | 182 |

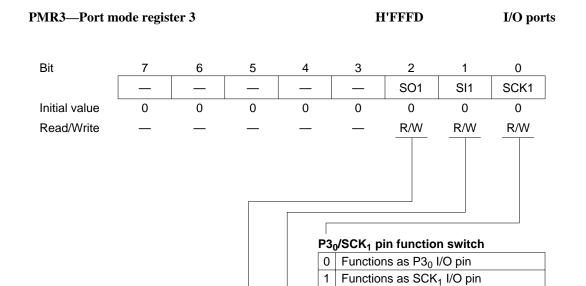

|      | 8.4.2   | Register Configuration and Description                     | 182 |

|      | 8.4.3   | Pin Functions                                              | 186 |

|      | 8.4.4   | Pin States                                                 | 187 |

|      | 8.4.5   | MOS Input Pull-Up                                          | 187 |

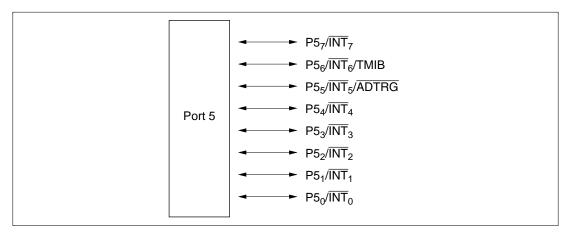

| 8.5  | Port 5. |                                                            | 188 |

|      | 8.5.1   | Overview                                                   |     |

|      | 8.5.2   | Register Configuration and Description                     |     |

|      | 8.5.3   | Pin Functions                                              |     |

|      | 8.5.4   | Pin States                                                 |     |

|      | 8.5.5   | MOS Input Pull-Up                                          |     |

|      |         | <u>.</u>                                                   |     |

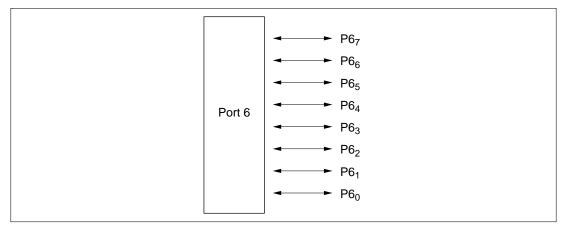

| 8.6             | Port 6 |                                        | 192 |

|-----------------|--------|----------------------------------------|-----|

|                 | 8.6.1  | Overview                               | 192 |

|                 | 8.6.2  | Register Configuration and Description | 192 |

|                 | 8.6.3  | Pin Functions                          | 193 |

|                 | 8.6.4  | Pin States                             | 194 |

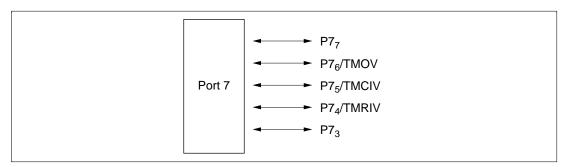

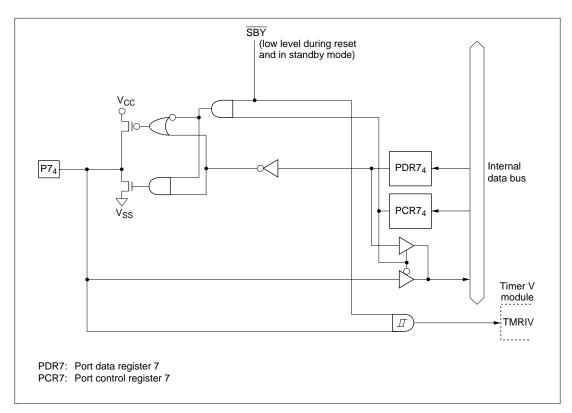

| 8.7             | Port 7 |                                        | 195 |

|                 | 8.7.1  | Overview                               | 195 |

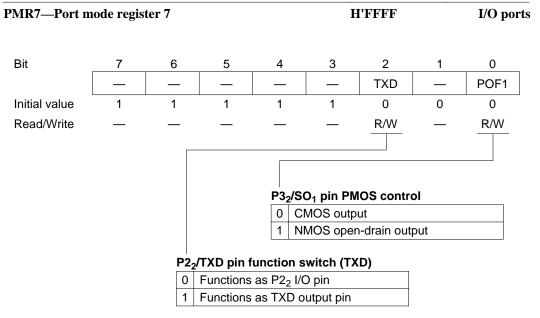

|                 | 8.7.2  | Register Configuration and Description | 195 |

|                 | 8.7.3  | Pin Functions.                         | 197 |

|                 | 8.7.4  | Pin States                             | 197 |

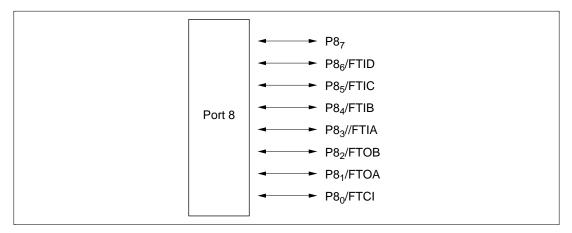

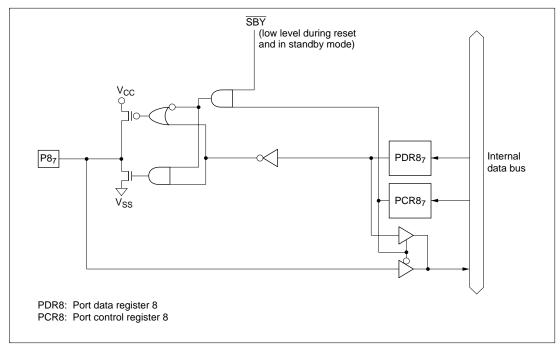

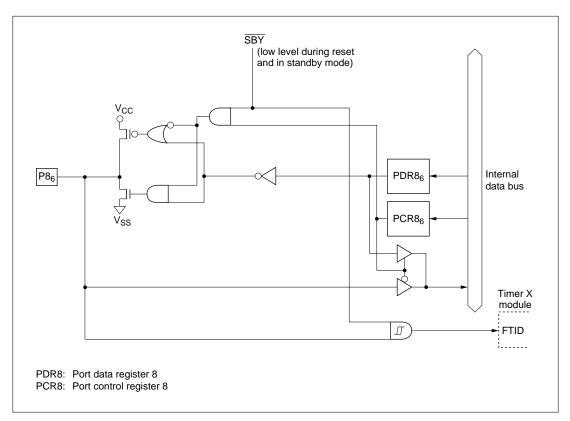

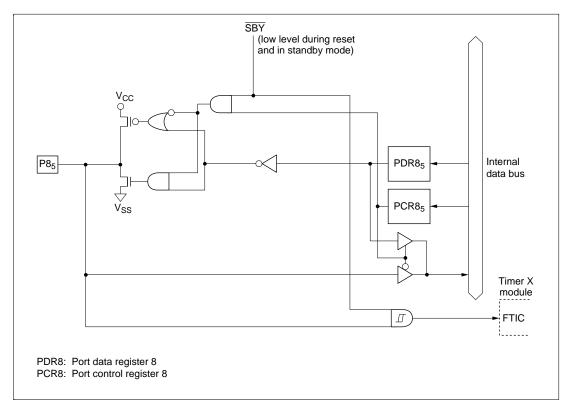

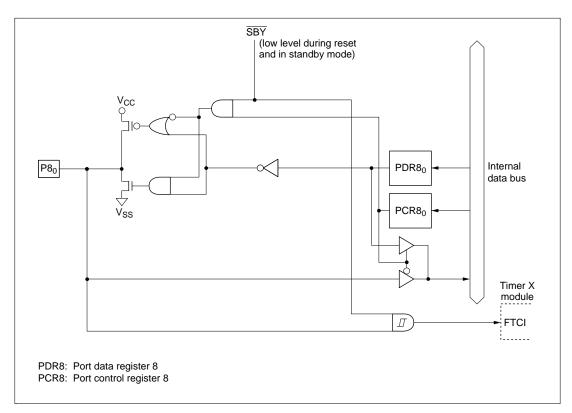

| 8.8             | Port 8 |                                        | 198 |

|                 | 8.8.1  | Overview                               | 198 |

|                 | 8.8.2  | Register Configuration and Description | 198 |

|                 | 8.8.3  | Pin Functions.                         | 200 |

|                 | 8.8.4  | Pin States                             | 201 |

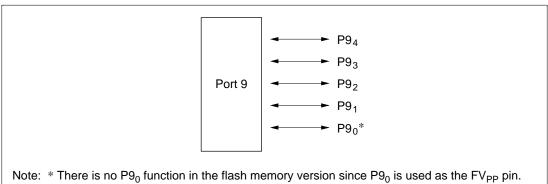

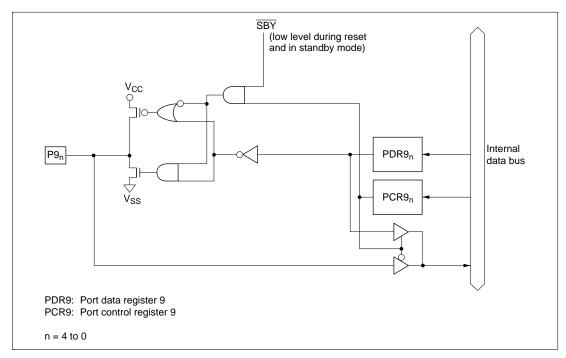

| 8.9             | Port 9 |                                        | 202 |

|                 | 8.9.1  | Overview                               | 202 |

|                 | 8.9.2  | Register Configuration and Description | 202 |

|                 | 8.9.3  | Pin Functions                          | 204 |

|                 | 8.9.4  | Pin States                             | 204 |

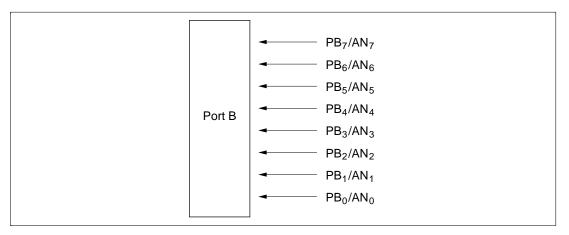

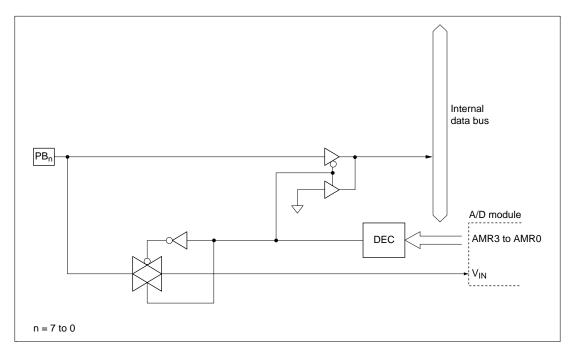

| 8.10            | Port B |                                        | 205 |

|                 | 8.10.1 | Overview                               | 205 |

|                 | 8.10.2 | Register Configuration and Description | 205 |

|                 | 8.10.3 | Pin Functions                          | 206 |

|                 | 8.10.4 | Pin States                             | 206 |

| Sect            | ion 9  | Timers                                 | 207 |

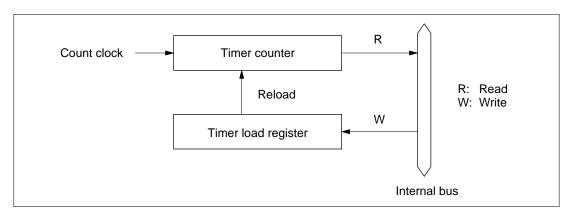

| 9.1             | -      | ew                                     |     |

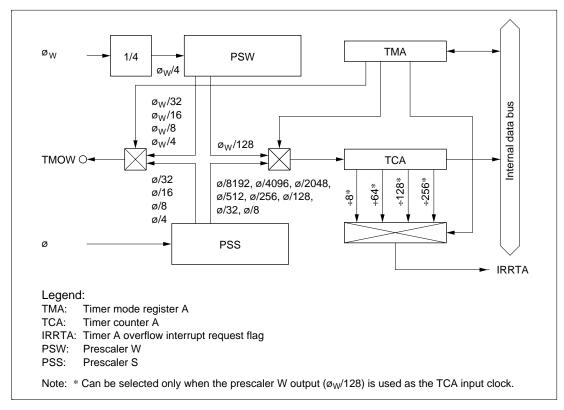

| 9.2             |        | A                                      |     |

| 7.2             | 9.2.1  | Overview                               |     |

|                 | 9.2.2  | Register Descriptions.                 |     |

|                 | 9.2.3  | Timer Operation                        |     |

|                 | 9.2.4  | Timer A Operation States               |     |

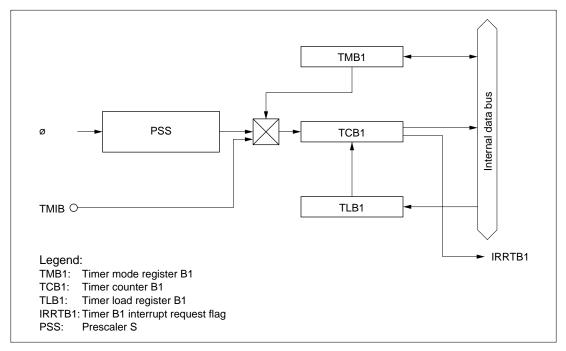

| 9.3             | ,      | B1                                     |     |

| 7.5             |        | Overview                               | 214 |

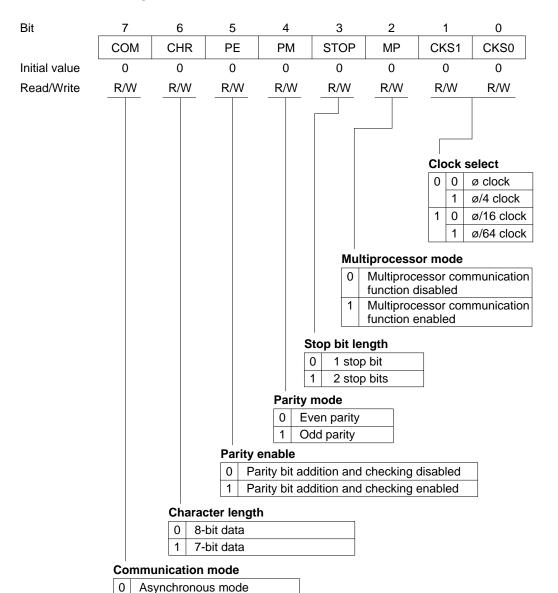

|                 | 9.3.2  | Register Descriptions.                 |     |

|                 | 9.3.3  | Timer Operation                        |     |

|                 | 9.3.4  | Timer B1 Operation States              |     |

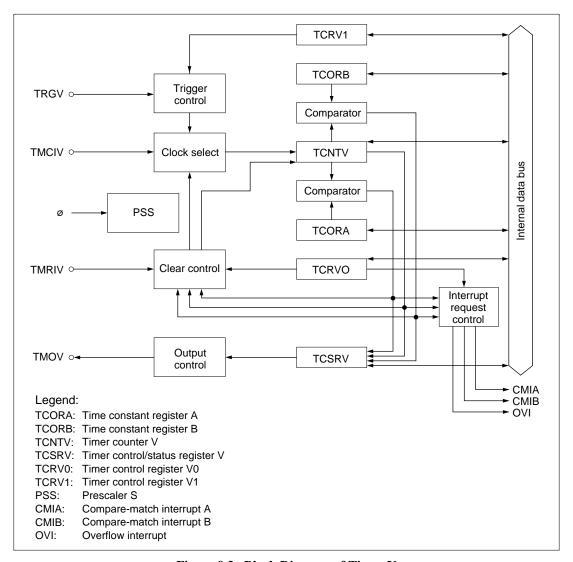

| 9.4             |        | V                                      |     |

| J. <del>T</del> | 9.4.1  | Overview                               |     |

|                 | 9.4.1  | Register Descriptions.                 |     |

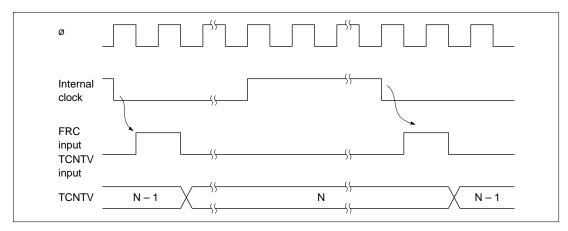

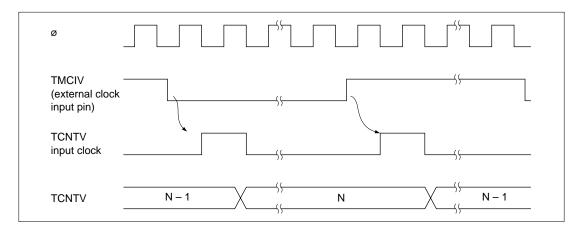

|                 | 9.4.2  | Timer Operation                        |     |

|                 | 9.4.3  | Timer V Operation Modes                |     |

|                 | ノ・マ・エ  | 1 111101 1 Operation 1/100co           | 200 |

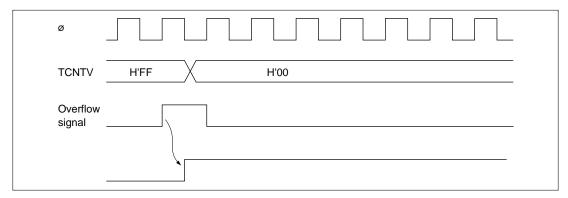

|       | 9.4.5   | Interrupt Sources                     | 233        |

|-------|---------|---------------------------------------|------------|

|       | 9.4.6   | Application Examples                  | 234        |

|       | 9.4.7   | Application Notes                     | 236        |

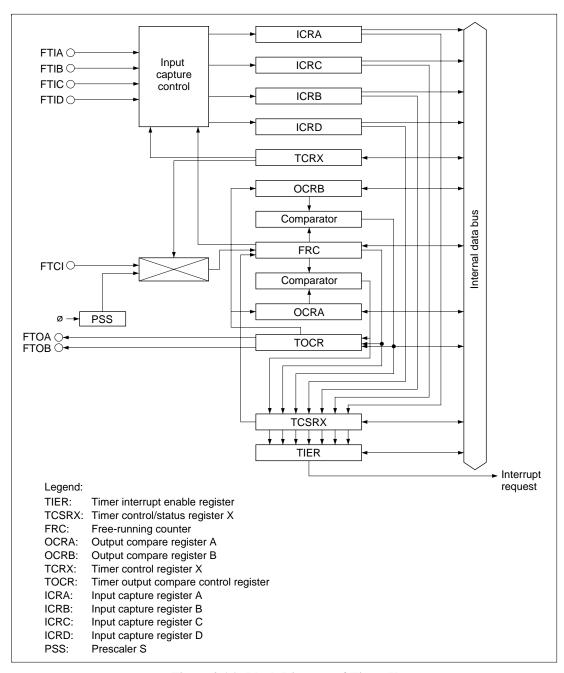

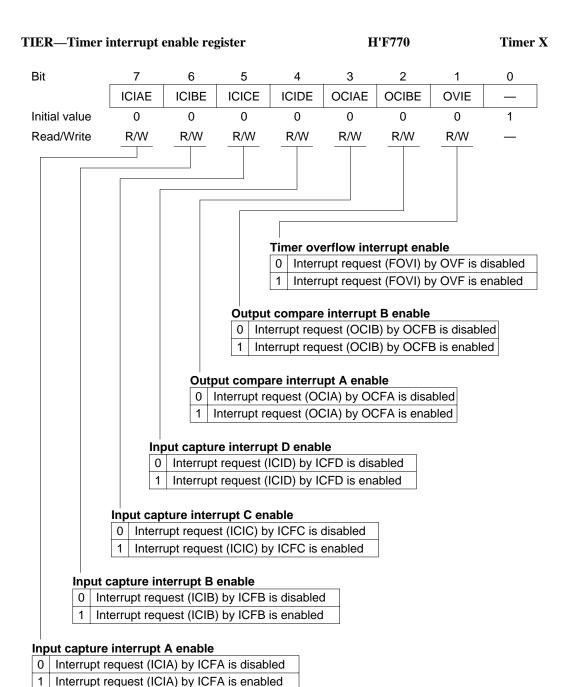

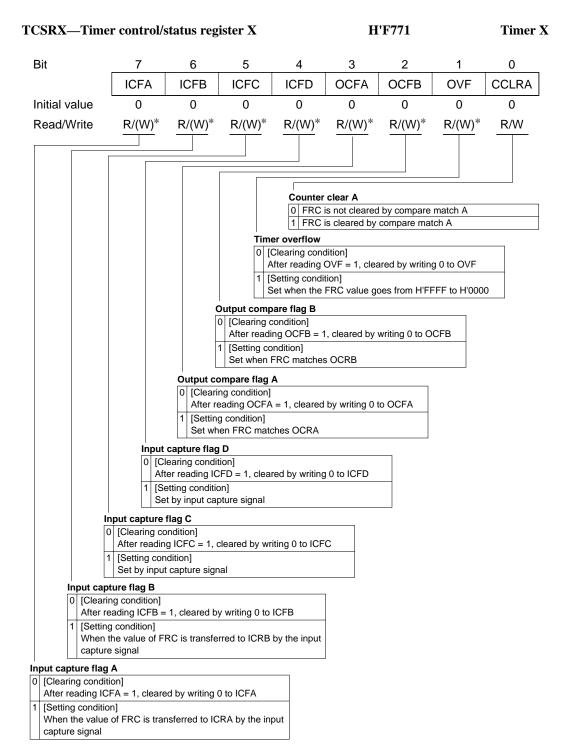

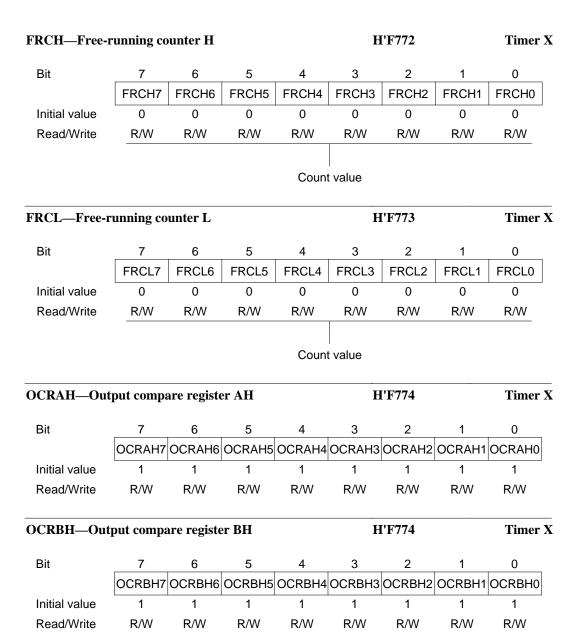

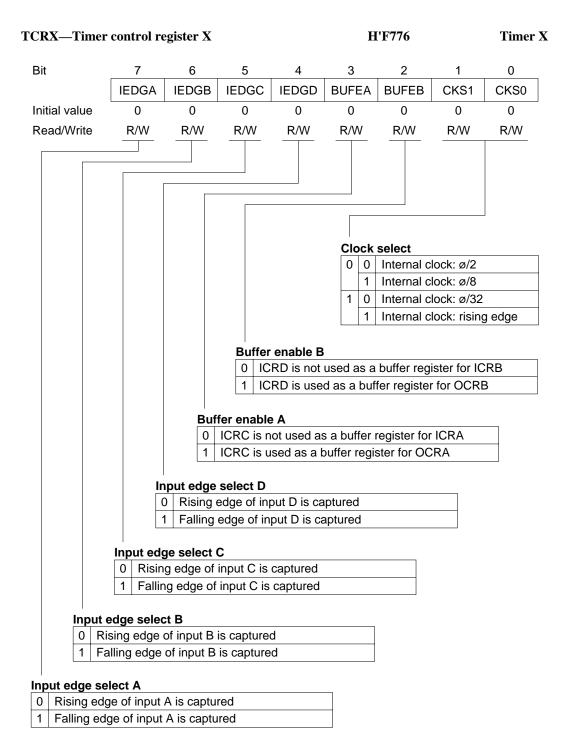

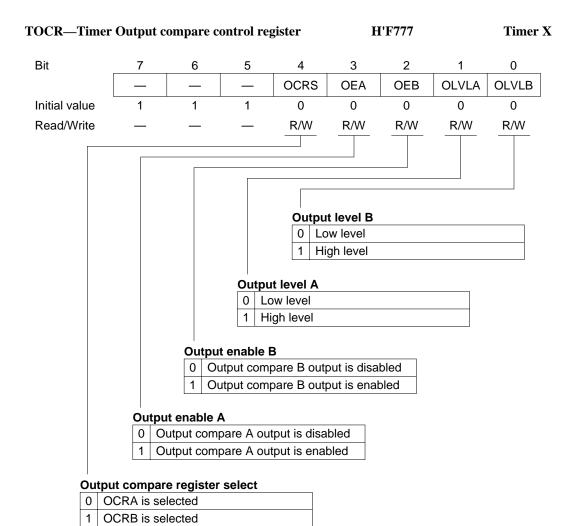

| 9.5   | Timer 2 | X                                     | 242        |

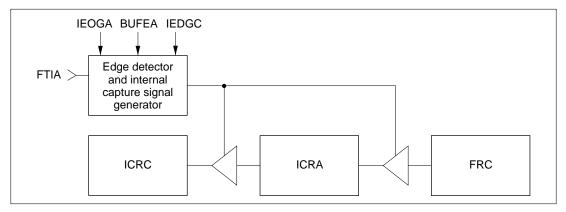

|       | 9.5.1   | Overview                              | 242        |

|       | 9.5.2   | Register Descriptions                 | 246        |

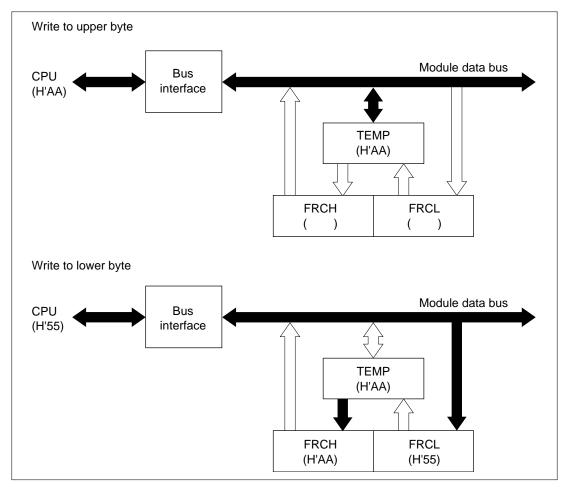

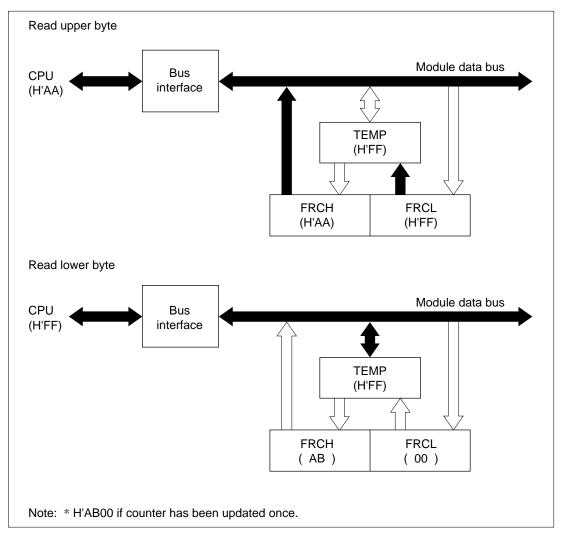

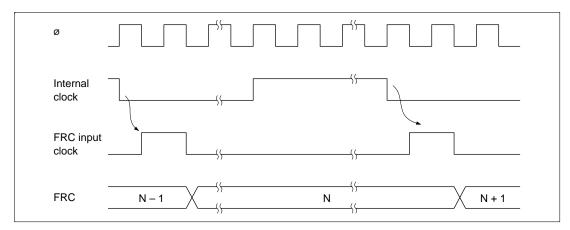

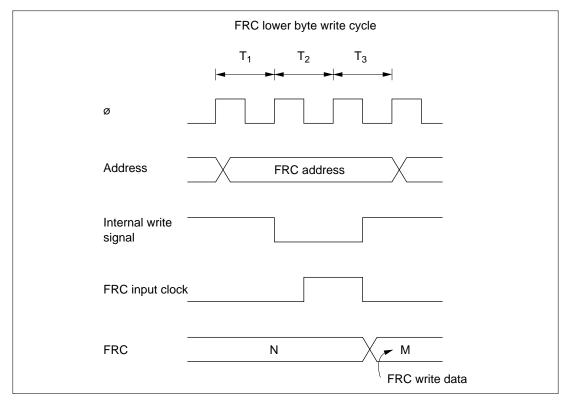

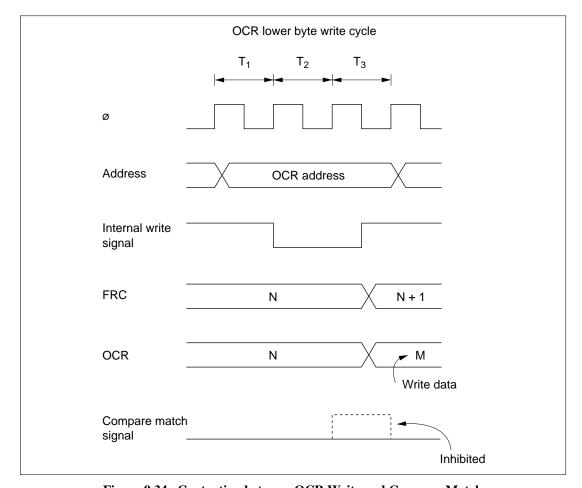

|       | 9.5.3   | CPU Interface                         | 257        |

|       | 9.5.4   | Timer Operation                       | 260        |

|       | 9.5.5   | Timer X Operation Modes               | 267        |

|       | 9.5.6   | Interrupt Sources                     | 267        |

|       | 9.5.7   | Timer X Application Example           | 268        |

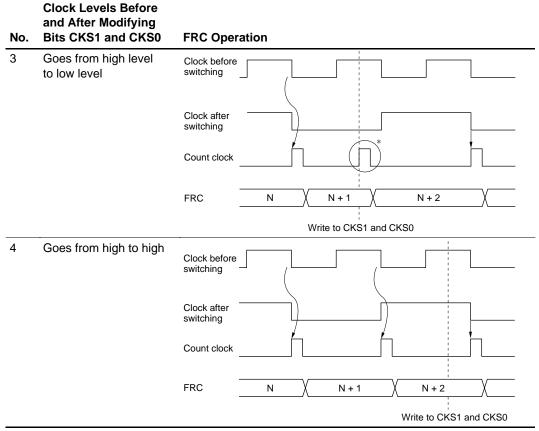

|       | 9.5.8   | Application Notes                     | 269        |

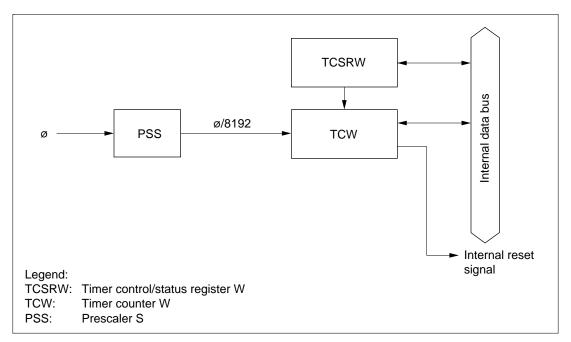

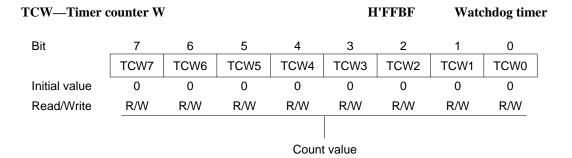

| 9.6   | Watcho  | log Timer                             | 274        |

|       | 9.6.1   | Overview                              | 274        |

|       | 9.6.2   | Register Descriptions.                | 275        |

|       | 9.6.3   | Timer Operation                       | 278        |

|       | 9.6.4   | Watchdog Timer Operation States       | 279        |

|       |         |                                       |            |

| Secti |         | Serial Communication Interface        |            |

| 10.1  |         | ew                                    |            |

| 10.2  |         |                                       |            |

|       |         | Overview                              |            |

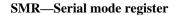

|       |         | Register Descriptions                 |            |

|       |         | Operation in Synchronous Mode         |            |

|       |         | Operation in SSB Mode                 |            |

|       |         | Interrupts                            |            |

| 10.3  |         |                                       |            |

|       |         | Overview                              |            |

|       |         | Register Descriptions                 |            |

|       |         | Operation                             |            |

|       |         | Operation in Asynchronous Mode        |            |

|       |         | Operation in Synchronous Mode         |            |

|       |         | Multiprocessor Communication Function |            |

|       |         | Interrupts                            |            |

|       | 10.3.8  | Application Notes                     | 341        |

|       |         |                                       |            |

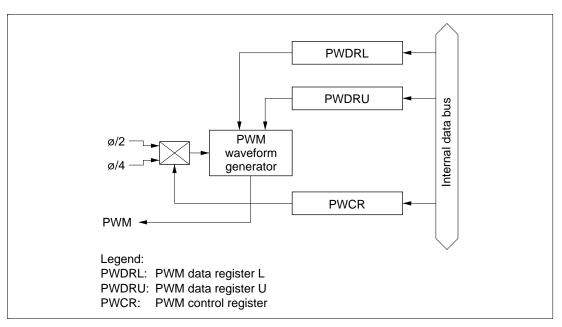

| Saat  | ion 11  | 14-Bit PWM                            | 215        |

|       |         | V                                     | 345        |

| 11.1  |         | V<br>Features                         | 345<br>345 |

|       |         |                                       |            |

|       |         | Block Diagram                         |            |

|       |         | Pin Configuration.                    |            |

|       | 11.1.4  | Register Configuration                | 340        |

| 11.2 Register Descriptions                                                 | 346 |

|----------------------------------------------------------------------------|-----|

| 11.2.1 PWM Control Register (PWCR)                                         | 346 |

| 11.2.2 PWM Data Registers U and L (PWDRU, PWDRL)                           | 347 |

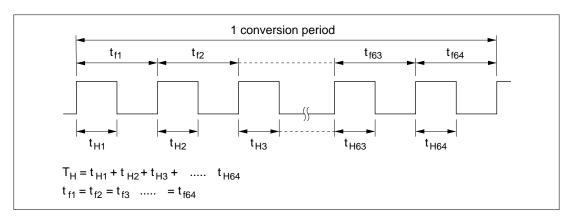

| 11.3 Operation                                                             |     |

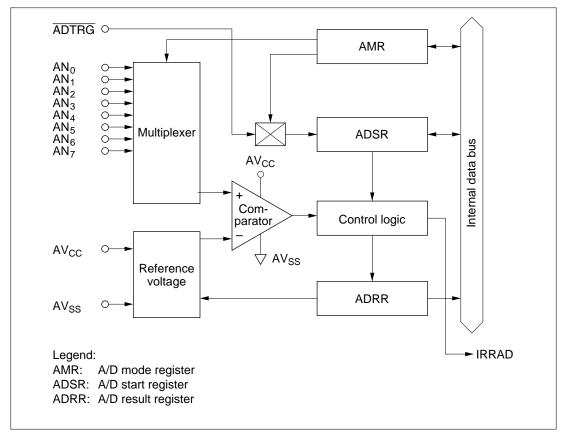

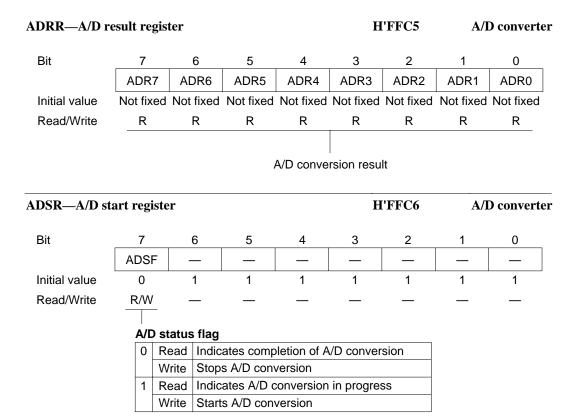

| Section 12 A/D Converter                                                   | 349 |

| 12.1 Overview                                                              |     |

| 12.1.1 Features                                                            |     |

| 12.1.2 Block Diagram                                                       |     |

| 12.1.3 Pin Configuration                                                   |     |

| 12.1.4 Register Configuration.                                             |     |

| 12.2 Register Descriptions                                                 |     |

| 12.2.1 A/D Result Register (ADRR)                                          |     |

| 12.2.2 A/D Mode Register (AMR)                                             |     |

| 12.2.3 A/D Start Register (ADSR)                                           |     |

| 12.3 Operation                                                             |     |

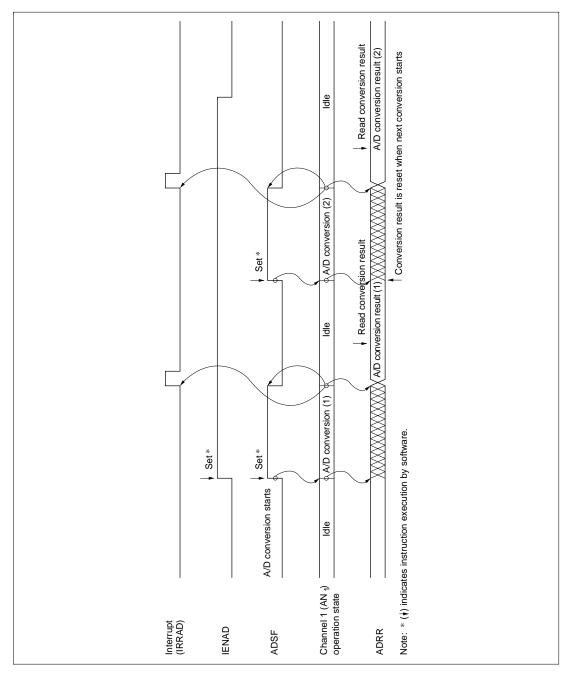

| 12.3.1 A/D Conversion Operation                                            |     |

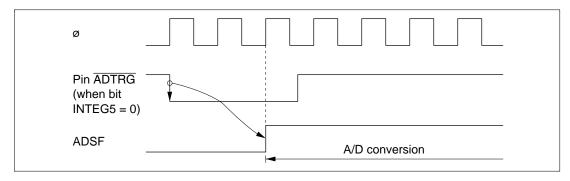

| 12.3.2 Start of A/D Conversion by External Trigger Input                   |     |

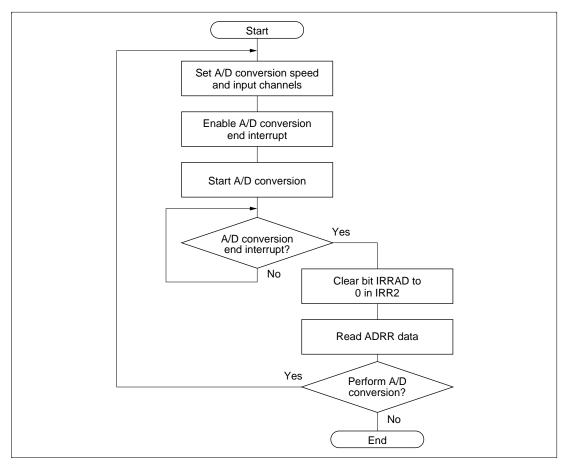

| 12.4 Interrupts                                                            |     |

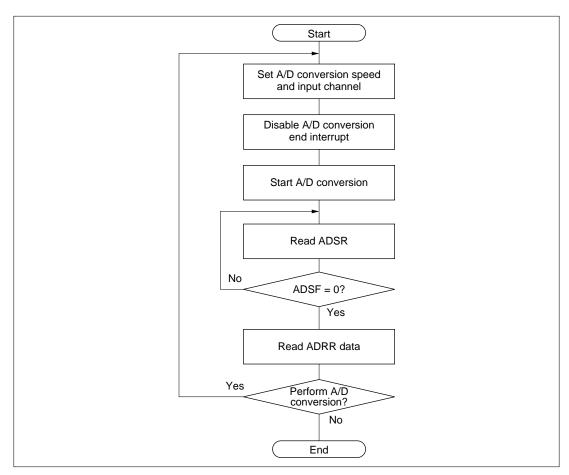

| 12.5 Typical Use                                                           | 356 |

| 12.6 Application Notes                                                     |     |

|                                                                            |     |

| Section 13 Electrical Characteristics                                      | 361 |

| 13.1 Absolute Maximum Ratings                                              | 361 |

| 13.2 Electrical Characteristics (ZTAT <sup>TM</sup> , Mask ROM Version)    | 362 |

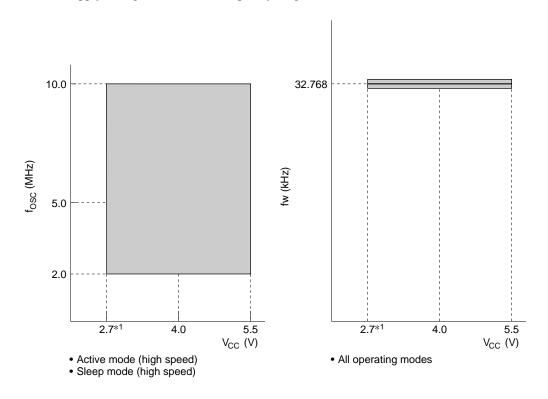

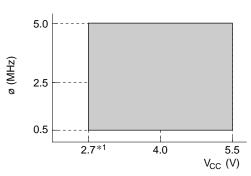

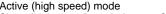

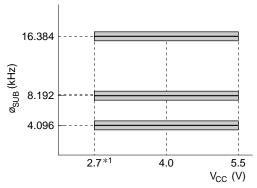

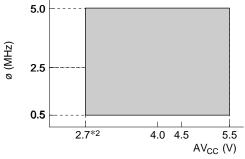

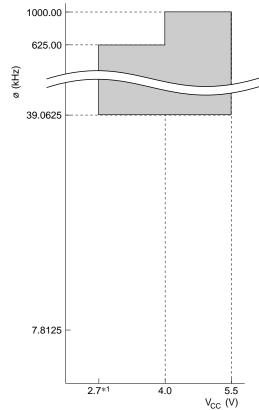

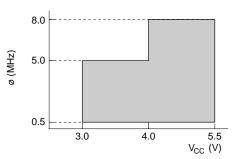

| 13.2.1 Power Supply Voltage and Operating Range                            | 362 |

| 13.2.2 DC Characteristics (HD6473644)                                      | 365 |

| 13.2.3 AC Characteristics (HD6473644)                                      | 371 |

| 13.2.4 DC Characteristics (HD6433644, HD6433643, HD6433642, HD6433641,     |     |

| HD6433640)                                                                 | 374 |

| 13.2.5 AC Characteristics (HD6433644, HD6433643, HD6433642, HD6433641,     |     |

| HD6433640)                                                                 | 379 |

| 13.2.6 A/D Converter Characteristics                                       | 383 |

| 13.3 Electrical Characteristics (ZTAT and R of the Mask ROM version)       |     |

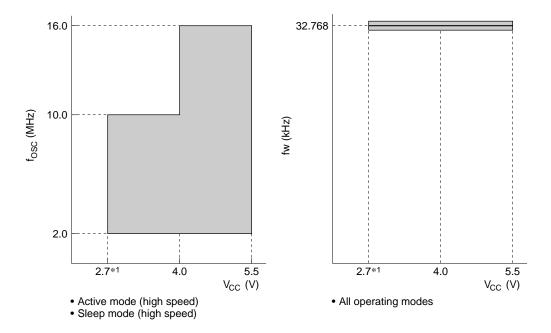

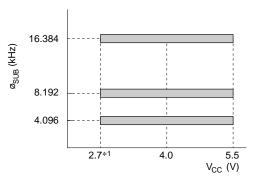

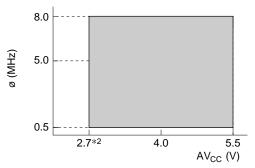

| 13.3.1 Power Supply Voltage and Operating Range                            | 384 |

| 13.3.2 DC Characteristics (HD6473644R)                                     | 387 |

| 13.3.3 AC Characteristics (HD6473644R)                                     | 393 |

| 13.3.4 DC Characteristics (HD6433644R, HD6433643R, HD6433642R, HD6433641R, |     |

| HD6433640R)                                                                | 396 |

| 13.3.5 AC Characteristics (HD6433644R, HD6433643R, HD6433642R, HD6433641R, |     |

| HD6433640R)                                                                |     |

| 13.3.6 A/D Converter Characteristics                                       |     |

| 13.4 Electrical Characteristics (F-ZTAT <sup>TM</sup> version)             |     |

vii

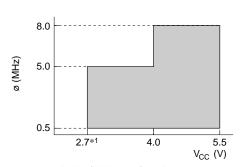

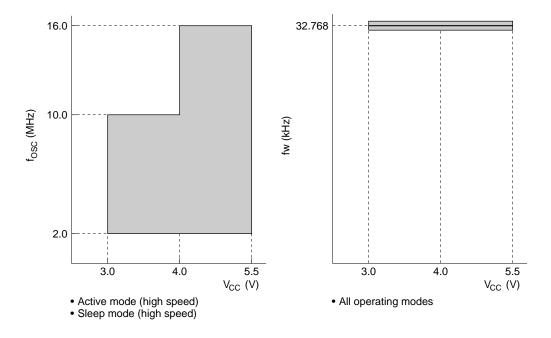

| 13.4.1 Power Supply Voltage and Operating Range              | 406 |

|--------------------------------------------------------------|-----|

| 13.4.2 DC Characteristics (HD64F3644, HD64F3643, HD64F3642A) | 409 |

| 13.4.3 AC Characteristics (HD64F3644, HD64F3643, HD64F3642A) | 415 |

| 13.4.4 A/D Converter Characteristics                         | 418 |

| 13.5 Operation Timing                                        | 419 |

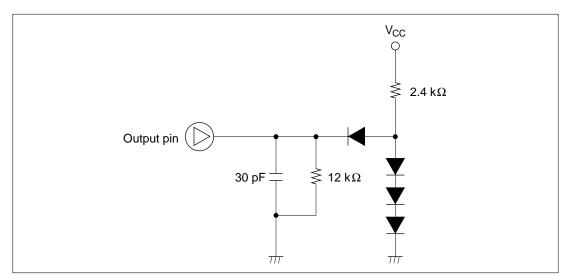

| 13.6 Output Load Circuit                                     | 422 |

| Appendix A CPU Instruction Set                               | 423 |

| A.1 Instructions                                             | 423 |

| A.2 Operation Code Map                                       | 430 |

| A.3 Number of Execution States                               | 433 |

| Appendix B Internal I/O Registers                            | 441 |

| B.1 Addresses                                                |     |

| B.2 Functions                                                | 445 |

| Appendix C I/O Port Block Diagrams                           | 493 |

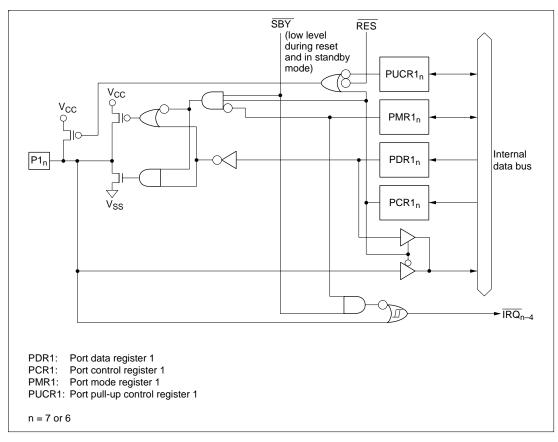

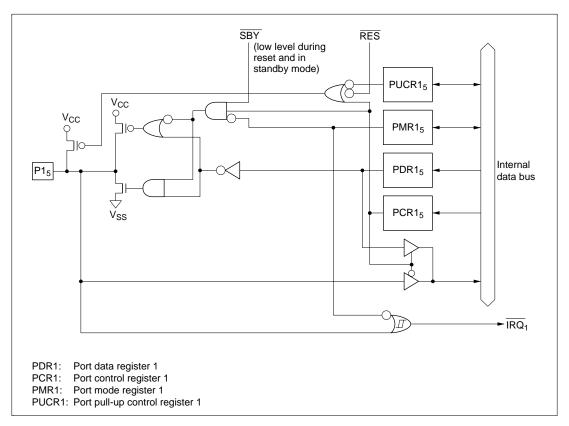

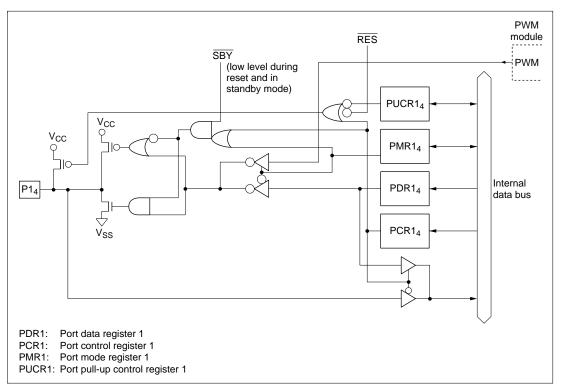

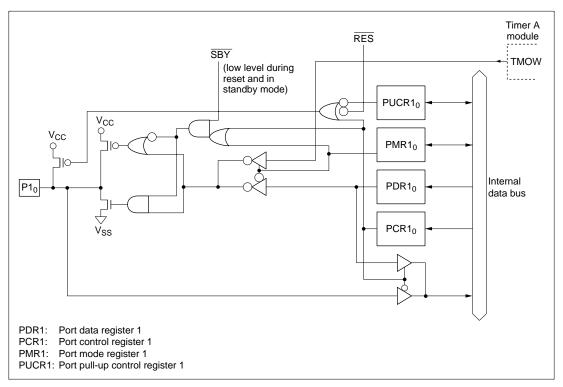

| C.1 Block Diagrams of Port 1                                 | 493 |

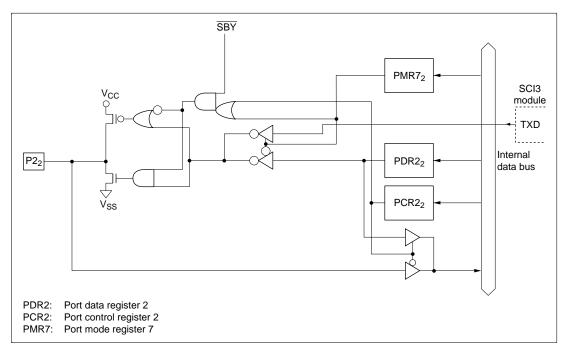

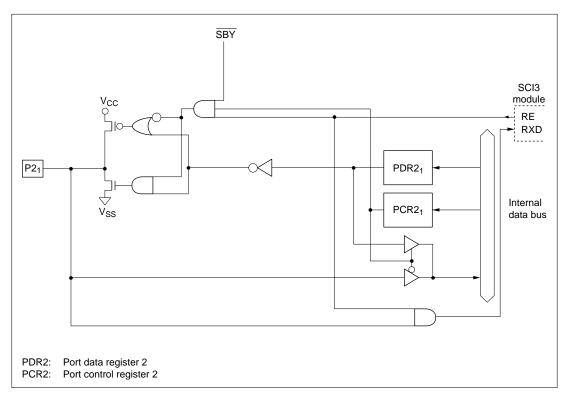

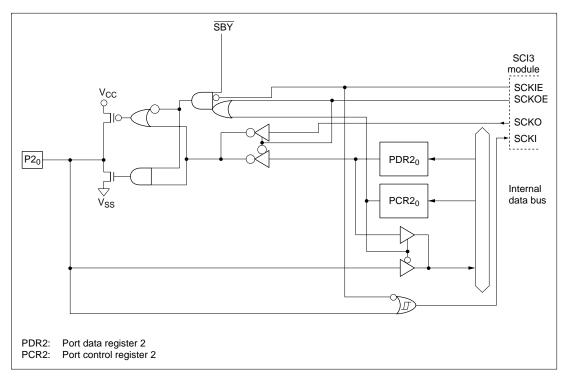

| C.2 Block Diagrams of Port 2                                 | 497 |

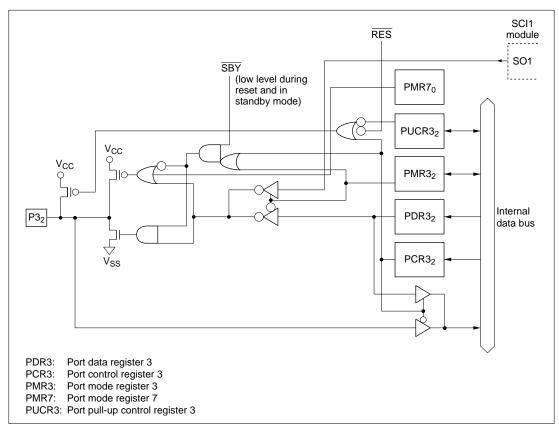

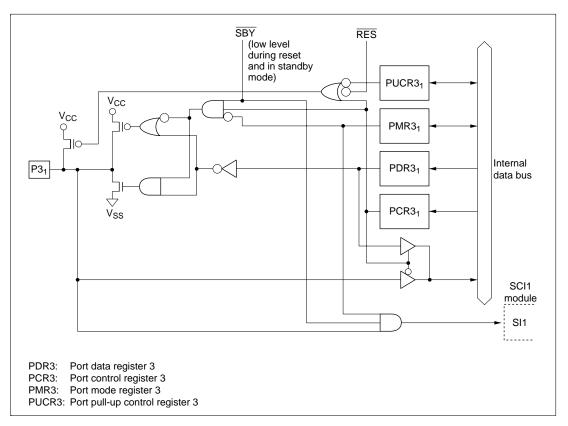

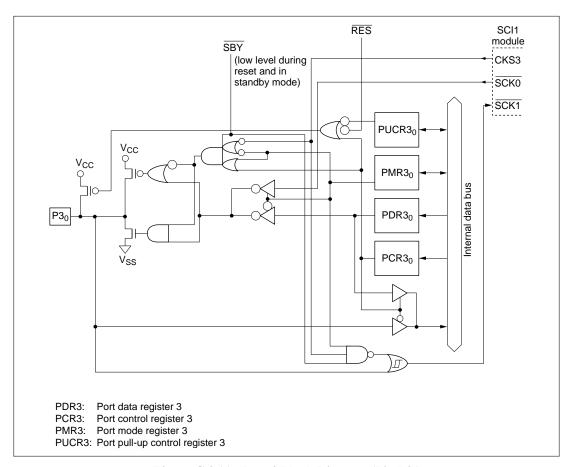

| C.3 Block Diagrams of Port 3                                 | 500 |

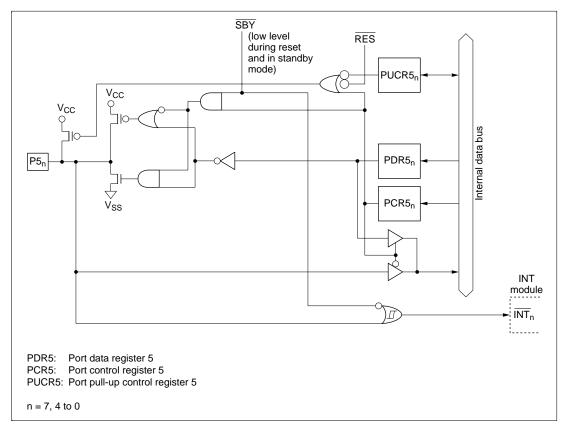

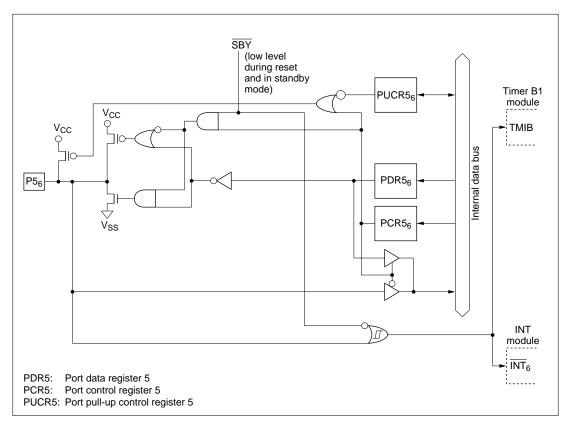

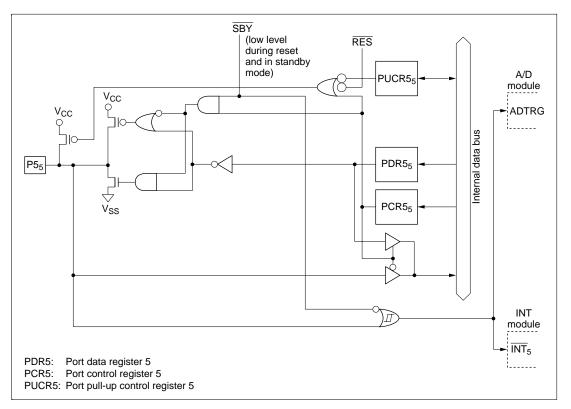

| C.4 Block Diagrams of Port 5                                 | 503 |

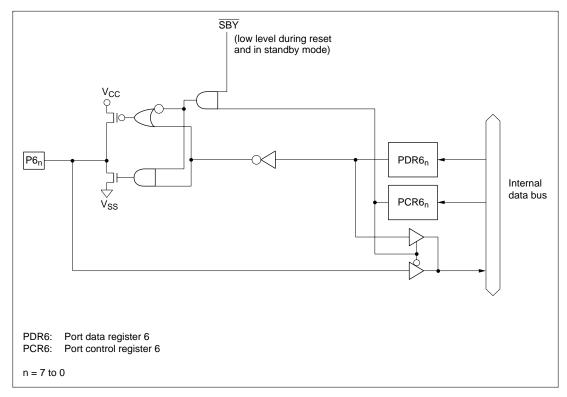

| C.5 Block Diagram of Port 6                                  | 506 |

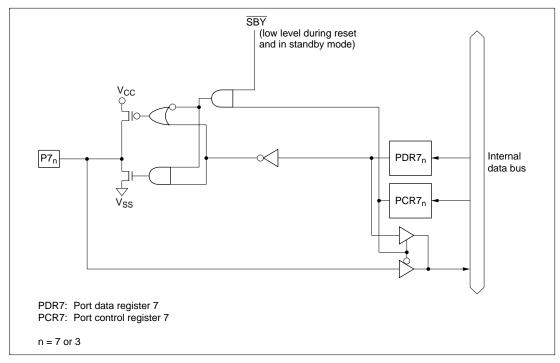

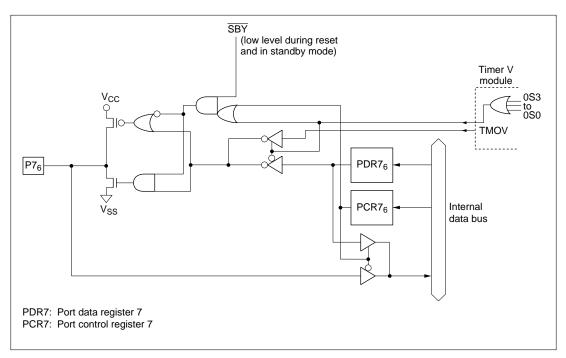

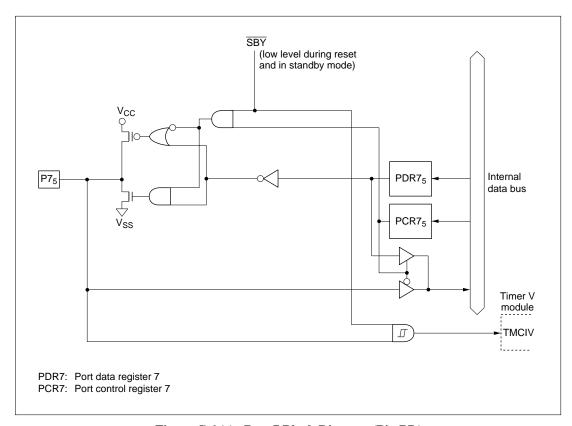

| C.6 Block Diagrams of Port 7                                 | 507 |

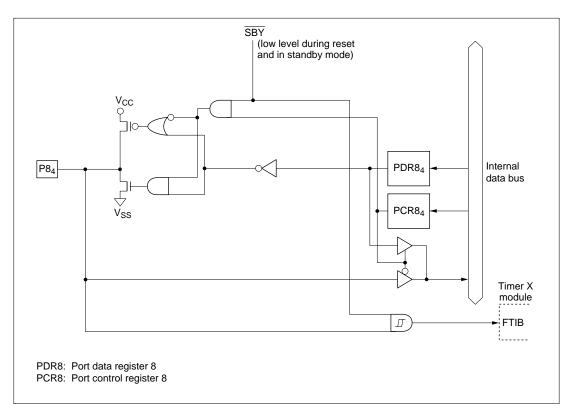

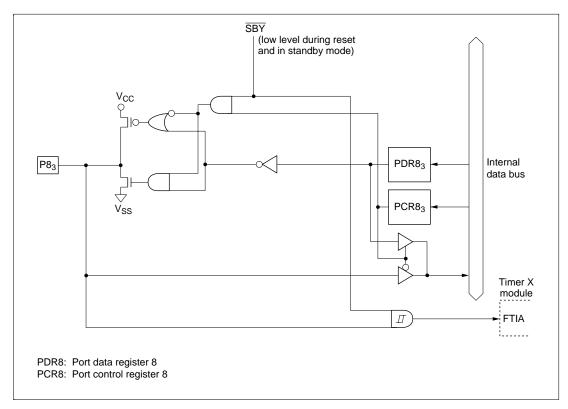

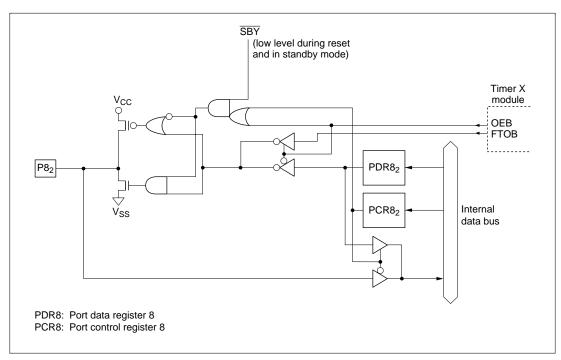

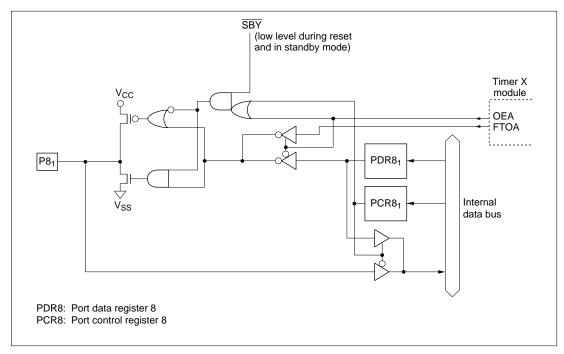

| C.7 Block Diagrams of Port 8                                 | 511 |

| C.8 Block Diagram of Port 9                                  | 519 |

| C.9 Block Diagram of Port B                                  | 520 |

| Appendix D Port States in the Different Processing States    | 521 |

| Appendix E Product Code Lineup                               | 523 |

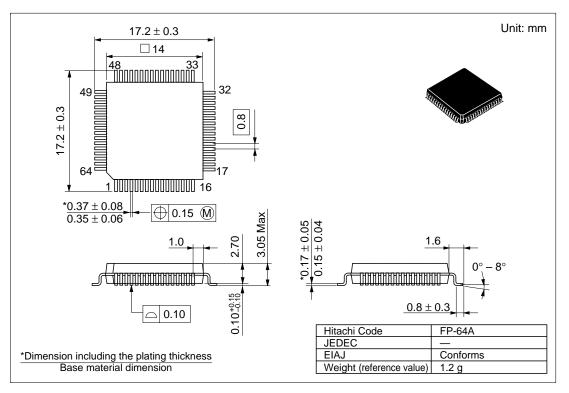

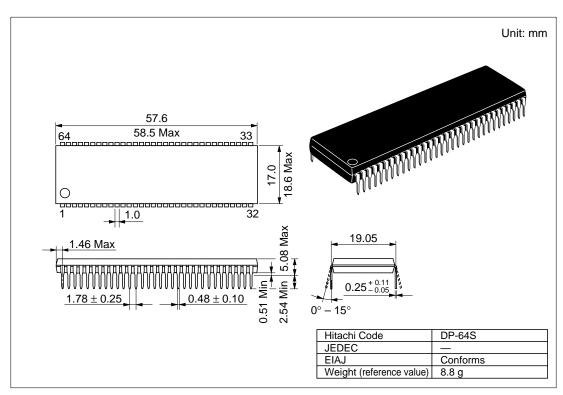

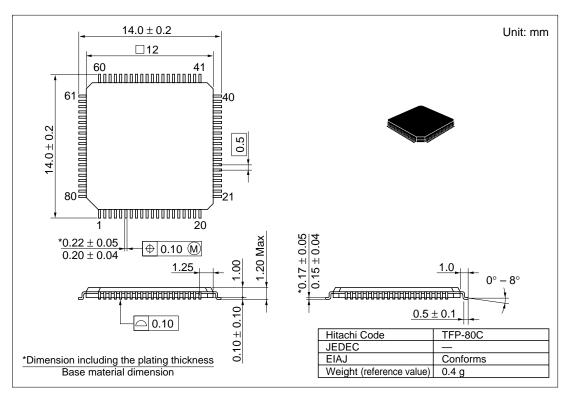

| Appendix F. Package Dimensions                               | 525 |

# Section 1 Overview

#### 1.1 Overview

The H8/300L Series is a series of single-chip microcomputers (MCU: microcomputer unit), built around the high-speed H8/300L CPU and equipped with peripheral system functions on-chip.

Within the H8/300L Series, the H8/3644 Series of microcomputers are equipped with a UART (Universal Asynchronous Receiver/Transmitter). Other on-chip peripheral functions include five timers, a 14-bit pulse width modulator (PWM), two serial communication interface channels, and an A/D converter, providing an ideal configuration as a microcomputer for embedding in high-level control systems. In addition to the mask ROM version, the H8/3644 is also available in a ZTAT<sup>TM\*1</sup> version with on-chip user-programmable PROM, and an F-ZTAT<sup>TM\*2</sup> version with on-chip flash memory that can be programmed on-board. Table 1 summarizes the features of the H8/3644 Series.

Notes: 1. ZTAT is a trademark of Hitachi, Ltd.

2. F-ZTAT is a registered trademark of Hitachi, Ltd.

**Table 1.1** Features

| Item             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| CPU              | High-speed H8/300L CPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|                  | General-register architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|                  | General registers: Sixteen 8-bit registers (can be used as eight 16-bit registers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|                  | Operating speed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|                  | <ul> <li>Max. operation speed: 5 MHz (mask ROM and ZTAT versions)</li> <li>8 MHz (Applies only to F-ZTAT, R of the ZTAT, and R of the mask ROM version)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|                  | <ul> <li>— Add/subtract: 0.4 μs (operating at Ø = 5 MHz)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|                  | 0.25 $\mu$ s (operating at $\emptyset = 8$ MHz)* <sup>1</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|                  | <ul> <li>— Multiply/divide: 2.8 μs (operating at Ø = 5 MHz)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|                  | 1.75 $\mu$ s (operating at $\emptyset = 8$ MHz)* <sup>1</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|                  | <ul> <li>Can run on 32.768 kHz subclock</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|                  | <ul> <li>Instruction set compatible with H8/300 CPU</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|                  | <ul> <li>Instruction length of 2 bytes or 4 bytes</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|                  | <ul> <li>Basic arithmetic operations between registers</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|                  | <ul> <li>MOV instruction for data transfer between memory and registers</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|                  | Typical instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|                  | — Multiply (8 bits × 8 bits)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|                  | — Divide (16 bits ÷ 8 bits)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|                  | Bit accumulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| -                | Register-indirect designation of bit position                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

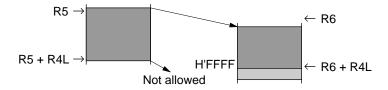

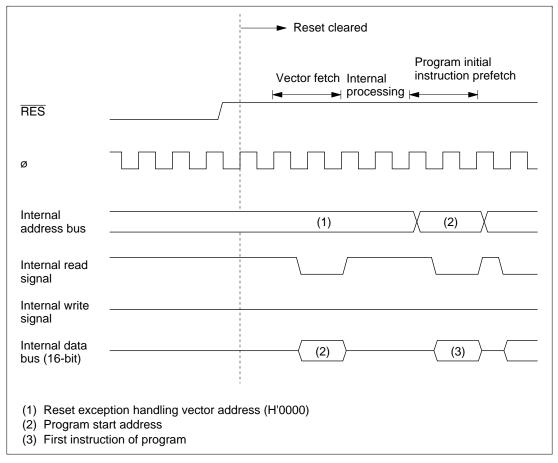

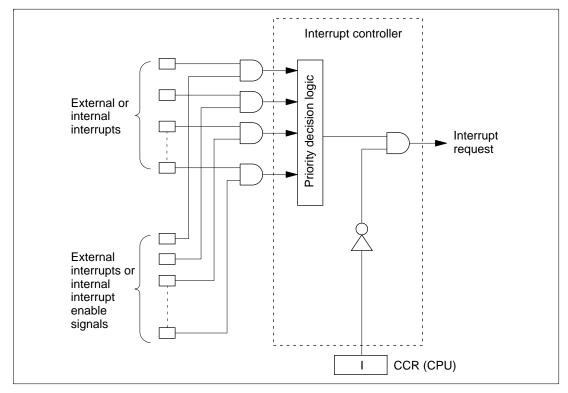

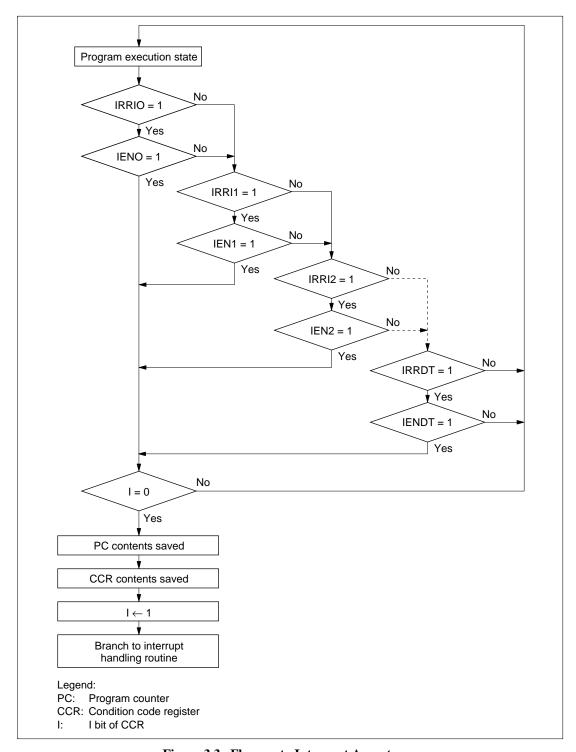

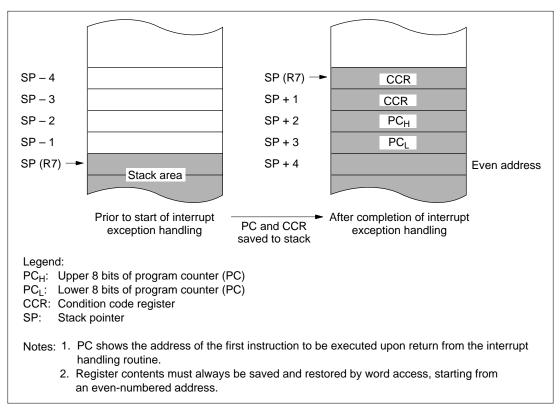

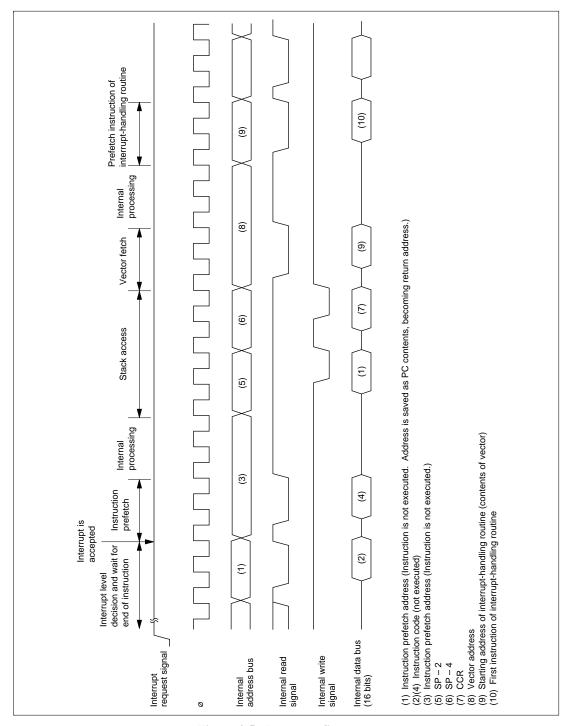

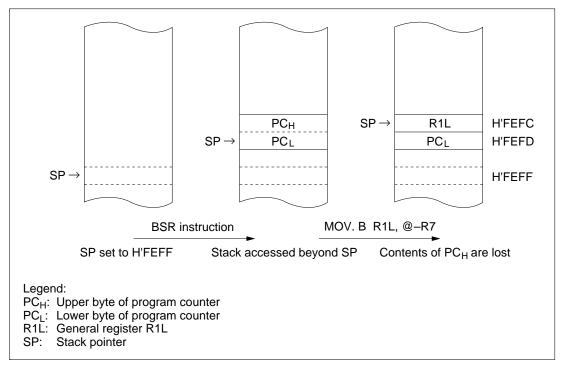

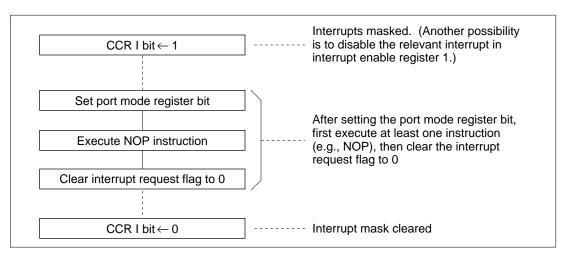

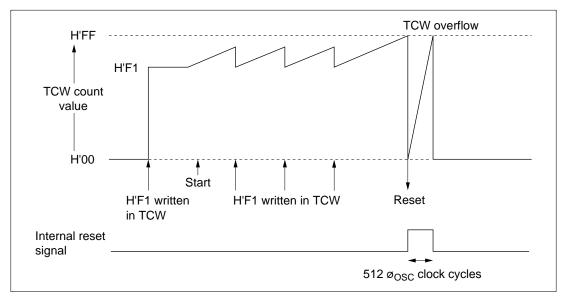

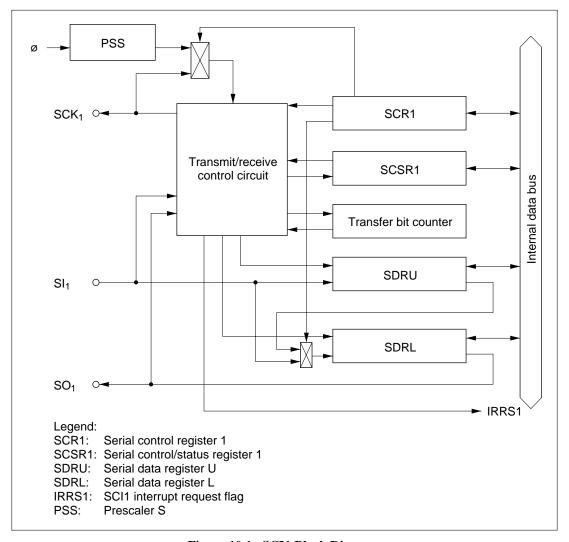

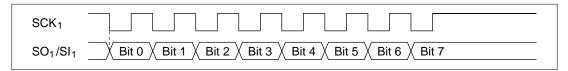

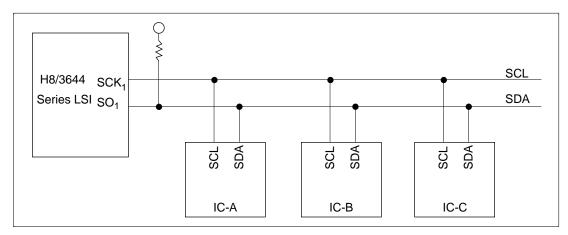

| Interrupts       | 33 interrupt sources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |