# **OKI** Semiconductor

This version: Jan. 1998 Previous version: May. 1997

# **MSM63V89C**

1,048,576-Word x 1-Bit Solid-State Recorder Data Register

#### **GENERAL DESCRIPTION**

The MSM63V89C is a solid-state recorder data register in 1,048,576 words x 1 bit configuration.

The MSM63V89C has a built-in internal address generator circuit allowing continuous serial read/write operation by single external clock input. The internal address is automatically incremented by one by read/write operation.

Address designation in units of 1024 words in the direction of words is possible by an external serial address input.

The built-in refresh timer and refresh counter have eliminated the need of an external refresh circuit and realized a low power consumption.

26/20-pin plastic TSOP is used as the package and the operating temperature range is between  $0^{\circ}$ C and  $70^{\circ}$ C.

The MSM63V89C is suitable for storing large capacity data with battery backup. A solid state recording and playback system can easily be constructed in combination with OKI's voice synthesizer ICs.

#### **FEATURES**

• Configuration: 1,048,576 x 1 bit

• Serial access operation:

Serial access time 1.5µs (3.0µs) Serial read/write cycle time 2.0µs (4.0µs) Fast mode read/write cycle time 0.4µs (0.4µs)

Times in parentheses indicate ones in self-refresh mode.

• Low current consumption: 50  $\mu$ A max. (for data holding,  $V_{CC}$ =3.0 V)

• Wide operating supply voltage range: Single 2.7 to 3.6V

• Auto-refresh/self-refresh changeable

• Package:

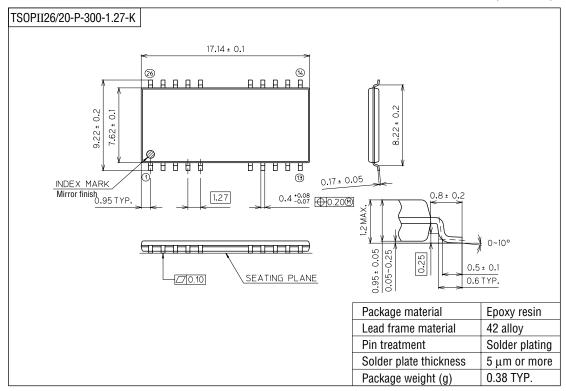

26/20-pin plastic TSOP (TSOPII26/20-P-300-1.27-K) (Product name: MSM63V89CTS-K)

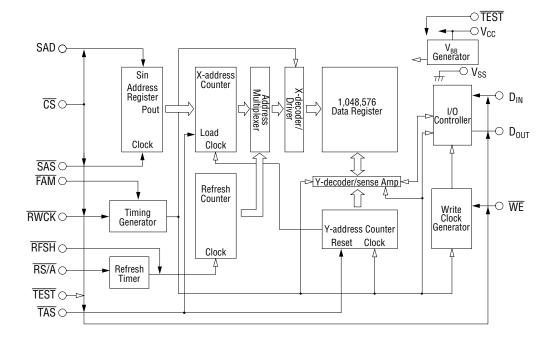

### **BLOCK DIAGRAM**

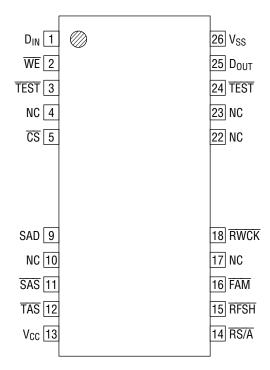

# **PIN CONFIGURATION (TOP VIEW)**

NC: No connection

26/20-pin plastic TSOP

## **PIN DESCRIPTIONS**

| Pin   | Symbol           | Description                      |

|-------|------------------|----------------------------------|

| 1     | D <sub>IN</sub>  | Data input                       |

| 2     | WE               | Write enable                     |

| 3, 24 | TEST             | Test input                       |

| 5     | <del>CS</del>    | Chip select                      |

| 9     | SAD              | Serial address data              |

| 11    | SAS              | Serial address strobe            |

| 12    | TAS              | Transfer address strobe          |

| 13    | V <sub>CC</sub>  | Power supply (3.3 V)             |

| 14    | RS/A             | Auto-Refresh/Self-Refresh Select |

| 15    | RFSH             | Refresh Clock Input              |

| 16    | FAM              | Fast Access Mode Select          |

| 18    | RWCK             | Read/write clock                 |

| 25    | D <sub>OUT</sub> | Data output                      |

| 26    | $V_{SS}$         | Ground (0 V)                     |

## **ABSOLUTE MAXIMUM RATINGS**

| Parameter                    | Symbol           | Condition                              | Rating       | Unit |

|------------------------------|------------------|----------------------------------------|--------------|------|

| Terminal Voltage             | V <sub>T</sub>   | Ta = 25°C, relative to V <sub>SS</sub> | -1.0 to +7.0 | V    |

| Output Short-Circuit Current | I <sub>0S</sub>  | Ta = 25°C                              | 50           | mA   |

| Power Dissipation            | P <sub>D</sub>   | Ta = 25°C                              | 1            | W    |

| Operating Temperature        | T <sub>op</sub>  | _                                      | 0 to 70      | °C   |

| Storage Temperature          | T <sub>STG</sub> | _                                      | −55 to +150  | °C   |

## RECOMMENDED OPERATING CONDITIONS

$(Ta = 0 \text{ to } 70^{\circ}C)$

| Parameter         | Symbol          | Min.                  | Тур.            | Max.                  | Unit |

|-------------------|-----------------|-----------------------|-----------------|-----------------------|------|

| Supply Voltage    | V <sub>CC</sub> | 2.7                   | 3.3             | 3.6                   | V    |

| Supply Voltage    | V <sub>SS</sub> | 0                     | 0               | 0                     | V    |

| "H" Input Voltage | V <sub>IH</sub> | V <sub>CC</sub> - 0.5 | V <sub>CC</sub> | V <sub>CC</sub> + 0.5 | V    |

| "L" Input Voltage | V <sub>IL</sub> | -0.5                  | 0               | +0.5                  | V    |

## **ELECTRICAL CHARACTERISTICS**

#### **DC** Characteristics

$(V_{CC} = 2.7 \text{ V to } 3.6 \text{ V}, \text{ Ta} = 0 \text{ to } 70^{\circ}\text{C})$

|                                     |                  |                                                    |                       |     | ,    |

|-------------------------------------|------------------|----------------------------------------------------|-----------------------|-----|------|

| Parameter                           | Symbol           | Condition                                          | Min. Max.             |     | Unit |

| "H" Output Voltage                  | $V_{OH}$         | $I_{OH} = -0.5 \text{ mA}$                         | V <sub>CC</sub> - 0.5 | _   | V    |

| "L" Output Voltage                  | $V_{OL}$         | I <sub>OL</sub> = 0.5 mA                           | _                     | 0.4 | V    |

| Input Leakage Current               | ILI              | $V_I = 0 V \text{ to } V_{CC}$                     | -1                    | +1  | μΑ   |

| Output Leakage Current              | I <sub>LO</sub>  | $V_0 = 0 \text{ V to } V_{CC}$                     | -1                    | +1  | μΑ   |

| Supply Current (in operating state) | I <sub>CC1</sub> | $V_{CC} = 3 \text{ V}, t_{RWC} = 2 \mu \text{s}$   | _                     | 3   | mA   |

| Supply Current (in standby state)   | I <sub>CC2</sub> | V <sub>CC</sub> = 3 V                              | _                     | 50  | μΑ   |

| Supply Current (FAM)                | I <sub>CC3</sub> | $V_{CC} = 3 \text{ V}, t_{RWC} = 0.4 \mu \text{s}$ | _                     | 10  | mA   |

## **AC Characteristics**

$(V_{CC} = 2.7 \text{ V to } 3.6 \text{ V}, Ta = 0 \text{ to } 70^{\circ}\text{C})$

|                             |                  | MSM63V89C-SELF |         | MSM63V89C-AUTO |         | Unit |

|-----------------------------|------------------|----------------|---------|----------------|---------|------|

| Parameter                   | Symbol           | Min. Max.      |         | Min. Max.      |         |      |

| Refresh Cycle               | t <sub>REF</sub> | _              | _       | _              | 100     | ms   |

| Read/Write Cycle Time       | t <sub>RWC</sub> | 4,000          | _       | 2,000          | _       | ns   |

| Access Time                 | t <sub>ACC</sub> | _              | 3,000   | _              | 1,500   | ns   |

| Output Turn-off Delay Time  | t <sub>OFF</sub> | 0              | 50      | 0              | 50      | ns   |

| Input Signal Rise/Fall Time | t <sub>T</sub>   | 3              | 50      | 3              | 50      | ns   |

| RWCK Precharge Time         | t <sub>RWP</sub> | 1,000          | _       | 500            | _       | ns   |

| RWCK Pulse Width            | t <sub>RW</sub>  | 3,000          | 10,000  | 1,500          | 10,000  | ns   |

| SAS Cycle Time              | t <sub>SSC</sub> | 100            | _       | 100            | _       | ns   |

| SAS Pulse Width             | t <sub>SAS</sub> | 50             | _       | 50             | _       | ns   |

| SAS Precharge Time          | t <sub>SAP</sub> | 50             | _       | 50             | _       | ns   |

| Address Setup Time          | t <sub>AS</sub>  | 0              | _       | 0              | _       | ns   |

| Address Hold Time           | t <sub>AH</sub>  | 50             | _       | 50             | _       | ns   |

| TAS Setup Time              | t <sub>ATS</sub> | 50             | _       | 50             | _       | ns   |

| TAS to RWCK Setup Time      | t <sub>TRS</sub> | 50             | _       | 50             | _       | ns   |

| TAS Pulse Width             | t <sub>TAS</sub> | 50             | _       | 50             | _       | ns   |

| Read Command Setup Time     | t <sub>RRS</sub> | 0              | _       | 0              | _       | ns   |

| Read Command Hold Time      | t <sub>RRH</sub> | 50             | _       | 50             | _       | ns   |

| Write Command Setup Time    | t <sub>WRS</sub> | 0              | _       | 0              | _       | ns   |

| Write Command Hold Time     | t <sub>WRH</sub> | 50             | _       | 50             | _       | ns   |

| Write Command Pulse Width   | t <sub>WP</sub>  | 50             | _       | 50             | _       | ns   |

| WE to RWCK Lead Time        | t <sub>RWL</sub> | 50             | _       | 50             | _       | ns   |

| Data Setup Time             | t <sub>DS</sub>  | 0              | _       | 0              | _       | ns   |

| Data Hold Time              | t <sub>DH</sub>  | 50             | _       | 50             | _       | ns   |

| RWCK to WE Delay Time       | t <sub>RWD</sub> | 100            | _       | 100            | _       | ns   |

| RFSH Setup Time             | t <sub>RFS</sub> | _              | _       | 500            | _       | ns   |

| RFSH Precharge Time         | t <sub>RFP</sub> | _              | _       | 500            | _       | ns   |

| RFSH Pulse Width            | t <sub>RF</sub>  | _              | _       | 1,500          | 10,000  | ns   |

| RFSH RWCK Precharge Time    | t <sub>RRP</sub> | _              | _       | 500            | _       | ns   |

| Fast Mode Cycle Time        | t <sub>FC</sub>  | 400            | _       | 400            | _       | ns   |

| Fast RWCK Mode Access Time  | t <sub>FAC</sub> | _              | 300     | _              | 300     | ns   |

| Fast RWCK Precharge Time    | t <sub>FCP</sub> | 100            | _       | 100            | _       | ns   |

| Fast Mode RWCK Pulse Width  | t <sub>FR</sub>  | 300            | _       | 300            | _       | ns   |

| Fast Mode Setup Time        | t <sub>FS</sub>  | 0              | _       | 0              | _       | ns   |

| Fast Mode Hold Time         | t <sub>FH</sub>  | 50             | _       | 50             | _       | ns   |

| Fast Mode Width             | t <sub>FCC</sub> | 4,000          | 100,000 | 2,000          | 100,000 | ns   |

| Slow Mode Setup Time        | t <sub>SS</sub>  | 0              | _       | 0              | _       | ns   |

| Slow Mode Hold Time         | t <sub>SH</sub>  | 50             | _       | 50             | _       | ns   |

Note: Switching to the fast mode should be made satisfying the timings of  $t_{FS}$  and  $t_{SS}$  at the "L" level of  $\overline{RWCK}$ .

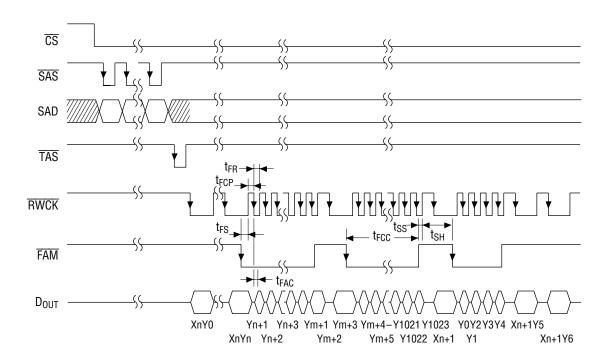

## **TIMING DIAGRAMS**

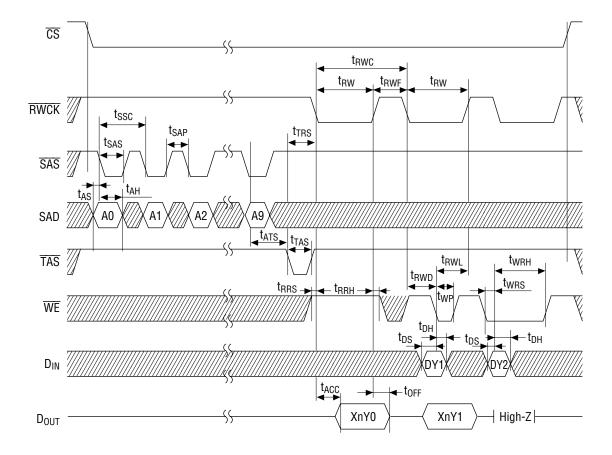

# Read/Write/Read Modify Write Cycle

#### **Auto-Refresh Mode**

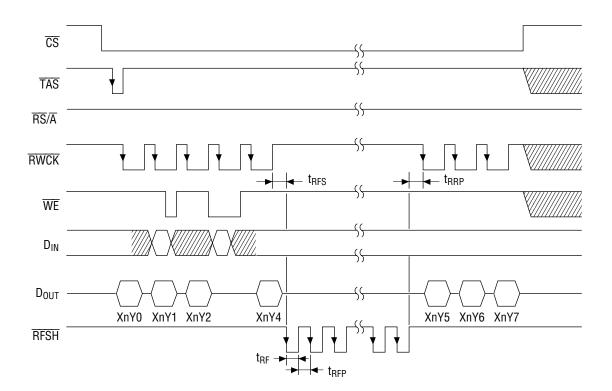

### **Fast Access Mode**

#### **FUNCTIONAL DESCRIPTION**

#### Serial Address Input (SAD)

Pin for inputting the start address for read/write. Address data can be input in units of 1024 words. The 1,024 address data can be input as 10-bit (A0-A9) serial from the SAD pin.

## Serial Address Strobe (SAS)

Pin for the clock used to store the serial address data into the internal register.

#### Address Transfer Strobe (TAS)

Input pin for setting the serial address data stored in the address register to the internal address counter.

When the  $\overline{TAS}$  falls, the Y address is set to address 0.

### Read/Write Clock (RWCK)

Input pin for the data register information read/write clock.

Internal operation starts at the falling edge of  $\overline{RWCK}$ . The information in the data register is output to the DOUT pin in the read mode, and the information at the DIN pin is written into the data register in the write mode. The internal address counter is automatically incremented when  $\overline{RWCK}$  falls.

#### Write Enable (WE)

Input pin for selecting the read mode, write mode or read modify write mode.

The read mode is set when  $\overline{WE}$  is "H", and the write mode is set when  $\overline{WE}$  is "L". When  $\overline{WE}$  falls from "H" to "L" while  $\overline{RWCK}$  is active, the read modify write mode is set.

#### Data Input (D<sub>IN</sub>)

Input pin for write data.

The information at the data input pin is stored at the falling edge of  $\overline{RWCK}$  in the write mode, and at the falling edge of  $\overline{WE}$  in the read modify write mode.

#### Data Output (D<sub>OUT</sub>)

The data output pin is always kept in the high impedance state when  $\overline{RWCK}$  or  $\overline{CS}$  is kept at "H". When "H" or "L" information is read in the read operation, the output pin is set to "H" to "L" and holds the read information until  $\overline{RWCK}$  is again set to "H". In the early write mode the output pin maintains the high impedance state, so I/O common operation by connecting  $D_{IN}$  and  $D_{OUT}$  is possible.

#### Self/Auto Refresh Select (RS/A)

Pin for selecting a refresh mode in order to retain memory cell data.

If the  $\overline{RS/A}$  pin is set to "L" level, the self-refresh mode is selected and no external refresh control is required. If the  $\overline{RS/A}$  pin is set to "H" level, the auto-refresh mode is selected and refresh operation is required to retain memory cell data.

#### Refresh Clock Input (RFSH)

Input pin for controlling the external refresh when the auto refresh mode is selected. When the autorefresh mode is selected, 1024 refresh operations are required within 100ms via the  $\overline{RFSH}$  pin while the  $\overline{RWCK}$  is at "H" level.

## Fast Access Mode Select (FAM)

Pin for fast read/write operations. Fast read/write is possible by keeping the  $\overline{FAM}$  pin at "L" level. The fast access mode is set or released by inputting "L" level or "H" level to the  $\overline{FAM}$  pin when the  $\overline{RWCK}$  pin is at "L" level, and when  $t_{FS}$  and  $t_{SS}$  are satisfied.

When 1024-word data access is complete, be sure to insert a normal cycle in order to increment the X address.

## Chip Select (CS)

Input pin for disabling all input and output pins. This pin enables parallel use of multiple MSM63V89Cs by connecting the data input and output pins.

#### Test (TEST)

The TEST pin is fixed to "H" level.

### **Turning the power ON**

To stabilize the device, it is required to pause for over 100 $\mu$ s after the V<sub>CC</sub> reaches the specified voltage. Then it is needed to add eight or more  $\overline{RWCK}$  cycles (read cycles or pseudo data write cycles).

## **PACKAGE DIMENSIONS**

(Unit: mm)

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, SOJ, QFJ (PLCC), SHP and BGA are surface mount type packages, which are very susceptible to heat in reflow mounting and humidity absorbed in storage.

Therefore, before you perform reflow mounting, contact Oki's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).