# **STV0300**

# FAST SINGLE CHIP OF 8192 COMPLEX POINT FAST FOURIER TRANSFORM

#### PRELIMINARY DATA

- PROGRAMMABLE FFT SIZE FROM 2 TO 8192 COMPLEX WORDS

- 16K WORDS OF ON-CHIP MEMORY (NO EXTERNAL MEMORY NEEDED). HALF OF THE MEMORY ACTS AS AN INPUT BUFFER TO ALLOW SERIAL PROCESSING OF ADJACENT DATA BLOCKS.

- INPUT SAMPLING FREQUENCY AT 20MHz:

- 8192 FFT PERFORMED EVERY 410us

- 4096 FFT PERFORMED EVERY 205µs

- 2048 FFT PERFORMED EVERY 103us

- 1024 FFT PERFORMED EVERY 52us

- 512 FFT PERFORMED EVERY 26 us

- 256 FFT PERFORMED EVERY 13 us

- 128 FFT PERFORMED EVERY 7μs

- 64 FFT PERFORMED EVERY 4μs

- 32 FFT PERFORMED EVERY 2µs

- 2 x 10 BIT COMPLEX INPUT IN NATURAL OR-DER FOR 8192-POINTS AND 4092-POINTS FFT

- 2 x 12 BIT COMPLEX INPUT IN NATURAL ORDER FOR FFT OF UP TO 2048 COMPLEX POINTS

- 10-BIT ACCURACY FOR SINE AND COSINE VALUES

- 2 x 12 BIT INTERNAL ACCURACY

- 2 x 12 BIT COMPLEX OUTPUT IN BIT REVERSE ORDER

- DIRECT OR INVERSE FFT

- PROCESSING OF {x<sub>n</sub>} or {-1<sup>n</sup> x<sub>n</sub>}

# **APPLICATIONS**

- ORTHOGONAL FREQUENCY DIVISION MUL-TIPLEX (DIGITAL AUDIO BROADCASTING, DIGITALTERRESTRIAL TV BROADCASTING)

- SINGLE FREQUENCY NETWORKS FOR DIGITALTV

- SPECTRAL ANALYSIS (MEASUREMENT SYSTEMS, RADARS, ...)

- FIR FILTERING

## **TECHNICAL FEATURES**

■ INPUT SAMPLING FREQUENCY:

- MINIMAL : 1kHz - MAXIMAL : 30MHZ

- LATENCY (BETWEEN FIRST DATA OF INPUT BLOCK AND FIRST DATA OF OUTPUT BLOCK):

- 8192 POINTS: 8918 CYCLES

- 4096 POINTS: 6870 CYCLES

- 2048 POINTS: 2768 CYCLES

- 1024 POINTS: 1744 CYCLES

- 512 POINTS: 714 CYCLES

- 256 POINTS: 458 CYCLES

- 128 POINTS: 196 CYCLES

- 64 POINTS: 132 CYCLES

- 32 POINTS: 62 CYCLES

- 16 POINTS: 46 CYCLES

- 8 POINTS: 24 CYCLES

- 4 POINTS: 20 CYCLES

- 2 POINTS: 12 CYCLES

- 1 POINT(TEST MODE) : 12 CYCLES

- INPUT LEVEL:

- TTL COMPATIBLE, 0 -3.3V  $\pm$  10% (3V-3.6V)

- DISSIPATED POWER: 0.6W at 20MHz

#### **DESCRIPTION**

This chip is dedicated to the computation of Fast Fourier Transforms of up to 8192 complex points. It includes all necessary data and coefficient storage elements (350 kbits of internal memory) for single chip operation.

This component has been specified with the CCETT and developed by the CNET of Grenoble for the validation of the single frequency network concept in an OFDM digital terrestrial television system. SGS-THOMSON is licensed by France Telecom CNET.

#### **PRODUCT STATUS:**

Non Recurring Engineering Samples available.

July 1997 1/7

This is advance information on a new product now in development or undergoing evaluation. Details are subject to change without notice

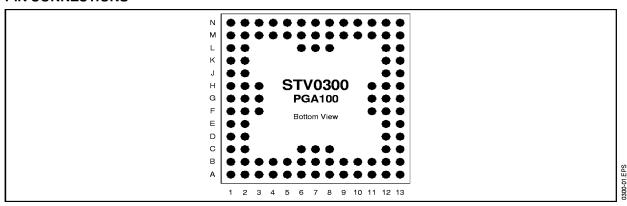

# **PIN CONNECTIONS**

# **PIN DESCRIPTION**

| Pad Name                                                                                                         | Pin                                                            | Туре | Levels   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| CK                                                                                                               | N5                                                             | I    | 0 - 3.3V | Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| SYNC_IN                                                                                                          | N11                                                            | I    | 0 - 3.3V | Each block of data must begin on a rising edge of SYNC_IN synchronous to the rising edge of CK.                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| IN_R[11] IN_R[10] IN_R[8] IN_R[8] IN_R[6] IN_R[6] IN_R[5] IN_R[5] IN_R[3] IN_R[2] IN_R[11] IN_R[0]               | E1<br>F3<br>F2<br>F1<br>H2<br>H3<br>J1<br>J2<br>K1<br>K2<br>L1 | I    | 0 - 3.3V | Input data real part two complement's notation for 8192-points and 4096-points FFT, IN_R[1:0] is not used and can be left unconnected (internally tied to ground level) synchronous to the rising edge of CK.                                                                                                                                                                                                                                                                     |  |  |

| IN_[[11]<br>IN_[[10]<br>IN_[9]<br>IN_[8]<br>IN_[7]<br>IN_[6]<br>IN_[5]<br>IN_[4]<br>IN_[3]<br>IN_[11]<br>IN_[10] | B5<br>A4<br>A3<br>A2<br>B3<br>B1<br>C2<br>C1<br>D2<br>D1<br>E2 | ı    | 0 - 3.3V | Input data imaginary part two complement's notation for 8192-points and 4096-points FFT, IN_[[1:0] is not used and can be left unconnected (internally tied to ground level) synchronous to the rising edge of CK.                                                                                                                                                                                                                                                                |  |  |

| MINUS                                                                                                            | N10                                                            | I    | 0 - 3.3V | When MINUS is high, the corresponding data is multiplied by -1 synchronous to the rising edge of CK.                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| LEN[3]<br>LEN[2]<br>LEN[1]<br>LEN[0]                                                                             | M1<br>L2<br>N1<br>M3                                           |      | 0 - 3.3V | FFT length: - 8192 points FFT when 1101 - 4096 points FFT when 1100 - 2048 points FFT when 1011 - 1024 points FFT when 1010 - 512 points FFT when 1001 - 256 points FFT when 1000 - 128 points FFT when 0111 - 64 points FFT when 0110 - 32 points FFT when 0101 - 16 points FFT when 0100 - 8 points FFT when 0011 - 4 points FFT when 0011 - 2 points FFT when 0010 - 2 points FFT when 0000 Values 1110 and 1111 should not be selected. Synchronous to the rising edge of CK. |  |  |

# PIN DESCRIPTION (continued)

| Pad Name                                                                                                                   | Pin                                                                       | Туре | Levels                 | Description                                                                                                  |  |  |

|----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------|------------------------|--------------------------------------------------------------------------------------------------------------|--|--|

| GAIN_IN                                                                                                                    | N12                                                                       | I    | 0 - 3.3V               | In order to improve SNR for 8192 points FFT only (recommended value :1, 0 for high dynamic input).           |  |  |

| GAIN_OUT[3]<br>GAIN_OUT[2]<br>GAIN_OUT[1]<br>GAIN_OUT[0]                                                                   | N3<br>M4<br>N4<br>M5                                                      | 1    | 0 - 3.3V               | In order to compute circuit gain (see §2 for limit values).                                                  |  |  |

| FFTINV                                                                                                                     | M10                                                                       | I    | 0 - 3.3V               | Direct FFT when low, inverse FFT when High.                                                                  |  |  |

| TEST_IN[7] TEST_IN[6] TEST_IN[5] TEST_IN[4] TEST_IN[3] TEST_IN[2] TEST_IN[1] TEST_IN[0]                                    | L6<br>N6<br>M7<br>L7<br>N8<br>M8<br>L8<br>M9                              |      | 0 - 3.3V               | To be set to low for normal operation mode.                                                                  |  |  |

| NRST                                                                                                                       | N13                                                                       | I    | 0 - 3.3V               | Chip reset, synchronous to the rising edge of CK.                                                            |  |  |

| SYNC_OUT                                                                                                                   | M13                                                                       | 0    | 0 - V <sub>DD</sub> _P | A high level occurs on the first data of a block synchronous to the rising edge of CK.                       |  |  |

| OUT_R[11] OUT_R[9] OUT_R[8] OUT_R[7] OUT_R[6] OUT_R[6] OUT_R[4] OUT_R[4] OUT_R[3] OUT_R[2] OUT_R[1]                        | A13<br>B13<br>C13<br>D13<br>E12<br>E13<br>F12<br>F13<br>H12<br>H11<br>J13 | 0    | 0 - V <sub>DD</sub> _P | Output data real part two complement's notation bit reverse order synchronous to the rising edge of CK.      |  |  |

| OUT_[[11]<br>OUT_[[3]<br>OUT_[8]<br>OUT_[6]<br>OUT_[6]<br>OUT_[6]<br>OUT_[4]<br>OUT_[3]<br>OUT_[2]<br>OUT_[12]<br>OUT_[12] | A5<br>C6<br>B6<br>A7<br>A8<br>B8<br>C8<br>A9<br>A11<br>B11<br>B12         | 0    | 0 - V <sub>DD</sub> P  | Output data imaginary part two complement's notation bit reverse order synchronous to the rising edge of CK. |  |  |

| TEST_OUT[3] TEST_OUT[2] TEST_OUT[1] TEST_OUT[0]                                                                            | K13<br>K12<br>L13<br>L12                                                  | 0    | 0 - V <sub>DD</sub> _P | Output test pins can be left unconnected.                                                                    |  |  |

| V <sub>SS</sub>                                                                                                            | B2, G3,<br>G1, M2,<br>M12, G12,<br>G11, G13,<br>A12, B10,<br>A10, B9      | G    | 0V                     | Ground                                                                                                       |  |  |

| V <sub>DD</sub> _P                                                                                                         | G2, N7,<br>H13, C7                                                        | Р    | 3.3V                   | Power for pad                                                                                                |  |  |

| V <sub>CC</sub> _C                                                                                                         | N2, M6,<br>N9, M11,<br>F11, D12,<br>C12, B7, B4                           | Р    | 3.3V                   | Power                                                                                                        |  |  |

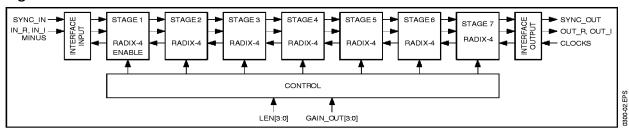

#### **FUNCTIONAL DESCRIPTION**

The FFT8K chip uses a pipelined architecture to compute the FFT (see Figure 1). Such an architecture allows high speed processing without the need of a fast clock. All computations are synchronous to the input data sampling clock (up to 30MHz).

The chip contains:

- an input interface that latches inputs,

- an output interface which controls the circuit gain and latches outputs,

- a control block which enables or not the radix-2 stage or the radix-4 stages depending on the FFT length and defines the circuit gain,

- a radix-2 stage,

- 6 radix-4 stages.

Figure 1 : Architecture

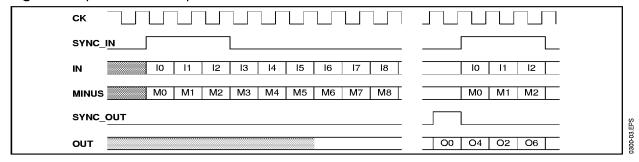

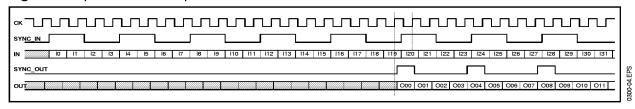

The FFT8K chip works on data organized into blocks whose size is equal to the FFT length. Each block must start on a rising edge of SYNC\_IN which must remain high at least one cycle. Similarly, the chip generates a high level on the SYNC\_OUT padduring the first data of an output block. Input data are in natural order; output data are in bit reverse order. Figure 2 shows an example for an 8-point FFT.

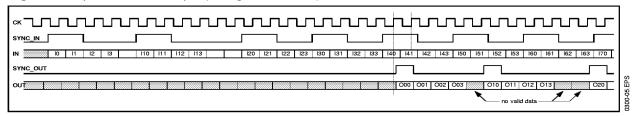

Due to its pipelined architecture, the FFT8K chip is able to process a continuous data flow: it can read a new block while processing the previous one (see Figure 3).

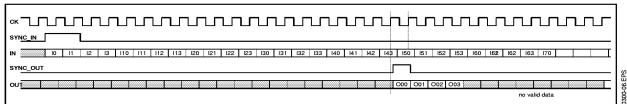

Between two consecutive symbols, non valid data can be inserted (see Figure 4).

Figure 2: 8-points FFT Example

Figure 3: 4-points FFT Example

### FUNCTIONAL DESCRIPTION (continued)

Figure 4: 4-points FFT Example (with guard interval)

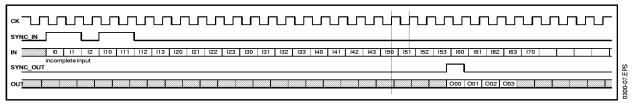

If the input of the current block is still going on (there has been no rising edge on the SYNC\_IN to indicate the beginning of new block), the data available at the output pins after the complete result of this block are not valid (see Figure 5).

If symbol (between 2 sync pulses) is shorter than the FFT length, the output is non valid and no SYNC\_OUT high level is generated (see Figure 6).

The circuit computes the following equation:

$$OUT(k) = G \times \Sigma (-1)^{MINUS(i)} \times IN(i) W^{ik}N$$

where  $w^{ik}N = exp((-1)^{(FFTINV)+1)} 2ikP/N)$ ,

FFTINV must be set to 0 for a direct FFT and to 1 for an inverse FFT, MINUS is an input of the Circuit (used to select  $x_n$  or  $(-1)^n x_n$ , IN is the input data and is defined by its imaginary part IN\_I and real part IN\_R, OUT is the output data and is defined by its imaginary part OUT\_I and its real part OUT\_R. It is provided in the bit reverse order.

Circuit gain is given by the following equation:  $-\log_2G = GAIN_OUT - \lfloor \log_4N \rfloor - 9$  if  $N \le 8192$

- log2G = GAIN\_OUT |log4N| 10 if N = 8192 and GAIN IN = 0

- log2G = GAIN\_OUT |log4N| 8 if N = 8192 and GAIN IN = 1

where N is the FFT length, |log4N| is the highest integer lower or equal to log4N, and GAIN\_OUT a user selectable parameter to adjust the output dynamic.

```

8192 points

-16 ≤ log2G ≤ 1

4096 points

-15 \le \log 2G \le 0

-14 \le \log 2G \le 1

2048 points

-14 ≤ log2G ≤ 1

1024 points

512 points

-13 ≤ log2G ≤ 2

-13 ≤ log2G ≤ 2

256 points

128 points

-12 \le \log 2G \le 3

64 points

-12 \le log 2G \le 3

32 points

-11 \le \log 2G \le 4

16 points

-11 \le \log 2G \le 4

8 points

-10 \le log 2G \le 5

-10 \le log2G \le 5

4 points

2 points

-9 \le \log 2G \le 6

-9 ≤ loa2G ≤ 6

1 point

```

Figure 5: 4-points FFT Example (with SYNC\_IN rising edge)

Figure 6: 4-points FFT Example (with incomplete symbol)

SGS-THOMSON MICROELECTRONICS

# RECOMMENDED OPERATING CONDITIONS

$TT Levels: low = 0.4V, high = 2.4V - CMOS Output: low = 0V, high = V_{DD}\_P - Maximum Output Load: 25pF - Maximu$

| Symbol                                 | Parameter             | Value  | Unit |

|----------------------------------------|-----------------------|--------|------|

| V <sub>DD</sub> _P, V <sub>DD</sub> _C | Supply Voltage        | 3, 3.6 | ٧    |

| V <sub>SS</sub>                        | Ground Voltage        | 0      | ٧    |

| T <sub>oper</sub>                      | Operating Temperature | 0, +85 | °C   |

Note: The inputs can not be directly connected to the outputs of TTL devices supplied with 5V and must be converted to 3.3V before connecting them on the chip. The outputs of the chip are able to supply TTL devices with 5V power supply.

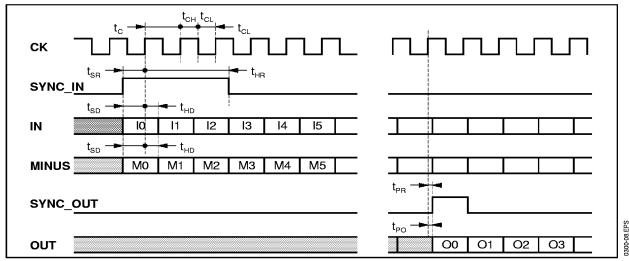

# TIMING CHARACTERISTICS

| Symbol          | Parameter                      | Min. | Тур. | Max. | Unit |

|-----------------|--------------------------------|------|------|------|------|

| t <sub>C</sub>  | Cycle Time                     | 33   |      |      | ns   |

| t <sub>CL</sub> | Low Level Hold Time for Clock  | 10   |      |      | ns   |

| t <sub>CH</sub> | High Level Hold Time for Clock | 10   |      |      | ns   |

| t <sub>SD</sub> | Dat Set-up Time                | -20  |      |      | ns   |

| t <sub>HD</sub> | Data Hold Time                 | 30   |      |      | ns   |

| t <sub>SR</sub> | Sync_in Set-up Time            | -20  |      |      | ns   |

| t <sub>HR</sub> | Sync_in Hold Time              | 30   |      |      | ns   |

| t <sub>PO</sub> | Output Propagation Time        |      |      | 15   | ns   |

| t <sub>PR</sub> | Sync_out Propagation Time      |      |      | 15   | ns   |

Figure 7: Waveforms

Note: The output is provided in the bit reverse order: for a 8-points FFT, X0, X4, X6, X1, X5, X3, X7.

SGS-THOMSON

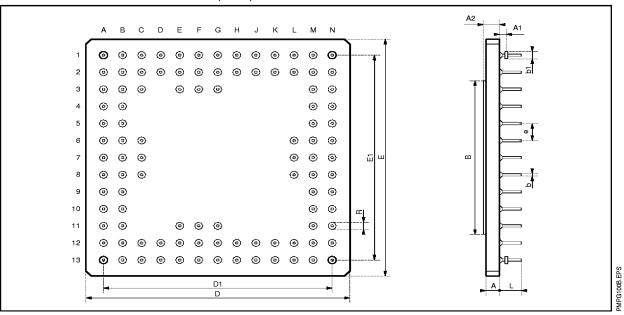

#### PACKAGE MECHANICAL DATA

100 PINS - CERAMIC GRID ARRAY (PGA)

| Dimensions |      | Millimeters |       | Inches |       |       |  |

|------------|------|-------------|-------|--------|-------|-------|--|

|            | Min. | Тур.        | Max.  | Min.   | Тур.  | Max.  |  |

| А          |      |             | 2.24  |        |       | 0.088 |  |

| A1         |      |             | 1.40  |        |       | 0.055 |  |

| A2         |      |             | 2.54  |        |       | 0.100 |  |

| В          |      |             | 17.78 |        |       | 0.700 |  |

| b          |      |             | 0.50  |        |       | 0.020 |  |

| b1         |      |             | 1.68  |        |       | 0.065 |  |

| D          |      |             | 33.58 |        |       | 1.332 |  |

| D1         |      |             | 30.78 |        |       | 1.212 |  |

| E          |      |             | 33.58 |        |       | 1.332 |  |

| E1         |      |             | 30.78 |        |       | 1.212 |  |

| е          |      | 2.54        |       |        | 0.100 |       |  |

| L          |      |             | 4.70  |        |       | 0.185 |  |

| R          |      |             | 1.78  |        |       | 0.070 |  |

GA100B.TBL

Information furnished is believed to be accurate and reliable. However, SGS-THOMSON Microelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No licence is granted by implication or otherwise under any patent or patent rights of SGS-THOMSON Microelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. SGS-THOMSON Microelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of SGS-THOMSON Microelectronics.

© 1997 SGS-THOMSON Microelectronics - All Rights Reserved

Purchase of I<sup>2</sup>C Components of SGS-THOMSON Microelectronics, conveys a license under the Philips I<sup>2</sup>C Patent. Rights to use these components in a I<sup>2</sup>C system, is granted provided that the system conforms to the I<sup>2</sup>C Standard Specifications as defined by Philips.

#### SGS-THOMSON Microelectronics GROUP OF COMPANIES

Australia - Brazil - Canada - China - France - Germany - Hong Kong - Italy - Japan - Korea - Malaysia - Malta - Morocco The Netherlands - Singapore - Spain - Sweden - Switzerland - Taiwan - Thailand - United Kingdom - U.S.A.