## **PM5310**

TBS<sup>TM</sup>

# **TelecomBus Serializer**

# **DATA SHEET**

Proprietary and Confidential Released

Issue 7: November, 2001

#### **Legal Information**

#### Copyright

© 2001 PMC-Sierra, Inc.

The information is proprietary and confidential to PMC-Sierra, Inc., and for its customers' internal use. In any event, you cannot reproduce any part of this document, in any form, without the express written consent of PMC-Sierra, Inc.

PMC-1991257 (R7)

#### **Disclaimer**

None of the information contained in this document constitutes an express or implied warranty by PMC-Sierra, Inc. as to the sufficiency, fitness or suitability for a particular purpose of any such information or the fitness, or suitability for a particular purpose, merchantability, performance, compatibility with other parts or systems, of any of the products of PMC-Sierra, Inc., or any portion thereof, referred to in this document. PMC-Sierra, Inc. expressly disclaims all representations and warranties of any kind regarding the contents or use of the information, including, but not limited to, express and implied warranties of accuracy, completeness, merchantability, fitness for a particular use, or non-infringement.

In no event will PMC-Sierra, Inc. be liable for any direct, indirect, special, incidental or consequential damages, including, but not limited to, lost profits, lost business or lost data resulting from any use of or reliance upon the information, whether or not PMC-Sierra, Inc. has been advised of the possibility of such damage.

#### **Trademarks**

S/UNI is a registered trademark of PMC-Sierra, Inc. PMC-Sierra

TBS, TSE, SPECTRA-2488, TUPP+622, CHESS, and TEMUX are trademarks of PMC-Sierra, Inc. Other product and company names mentioned herein may be the trademarks of their respective owners.

### **Contacting PMC-Sierra**

PMC-Sierra 8555 Baxter Place Burnaby, BC Canada V5A 4V7

Tel: 1 (604) 415-6000 Fax: 1 (604) 415-6200

Document Information: document@pmc-sierra.com Corporate Information: info@pmc-sierra.com Technical Support: apps@pmc-sierra.com

## **Revision History**

| Issue<br>No. | Issue Date       | Details of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1            | Sept. 1999       | Added func timing, registers, and operations sections.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2            | Feb. 2000        | Fixed Header, format of document, mechanical information, changed 1.8V to +- 5%, corrected LVDS diagram, added pinout, added pin #., changes res/resk to 3.16 from 4.75 k. Updated register descriptions and added numerous technical updates/corrections. DLL added.                                                                                                                                                                                                                                                                                                     |

| 3            | May 2000         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|              |                  | Updated active page switch over timing to switching two frames after CMP is asserted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|              |                  | Added J0 synchronization and initialization subsections.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|              |                  | Changed connection information for ATB[0:1] pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|              |                  | Added notes to registers 1A0, 1A1, 1C0, 1C1. Changed registers 132 - 137h, 142h, and 1CC to reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|              |                  | Changed indirect registers 0, 1, 2, 3 of address 1C1h to the correct indirect addresses 8, 9, A, and B respectively.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4            | November<br>2000 | Completed table 11. Changed the number of bytes req'd to go out of sync on PRBS monitors from 4 to 3. Updated section 14.9. Updated INCIJ0J1 bit definition to cover IJ0J1[1] override of IJ0J1[x] signals. Updated Monitor Error Count register definition to cover the possible counting of 2 extra bytes when losing sync. Updated section 14.9.2, the synci and syncv bit definitions to state that the prbs monitor's accumulator value must be checked after sync is declared to confirm that the monitor has not been falsely sync'd to an all 1 or all 0 pattern. |

| Issue<br>No. | Issue Date    | Details of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4 cont'd     | November 2000 | Clarified that syncv bit is only valid when monitor enabled. Also clarified synci in all register descriptions wrt concatenated payloads. Reg 53h was modified so that change, changei, refclki, sysclki bits were made reserved bits. Changed register Ch bit 15 from Reserved to unused. Clarified section 14.9.4 with regards to how error counts are accumulated for concatenated payloads. Changed bit 11 of reg21h, 31h, 41h to IP8ESEL from reserved. Added comment in 11.2.2 to indicate order of precedence in the 8b/10b encoding table. Clarified FUOI bit definition.  Documented reg 52h, the DLL Reset register.  Changed registers 1D0 and 1D1h to reserved (were the OT8D frame alignment status and interrupt bits). Clarified section 11.14 by stating OT8D operates in continuous character alignment. Changed max power from 4.2 W to 3.55 W. Changed all TIP bit occurrences from R/W to R. Changed OT8D interrupt and interrupt enable bits to reserved. In section 15.1 changed references about IJ0J1[4] and IPL[4] to IJ0J1[1] and IPL[1]. Removed from initialization section the writes to addr 135h, 145h, 155h etc. since they were unnecessary. Clarified the definition of the DLCV bit in the T8TE blocks. Corrected the information on how to force the PRGM blocks to transfer the accumulated error counts by writing to addr 05h or addr X0Ch (eg 10C, 20C etc). Clarified timing of TCMP, OCMP and RWSEL in pin descriptions. Numerous format/font changes. Updated absolute maximums table. Updated BSDL table. Changed "IDLE" (bit in multiple registers) to "CHARACTER OVERWRITE" and clarified the idle character description. Corrected title of reg 112h. Added Thaw parameter to the microprocessor write table. Added note in section 14.11 (point 4) about the need to write to the CSU registers on initialization. Added input pad tolerance spec to absolute maximum ratings section. Corrected point 8 in figure 10 to read S/UNI-MACH48 instead of TSE. Updated OPAIS pin description to indicate the signal is invalid during J0/Z0 timeslots. |

| 4 cont'd     | November 2000 | Added note to receive LVDS pins and OJ0J1 pins to see section 14.19 with respect to using LVDS receive links independently. Added section 14.19. Added power consumption to the DC. Characteristics section. Clarified section 14.9 wrt PRGM non compatibility with external test equipment. IP8E_PRBS_ENA and ID8E_PRBS_ENA bits use clarified (see reg 101h, IADDR 8). Added 50 ma latch up current spec for RESK pin in Absolute Maximum Ratings section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Issue<br>No. | Issue Date        | Details of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5            | December,<br>2000 | Modified I <sub>I</sub> LPU D.C.Characteristics to be $-200$ , $-50$ , $-4$ $\mu$ A. Added note in OPL pin description indicating OPL always high during H3 byte location when in MST mode. Modified registers 135h, 145h, 155h, to show bits 7 & 8 and registers 163h, 173h, 183h to show bits 12 and 13 and added notes to these registers w.r.t. disabling LVDS links for power savings. Added power up sequencing and Disabling Links for Power savings subsections (14.1 & 14.2 ). Added w.c. power for AVDH, AVDL, CSU_AVDH in D.C. Characteristics section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5            | January,<br>2001  | Added descriptions for Registers 135h, 145h, 155h, 163h, 173h and 183h in the Register Memory Map. Added detail to power sequencing information. Added Section 14.1 power estimates. Added Sections 14.4 and 14.5. Added thermal information in Section 21.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5            | January,<br>2001  | Added note regarding FIFOERRI default value of "0" in Registers 0x131, 0x141, 0x151. Added note to 11.1.1 to explain that monitoring of TBS or MACH48 PRBS streams requires transmission in HPT mode. Added note that B1E1 insertion on the IP8E path will only occur if both B1E1_ENA and IP8E_PRBS_ENA are set to 1. Added warning about inadvertently clearing ERRORI when polling Register 0x53. Added TCB series termination note in Section 14.2. Removed erroneous statements that "for STS-Nc PRBS functions, only the master slice needs to be configured". Added instructions to check CSU lock status and re-center transmit FIFOs in Section 14.17 (Initialization Procedure). Revealed TxDE Test Pattern registers, Fixed incorrect block instance references in the section that cross-references instance #2, #3 and #4 block registers to instance #1 register descriptions. Added Section 14.11 describing inter-relationships of receive decoder status bits. Added instructions for enabling RAPMI #1-#4 and RPTII based on datasheet errata. |

| 5            | February, 2001    | Added JTAG AC Timing info. Changed temp spec from "Tc=-40 to +85C" to "Tc=-40C to Tj=+120C". Clarified note on external interconnection of VDDI, VDDO, AVDH, AVDL pins. Changed VDDI spec to +/-5% from +/-10%. Changed VT+ limit in Section 17 from 2.0 to 2.2V and added SYSCLK to its pin list. Changed max power value from 3.55W to 2.95W. Changed max Iddop3.3V from 369mA to 330mA. Changed max Iddop1.8V from 1170mA to 1240mA. Added note to section 10 that Schmitt trigger inputs do not meet TTL levels. Added SYSCLK to Vth pin list in Section 17. Moved "LVDS Optimizations", "Hot Swapping" and "Trace Length" sections from "Functional Description" to "Operations". Added list of registers.                                                                                                                                                                                                                                                                                                                                                  |

| Issue<br>No. | Issue Date         | Details of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6            | June, 2001         | Updated Indirect Access section to discuss cases of BUSY bit being stuck at 1. Added J0RORDR bit on receive TSI blocks. Removed references to OT8D registers from the initialization procedure. Added description of AIS signals not being effected by PRBS insertion, which may over-ride attempts to insert a PRBS sequence into the SPE. Removed references to registers 110H, 120H from initialization section, included indirect access maximum BUSY times. Added Reset Timing. Changed JTAG ITV5[4] ID bit to 'H' to make JTAG version number 1H. Changed TBS Version/Part Number Register 012H to Default to 0x1531 (Changed VERSION field to 0x1) |

| 6            | July, 2001         | Removed references to LPT mode. Added analog power supply filtering recommendations. Clarified which pins are AVDL and which are CSU_AVDL in pin description and diagram. Added functional description of DLL and corrected DLL register descriptions. Changed VDDO, AVDH spec to +/-5% from +/-10%. Added IDDOP on for AVDH, AVDL, VDDI, VDDO. Updated Power Sequencing to allow for hot swap of LVDS links. Added cycle times to complete Performance Counter Accumulation. Updated B1/E1 mismatch interrupt status.                                                                                                                                    |

| 7            | Sept - Nov<br>2001 | Clarified B1E1_ENA and Monitor B1E1 register to state that B1E1_ENA must be high before the Monitor B1E1 register will be updated with the current B1 and E1 values. Clarified LCVI description. Clarified pin description on IJ0J1 to state that V1 pulses on this input will cause errors. Added new Power Information section. Moved power filtering and sequencing into new section. Changed Ta=-40 to Tc=120 to Ta= -40 to Tj = 125 throughout. Updated thermal info. Added patents pending. Updated absolute max table. Changed device status to released.                                                                                          |

### **Table of Contents**

| Leg  | al Info | ormation                                  | 2    |

|------|---------|-------------------------------------------|------|

|      |         | Copyright                                 | 2    |

|      |         | Disclaimer                                | 2    |

|      |         | Trademarks                                | 2    |

| Rev  | ision   | History                                   | 4    |

| Tab  | le of ( | Contents                                  | 8    |

| List | of Re   | gisters                                   |      |

| List | of Fig  | iures                                     | S 16 |

| List | of Tal  | oles                                      | 17   |

| 1    | Feat    | ures                                      | 18   |

| 2    | Appl    | uresications                              | 20   |

| 3    | Refe    | rences                                    | 21   |

| 4    |         |                                           |      |

| 5    | Appl    | ication Examples                          | 24   |

| 6    | Bloc    | k Diagram                                 | 25   |

| 7    | Loop    | nitions                                   | 26   |

| 8    | Dasa    | printion                                  | 28   |

| 9    | Pin [   | Diagram                                   | 29   |

| 10   | Pin [   | Diagram  Description                      | 34   |

| 11   | Fund    | ctional Description                       | 52   |

|      | 11.1    | Incoming TelecomBus PRBS Processor        | 52   |

|      |         | 11.1.1 PRBS Detector                      | 52   |

|      |         | 11.1.2 PRBS Generator                     | 52   |

|      | 11.2    | Incoming Data 8B/10B Encoder              | 53   |

|      |         | 11.2.1 Frame Counter                      | 53   |

|      |         | 11.2.2 8B/10B Encoder                     | 53   |

|      | 11.3    | Incoming PRBS 8B/10B Encoder              | 54   |

|      | 11.4    | Transmit Time-slot Interchange            | 55   |

|      | ~OZ"    | 11.4.1 Data Buffer                        | 55   |

|      | V       | 11.4.2 Connection Memory                  | 55   |

|      | 11.5    | Transmit 8B/10B Running Disparity Encoder | 55   |

|      | 11.6    | Transmit Serializer                       | 56   |

|      | 11.7    | LVDS Transmitter                          | 56   |

|    | 11.8  | CSTR56            |                                                    |             |

|----|-------|-------------------|----------------------------------------------------|-------------|

|    | 11.9  | DLL 56            |                                                    | Q           |

|    | 11.10 | LVDS Re           | eceiver                                            | 57          |

|    | 11.11 | Data Red          | covery Unit                                        | 57          |

|    | 11.12 | Receive           | 8B/10B TelecomBus Decoder                          | 57          |

|    |       | 11.12.1           | FIFO Buffer                                        | 57          |

|    |       | 11.12.2           | Frame Counter                                      | <b>.</b> 58 |

|    |       |                   | Character Alignment                                |             |

|    |       | 11.12.4           | Frame Alignment                                    | 58          |

|    |       | 11.12.5           | Character Decode                                   | 58          |

|    | 11.13 | Receive           | Character Decode                                   | 61          |

|    | 11.14 | Receive           | Time-slot Interchange                              | 62          |

|    |       |                   |                                                    |             |

|    | 11.16 | i Outaoina        | TelecomBus PRBS Generator                          | 62          |

|    | 11.17 | LVDS OV           | verviewocessor Interface                           | 62          |

|    | 11.18 | Micropro Micropro | cessor Interface                                   | 64          |

| 12 | Norr  | nal Mode          | Register Description                               | 70          |

| 13 | Test  | Feature D         | Description                                        | 317         |

| 14 | Ope   | ration            | Descriptiononservation                             | 318         |

|    | 14.1  | Power C           | onservation                                        | 318         |

|    |       |                   | TelecomBus Termination                             |             |

|    |       |                   | otimizations                                       |             |

|    |       |                   | ot Swapping                                        |             |

|    |       |                   | ace Lengths                                        |             |

|    | 14.6  | JTAG Te           | st Port                                            | 321         |

|    | 14.7  | JTAG Su           | ıpport                                             | 327         |

|    |       | 70.               | AP Controller                                      |             |

|    |       | 14.7.2 Sta        | ates                                               | 330         |

|    |       |                   | structions                                         |             |

|    | 14.8  | Interrupt         | Service Routine                                    | 331         |

| 4  |       |                   | ng Indirect Registers                              |             |

|    |       |                   | e Performance Monitoring Features                  |             |

|    |       | •                 | ing the Status of Receive Decoders                 |             |

|    | 14.12 | 2 Setting u       | p Timeslot Assignments in the RWTI, RPTI, and RATI |             |

|    |       | 14.12.1           | Receive Timeslot Mapping                           | 335         |

|    |       | 14.12.2       | Custom Timeslot Mappings                                         | . 335 |

|----|-------|---------------|------------------------------------------------------------------|-------|

|    | 14.13 | Setting up    | p Timeslot Assignments in the TWTI, TPTI, and TATI               | . 336 |

|    |       | 14.13.1       | Transmit Timeslot Mapping                                        | . 337 |

|    |       | 14.13.2       | Custom Timeslot Mappings                                         | . 337 |

|    |       | 14.13.3       | Active and Standby Pages in the TSI Blocks                       | . 337 |

|    | 14.14 | Using RW      | VSEL and RWTSEN, RPTSEN, and RATSEN                              | . 338 |

|    | 14.15 | PRBS Ge       | enerator and Monitor (PRGM)                                      |       |

|    |       | 14.15.1       | Mixed Payload (STS-12c, STS-3c, and STS-1)                       |       |

|    |       | 14.15.2       | Synchronization                                                  | . 339 |

|    |       | 14.15.3       | Master/Slave Configuration for STS-48c/STM-16c Payloads          | . 340 |

|    |       | 14.15.4       | Error Detection and Accumulation.                                | . 341 |

|    | 14.16 | "J0" Sync     | chronization of the TBS in a CHESS™ System                       | . 341 |

|    | 14.17 | 'Initializati | on Procedure                                                     | . 344 |

|    | 14.18 | Using the     | TBS with Low-Order Path Terminating Devices                      | . 346 |

|    |       | _             | the Working, Protect and Auxiliary Receive Links Independently . |       |

| 15 | Func  | tional Tim    | ing                                                              | . 348 |

|    | 15.1  | Incoming      | Parallel TelecomBus to Transmit Serial TelecomBus                | . 348 |

|    |       |               | Serial TelecomBus to Outgoing Parallel TelecomBus                |       |

| 16 | Abso  | olute maxir   | mum ratingstion                                                  | . 354 |

| 17 |       |               |                                                                  |       |

|    | 17.1  | Power Re      | equirements                                                      | . 355 |

|    | 17.2  | Power Se      | equencing                                                        | . 355 |

|    | 17.3  | Power Su      | upply Filtering                                                  | . 356 |

| 18 | D. C  | . Characte    | eristics                                                         | . 357 |

| 19 | Micro | oprocesso     | r Interface Timing Characteristics                               | . 359 |

| 20 | A.C.  | timing Ch     | aracteristics                                                    | . 363 |

|    | 20.1  | Serial Tel    | ecomBus Interface                                                | . 363 |

|    | 20.2  | Reset Tin     | ning                                                             | . 363 |

|    | 20.3  | Parallel T    | elecomBus Interface                                              | . 363 |

|    | 20.4  | JTAG Poi      | rt Interface                                                     | . 368 |

| 21 | Orde  | ering Inforr  | mation                                                           | . 370 |

| 22 | Ther  | mal Inform    | nation                                                           | . 371 |

| 23 | Mecl  | hanical Inf   | ormation                                                         | .372  |

## **List of Registers**

| Register 000H | TBS Master Incoming Configuration and Control                 | 71   |

|---------------|---------------------------------------------------------------|------|

| Register 001H | TBS Master Outgoing Configuration and Control                 | , 74 |

| Register 002H | TBS Master Input Signal Activity, Accumulation Trigger        | 76   |

| Register 003H | TBS Master Reset                                              | 78   |

| Register 004H | TBS Master Parity Error Interrupt Status                      | 81   |

| Register 005H | TBS Master Accumulation Transfer and Receive Synchronization  |      |

| Del           | FREE User Register                                            | 82   |

| Register 006H | FREE User Register                                            | 83   |

| Register 008H | TBS Master Interrupt Enable #1 TBS Master Interrupt Enable #2 | 84   |

| Register 009H | TBS Master Interrupt Enable #2                                | 87   |

| Register 00AH | TBS Master Interrupt Enable #3                                | 90   |

| Register 00BH | TBS Master Interrupt Enable #4                                | 93   |

| _             | TBS Master TSI, DLL and CSTR Interrupt Enable                 |      |

|               | TBS Master Interrupt Status #1                                |      |

| Register 00EH | TBS Master Interrupt Status #2                                | 101  |

| Register 00FH | TBS Master Interrupt Status #3                                | 104  |

| Register 010H | TBS Master Interrupt Status #4                                | 107  |

| Register 011H | TBS Master TSI, DLL and CSTR Interrupt Status                 | 110  |

| Register 012H | TBS Version/Part Number                                       | 112  |

| Register 013H | TBS Part Number/Manufacturer ID                               | 113  |

| Register 020H | TWTI Indirect Address                                         | 114  |

| Register 021H | TWTI Indirect Data                                            | 116  |

| Register 022H | TWTI Configuration and Status                                 | 119  |

| Register 023H | TWTI Interrupt Status                                         | 121  |

| Register 030H | TPTI Indirect Address                                         | 122  |

| Register 031H | TPTI Indirect Data                                            | 124  |

| Register 032H | TPTI Configuration and Status                                 | 127  |

| Register 033H | TPTI Interrupt Status                                         | 129  |

| Register 040H | TATI Indirect Address                                         | 130  |

| Register 041H | TATI Indirect Data                                            | 132  |

| Register 042H | TATI Configuration and Status                                 | 135  |

| Register 043H | TATI Interrupt Status                                         | 137  |

| Register 050H | DLL Configuration                                             | 138  |

| Register 052H | DLL Reset                                                     | 139  |

| Register 053H Control Status                                                  | 140 |

|-------------------------------------------------------------------------------|-----|

| Register 080H RWTI Indirect Address                                           | 142 |

| Register 081H RWTI Indirect Data                                              | 144 |

| Register 082H RWTI Configuration and Status                                   |     |

| Register 083H RWTI Interrupt Status                                           | 148 |

| Register 090H RPTI Indirect Address                                           | 149 |

| Register 091H RPTI Indirect Data                                              | 151 |

| Register 092H RPTI Configuration and Status                                   | 153 |

| Register 093H RPTI Interrupt Status                                           | 155 |

| Register 0A0H RATI Indirect Address                                           | 156 |

| Pegister 0.41H DATI Indirect Data                                             | 150 |

| Register 0A2H RATI Configuration and Status                                   | 160 |

| Register 0A11 RATI Indirect Data  Register 0A2H RATI Configuration and Status | 162 |

| Register 100h ITPP #1 Indirect Address                                        | 163 |

| Register 101h ITPP #1 Indirect Data                                           | 165 |

| Register 101h (IADDR = 0h) ITPP #1 Monitor STS-1 path Configuration           |     |

| Register 101h (IADDR = 1h) ITPP #1 Monitor PRBS[22:7] Accumulator             | 168 |

| Register 101h (IADDR = 2h) ITPP #1 Monitor PRBS[6:0] Accumulator              | 169 |

| Register 101h (IADDR = 3h) ITPP #1 Monitor B1/E1 Expected value               | 170 |

| Register 101h (IADDR = 4h) ITPP #1 Monitor Error count                        | 171 |

| Register 101h (IADDR = 5h) ITPP #1 Monitor Received B1/E1 bytes               | 172 |

| Register 101h (IADDR = 8h) ITPP #1 Generator STS-1 path Configuration         | 173 |

| Register 101h (IADDR = 9h) ITPP #1 Generator PRBS[22:7] Accumulator           | 175 |

| Register 101h (IADDR = Ah) ITPP #1 Generator PRBS[6:0] Accumulator            | 176 |

| Register 101h (IADDR = Bh): ITPP #1 Generator B1/E1 Value                     | 177 |

| Register 102h ITPP #1 Generator Payload Configuration                         | 178 |

| Register 103h ITPP #1 Monitor Payload Configuration                           | 181 |

| Register 104h ITPP #1 Monitor Byte Error Interrupt Status                     | 184 |

| Register 105h ITPP #1 Monitor Byte Error Interrupt Enable                     | 185 |

| Register 106h ITPP #1 Monitor B1/E1 Byte Mismatch Interrupt Status            | 186 |

| Register 107h ITPP#1 Monitor B1/E1 Mismatch Interrupt Enable                  | 187 |

| Register 109h ITPP#1 Monitor Synchronization Interrupt Status                 | 188 |

| Register 10Ah ITPP#1 Monitor Synchronization Interrupt Enable                 | 189 |

| Register 10Bh ITPP#1 Monitor Synchronization State                            | 190 |

| Register 10Ch ITPP #1 Performance Counters Transfer Trigger                   | 191 |

| Register 112H ID  | 08E #1 Time-slot Configuration #1                | 192 |

|-------------------|--------------------------------------------------|-----|

| Register 113H ID  | 08E #1 Time-slot Configuration #2                | 193 |

| Register 122H IP  | P8E #1 Time-slot Configuration #1                | 194 |

| Register 123H IP  | P8E #1 Time-slot Configuration #2                | 195 |

| Register 130H T\  | WDE #1 Control and Status                        | 196 |

| Register 131H T\  | WDE #1 Interrupt Status                          | 198 |

| Register 134H T\  | WDE #1 Test Pattern                              | 199 |

| Register 135H T\  | WDE #1 Analog Control                            | 200 |

| Register 140H TF  | PDE #1 Control and Status                        | 201 |

| Register 141H TF  | PDE #1 Interrupt Status                          | 203 |

| Register 144H TE  | PNF #1 Test Pattern                              | 204 |

| Register 145H TF  | PDE #1 Analog Control                            | 205 |

| Register 150H TA  | ADE #1 Control and StatusADE #1 Interrupt Status | 206 |

| Register 151H TA  | ADE #1 Interrupt Status                          | 208 |

| Register 154H TA  | ADE #1 Test Pattern                              | 209 |

|                   | ADE #1 Analog Control                            |     |

| Register 160H R   | W8D #1 Control and Status                        | 211 |

| Register 161H R   | W8D #1 Interrupt Status                          | 214 |

| Register 162H R   | W8D #1 Line Code Violation Count                 | 216 |

| Register 163H R   | W8D #1 Analog Control #1                         | 217 |

| Register 170H R   | P8D #1 Control and Status                        | 218 |

| Register 171H R   | P8D #1 Interrupt Status                          | 221 |

| Register 172H R   | P8D #1 Line Code Violation Count                 | 223 |

| Register 173H R   | P8D #1 Analog Control #1                         | 224 |

| Register 180H RA  | A8D #1 Control and Status                        | 225 |

| Register 181H R   | A8D #1 Interrupt Status                          | 228 |

| Register 182H R   | A8D #1 Line Code Violation Count                 | 230 |

| Register 183H R   | A8D #1 Analog Control #1                         | 231 |

| Register 190h RV  | WPM #1 Indirect Address                          | 232 |

| Register 191h RV  | WPM #1 Indirect Data                             | 234 |

| Register 191h (IA | DDR = 0h) RWPM #1 STS-1 path Configuration       | 235 |

| Register 191h (IA | DDR = 1h) RWPM #1 PRBS[22:7] Accumulator         | 237 |

| Register 191h (IA | DDR = 2h) RWPM #1 PRBS[6:0] Accumulator          | 238 |

| Register 191h (IA | DDR = 3h) RWPM #1 B1/E1 value                    | 239 |

| Register 191h (IA | DDR = 4h) RWPM #1 Error count                    | 240 |

| Register 191h (IADDR = 5h) RWPM #1 Received B1/E1 bytes            | 241   |

|--------------------------------------------------------------------|-------|

| Register 193h RWPM #1 Monitor Payload Configuration                | 242   |

| Register 194h RWPM #1 Monitor Byte Error Interrupt Status          | . 245 |

| Register 195h RWPM #1 Monitor Byte Error Interrupt Enable          | 246   |

| Register 196h RWPM #1 Monitor B1/E1 Byte Mismatch Interrupt Status | 247   |

| Register 197h RWPM#1 Monitor B1/E1 Mismatch Interrupt Enable       |       |

| Register 199h RWPM#1 Monitor Synchronization Interrupt Status      | 249   |

| Register 19Ah RWPM#1 Monitor Synchronization Interrupt Enable      |       |

| Register 19Bh RWPM#1 Monitor Synchronization State                 | 251   |

| Register 19Ch RWPM #1 Performance Counters Transfer Trigger        |       |

| Register 1A0h RPPM #1 Indirect Address                             | 253   |

| Register 1A1h RPPM #1 Indirect Data                                | 255   |

| Register 1A1h (IADDR = 0h) RPPM #1 STS-1 path Configuration        | 256   |

| Register 1A1h (IADDR = 1h) RPPM #1 PRBS[22:7] Accumulator          | 258   |

| Register 1A1h (IADDR = 2h) RPPM #1 PRBS[6:0] Accumulator           | 259   |

| Register 1A1h (IADDR = 3h) RPPM #1 B1/E1 value                     | 260   |

| Register 1A1h (IADDR = 4h) RPPM #1 Error count                     | 261   |

| Register 1A1h (IADDR = 5h) RPPM #1 Received B1/E1 bytes            | 262   |

| Register 1A3h RPPM #1 Monitor Payload Configuration                | 263   |

| Register 1A4h RPPM #1 Monitor Byte Error Interrupt Status          | 266   |

| Register 1A5h RPPM #1 Monitor Byte Error Interrupt Enable          | 267   |

| Register 1A6h RPPM #1 Monitor B1/E1 Byte Mismatch Interrupt Status | 268   |

| Register 1A7h RPPM#1 Monitor B1/E1 Mismatch Interrupt Enable       | 269   |

| Register 1A9h RPPM#1 Monitor Synchronization Interrupt Status      | 270   |

| Register 1AAh RPPM#1 Monitor Synchronization Interrupt Enable      | 271   |

| Register 1ABh RPPM#1 Monitor Synchronization State                 | 272   |

| Register 1ACh RPPM #1 Performance Counters Transfer Trigger        | 273   |

| Register 1B0h RAPM #1 Indirect Address                             | 274   |

| Register 1B1h RAPM #1 Indirect Data                                | 276   |

| Register 1B1h (IADDR = 0h) RAPM #1 STS-1 path Configuration        | 277   |

| Register 1B1h (IADDR = 1h) RAPM #1 PRBS[22:7] Accumulator          | 279   |

| Register 1B1h (IADDR = 2h) RAPM #1 PRBS[6:0] Accumulator           | 280   |

| Register 1B1h (IADDR = 3h) RAPM #1 B1/E1 value                     | 281   |

| Register 1B1h (IADDR = 4h) RAPM #1 Error count                     | 282   |

| Register 1B1h (IADDR = 5h) RAPM #1 Received B1/E1 bytes            | 283   |

| Register 1B3h | RAPM #1 Monitor Payload Configuration                | 284 |

|---------------|------------------------------------------------------|-----|

| Register 1B4h | RAPM #1 Monitor Byte Error Interrupt Status          | 287 |

| Register 1B5h | RAPM #1 Monitor Byte Error Interrupt Enable          | 288 |

| Register 1B6h | RAPM #1 Monitor B1/E1 Byte Mismatch Interrupt Status | 289 |

| Register 1B7h | RAPM#1 Monitor B1/E1 Mismatch Interrupt Enable       | 290 |

|               | RAPM#1 Monitor Synchronization Interrupt Status      | 291 |

| Register 1BAh | RAPM#1 Monitor Synchronization Interrupt Enable      | 292 |

|               | RAPM#1 Monitor Synchronization State                 | 293 |

| Register 1BCh | RAPM #1 Performance Counters Transfer Trigger        | 294 |

| Register 1C0h | OTPG #1 Indirect Address                             | 295 |

| Register 1C1h | OTPG #1 Indirect Data                                | 297 |

| Register 1C1h | (IADDR = 8h) OTPG #1 STS-1 path Configuration        | 298 |

| Register 1C1h | (IADDR = 9h) OTPG #1 PRBS[22:7] Accumulator          | 300 |

| Register 1C1h | (IADDR = Ah) OTPG #1 PRBS[6:0] Accumulator           | 301 |

| Register 1C1h | (IADDR = Bh) OTPG #1 B1/E1 Value                     | 302 |

| Register 1C2h | OTPG #1 Generator Payload Configuration              | 303 |

| Register 500H | CSTR Control                                         | 314 |

| Register 501H | CSTR Configuration and Status                        | 315 |

| Register 502H | CSTR Interrunt Status                                | 316 |

## **List of Figures**

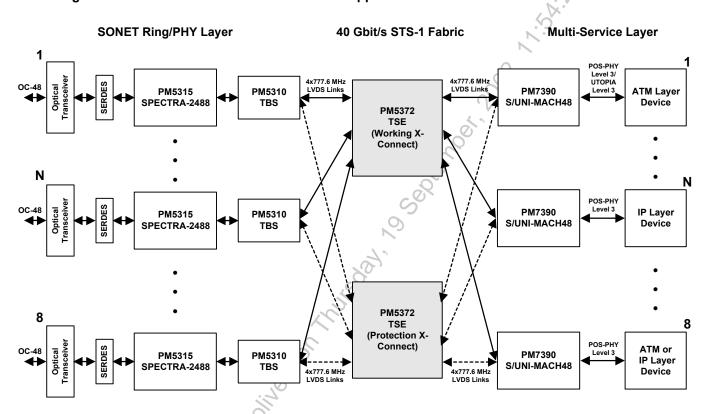

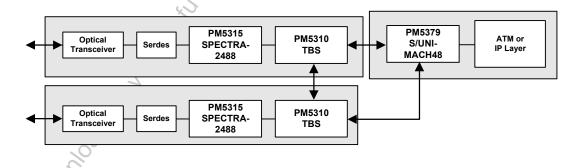

| Figure 1 Multi-Service ATM/POS Switch Port Application                   | 24      |

|--------------------------------------------------------------------------|---------|

| Figure 2 2.5 Gb/s Multi-service ADM                                      |         |

| Figure 3 Pin Diagram                                                     | 29      |

| Figure 4 Pin Diagram Top Left Corner                                     | 30      |

| Figure 5 Pin Diagram Top Right Corner                                    | 31      |

| Figure 6 Pin Diagram Bottom Left Corner                                  |         |

| Figure 7 Pin Diagram Bottom Right Corner                                 | 33      |

| Figure 8 Generic LVDS Link Block Diagram                                 | 63      |

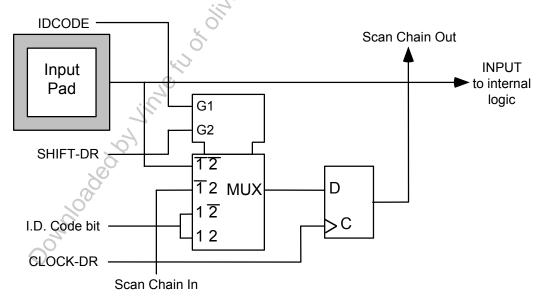

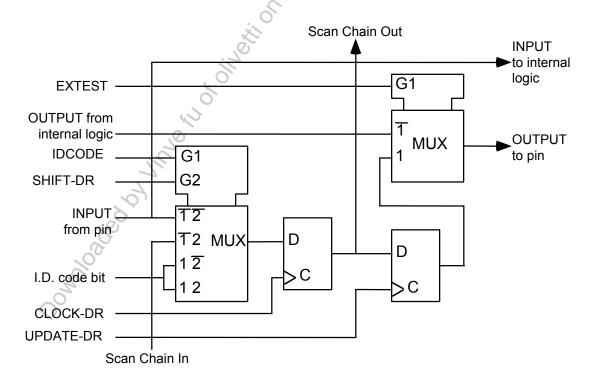

| Figure 9 Input Observation Cell (IN CELL)                                | 325     |

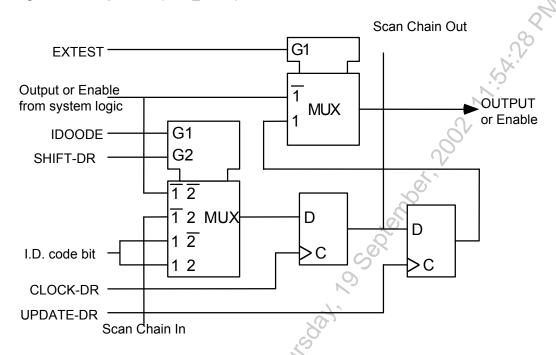

| Figure 10 Output Cell (OUT_CELL)                                         | 326     |

| Figure 10 Output Cell (OUT_CELL)                                         | 326     |

| Figure 12 Layout of Output Enable and Bi-directional Cells               | 327     |

| Figure 13 Boundary Scan Architecture                                     | 328     |

| Figure 14 TAP Controller Finite State Machine                            | 329     |

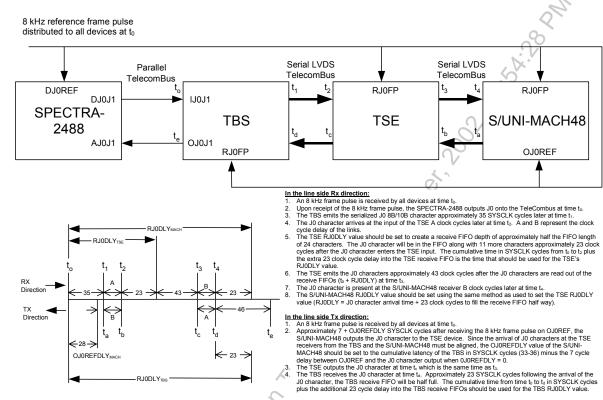

| Figure 15 "J0" Synchronization Control                                   | 344     |

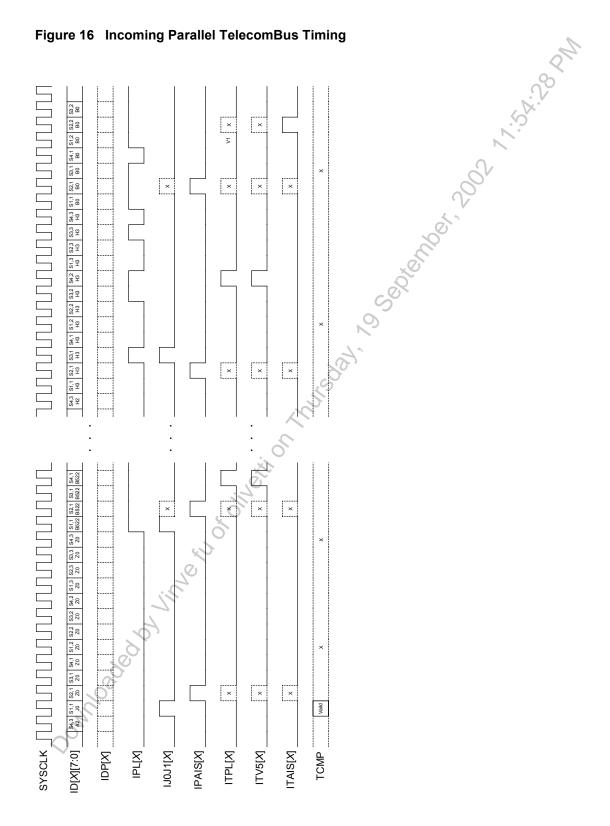

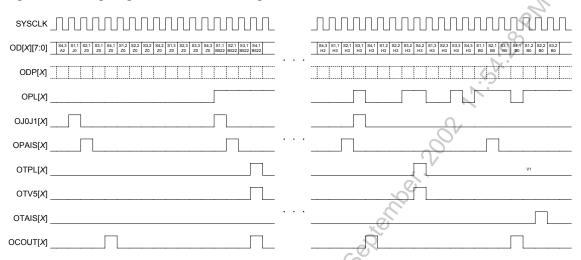

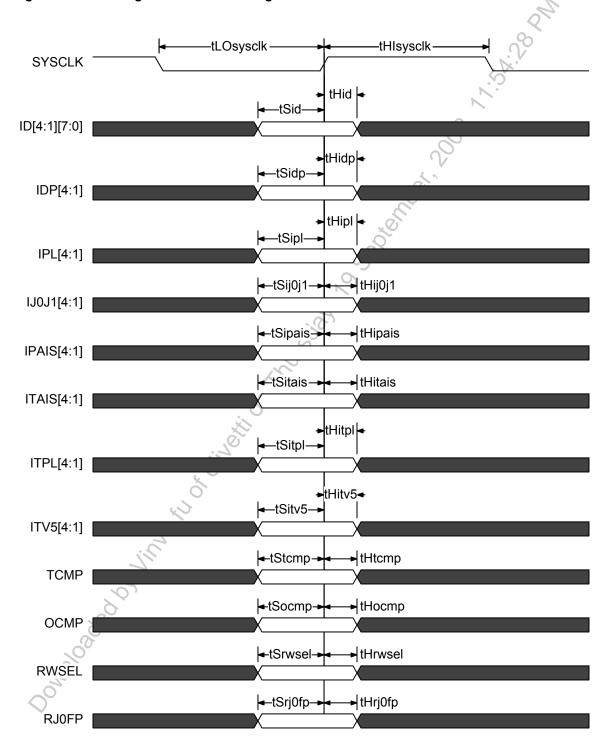

| Figure 16 Incoming Parallel TelecomBus Timing                            | 349     |

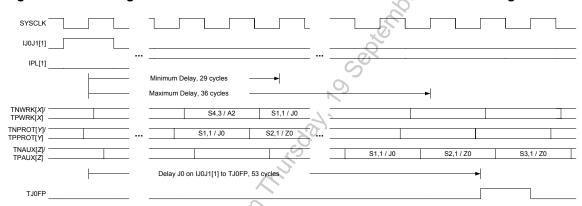

| Figure 17 Incoming Parallel TelecomBus to Transmit Serial TelecomBus Tim | ing 350 |

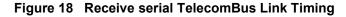

| Figure 18 Receive serial TelecomBus Link Timing                          | 351     |

| Figure 19 Outgoing TelecomBus Synchronization Timing                     | 351     |

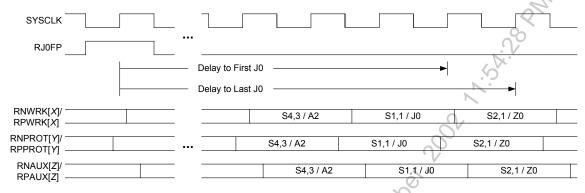

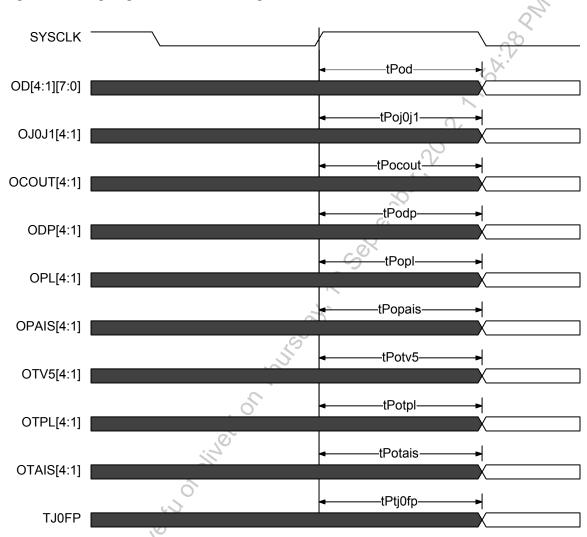

| Figure 20 Outgoing TelecomBus Timing                                     | 353     |

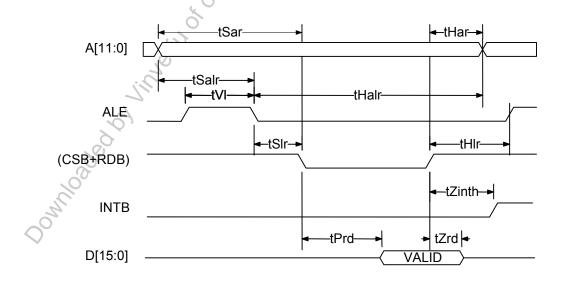

| Figure 21 Microprocessor Interface Read Timing                           | 359     |

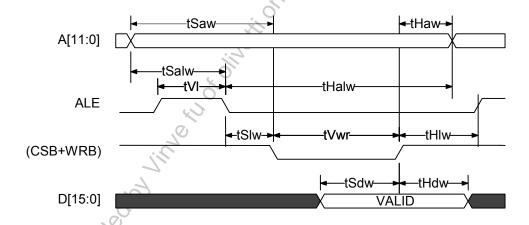

| Figure 22 Microprocessor Interface Write Timing                          | 361     |

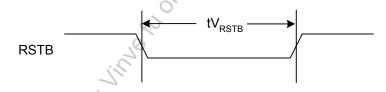

| Figure 23 RSTB Timing                                                    | 363     |

| Figure 24 Incoming TelecomBus Timing                                     | 365     |

| Figure 25 Outgoing TelecomBus Timing                                     | 368     |

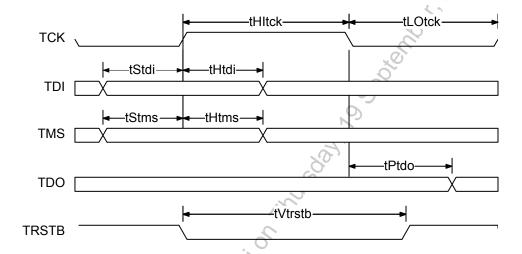

| Figure 26 JTAG Port Interface Timing                                     | 369     |

### **List of Tables**

|           | Serial TelecomBus 8B/10B Character Mapping                                   |     |

|-----------|------------------------------------------------------------------------------|-----|

| Table 2   | Serial TelecomBus 8B/10B character decoding                                  | 59  |

| Table 3 F | Register Memory Map                                                          | 65  |

| Table 4 T | WTI, TPTI, and TATI Mapping Modes                                            | 72  |

| Table 5 F | RWTI, RPTI, and RATI Mapping Modes                                           | 75  |

| Table 6   | Register configuration to select payload type for ITPP Generator and Monitor |     |

| Table 7   | Register configuration to select payload type for OTPG Generator             | 305 |

| Table 8   | Instruction Register (Length - 3 Bits)                                       | 321 |

| Table 9   | Instruction Register (Length - 3 Bits)                                       | 321 |

| Table 10  | Boundary Scan Register                                                       | 321 |

| Table 11  | Indirect Access Maximum BUSY Times                                           | 333 |

| Table 12  | Maximum Performance Monitor Counter Transfer Time                            | 334 |

| Table 14  | Standard Outgoing TelecomBus Timeslot Map                                    | 335 |

| Table 15  | Standard Incoming TelecomBus Timeslot Map                                    | 337 |

| Table 16  | Absolute Maximum Ratings                                                     | 354 |

| Table 16  | Power Requirements                                                           | 355 |

| Table 18  | D.C Characteristics                                                          | 357 |

| Table 19  | Microprocessor Interface Read Access (Figure 21)                             | 359 |

| Table 20  | Microprocessor Interface Write Access (Figure 22)                            | 361 |

| Table 21  | RSTB Timing (Figure 23)                                                      | 363 |

| Table 22  | TBS Incoming TelecomBus Timing (Figure 24)                                   | 363 |

| Table 23  | Outgoing TelecomBus Timing (Figure 25)                                       | 367 |

| Table 24  | JTAG Port Interface (Figure 26)                                              | 368 |

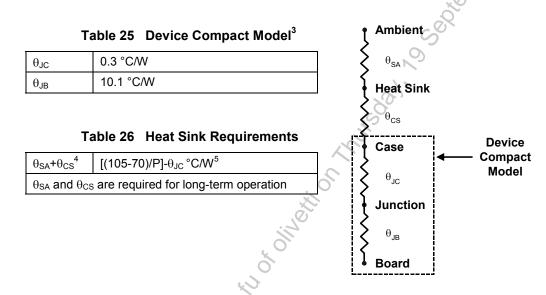

| Table 25  | Outside Plant Thermal Information                                            | 371 |

| Table 26  | Device Compact Model <sup>3</sup>                                            | 371 |

| Table 27  | Heat Sink Requirements                                                       | 371 |

#### 1 Features

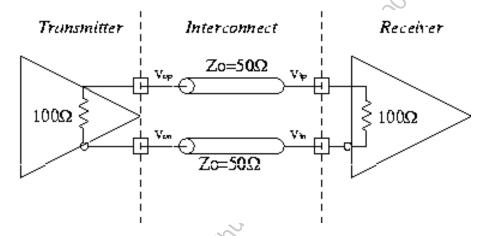

- Encodes data from the Incoming parallel TelecomBus to a set of four working, a set of four protection, and a set of four auxiliary 777.6MHz (622Mbps) LVDS serial TelecomBus links with extended 8B/10B-based encoding.

- Decodes data from a set of four working, a set of four protection, and a set of four auxiliary 777.6MHz LVDS serial links with extended 8B/10B-based encoding to the Outgoing parallel TelecomBus stream.

- Provides capacity to carry an STS-12/STM-4 stream in each LVDS serial TelecomBus link. Four links can be aggregated to form an STS-48c/STM-16c stream.

- Provides capacity to carry an STS-12/STM-4 stream in each 8-bit bus of the parallel TelecomBus stream. Four 8-bit buses can be aggregated to carry an STS-48c/STM-16c stream.

- Provides redundant working, protection and auxiliary transmit LVDS serial TelecomBus streams and redundant receive LVDS serial TelecomBus streams for protection switching purposes.

- Supports through-traffic, drop-traffic and protection switching in UPSR, 2-fibre BLSR and 4-fibre BLSR applications in conjunction with a peer PM5310 TBS or companion PM5372 TSE<sup>TM</sup> devices.

- Supports redundant working/protection time-space-time switch fabric.

- Provides Outgoing parallel TelecomBus selection of received Working, Protect, and Auxiliary data at STS-1 granularity.

- Provides independent time-slot interchange blocks on the Incoming and Outgoing parallel TelecomBus streams to allow arbitrary arrangement of time-slots at STS-1 granularity.

- Provides optional PRBS generation for each outgoing LVDS serial TelecomBus data link for off-line link verification.

- Provides optional PRBS generation for each 8-bit bus on the Outgoing parallel TelecomBus stream.

- Provides PRBS detection for each 8-bit bus on the Incoming parallel TelecomBus stream.

- Provides PRBS detection for each incoming LVDS serial TelecomBus stream for off-line link verification.

- Provides encoding of TelecomBus control signals at the multiplex section termination (MST) point and high-order path termination (HPT) point.

- Provides in-service link verification by optionally overwriting the B1 and E1 byte of each constituent STS-1/STM-0 with a unique software programmable byte and its complement.

- Uses extended 8B/10B-based line coding protocol on the serial links to provide transition density guarantee and DC balance and to offer a greater control character vocabulary than the standard 8B/10B protocol.

- Provides pins to coordinate updating of the connection map of the time-slot interchange blocks in the local device, peer TBS devices and companion PM5372 TSE devices.

- Derives all internal timing from a single 77.76MHz system clock.

- Provides a generic 16- bit microprocessor bus interface for configuration, control, and status monitoring.

- Implemented in 1.8V core and 3.3V I/O, 0.18μm CMOS and packaged in a 352 ball UBGA.

- Low power consumption of 2.82 W (typical)

### 2 Applications

- SONET/SDH Cross-connects

- SONET/SDH Add-Drop Multiplexers

- SONET/SDH Terminal Multiplexers

- TelecomBus Backplane Driver

#### 3 References

- 1. IEEE 802.3, "Carrier Sense Multiple Access with Collision Detection (CSMA/CD) Access Method and Physical Layer Specifications", Section 36.2, 1998.

- A.X. Widmer and P.A. Franaszek, "A DC-Balanced, Partitioned-Block, 8B/10B Transmission Code," IBM Journal of Research and Development, Vol. 27, No 5, September 1983, pp 440-451.

- 3. U.S. Patent No. 4,486,739, P.A. Franaszek and A.X. Widmer, "Byte Oriented DC Balanced (0,4) 8B/10B Partitioned Block Transmission Code," December 4, 1984.

- 4. Telcordia Technologies SONET Transport Systems: Common Generic Criteria, GR-253-CORE, Issue 2, September 2000.

- 5. ITU, Recommendation G.707 "Digital Transmission Systems Terminal equipments General", March 1996.

- 6. ITU, Rec Recommendation O.151 "Error Performance Measuring Equipment Operating at the Primary Rate and Above", October 1992.

- 7. PMC-1990736, Transmit 8B/10B TelecomBus Encoder Telecom System Block Engineering Document, Issue 2.

- 8. PMC-1990735, Receive 8B/10B TelecomBus Decoder Telecom System Block Engineering Document, Issue 2.

- 9. PMC-1990758, SONET/SDH Time Slot Interchange Telecom System Block Engineering Document, Issue 2.

- 10. PMC-1990848, Pseudo Random Bit Sequence (PRBS) Generator and Monitor Telecom System Block Engineering Document, Issue 2.

- 11. PMC-1990737, CSU1250 and TXLVREF\_1250 Analog Wrapper Telecom System Block Engineering Document, Issue 2.

#### 4 Definitions

| ADRU   | Auxiliary Data Recovery Unit                                                                      |

|--------|---------------------------------------------------------------------------------------------------|

| CSTR   | Clock Synthesis Unit (CSU)1250 and Transmit Low<br>Voltage Reference (TXLVREF)1250 Analog Wrapper |

| DLL    | Delay Lock Loop                                                                                   |

| DRU    | Data Recovery Unit                                                                                |

| FIFO   | First-In-First-Out storage element                                                                |

| ID8E   | Incoming Data 8B/10B Encoder                                                                      |

| ITPP   | Incoming TelecomBus PRBS Processor                                                                |

| IP8E   | Incoming PRBS 8B/10B Encoder                                                                      |

| LVDS   | Low Voltage Differential Signaling                                                                |

| OTPG   | Outgoing TelecomBus PRBS Generator                                                                |

| OT8D   | Outgoing TelecomBus 8B/10B Decoder                                                                |

| PDRU   | Protection Data Recovery Unit                                                                     |

| PISO   | Parallel to Serial Converter                                                                      |

| PRBS   | Pseudo-Random Bit Sequence                                                                        |

| PRGM   | SONET/SDH PRBS Generator/Monitor                                                                  |

| RALV   | Receive Auxiliary LVDS Interface                                                                  |

| RA8D   | Receive Auxiliary 8B/10B Decoder                                                                  |

| RAPM   | Receive Auxiliary PRBS Monitor                                                                    |

| RATI   | Receive Auxiliary Timeslot Interchange                                                            |

| RPLV   | Receive Protection LVDS Interface                                                                 |

| RP8D   | Receive Protection 8B/10B Decoder                                                                 |

| RPPM   | Receive Protection PRBS Monitor                                                                   |

| RPRM   | Receive PRBS Monitor                                                                              |

| RPTI   | Receive Protection Timeslot Interchange                                                           |

| RWLV   | Receive Working LVDS Interface                                                                    |

| RW8D   | Receive Working 8B/10B Decoder                                                                    |

| RWPM   | Receive Working PRBS Monitor                                                                      |

| RWTI   | Receive Working Timeslot Interchange                                                              |

| TADE O | Transmit Auxiliary Disparity Encoder                                                              |

| TALV   | Transmit Auxiliary LVDS Interface                                                                 |

| TAPS   | Transmit Auxiliary Serializer                                                                     |

| TATI   | Transmit Auxiliary Timeslot Interchange                                                           |

| TPDE   | Transmit Protection Disparity Encoder                                                             |

| TPLV   | Transmit Protection LVDS Interface                                                                |

| TPPS   | Transmit Protection Serializer                                                                    |

| TPTI | Transmit Protection Timeslot Interchange |

|------|------------------------------------------|

| TSI  | Timeslot Interchange                     |

| TWDE | Transmit Working Disparity Encoder       |

| TWLV | Transmit Working LVDS Interface          |

| TWPS | Transmit Working Serializer              |

| TWTI | Transmit Working Timeslot Interchange    |

| WDRU | Working Data Recovery Unit               |

### 5 Application Examples

Figure 1 Multi-Service ATM/POS Switch Port Application

Figure 2 2.5 Gb/s Multi-service ADM

#### 8 Description

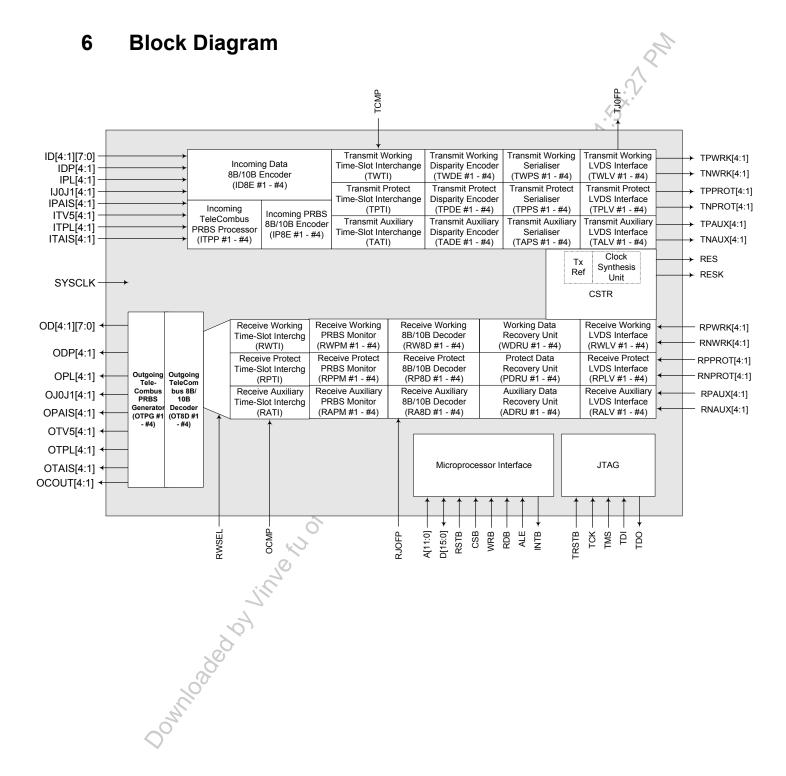

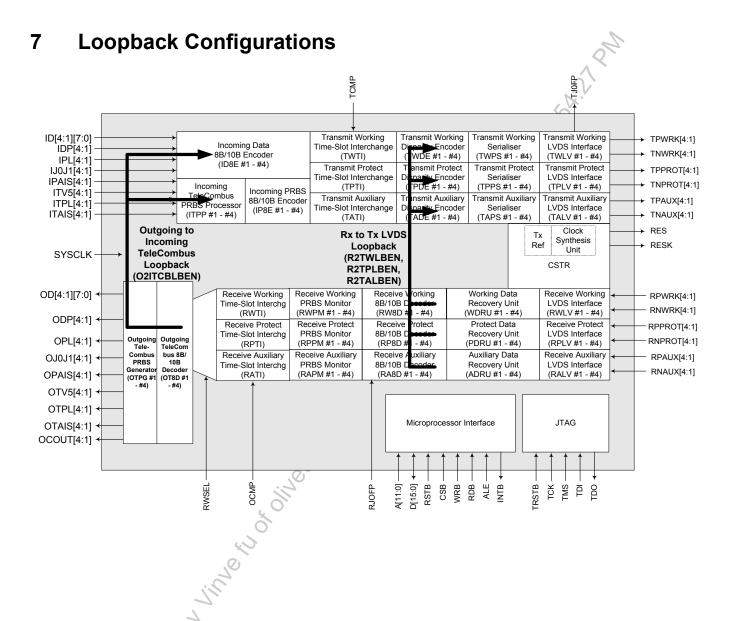

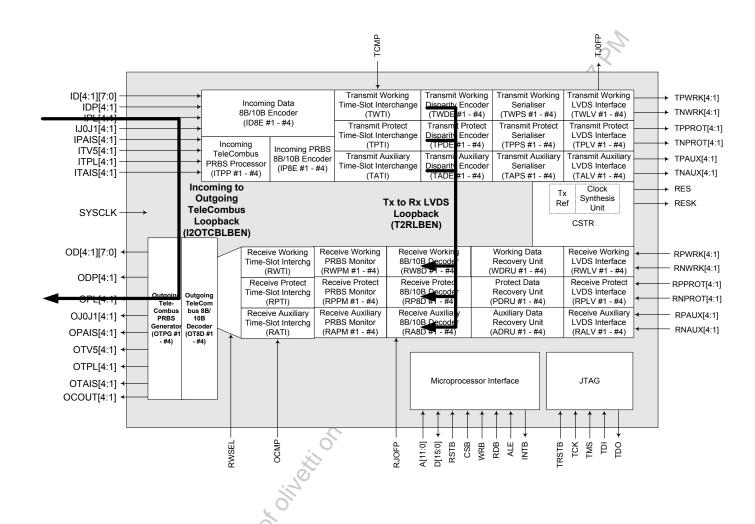

The PM5310 TBS TelecomBus Serializer is a monolithic integrated circuit that implements conversion between byte-serial parallel TelecomBus and bit-serial 8B/10B-based serial TelecomBus data formats. The TBS can be used to connect SONET/SDH framer devices (e.g. PM5315 SPECTRA-2488 <sup>TM</sup>) to ATM/POS processor devices (e.g. PM7390 S/UNI®-MACH48), or to SONET/SDH cross-connect devices (e.g. PM5372 TSE <sup>TM</sup>). It can also be used to connect SONET/SDH tributary unit processors (e.g. PM5363 TUPP+622 <sup>TM</sup>) and PDH mapper devices (e.g. PM8315 TEMUX <sup>TM</sup>) to SONET/SDH cross-connect devices (e.g. PM5372 TSE).

In the ingress direction, the TBS connects an incoming parallel TelecomBus stream to a set of three LVDS serial TelecomBus links. The incoming parallel TelecomBus can carry an STS-48/STM-16 stream or four STS-12/STM-4 streams that share a common clock, and a common transport frame alignment. Incoming data is encoded into an extended set of 8B/10B characters and transferred onto three independent sets of 777,6 MHz LVDS serial TelecomBus links. Transport and payload frame boundaries, pointer justification events and alarm conditions are marked by 8B/10B control characters. A pseudo-random bit sequence (PRBS) processor is provided to monitor the incoming payload for the  $X^{23} + X^{18} + 1$  pattern. Incoming payload bytes may be optionally overwritten with the locally generated PRBS pattern for diagnosis of downstream equipment. The PRBS processor is configurable to handle all legal mixes of STS-1/AU3, STS-3c/AU4, STS-12c/AU4-4c and STS-48c/AU4-16c in the incoming TelecomBus stream. Time-slot interchange blocks are provided to allow arbitrary mapping of streams on the incoming parallel TelecomBus stream to each of the three sets of LVDS serial TelecomBus links at STS-1/AU3 granularity. Multicast is supported.

In the egress direction, the TBS connects three independent sets of 777.6 MHz LVDS serial TelecomBus links to an outgoing TelecomBus stream. Each link contains a constituent STS-12/STM-4 of an STS-48/STM-16 stream. Bytes on the links are carried as 8B/10B characters. The TBS decodes the characters into TelecomBus data and control signals. A pseudorandom bit sequence (PRBS) processor is provided to monitor the decoded payload for the  $X^{23} + X^{18} + 1$  pattern. Decoded payload bytes may be optionally overwritten with the  $X^{23} + X^{18} + 1$  pattern for diagnosis of downstream equipment. The PRBS processor is configurable to handle all legal mixes of STS-1/AU3, STS-3c/AU4, STS-12c/AU4-4c and STS-48c/AU4-16c in the LVDS links. Data on the outgoing TelecomBus stream may be sourced from arbitrary time-slots of any of the three sets of LVDS links.

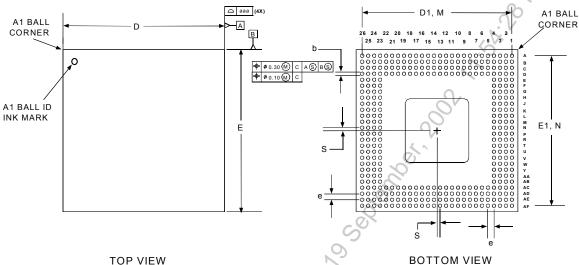

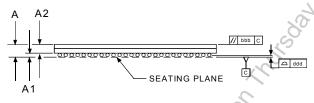

## 9 Pin Diagram

The TBS is packaged in a custom Ultra-BGA with 352 balls.

#### Figure 3 Pin Diagram

|    | 26            | 25            | 24            | 23            | 22       | 21       | 20       | 19       | 18      | 17       | 16       | 15       | 14       | 13        | 12       | 11       | 10       | 9        | 8        | 7        | 6        | 5        | 4        | 3        | 2        | 1        |    |

|----|---------------|---------------|---------------|---------------|----------|----------|----------|----------|---------|----------|----------|----------|----------|-----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----|

| Α  | VSS           | vss           | OCMP          | RSTB          | NC       | VDDI     | INTB     | NC       | VDDI    | A[3]     | A[6]     | A[9]     | VSS      | VSS       | D[0]     | D[3]     | NC       | D[9]     | VDDI     | D[15]    | OD[1][0] | OD[1][2] | OD[1][6] | ODP[1]   | VSS      | VSS      | A  |

| В  | VSS           | VDDO          | vss           | NC            | NC       | TRSTB    | TDO      | WRB      | RDB     | A[1]     | A[4]     | A[8]     | A[10]    | A[11]/TRS | D[1]     | D[5]     | D[7]     | D[11]    | D[14]    | OPL[1]   | VDDI     | OD[1][5] | OCOUT[1] | VSS      | VDDO     | VSS      | В  |

| С  | vss           | vss           | VDDO          | TCMP          | RWSEL    | тск      | NC       | NC       | NC      | ALE      | A[2]     | A[7]     | NC       | VDDI      | D[2]     | D[6]     | D[10]    | D[13]    | OJ0J1[1] | OD[1][1] | OD[1][4] | NC       | NC       | VDDO     | VSS      | OTPL[1]  | С  |

| D  | vss           | vss           | AVDH          | VDDO          | NC       | VDDI     | TMS      | TDI      | VDDO    | CSB      | A[0]     | A[5]     | NC       | VDDO      | D[4]     | D[8]     | D[12]    | NC       | VDDO     | OD[1][3] | OD[1][7] | NC       | VDDO     | OPAIS[1] | OTV5[1]  | VDDI     | D  |

| E  | vss           | RES           | AVDH          | RESK          |          |          |          |          |         |          |          |          |          |           |          |          |          |          |          |          |          |          | OTAIS[1] | IJOJ1[1] | ID[1][0] | ID[1][3] | E  |

| F  | RNWRK[1       | RPWRK[1       | RNWRK[2       | RPWRK[2<br>]  |          |          |          |          |         |          |          |          |          |           |          |          |          |          |          |          |          |          | IPL[1]   | ID[1][1] | ID[1][4] | ID[1][6] | F  |

| G  | vss           | RNWRK[3       | RPWRK[3       | AVDL          |          |          |          |          |         |          |          |          |          |           |          |          |          |          |          |          |          |          | ID[1][2] | ID[1][5] | ID[1][7] | IDP[1]   | G  |

| н  | RNWRK[4       | RPWRK[4       | TPWRK[1]      | TNWRK[1]      |          |          |          |          |         |          |          |          |          |           |          |          |          |          |          |          |          |          | VDDO     | VDDI     | IPAIS[1] | ITV5[1]  | н  |

| J  | vss           | TPWRK[2]      | TNWRK[2]      | AVDH          |          |          |          |          |         |          |          |          |          |           |          |          |          |          |          |          |          |          | NC       | ITAIS[1] | VDDI     | OPL[2]   | J  |

| K  | TPWRK[3]      | TNWRK[3]      | TPWRK[4]      | TNWRK[4]      |          |          |          |          |         |          |          |          |          |           |          |          |          |          |          |          |          |          | ITPL[1]  | OJ0J1[2] | OD[2][1] | OD[2][3] | ĸ  |

| L  | vss           | RNPROT[<br>1] | RPPROT[<br>1] | AVDL          |          |          |          |          |         |          |          |          |          |           |          |          |          |          |          |          |          |          | OD[2][0] | OD[2][2] | OD[2][4] | OD[2][6] | L  |

| М  | RNPROT[<br>2] | RPPROπ<br>2]  | RNPROT[<br>3] | RPPROT[<br>3] |          |          |          |          |         |          |          |          |          |           |          |          |          |          |          |          |          |          | OD[2][5] | OD[2][7] | осоит[2] | ODP[2]   | м  |

| N  | RNPROT[<br>4] | RPPROT[<br>4] | CSU_AVD       | CSU_AVD<br>H  |          |          |          |          |         |          |          |          |          |           |          |          |          |          |          |          |          |          | VDDO     | OPAIS[2] | OTAIS[2] | VSS      | N  |

| Р  | TPPROT[<br>1] | TNPROΤ[<br>1] | CSU_AVD       | CSU_AVD<br>L  |          |          |          |          |         |          |          |          |          |           |          |          |          |          |          |          |          |          | VDDI     | OTV5[2]  | OTPL[2]  | VSS      | Р  |

| R  | TPPROT[<br>3] | TNPROT[<br>3] | TPPROT[       | TNPROT[<br>2] |          |          |          |          |         |          |          |          |          |           |          |          |          |          |          |          |          |          | ID[2][2] | ID[2][0] | IPL[2]   | UOJ1[2]  | R  |

| т  | vss           | TPPROT[<br>4] | TNPROT[<br>4] | AVDH          |          |          |          |          |         |          |          |          |          |           |          |          |          |          |          |          |          |          | NC       | ID[2][4] | ID[2][3] | ID[2][1] | т  |

| U  | RNAUX[2]      | RPAUX[2]      | RNAUX[1]      | RPAUX[1]      |          |          |          |          |         |          |          |          |          |           |          |          |          |          |          |          |          |          | ITAIS[2] | ID[2][7] | ID[2][5] | VDDI     | U  |

| ٧  | vss           | RNAUX[3]      | RPAUX[3]      | AVDL          |          |          |          |          |         |          |          |          |          |           |          |          |          |          |          |          |          |          | VDDO     | ITPL[2]  | IDP[2]   | ID[2][6] | v  |

| w  | TPAUX[1]      | TNAUX[1]      | RNAUX[4]      | RPAUX[4]      |          |          |          |          |         |          |          |          |          |           |          |          |          |          |          |          |          |          | OD[3][0] | 0J0J1[3] | ITV5[2]  | IPAIS[2] | w  |

| Υ  | vss           | TPAUX[2]      | TNAUX[2]      | AVDH          |          |          |          |          |         |          |          |          |          |           |          |          |          |          |          |          |          |          | OD[3][4] | OD[3][1] | OPL[3]   | VDDI     | Υ  |

| AA | TPAUX[4]      | TNAUX[4]      | TPAUX[3]      | TNAUX[3]      |          |          |          |          |         |          |          |          |          |           |          |          |          |          |          |          |          |          | OD[3][7] | NC       | OD[3][2] | NC       | АА |

| АВ | vss           | ATB1          | AVDH          | ATB0          |          |          |          |          |         |          |          |          |          |           |          |          |          |          |          |          |          |          | ODP[3]   | NC       | OD[3][5] | OD[3][3] | ΑВ |

| AC | vss           | vss           | AVDH          | VDDO          | TJ0FP    | ITAIS[4] | ID[4][6] | VDDO     | NC      | NC       | NC       | OCOUT[4  | VDDO     | NC        | OPL[4]   | NC       | ID[3][7] | VDDO     | ID[3][2] | NC       | NC       | OTAIS[3] | VDDO     | NC       | VDDI     | OD[3][6] | AC |

| AD | VSS           | vss           | VDDO          | RJ0FP         | VDDI     | ID[4][7] | VDDI     | ID[4][1] | IPL[4]  | OTV5[4]  | OPAIS[4] | OD[4][6] | OD[4][3] | OD[4][1]  | SYSCLK   | ITV5[3]  | IPAIS[3] | ID[3][6] | ID[3][4] | VDDI     | IPL[3]   | OTV5[3]  | OPAIS[3] | VDDO     | VSS      | осоцт[3] | AD |

| ΑE | VSS           | VDDO          | vss           | ITPL[4]       | IDP[4]   | ID[4][4] | ID[4][2] | NC       | VDDI    | OTAIS[4] | NC       | OD[4][5] | NC       | OD[4][2]  | VDDI     | OJ0J1[4] | ITPL[3]  | IDP[3]   | VDDI     | NC       | ID[3][1] | VDDI     | OTPL[3]  | VSS      | VDDO     | VSS      | ΑE |

| AF | VSS           | vss           | ITV5[4]       | IPAIS[4]      | ID[4][5] | ID[4][3] | ID[4][0] | JJOJ1[4] | OTPL[4] | ODP[4]   | OD[4][7] | OD[4][4] | vss      | VSS       | OD[4][0] | NC       | NC       | ITAIS[3] | NC       | ID[3][5] | ID[3][3] | ID[3][0] | UOJ1[3]  | NC       | VSS      | VSS      | AF |

|    | 26            | 25            | 24            | 23            | 22       | 21       | 20       | 19       | 18      | 17       | 16       | 15       | 14       | 13        | 12       | 11       | 10       | 9        | 8        | 7        | 6        | 5        | 4        | 3        | 2        | 1        | •  |

Figure 4 Pin Diagram Top Left Corner

|   | 26          | 25             | 24                 | 23                 | 22    | 21    | 20   | 19  | 18   | 17   | 16   | 15   | 14    | ć   |

|---|-------------|----------------|--------------------|--------------------|-------|-------|------|-----|------|------|------|------|-------|-----|

| Α | VSS         | VSS            | OCMP               | RSTB               | NC    | VDDI  | INTB | NC  | VDDI | A[3] | A[6] | A[9] | VSS   | SX. |

| В | VSS         | VDDO           | VSS                | NC                 | NC    | TRSTB | TDO  | WRB | RDB  | A[1] | A[4] | A[8] | A[10] |     |

| С | VSS         | VSS            | VDDO               | ТСМР               | RWSEI | TCK   | NC   | NC  | NC   | ALE  | A[2] | A[7] | NC    |     |

| D | VSS         | VSS            | AVDH               | VDDO               | NC    | VDDI  | TMS  | TDI | VDDO | CSB  | A[0] | A[5] | NC    |     |