# SEMICONDUCTEURS SPECIFIQUES

## TSPC603E

#### DESCRIPTION

The PID6-603e implementation of PC603e (after named 603e) is a low-power implementation of reduced instruction set computer (RISC) microprocessors PowerPC<sup>™</sup> family. The 603e implements 32-bit effective addresses, integer data types of 8, 16 and 32 bits, and floating-point data types of 32 and 64 bits.

The 603e is a low-power 3.3-volt design and provides four software controllable power-saving modes.

The 603e is a superscalar processor capable of issuing and retiring as many as three instructions per clock. Instructions can execute out of order for increased performance; however, the 603e makes completion appear sequential. The 603e integrates five execution units and is able to execute five instructions in parallel.

The 603e provides independent on-chip, 16-Kbyte, four-way set-associative, physically addressed caches for instructions and data and on-chip instruction and data memory management units (MMUs). The MMUs contain 64-entry, two-way set-associative, data and instruction translation lookaside buffers that provide support for demand-paged virtual memory address translation and variable-sized block translation.

The 603e has a selectable 32 or 64-bit data bus and a 32-bit address bus. The 603e interface protocol allows multiple masters to complete for system resources through a central external arbiter. The 603e supports single-beat and burst data transfers for memory accesses, and supports memory-mapped I/O.

The 603e uses an advanced, 3.3-V CMOS process technology and maintains full interface compatibility with TTL devices.

The 603e integrates in system testability and debugging features through JTAG boundary-scan capability.

#### MAIN FEATURES

- 2.4 SPECint95, 2.1 SPECfp95 @ 100 MHz (estimated)

- Superscalar (3 instructions per clock peak).

- Dual 16KB caches.

- Selectable bus clock.

- 32-bit compatibility PowerPC implementation.

- On chip debug support.

- P<sub>D</sub> typical = 3.2 Watts (100 MHz), full operating conditions.

- Nap, doze and sleep modes for power savings.

- Branch folding.

- 64-bit data bus (32-bit data bus option).

- 4-Gbyte direct addressing range.

- Pipelined single/double precision float unit. IEEE 754 compatible FPU.

- IEEE P 1149-1 test mode (JTAG/C0P).

- f<sub>int</sub> max = 100/120/133 MHz.

- f<sub>bus</sub> max = 66 MHz.

- Compatible CMOS input TTL Output.

December1998

#### **SCREENING / QUALITY / PACKAGING**

This product is manufactured in full compliance with :

- MIL-STD-883 class B or According to TCS standards

- Upscreenings based upon TCS standards

- Full military temperature range (T<sub>c</sub> = -55°C, T<sub>c</sub> = +125°C) Industrial temperature range (T<sub>c</sub> = -40°C, T<sub>c</sub> = +110°C)

- $V_{CC} = 3.3 V \pm 5 \%$ .

- 240 pin Cerquad or 255 pin CBGA packages

#### SUMMARY

| Α.      | <u>GEN</u>   | IERAL                                | DESCRIPTION 3                                                                                                          |  |  |  |  |

|---------|--------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1.      | INTRODUCTION |                                      |                                                                                                                        |  |  |  |  |

| 2.      | PIN          | ASSIG                                | MENTS 4                                                                                                                |  |  |  |  |

|         | 2.1.         | CQFP                                 | 240 package 4                                                                                                          |  |  |  |  |

|         | 2.2.         | CBGA                                 | package 5                                                                                                              |  |  |  |  |

|         | 2.3.         | Pinout                               | listing 6                                                                                                              |  |  |  |  |

| ataShee | SIG          | NAL DE                               | SCRIPTION8                                                                                                             |  |  |  |  |

|         |              |                                      |                                                                                                                        |  |  |  |  |

| В.      | <u>DE1</u>   | AILED                                | SPECIFICATIONS 11                                                                                                      |  |  |  |  |

| 1.      | SCC          | PE                                   |                                                                                                                        |  |  |  |  |

| 2.      | APP          | LICABI                               | E DOCUMENTS 11                                                                                                         |  |  |  |  |

| 3.      | REC          | UIREM                                | ENTS 11                                                                                                                |  |  |  |  |

|         | 3.1.         | Genera                               | al 11                                                                                                                  |  |  |  |  |

|         | 3.2.         | Design<br>3.2.1.<br>3.2.2.<br>3.2.3. | and construction11Terminal connections11Lead material and finish11Package11                                            |  |  |  |  |

|         | 3.3.         | Absolu                               | te maximum ratings 11                                                                                                  |  |  |  |  |

|         | 3.4.         | Recom                                | mended operating conditions 11                                                                                         |  |  |  |  |

|         | 3.5.         | Therma<br>3.5.1.<br>3.5.2.           | al characteristics                                                                                                     |  |  |  |  |

|         | 3.6.         | 3.6.1.<br>3.6.2.<br>3.6.3.<br>3.6.4. | consideration14Dynamic Power Management14Programmable Power Modes14Power Management Modes14Power Management Software16 |  |  |  |  |

|         |              |                                      | Power dissipation 16                                                                                                   |  |  |  |  |

|         |              |                                      | g                                                                                                                      |  |  |  |  |

| 4.      |              |                                      | AL CHARACTERISTICS                                                                                                     |  |  |  |  |

|         |              |                                      | al requirements17                                                                                                      |  |  |  |  |

|         |              |                                      | characteristics17                                                                                                      |  |  |  |  |

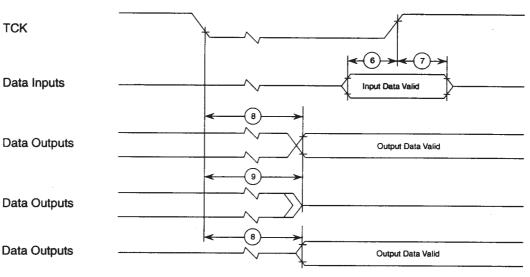

|         | 4.3.         | Dynam<br>4.3.1.<br>4.3.2.<br>4.3.3.  | ic characteristics18Clock AC specifications18Input AC specifications19Output AC specifications20                       |  |  |  |  |

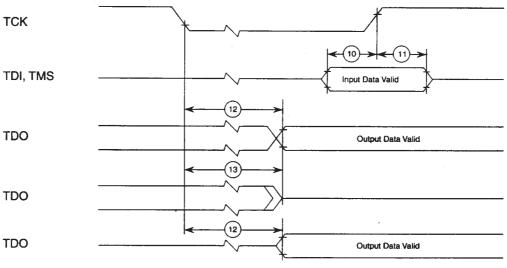

|    | 4.4.                     | JTAG A                                                                                | AC timing specifications                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|----|--------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 5. | FUN                      |                                                                                       | AL DESCRIPTION24                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

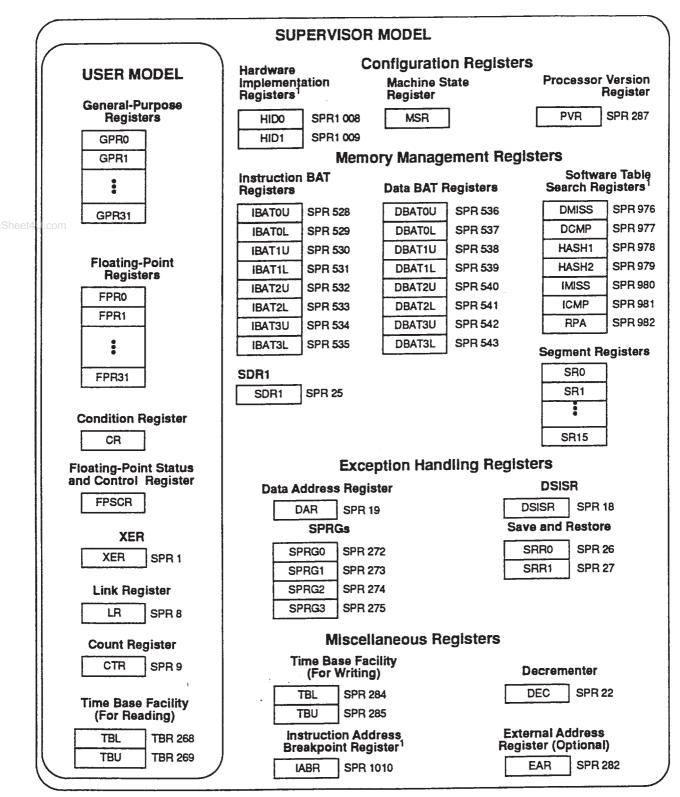

|    | 5.1.                     | Powerl<br>model<br>5.1.1.<br>5.1.2.<br>5.1.3.<br>5.1.4.<br>5.1.5.<br>5.1.6.<br>5.1.7. | PC registers and programming<br>General-Purpose Registers (GPRs) 24<br>Floating-Point Registers (FPRs) 24<br>Condition Register (CR) 24<br>Floating-Point Status and Control Register<br>(FPSC) 24<br>Machine State Register (MSR) 24<br>Segment Registers (SRs) 24<br>Special-Purpose Registers (SPRs) 24 |  |  |  |  |  |

|    | 5.2.                     | Instruc<br>5.2.1.<br>5.2.2.                                                           | tion set and addressing modes 27<br>PowerPC instruction set and addressing<br>modes                                                                                                                                                                                                                        |  |  |  |  |  |

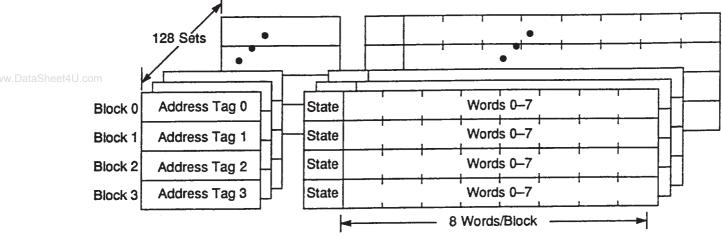

|    | 5.3.                     | Cache<br>5.3.1.<br>5.3.2.                                                             | implementation28PowerPC cache characteristics28PowerPC 603e microprocessor cache28implementation28                                                                                                                                                                                                         |  |  |  |  |  |

|    | 5.4.                     | Except<br>5.4.1.<br>5.4.2.                                                            | ion model                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

|    | 5.5.                     | Memor<br>5.5.1.<br>5.5.2.                                                             | y management                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|    | 5.6.                     | Instruc                                                                               | tion timing                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| 6. | PRE                      | PARAT                                                                                 | ION FOR DELIVERY                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|    | 6.1.                     | Packag                                                                                | ging                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|    | 6.2.                     | Certific                                                                              | ate of compliance                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| 7. | HAN                      | IDLING                                                                                |                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

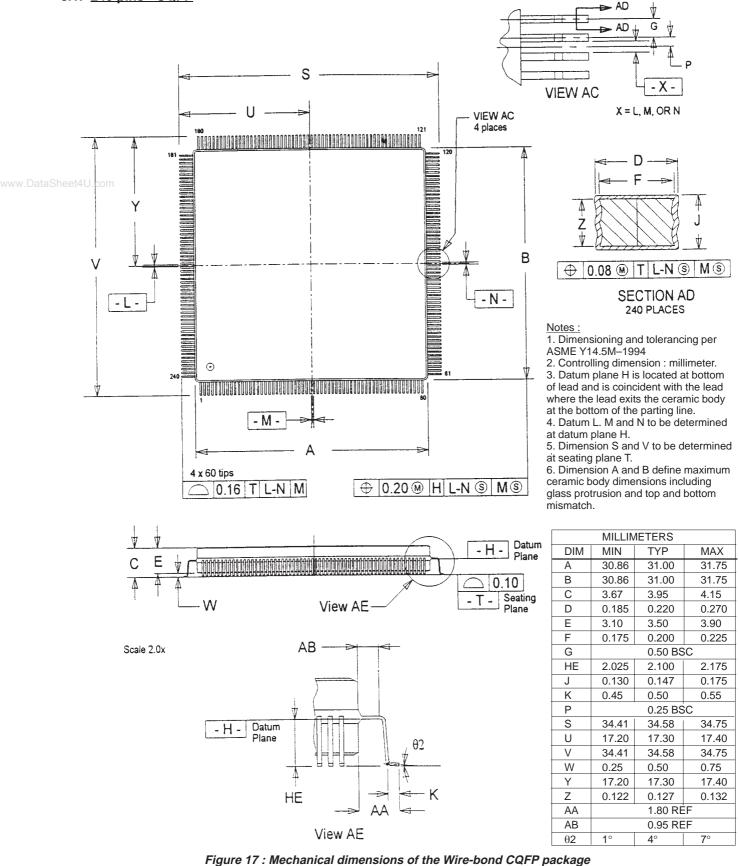

| 8. | PAC                      | KAGE                                                                                  | MECHANICAL DATA35                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|    | 8.1.                     | 240 pir                                                                               | ns - CQFP 35                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

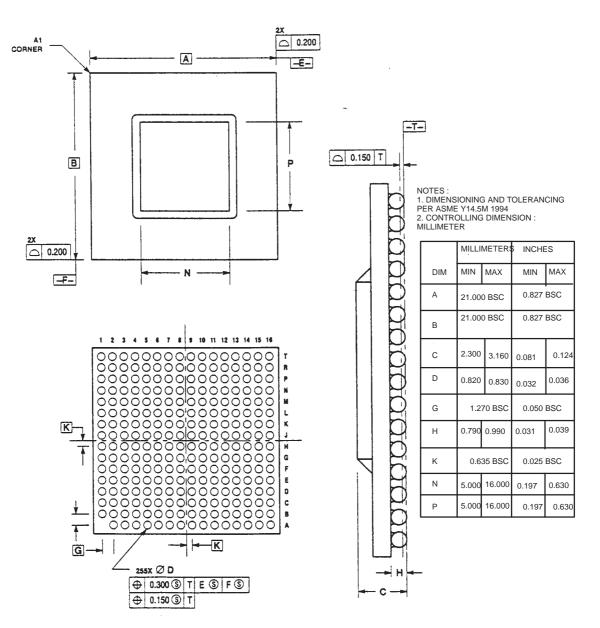

|    | 8.2.                     | BGA pa<br>8.2.1.<br>8.2.2.                                                            | ackage description36Package parameters36Mechanical dimensions of the BGA package36                                                                                                                                                                                                                         |  |  |  |  |  |

| 9. | CLO                      | CK RE                                                                                 | LATIONSHIPS CHOICE                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| 10 | 10. ORDERING INFORMATION |                                                                                       |                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

SEMICONDUCTEURS SPECIFIQUES

### A. GENERAL DESCRIPTION

ww.DataSheet4U.com

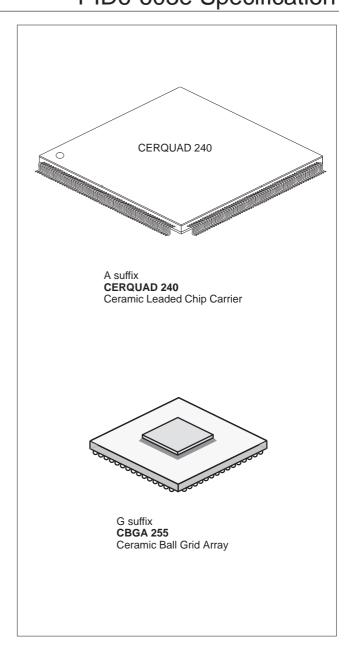

Figure 1 : Block diagram

#### 1. INTRODUCTION

The 603e is a low-power implementation of the PowerPC microprocessor family of reduced instruction set commuter (RISC) microprocessors. The 603e implements the 32-bit portion of the PowerPC architecture, which provides 32-bit effective addresses, integer data types of 8, 16 and 32 bits, and floating-point data types of 32 and 64 bits. For 64-bit PowerPC microprocessors, the PowerPC architecture provides 64-bit integer data types, 64-bit addressing, and other features required to complete the 64-bit architecture.

The 603e provides four software controllable power-saving modes. Three of the modes (the nap, doze, and sleep modes) are static in nature, and progressively reduce the amount of power dissipated by the processor. The fourth is a dynamic power management mode that causes the functional units in the 603e to automatically enter a low-power mode when the functional units are idle without affecting operational performance, software execution, or any external hardware.

The 603e is a superscalar processor capable of issuing and retiring as many as three instructions per clock. Instructions can execute out of order for increased performance ; however, the 603e makes completion appear sequential.

The 603 e integrates five execution units - an integer unit (IU), a floating-point unit (FPU), a branch processing unit (BPU), a load/store unit (LSU) and a system register unit (SRU). The ability to execute five instructions in parallel and the use of simple instructions with rapid execution times yield high efficiency and throughput for 603e-based systems. Most integer instructions execute in one clock cycle. The FPU is pipelined so a single-precision multiply-add instruction can be issued every clock cycle.

The 603e provides independent on-chip, 16 Kbyte, four-way set-associative, physically addressed caches for instructions and data and on-chip instruction and data memory management units (MMUs). The MMUs contain 64-entry, two-way set-associative, data and instruction translation lookaside buffers (DTLB and ITLB) that provide support for demand-paged virtual memory address translation and variable-sized block translation. The TLBs and caches use a least recently used (LRU) replacement algorithm. The 603e also supports block address translation through the use of two independent instruction and data block address translation (IBAT and DBAT) arrays of four entries each. Effective addresses are compared simultaneously with all four entries in the BAT array during block translation. In accordance with the PowerPC architecture, if an effective address hits in both the TLB and BAT array, the BAT translation takes priority.

The 603e has a selectable 32 - or 64-bit - data bus and a 32-bit address bus. The 603e interface protocol allows multiple masters to compete for system resources through a central external arbiter. The 603e provides a three-state coherency protocol that supports the exclusive, modified, and invalid cache states. This protocol as a compatible subset of the MESI (modified/exclusive/shared/invalid) four-state protocol and operates coherently in systems that contain four-state caches. The 603e supports single-beat and burst data transfers for memory accesses, and supports memory-mapped I/O.

The 603e uses an advanced, 3.3 V CMOS process technology and maintains full interface compatibility with TTL devices.

THOMSON-CSF SEMICONDUCTEURS SPECIFIQUES

#### 2. PIN ASSIGNMENTS

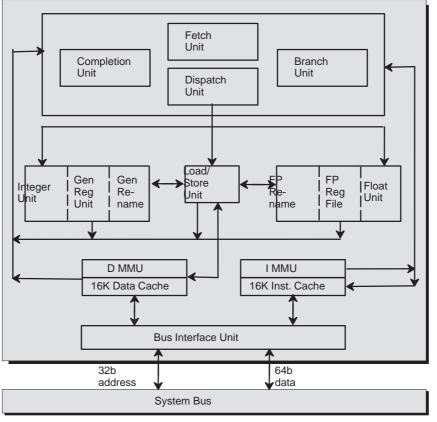

2.1. CQFP 240 package

Figure 2 : CQFP 240 : Top view

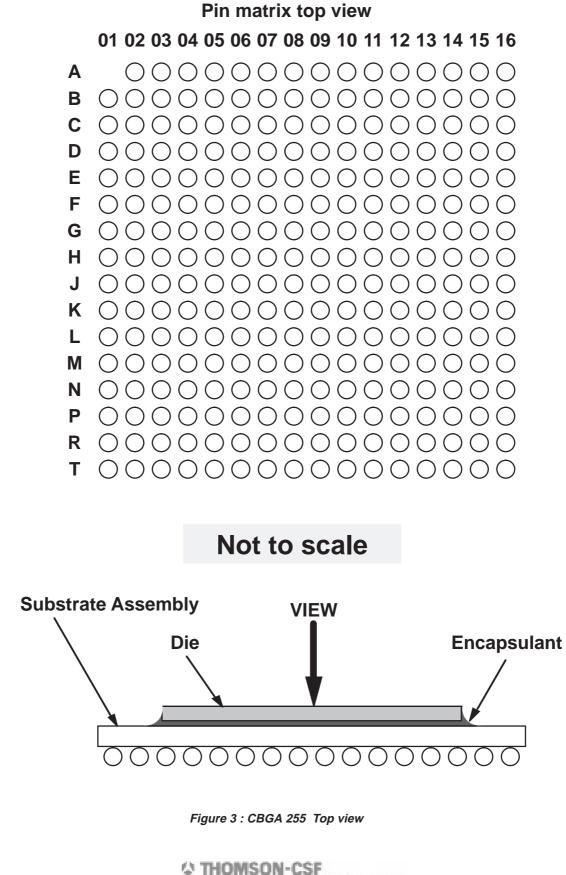

#### 2.2. CBGA255 package

Figure 3 (pin matrix) shows the pinout as viewed from the top of the CBGA package. The direction of the top surface view is shown by the side profile of the CBGA package.

SEMICONDUCTEURS SPECIFIQUES

ww.DataSheet4U.com

#### 2.3. Pinout listing

| Table 1 | : | Power | and | ground | pins |

|---------|---|-------|-----|--------|------|

|---------|---|-------|-----|--------|------|

|                | CQFP240 package                                                                                                     |                                                                                                                 | CBGA255 package                                                                                                |                                                                                                                           |  |

|----------------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--|

|                | VCC                                                                                                                 | GND                                                                                                             | vcc                                                                                                            | GND                                                                                                                       |  |

| PLL (AVDD)     | 209                                                                                                                 |                                                                                                                 | A10                                                                                                            |                                                                                                                           |  |

| Internal logic | 4, 14, 24, 34, 44, 59,<br>122, 137, 147, 157, 167,<br>177, 207                                                      | 9, 19,29, 39, 49, 65, 116,<br>132, 142, 152, 162, 172,<br>182, 206, 239                                         | F06, F08, F09, F11, G07,<br>G10, H06, H08, H09,<br>H11, J06, J08, J09, J11,<br>K07, K10, L06, L08, L09,<br>L11 | C05, C12, E03, E06,<br>E08, E09, E11, E14, F05,<br>F07, F10, F12, G06,<br>G08, G09, G11, H05,<br>H07, H10, H12, J05, J07, |  |

| Output drivers | 10, 20, 35, 45, 54, 61,<br>70, 79, 88, 96, 104, 112,<br>121, 128, 138, 148, 163,<br>173, 183, 194, 222, 229,<br>240 | 8, 18, 33, 43, 53, 60, 69,<br>77, 86, 95, 103, 111, 120,<br>127, 136, 146, 161, 171,<br>181, 193, 220, 228, 238 | C07, E05, E07, E10,<br>E12, G03, G05, G12,<br>G14, K03, K05, K12,<br>K14, M05, M07, M10,<br>M12, P07, P10      | J10, J12, K06, K08, K09,<br>K11, L05, L07, L10, L12,<br>M03, M06, M08, M09,<br>M11, M14, P05, P12                         |  |

| Signal name | CQFP Pin number                                                                                                                                                | CBGA Pin number                                                                                                                                                            | Active | I/O    |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|

| A[0-31]     | 179, 2, 178, 3, 176, 5, 175, 6, 174, 7,<br>170, 11, 169, 12, 168, 13, 166, 15, 165,<br>16, 164, 17, 160, 21, 159, 22, 158, 23,<br>151, 30, 144, 37             | C16, E04, D13, F02, D14, G01, D15,<br>E02, D16, D04, E13, G02, E15, H01,<br>E16, H02, F13, J01, F14, J02, F15, H03,<br>F16, F04, G13, K01, G15, K02, H16,<br>M01, J15, P01 | High   | I/O    |

| AACK        | 28                                                                                                                                                             | L02                                                                                                                                                                        | Low    | Input  |

| ABB         | 36                                                                                                                                                             | K04                                                                                                                                                                        | Low    | I/O    |

| AP[0-3]     | 231,230,227,226                                                                                                                                                | C01, B04, B03, B02                                                                                                                                                         | High   | I/O    |

| APE         | 218                                                                                                                                                            | A04                                                                                                                                                                        | Low    | Output |

| ARTRY       | 32                                                                                                                                                             | J04                                                                                                                                                                        | Low    | I/O    |

| BG          | 27                                                                                                                                                             | L01                                                                                                                                                                        | Low    | Input  |

| BR          | 219                                                                                                                                                            | B06                                                                                                                                                                        | Low    | Output |

| टा          | 237                                                                                                                                                            | E01                                                                                                                                                                        | Low    | Output |

| CKSTP_IN    | 215                                                                                                                                                            | D08                                                                                                                                                                        | Low    | Input  |

| CKSTP_OUT   | 216                                                                                                                                                            | A06                                                                                                                                                                        | Low    | Output |

| CLK_OUT     | 221                                                                                                                                                            | D07                                                                                                                                                                        | -      | Output |

| CSE[0-1]    | 225,150                                                                                                                                                        | B01, B05                                                                                                                                                                   | High   | Output |

| DBB         | 145                                                                                                                                                            | J14                                                                                                                                                                        | Low    | I/O    |

| DBG         | 26                                                                                                                                                             | N01                                                                                                                                                                        | Low    | Input  |

| DBDIS       | 153                                                                                                                                                            | H15                                                                                                                                                                        | Low    | Input  |

| DBWO        | 25                                                                                                                                                             | G04                                                                                                                                                                        | Low    | Input  |

| DH[0-31]    | 115, 114, 113, 110, 109, 108, 99, 98,<br>97, 94, 93, 92, 91, 90, 89, 87, 85,<br>84, 83, 82, 81, 80, 78, 76, 75, 74,<br>73, 72, 71, 68, 67, 66                  | P14, T16, R15, T15, R13, R12, P11,<br>N11, R11, T12, T11, R10, P09, N09,                                                                                                   |        | I/O    |

| DL[0-31]    | 143, 141, 140, 139, 135, 134, 133, 131,<br>130, 129, 126, 125, 124, 123, 119, 118,<br>117, 107, 106, 105, 102, 101, 100, 51,<br>52, 55, 56, 57, 58, 62, 63, 64 | K13, K15, K16, L16, L15, L13, L14,<br>M16, M15, M13, N16, N15, N13, N14,<br>P16, P15, R16, R14, T14, N10, P13,<br>N12, T13, P03, N03, N04, R03, T01,<br>T02, P04, T03, R04 | High   | I/O    |

| Signal name                        | CQFP Pin number                | CBGA Pin number                                     | Active | I/O    |

|------------------------------------|--------------------------------|-----------------------------------------------------|--------|--------|

| DP[0-7]                            | 38, 40, 41, 42, 46, 47, 48, 50 | M02, L03, N02, L04, R01, P02, M04,<br>R02           | High   | I/O    |

| DPE                                | 217                            | A05                                                 | Low    | Output |

| DRTRY                              | 156                            | G16                                                 | Low    | Input  |

| GBL                                | 1                              | F01                                                 | Low    | I/O    |

| HRESET                             | 214                            | A07                                                 | Low    | Input  |

| INT                                | 188                            | B15                                                 | Low    | Input  |

| L1_TSTCLK1                         | 204                            | D11                                                 | -      | Input  |

| L2 <sub></sub> TSTCLK <sup>1</sup> | 203                            | D12                                                 | -      | Input  |

| LSSD_MODE <sup>1</sup>             | 205                            | B10                                                 | Low    | Input  |

| MCP                                | 186                            | C13                                                 | Low    | Input  |

| PLL_CFG[0-3]                       | 213, 211, 210, 208             | A08, B09, A09, D09                                  | High   | Input  |

| QACK                               | 235                            | D03                                                 | Low    | Input  |

| QREQ                               | 31                             | J03                                                 | Low    | Outpu  |

| RSRV                               | 232                            | D01                                                 | Low    | Outpu  |

| SMI                                | 187                            | A16                                                 | Low    | Input  |

| SRESET                             | 189                            | B14                                                 | Low    | Input  |

| SYSCLK                             | 212                            | C09                                                 | -      | Input  |

| TA                                 | 155                            | H14                                                 | Low    | Input  |

| TBEN                               | 234                            | C02                                                 | High   | Input  |

| TBST                               | 192                            | A14                                                 | Low    | I/O    |

| TC[0–1]                            | 224, 223                       | A02, A03                                            | High   | Outpu  |

| ТСК                                | 201                            | C11                                                 | -      | Input  |

| TDI                                | 199                            | A11                                                 | High   | Input  |

| TDO                                | 198                            | A12                                                 | High   | Outpu  |

| TEA                                | 154                            | H13                                                 | Low    | Input  |

| TLBISYNC                           | 233                            | C04                                                 | Low    | Input  |

| TMS                                | 200                            | B11                                                 | High   | Input  |

| TRST                               | 202                            | C10                                                 | Low    | Input  |

| TS                                 | 149                            | J13                                                 | Low    | I/O    |

| TSIZ[0-2]                          | 197, 196, 195                  | A13, D10, B12                                       | High   | I/O    |

| TT[0-4]                            | 191, 190, 185, 184, 180        | B13, A15, B16, C14, C15                             | High   | I/O    |

| WT                                 | 236                            | D02                                                 | Low    | Outpu  |

| NC                                 |                                | B07, B08, C03, C06, C08, D05, D06,<br>F03, H04, J16 | Low    | Input  |

#### Notes :

1. These are test signals for factory use only and must be pulled up to VDD for normal machine operation.

2. OVDD inputs supply power to the I/O drivers and VDD inputs supply power to the processor core. Future members of the 603 family may use different OVDD and VDD input levels.

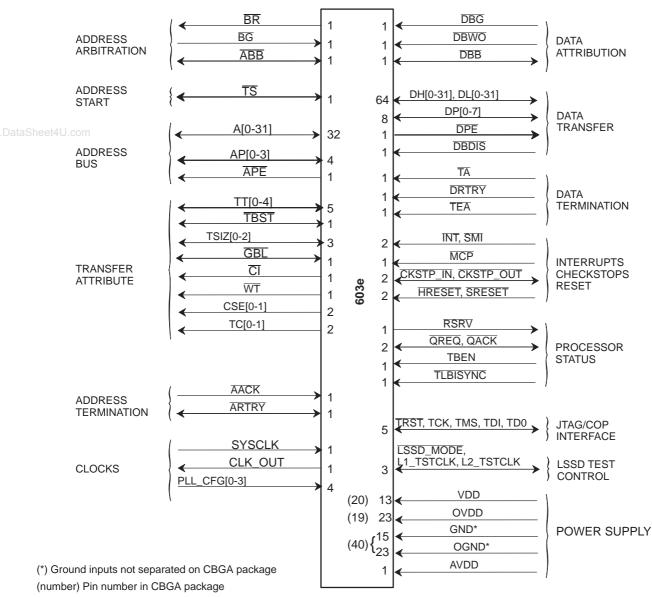

#### 3. SIGNAL DESCRIPTION

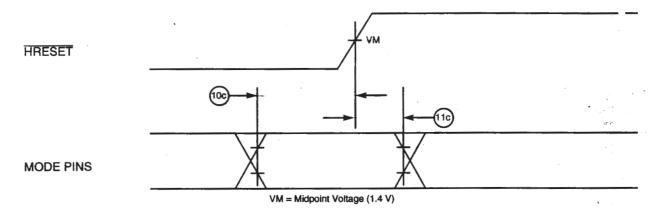

Figure 4, Table 3 and Table 4 describe the signal on the TSPC603e and indicate signal functions. The test signals, TRST, TMS, TCK, TDI and TDO, comply with subset P-1149.1 of the IEEE testability bus standard.

The 3 signals <u>LSSD\_MODE</u>, LI\_TSTCLK and L2\_TSTCLK are test signals for factory use only and must be pulled up to VDD for normal machine operations.

Figure 4 : Functional signal groups

| Signal name | Mnemonic | Signal function                                                                                                           | Signal<br>type |

|-------------|----------|---------------------------------------------------------------------------------------------------------------------------|----------------|

| Address bus | A[0-31]  | if output, physical address of data to be transferred.<br>if input, represents the physical address of a snoop operation. | I/O            |

| Data bus    | DH[0-31] | Represents the state of data, during a data write operation if output, or during a data read operation if input.          | I/O            |

| Data bus    | DL[0-31] | Represents the state of data, during a data write operation if output, or during a data read operation if input.          | I/O            |

Table 4 : Signal index

| Signal name          | Mnemonic  | Signal function                                                                                                                                                                                             | Signal<br>type |  |

|----------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--|

| Address Acknowledge  | AACK      | The address phase of a transaction is complete                                                                                                                                                              | Input          |  |

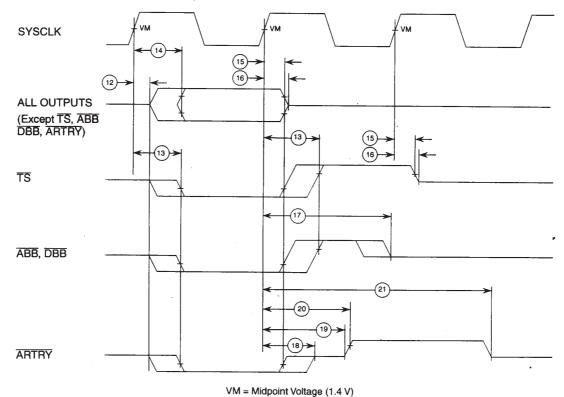

| Address Bus Busy     | ABB       | If output, the 603e is the address bus master<br>If input, the address bus is in use                                                                                                                        | I/O            |  |

| Address Bus Parity   | AP[0-3]   | If output, represents odd parity for each of 4 bytes of the physical<br>address for a transaction<br>If input, represents odd parity for each of 4 bytes of the physical address<br>for snooping operations |                |  |

| Address Parity Error | APE       | Incorrect address bus parity detected on a snoop                                                                                                                                                            | Output         |  |

| Address retry        | ARTRY     | If output, detects a condition in which a snooped address tenure must be retried<br>If input, must retry the preceding address tenure                                                                       | I/O            |  |

| Bus grant            | BG        | May, with the proper qualification, assume mastership of the address bus                                                                                                                                    | Input          |  |

| Bus request          | BR        | Request mastership of the address bus                                                                                                                                                                       | Output         |  |

| Cache Inhibit        | CI        | A single-beat transfer will not be cached                                                                                                                                                                   | Output         |  |

| Test Clock           | CLK_OUT   | Provides PLL clock output for PLL testing and monitoring                                                                                                                                                    | Output         |  |

| Checkstop Input      | CKSTP_IN  | Must terminate operation by internally gating off all clocks, and release all outputs                                                                                                                       | Input          |  |

| Checkstop Output     | CKSTP_OUT | Has detected a checkstop condition and has ceased operation                                                                                                                                                 | Output         |  |

| Cache Set Entry      | CSE[0-1]  | Cache replacement set element for the current transaction reloading into or writing out of the cache                                                                                                        |                |  |

| Data Bus Busy        | DBB       |                                                                                                                                                                                                             |                |  |

| Data Bus Disable     | DBDIS     | (For a write transaction) must release data bus and the data bus parity to high impedance during the following cycle                                                                                        | Input          |  |

| Data Bus Grant       | DBG       | May, with the proper qualification, assume mastership of the data bus                                                                                                                                       | Input          |  |

| Data Bus Write Only  | DBW0      | May run the data bus tenure                                                                                                                                                                                 | Input          |  |

| Data Bus Parity      | DP[0-7]   | If output, odd parity for each of 8 bytes of data write transactions<br>If input, odd parity for each byte of read data                                                                                     | I/O            |  |

| Data Parity Error    | DPE       | Incorrect data bus parity                                                                                                                                                                                   | Output         |  |

| Data Retry           | DRTRY     | Must invalidate the data from the previous read operation                                                                                                                                                   | Input          |  |

| Global               | GBL       | If output, a transaction is global<br>If input, a transaction must be snooped by the 603e                                                                                                                   | I/O            |  |

| Hard Reset           | HRESET    | Initiates a complete hard reset operation                                                                                                                                                                   | Input          |  |

| Interrupt            | INT       | Initiates an interrupt if bit EE of MSR register is set                                                                                                                                                     | Input          |  |

|                      | LSSD_MODE | LSSD test control signal for factory use only                                                                                                                                                               | Input          |  |

|                      | L1_TSTCLK | LSSD test control signal for factory use only                                                                                                                                                               | Input          |  |

| Signal name                                                                                                                                                                                                                                                                           | Mnemonic     | Signal function                                                                                                   | Signal<br>type |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------------------------------------------------------------------------------------------------------------|----------------|--|

|                                                                                                                                                                                                                                                                                       | L2_TSTCLK    | LSSD test control signal for factory use only                                                                     | Input          |  |

| Machine Check Inter-<br>rupt                                                                                                                                                                                                                                                          | MCP          | Initiates a machine check interrupt operation if the bit ME of MSR register and bit EMCP of HID0 register are set | Input          |  |

| PLL Configuration                                                                                                                                                                                                                                                                     | PLL_CFG[0-3] | Configures the operation of the PLL and the internal processor clock frequency                                    | Input          |  |

| Quiescent<br>Acknowledge                                                                                                                                                                                                                                                              | QACK         | All bus activity has terminated and the 603e may enter a quiescent (or low power) state                           | Input          |  |

| Quiescent Request                                                                                                                                                                                                                                                                     | QREQ         | Is requesting all bus activity normally to enter a quiescent (low power) state                                    | Output         |  |

| Reservation                                                                                                                                                                                                                                                                           | RSRV         | Represents the state of the reservation coherency bit in the reservation address register                         | Output         |  |

| System Management<br>Interrupt                                                                                                                                                                                                                                                        | SMI          | Initiates a system management interrupt operation if the bit EE of MSR register is set                            | Input          |  |

| Soft Reset                                                                                                                                                                                                                                                                            | SRESET       | Initiates processing for a reset exception                                                                        | Input          |  |

| System Clock                                                                                                                                                                                                                                                                          | SYSCLK       | Represents the primary clock input for the 603e, and the bus clock fre-<br>quency for 603e bus operation          | Input          |  |

| Transfer Acknowledge                                                                                                                                                                                                                                                                  | TA           | TA A single-beat data transfer completed successfully or a data beat in a burst transfer completed successfully   |                |  |

| Timebase Enable                                                                                                                                                                                                                                                                       | TBEN         | The timebase should continue clocking                                                                             |                |  |

| Transfer Burst                                                                                                                                                                                                                                                                        | TBST         | If output, a burst transfer is in progress<br>If input, when snooping for single-beat reads                       |                |  |

| Transfer Code                                                                                                                                                                                                                                                                         | TC[0-1]      | Special encoding for the transfer in progress                                                                     | Output         |  |

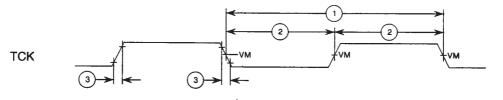

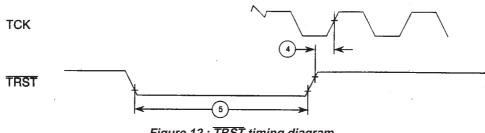

| Test clock                                                                                                                                                                                                                                                                            | тск          | Clock signal for the IEEE P1149.1 test access port (TAP)                                                          | Input          |  |

| Test data input                                                                                                                                                                                                                                                                       | TDI          | Serial data input for the TAP                                                                                     | Input          |  |

| Test data output                                                                                                                                                                                                                                                                      | TDO          | Serial data output for the TAP                                                                                    | Output         |  |

| Transfer Error<br>Acknowledge                                                                                                                                                                                                                                                         | TEA          | A bus error occurred                                                                                              | Input          |  |

| TLBI Sync                                                                                                                                                                                                                                                                             | TLBISYNC     | Instruction execution should stop after execution of a <b>tlbsync</b> instruction                                 | Input          |  |

| Test mode select                                                                                                                                                                                                                                                                      | TMS          | Selects the principal operations of the test-support circuitry                                                    | Input          |  |

| Test reset                                                                                                                                                                                                                                                                            | TRST         | Provides an asynchronous reset of the TAP controller                                                              | Input          |  |

| Transfer Size                                                                                                                                                                                                                                                                         | TSIZ[0-2]    | For memory accesses, these signals along with TBST indicate the data transfer size for the current bus operation  | I/O            |  |

| Transfer start       TS       If output, begun a memory bus transaction and the address bus and transfer attribute signals are valid         If input, another master has begun a bus transaction and the address bus and transfer attribute signals are valid for snooping (see GBL) |              | transfer attribute signals are valid                                                                              | I/O            |  |

| Transfer Type                                                                                                                                                                                                                                                                         | TT[0-4]      | Type of transfer in progress                                                                                      | I/O            |  |

| Write-Through                                                                                                                                                                                                                                                                         | WT           | A single-beat transaction is write-through                                                                        | Output         |  |

## SEMICONDUCTEURS SPECIFIQUES

#### **B. DETAILED SPECIFICATIONS**

#### 1. SCOPE

This drawing describes the specific requirements for the microprocessor TSPC603e, in compliance with MIL-STD-883 class B or TCS standard screening.

#### 2. APPLICABLE DOCUMENTS

1) MIL-STD-883 : Test methods and procedures for electronics.

2) MIL-PRF-38535 appendix A : General specifications for microcircuits.

#### 3. REQUIREMENTS

.DataSheet4U.com

#### 3.1. <u>General</u>

The microcircuits are in accordance with the applicable documents and as specified herein.

#### 3.2. Design and construction

#### 3.2.1. Terminal connections

Depending on the package, the terminal connections shall be is shown in Figure 2 and Figure 4 (§ A. GENERAL DESCRIPTION).

#### 3.2.2. Lead material and finish

Lead material and finish shall be as specified in MIL-STD-1835 (see enclosed § 8)

#### 3.2.3. Hermetic Package

The macrocircuits are packaged in 240 pin ceramic quad flat packages (see § 8.1) The precise case outlines are described at the end of the specification (§ 8.1) and into MIL-STD-1835.

#### 3.3. Absolute maximum ratings

Absolute maximum ratings are stress ratings only, and functional operation at the maximums is not guaranteed. Stresses beyond those listed may affect device reliability or cause permanent damage to the device.

| Parameter                      | Symbol           | Min  | Мах  | Unit |

|--------------------------------|------------------|------|------|------|

| Core supply voltage            | V <sub>DD</sub>  | -0.3 | 4.0  | V    |

| P <sub>LL</sub> supply voltage | AV <sub>DD</sub> | -0.3 | 4.0  | V    |

| I/O supply voltage             | OV <sub>DD</sub> | -0.3 | 4.0  | V    |

| Input voltage                  | V <sub>in</sub>  | -0.3 | 5.5  | V    |

| Storage temperature range      | T <sub>stg</sub> | -55  | +150 | °C   |

#### Table 5 : Absolute maximum rating for the 603e

Note 1: Functional operating conditions are given in AC and DC electrical specifications. Stresses beyond the absolute maximums listed may affect device reliability or cause permanent damage to the device.

Note 2: Caution : Input voltage must not be greater than the OVDD supply voltage by more than 2.5 V at all times including during power-on reset.

Note 3 : Caution : OVDD voltage must not be greater than AVDD supply voltage by more than 2.5 V at all times including during power-on reset.

Note 4: Caution : AVDD voltage must not be greater than OVDD supply voltage by more than 0.4 V at all times including during power-on reset.

#### 3.4. <u>Recommended operating conditions</u>

These are the recommended and tested operating conditions. Proper device operation outside of these conditions is not garanteed.

#### THOMSON-CSF SEMICONDUCTEURS SPECIFIQUES

| Parameter                      | Symbol           | Min   | Мах   | Unit |

|--------------------------------|------------------|-------|-------|------|

| Core supply voltage            | V <sub>DD</sub>  | 3.135 | 3.465 | V    |

| P <sub>LL</sub> supply voltage | AV <sub>DD</sub> | 3.135 | 3.465 | V    |

| I/O supply voltage             | OV <sub>DD</sub> | 3.135 | 3.465 | V    |

| Input voltage                  | V <sub>in</sub>  | GND   | 5.5   | V    |

| Operating temperature          | T <sub>c</sub>   | -55   | +125  | °C   |

#### 3.5. Thermal characteristics

#### aS3.5.1.CQFP240 package

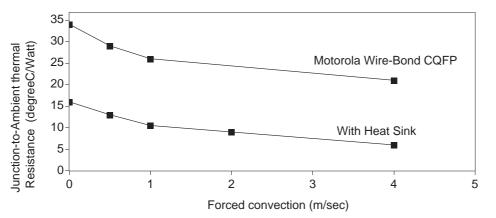

This section provides thermal management data for the 603e; this information is based on a typical desktop configuration using a 240 lead, 32 mm x 32 mm, wire-bond CQFP package. The heat sink used for this data is a pinfin configuration from Thermalloy, part number 2338.

#### 3.5.1.1. Thermal characteristics

The thermal characteristics for a wire-bond CQFP package are as follows :

Thermal resistance (junction-to-case) (typical)=  $R_{\theta jc}$  or  $\theta_{jc}$  = 2.2°C/Watt.

Wire–bond CQFP die junction–to–lead thermal resistance (typical) =  $\theta_{JB}$  = 18 °C/W

#### 3.5.1.2. Thermal management example

The following example is based on a typical desktop configuration using a wire-bond CQFP package. The heat sink used for this data is a pinfin heat sink #2338 attached to the wire-bond CQFP package with thermal grease.

Figure 5 provides a thermal management example for the CQFP package.

The junction temperature can be calculated from the junction to ambient thermal resistance, as follows :

Junction temperature :

$$T_i = T_a + (R_{\theta ic} + R_{cs} + R_{sa}) * P$$

#### Where :

Ta is the ambient temperature in the vicinity of the device

$R_{\theta ja}$  is the junction-to-ambient thermal resistance

or

$R_{\theta ic}$  is the junction-to-case thermal resistance of the device

R<sub>cs</sub> is the case-to-heat sink thermal resistance of the interface material

$T_i = T_a + R_{\theta ia} * P$

Rsa is the heat sink-to-ambient thermal resistance

P is the power dissipated by the device

In this environment, it can be assumed that all the heat is dissipated to the ambient through the heat sink, so the junction-to-ambient thermal resistance is the sum of the resistances from the junction to the case, from the case to the heat sink, and from the heat sink to the ambient.

Note that verification of external thermal resistance and case temperature should be performed for each application. Thermal resistance can vary considerably due to many factors including degree of air turbulence.

For a power dissipation of 2.5 Watts in an ambient temperature of 40°C at 1 m/sec with the heat sink measured above, the junction temperature of the device would be as follows :

$$T_j = T_a + R_{\theta ja} * F$$

$$T_i = 40^{\circ}C + (10^{\circ}C/Watt * 2.5 watts) = 65^{\circ}C$$

which is well within the reliability limits of the device.

#### Notes :

- 1. Junction-to-ambient thermal resistance is based on measurements on single-sided printed circuit boards per SEMI (Semiconductor Equipment and Materials International) G38-87 in natural convection.

- 2. Junction-to-case thermal resistance is based on measurements using a cold plate per SEMI G30-88 with the exception that the cold plate temperature is used for the case temperature.

#### 3.5.2.CBGA255 package

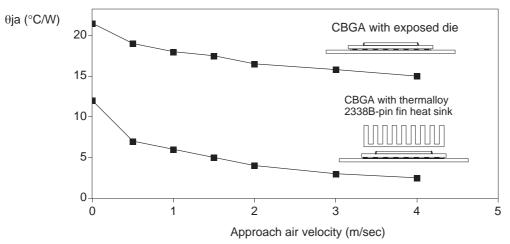

The data found in this section concerns 603e's packaged in the 255-lead 21 mm multi-layer ceramic (MLC), ceramic BGA package. Data is shown for two cases, the expoded-die case (no heat sink) and using the Thermalloy 2338-pin fin heat sink.

#### 3.5.2.1. Thermal characteristics

The internal thermal resistance for this package is negligible due to the exposed die design. A heat sink is attached directly to the silicon die surface only when external thermal enhancement is necessary.

Additionally, the CBGA package offers an excellent thermal connection to the card and power planes. Heat generated at the chip is dissipated through the package, the heat sink (when used) and the card. The parallel heat flow paths result in the lowest overall thermal resistance as well as offer significantly better power dissipation capability when a heat sink is not used.

The thermal characteristics for the flip-chip CBGA package are as follows :

Thermal resistance (junction-to-case) =  $R_{\theta jc}$  or  $\theta_{jc} = 0.08^{\circ}C/Watt$ .

Thermal resistance (junction-to-ball) =  $R_{\theta jb}$  or  $\theta_{jb}$  = 2.8°C/Watt .

#### 3.5.2.2. Thermal management example

The calculations are performed exactly as shown in the previous section for CPFP240. Figure 6 shows typical thermal performance data for the 21 mm CBGA package mounted to a test card.

#### Assumptions :

- 1. 2P card with 1 OZ Cu planes

- 2. 63 mm x 76 mm card

- 3. Air flow on both sides of card

- 4. Vertical orientation

- 5. 2-stage epoxy heat sink attach

Temperature calculations are also performed identically to those in the previous section. For a power dissipation of 2.5 Watts in an ambient of 40°C at 1.0 m/sec, the associated overall thermal resistance and junction temperature, found in Table 6 will result.

THOMSON-CSF SEMICONDUCTEURS SPECIFIQUES

| Configuration              | θ <sub>ja</sub> (°C/W)          | Т <sub>ј</sub> (°С) |  |  |  |

|----------------------------|---------------------------------|---------------------|--|--|--|

| Exposed die (no heat sink) | Exposed die (no heat sink) 18.4 |                     |  |  |  |

| With 2338 heat sink        | 5.3                             | 53                  |  |  |  |

#### Table 6 : Thermal resistance and junction temperature

Vendors such as Aavid Engineering Inc., Thermalloy, and Wakefield Engineering can supply heat sinks with a wide range of thermal performance.

#### 3.6. Power consideration

The PowerPC603e microprocessor is the first microprocessor specifically designed for low-power operation. The 603e provides both automatic and program-controllable power reduction modes for progressive reduction of power consumption. This chapter describes the hardware support provided by the 603e for power management.

#### 3.6.1. Dynamic Power Management

Dynamic power management automatically powers up and down the individual execution units of the 603e, based upon the contents of the instruction stream. For example, if no floating-point instructions are being executed, the floating-point unit is automatically powered down. Power is not actually removed from the execution unit ; instead, each execution unit has an independent clock input, which is automatically controlled on a clock-by- clock basis. Since CMOS circuits consume negligible power when they are not switching, stopping the clock to an execution unit effectively eliminates its power consumption. The operation of DPM is completely transparent to software or any external hardware. Dynamic power management is enabled by setting bit 11 in HID0 on power-up, of following HRESET.

#### 3.6.2. Programmable Power Modes

The 603e provides four programmable power states - full power, doze, nap and sleep. Software selects these modes by setting one (and only one) of the three power saving mode bits. Hardware can enable a power management state through external asynchronous interrupts The hardware interrupt causes the transfer of program flow to interrupt handler code. The appropriate mode is then set by the software. The 603e provides a separate interrupt and interrupt vector for power management - the system management interrupt (SMI). The 603e also contains a decrement timer which allows it to enter the nap or doze mode for a predetermined amount of time and then return to full power operation through the decrementer interrupt (DI). Note that the 603e cannot switch from on power management mode to another without first returning to full on mode. The nap and sleep modes disable bus snooping ; therefore, a hardware handshake is provided to ensure coherency before the 603e enters these power management modes. Table 7 summarizes the four power states.

| PM Mode               | Functioning Units                                               | Activation Method                   | Full-Power Wake Up Method                                           |

|-----------------------|-----------------------------------------------------------------|-------------------------------------|---------------------------------------------------------------------|

| Full power            | All units active                                                | -                                   | _                                                                   |

| Full power (with DPM) | Requested logic by demand                                       | By instruction dispatch             | _                                                                   |

| Doze                  | - Bus snooping<br>- Data cache as needed<br>- Decrementer timer | Controlled by SW                    | External asynchronous exceptions*<br>Decrementer interrupt<br>Reset |

| Nap                   | Decrementer timer                                               | Controlled by hardware and software | External asynchronous exceptions<br>Decrementer interrupt<br>Reset  |

| Sleep                 | None                                                            | Controlled by hardware and software | External asynchronous exceptions<br>Reset                           |

\* Exceptions are referred to as interrupts in the architecture specification

#### 3.6.3. Power Management Modes

The following sections describe the characteristics of the 603e's power management modes, the requirements for entering and exiting the various modes, and the system capabilities provided by the 603e while the power management modes are active.

14/38

#### 3.6.3.1. Full-Power Mode with DPM Disabled

Full-power mode with DPM disabled power mode is selected when the DPM enable bit (bit 11) in HID0 is cleared.

- Default state following power-up and HRESET.

- All functional units are operating at full processor speed at all times.

#### 3.6.3.2. Full-Power Mode with DPM Enabled

Full-power mode with DPM enabled (HID0[11] = 1) provides on-chip power management without affecting the functionality or performance of the 603e.

- Required functional units are operating at full processor speed.

- Functional units are clocked only when needed.

- No software or hardware intervention required after mode is set.

- Software/hardware and performance transparent.

#### 3.6.3.3. Doze Mode

Doze ode disables most functional units but maintains cache coherency by enabling the bus interface unit and snooping. A snoop hit will cause the 603e to enable the data cache, copy the data back to memory, disable the cache, and fully return to the doze state.

- Most functional units disabled.

- Bus snooping and time base/decrementer still enabled.

- Dose mode sequence :

- Set doze bit (HID0[8) = 1).

- 603e enters doze mode after several processor clocks.

- Several methods of returning to full-power mode :

- Assert INT, SMI, MCP or decrementer interrupts.

- Assert hard reset or soft reset.

- Transition to full-power state takes no more than a few processor cycles.

- PLL running and locked to SYSCLK.

#### 3.6.3.4. Nap Mode

The nap mode disables the 603e but still maintains the phase locked loop (PLL) and the time base/decrementer. The time base can be used to restore the 603e to full-on state after a programmed amount of time. Because bus snooping is disabled for nap and sleep mode, a hardware handshake using the quiesce request (QREQ) and quiesce acknowledge (QACK) signals are requires to maintain data coherency. The 603e will assert the QREQ signal to indicate that it is ready to disable bus snooping. When the system has ensured that snooping is no longer necessary, it will assert QACK and the 603e will enter the sleep or nap mode.

- Time base/decrementer still enabled.

- Most functional units disabled (including bus snooping).

- All nonessential input receivers disables.

- Nap mode sequence :

- Set nap bit (HID0[9] = 1).

- 603e asserts quiesce request (QREQ) signal.

- System asserts quiesce acknowledge (QACK) signal.

- 603e enters sleep mode after several processor clocks.

- Several methods of returning to full-power mode :

- Assert INT, SPI, MCP or decrementer interrupts.

- Assert hard reset or soft reset.

- Transition to full-power takes no more than a few processor cycles.

- PLL running and locked to SYSCLK.

#### 3.6.3.5. Sleep Mode

Sleep mode consumes the least amount of power of the four modes since all functional units are disabled. To conserve the maximum amount of power, the PLL may be disabled and the SYSCLK may be removed. Due to the fully static design of the 603e, internal processor state is preserved when no internal clock is present. Because the time base and decrementer are disabled while the 603e is in sleep mode, the 603e's time base contents will have to be updated from an external time base following sleep mode if accurate time-of-day maintenance is required. Before the 603e enters the sleep mode, the 603e will assert the QREQ signal to indicate that it is ready to disable bus snooping. When the system has ensured that snooping is no longer necessary, it will assert QACK and the 603e will enter the sleep mode.

- All functional units disabled (including bus snooping and time base).

- All nonessential input receivers disabled :

- Internal clock regenerators disabled.

- PLL still running (see below).

#### THOMSON-CSF SEMICONDUCTEURS SPECIFIQUES

- Sleep mode sequence :

- Set sleep bit (HID0[10] = 1).

- 603e asserts quiesce request (QREQ).

- System asserts quiesce acknowledge (QACK).

- 603e enters sleep mode after several processor clocks.

- Several methods of returning to full-power mode :

- Assert INT, SMI, or MCP interrupts.

- Assert hard reset or soft reset.

- PLL may be disabled and SYSCLK may be removed while in sleep mode.

- Return to full-power mode after PLL and SYSCLK disabled in sleep mode :

- Enable SYSCLK.

- Reconfigure PLL into desired processor clock mode.

- System logic waits for PLL startup and relock time (100  $\mu$ sec).

- System logic asserts one of the sleep recovery signals (for example, INT or SMI).

#### v.DataSheet4U.com

#### 3.6.4. Power Management Software Considerations

Since the 603e is a dual issue processor with out -of-order execution capability, care must be taken in how the power management mode is entered. Furthermore, nap and sleep modes require all outstanding bus operations to be completed before the power management mode is entered. Normally during system configuration time, one of the power management modes would be selected by setting the appropriate HID0 mode bit. Later on, the power management mode is invoked by setting the MSR[POW] bit. To provide a clean transition into and out of the power management mode, the **stmsr**[POW] should be preceded by a **sync** instruction and followed by an **isync** instruction.

#### 3.6.5. Power dissipation

#### Table 8 : Power dissipation

Vdd =  $3.3 \pm 5$  % V dc, GND = 0 V dc, 0°C  $\leq T_c \leq 125$ °C

#### **CPU clock Frequency**

|                                                 | 80 MHz         | 100 MHz         | 120 MHz | 133 MHz | Units |  |  |  |  |  |

|-------------------------------------------------|----------------|-----------------|---------|---------|-------|--|--|--|--|--|

| Full-On Mode (DPM Enabled)                      |                |                 |         |         |       |  |  |  |  |  |

| Typical                                         | 2.1            | 3.2             | 3.9     | 4.2     | W     |  |  |  |  |  |

| Max                                             | 3.0            | 4.0             | 4.8     | 5.3     | W     |  |  |  |  |  |

| Doze Mode <sup>1</sup>                          |                |                 |         |         |       |  |  |  |  |  |

| Typical                                         | 0.8            | 1.0             | 1.2     | 1.3     | W     |  |  |  |  |  |

| Nap Mode <sup>1</sup>                           |                |                 |         |         |       |  |  |  |  |  |

| Typical                                         | 70             | 70              | 80      | 85      | mW    |  |  |  |  |  |

| Sleep Mod                                       | e <sup>1</sup> |                 |         |         |       |  |  |  |  |  |

| Typical                                         | 40             | 40              | 45      | 50      | mW    |  |  |  |  |  |

| Sleep Mod                                       | e-PLL Disabl   | ed <sup>1</sup> |         |         |       |  |  |  |  |  |

| Typical                                         | 5.0            | 5.0             | 6.0     | 6.0     | mW    |  |  |  |  |  |

| Sleep Mode-PLL and SYSCLK Disabled <sup>1</sup> |                |                 |         |         |       |  |  |  |  |  |

| Typical                                         | 3.0            | 3.0             | 3.0     | 3.0     | mW    |  |  |  |  |  |

Note 1: The values provided for this mode do not include pad driver power (OVDD) or analog supply power (AVDD). Worst-case AVDD = 15 mW

Note : To calculate the power consumption at low temperature (-55°C), use a 1.25 factor Maximum power measurements are performed with a worst case instruction mix at VDD=3.465V

TSPC603E

#### 3.7. Marking

The document where are defined the marking are identified in the related reference documents. Each microcircuit are legible and permanently marked with the following information as minimum :

- Thomson logo,

- Manufacturer's part number,

- Class B identification if applicable,

- Date-code of inspection lot,

- ESD identifier if available,

- Country of manufacturing.

#### 4. ELECTRICAL CHARACTERISTICS

#### DataSheet4U.com

#### 4.1. General requirements

All static and dynamic electrical characteristics specified for inspection purposes and the relevant measurement conditions are given below :

- Table 9 : Static electrical characteristics for the electrical variants.

- Table 10 : Dynamic electrical characteristics for the 603e.

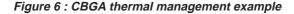

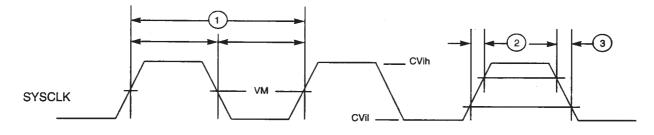

These specifications are for 80 MHz and 100 MHz processor core frequencies. The processor core frequency is determined by the bus (SYSCLK) frequency and the settings of the PLL\_CFG0\_PLL\_CFG3 signals. All timings are specified respective to the rise edge of SYSCLK.

#### 4.2. Static characteristics

#### Table 9 : Electrical characteristics

Vdd =  $3.3 \pm 5$  % V dc, GND = 0 V dc,  $-55^{\circ}C \le T_c \le 125^{\circ}C$

| Characteristics                                                          |                                          | Symbol           | Min | Max  | Unit |

|--------------------------------------------------------------------------|------------------------------------------|------------------|-----|------|------|

| Input high voltage (all inp                                              | outs except SYSCLK)                      | V <sub>IH</sub>  | 2.0 | 5.5  | V    |

| Input low voltage (all input                                             | uts except SYSCLK)                       | V <sub>IL</sub>  | GND | 0.8  | V    |

| SYSCLK input high volta                                                  | ge                                       | CVIH             | 2.4 | 5.5  | V    |