# **Signetics**

# 8X350 2K-Bit TTL Bipolar RAM (256×8)

#### Military Bipolar Memory Products

**Product Specification**

#### DESCRIPTION

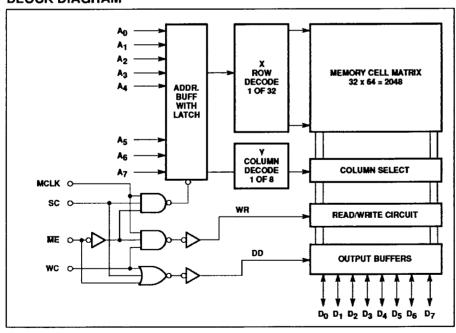

The 8X350 bipolar RAM is designed principally as a working storage element in an 8X305 based system. Internal circuitry is provided for direct use in 8X305 applications. When used with the 8X305, the RAM address and data busses are tied together and connected to the IV bus of the system.

The data inputs and outputs share a common I/O bus with 3-State outputs.

#### **ORDERING INFORMATION**

| DESCRIPTION                       | ORDER CODE |

|-----------------------------------|------------|

| 22-pin Ceramic DIP<br>400mil-wide | 8X350/BWA  |

#### **FEATURES**

- On-chip address latches

- Schottky clamped

- One master enable input

- Directly Interfaces with the 8X305 bipolar microprocessor with no external logic

- May be used on left or right bank

1

- Common I/O:

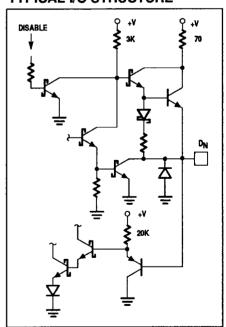

- Inputs: PNP bufferedOutputs: 3-State

#### **APPLICATIONS**

• 8X305 working storage

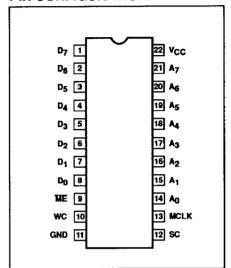

#### PIN CONFIGURATION

#### **BLOCK DIAGRAM**

#### **TYPICAL I/O STRUCTURE**

8X350

#### **ABSOLUTE MAXIMUM RATINGS**

| SYMBOL                                     | PARAMETER                                    | RATING       | UNIT                               |  |

|--------------------------------------------|----------------------------------------------|--------------|------------------------------------|--|

| V <sub>CC</sub> Supply voltage             |                                              | +7           | V <sub>DC</sub>                    |  |

| Vı                                         | Input voltage                                | +5.5         |                                    |  |

| V <sub>o</sub><br>V <sub>o</sub>           | Output voltage High Output voltage Off-state | +5.5<br>+5.5 | V <sub>DC</sub><br>V <sub>DC</sub> |  |

| T <sub>A</sub> Operating temperature range |                                              | -55 to +125  | °C                                 |  |

| T <sub>STG</sub>                           | Storage temperature range                    | -65 to +150  | °C                                 |  |

### DC ELECTRICAL CHARACTERISTICS -55°C $\leq T_A \leq +125$ °C, 4.75V $\leq V_{CC} \leq 5.25$ V<sup>2</sup>

| SYMBOL           | PARAMETER                         | TEST CONDITIONS <sup>1</sup>                  | LIMITS |     |      | UNIT |

|------------------|-----------------------------------|-----------------------------------------------|--------|-----|------|------|

|                  |                                   |                                               | Min    | Тур | Max  |      |

| Input voitag     | e                                 |                                               |        |     |      |      |

| V <sub>IL</sub>  | Low                               |                                               |        |     | 0.8  | V    |

| $V_{IH}$         | High                              |                                               | 2.0    | 1   |      | V    |

| V <sub>IK</sub>  | Clamp <sup>3</sup>                | $V_{CC} = 4.75V$ , $I_i = -18mA$              |        |     | -1.2 | ٧    |

| Output volt      | age                               |                                               |        |     |      |      |

|                  |                                   | V <sub>CC</sub> = 4.75V                       |        |     |      |      |

| VoL              | Low <sup>4</sup>                  | I <sub>OL</sub> = 9.6mA                       |        |     | 0.5  | ٧    |

| V <sub>OH</sub>  | High <sup>5</sup>                 | l <sub>OH</sub> = -2mA                        | 2.4    |     |      | V    |

| input curre      | nt                                |                                               |        |     |      |      |

|                  |                                   | V <sub>CC</sub> = 5.25V                       |        |     |      |      |

| l <sub>E</sub>   | Low                               | V <sub>I</sub> = 0.45V                        |        |     | -150 | μΑ   |

| l <sub>iH</sub>  | High                              | V <sub>I</sub> = 5.5V                         |        |     | 50   | μΑ   |

| Output cur       | ent                               |                                               |        |     |      |      |

|                  |                                   | V <sub>CC</sub> = 5.25V                       |        |     |      |      |

| loz              | Hi-Z state                        | $\overline{ME}$ = High, $V_0 = 5.5V$          |        |     | 60   | μΑ   |

|                  |                                   | $\overline{ME}$ = High, $V_O$ = 0.5V          |        | 1   | -100 | μA   |

| los              | Short circuit <sup>3, 6, 13</sup> | SC = WC, ME = Low                             |        | i   | 1    | ,    |

| -00              |                                   | $V_{CC} = 5.25V$ , $V_{O} = 0V$ , High stored | -15    | ĺ   | -85  | mA   |

| Supply cur       | ·ent <sup>7</sup>                 | •                                             |        |     |      |      |

| Icc              |                                   | V <sub>CC</sub> = 5.25V                       |        |     | 200  | mA   |

| Capacitano       | e <sup>13</sup>                   |                                               |        |     |      |      |

|                  |                                   | ME = High, V <sub>CC</sub> = 5.0V             |        |     |      |      |

| CIN              | Input                             | $V_1 = 2.0V$                                  |        | 5   | 10   | pF   |

| C <sub>OUT</sub> | Output                            | $V_0 = 2.0V$                                  | - 1    | 8   | 13   | рF   |

### 2K-Bit TTL Bipolar RAM (256 × 8)

#### **TRUTH TABLE**

| MODE                                           | ME | sc | wc | MCLK | BUSSED DATA/<br>ADDRESS LINES |

|------------------------------------------------|----|----|----|------|-------------------------------|

| Hold address<br>Disable data out               | 1  | x  | ×  | х    | Hi-Z data out                 |

| Input new address                              | 0  | 1  | 0  | 1    | Address Hi-Z                  |

| Hold address Disable data out                  | 0  | 1  | 0  | 0    | Hi-Z data out                 |

| Hold address<br>Write data                     | 0  | 0  | 1  | 1    | Data in                       |

| Hold address<br>Disable data out               | 0  | 0  | 1  | o    | Hi-Z data out                 |

| Hold address<br>Read data                      | 0  | 0  | 0  | ×    | Data out                      |

| Undefined state <sup>12</sup>                  | 0  | 1  | 1  | 1    | -                             |

| Hold address <sup>12</sup><br>Disable data out | 0  | 1  | 1  | 0    | Hi-Z data out                 |

X = Don't care

#### AC ELECTRICAL CHARACTERISTICS -55°C ≤ T<sub>A</sub> ≤ +125°C, 4.75V ≤ V<sub>CC</sub> ≤ 5.25V<sup>2</sup>

| SYMBOL                                                | L PARAMETER TO FI                          | FROM                 | LIMITS                     |             |     | UNIT     |                |

|-------------------------------------------------------|--------------------------------------------|----------------------|----------------------------|-------------|-----|----------|----------------|

|                                                       |                                            |                      |                            | Min         | Тур | Max      |                |

| t <sub>E1</sub><br>t <sub>E2</sub>                    | Output enable time<br>Output enable time   | Data out<br>Data out | SC-<br>ME-                 |             |     | 40<br>40 | ns<br>ns       |

| t <sub>D1</sub>                                       | Output disable time<br>Output disable time | Data out<br>Data out | SC+<br>ME+                 |             |     | 40<br>40 | ns<br>ns       |

| t <sub>W</sub>                                        | Master clock pulse width <sup>8</sup>      |                      |                            | 50          |     |          | ns             |

| t <sub>SA</sub><br>t <sub>HA</sub>                    | Setup time<br>Hold time                    | MCLK-<br>Address     | Address<br>MCLK-           | 40<br>10    |     |          | ns<br>ns       |

| t <sub>SD</sub>                                       | Setup time<br>Hold time                    | MCLK-<br>Data in     | Data in<br>MCLK-           | 45<br>10    |     |          | ns<br>ns       |

| t <sub>S3</sub><br>t <sub>H3</sub>                    | Setup time<br>Hold time                    | MCLK-<br>ME+         | ME-<br>MCLK-               | 50<br>5     |     |          | ns<br>ns       |

| t <sub>S1</sub><br>t <sub>H2</sub>                    | Setup time<br>Hold time                    | MCLK-<br>ME-         | ME-<br>MCLK-               | 40<br>5     |     |          | ns<br>ns       |

| t <sub>S2</sub><br>t <sub>H1</sub><br>t <sub>H4</sub> | Setup time<br>Hold time<br>Hold time       | ME-<br>SC-<br>WC-    | SC-, WC-<br>MCLK-<br>MCLK- | 5<br>5<br>5 |     |          | ns<br>ns<br>ns |

#### NOTES:

- 1. All voltage values are with respect to network ground terminal.

- 2. The operating ambient temperature ranges are guaranteed with transverse air flow exceeding 400 linear feet per minute and a one-minute warm-up. This testing will be guaranteed by testing at -40°C using instant on testing.

- 3. Test each pin one at a time.

- 4. Measured with a logic Low stored. Output sink current is supplied through a resistor to  $V_{\text{CC}}$ .

- 5. Measured with a logic High stored.

- 6. Duration of the short circuit should not exceed 1 second.

- 7.  $I_{CC}$  is measured with the Write enable and Memory enable inputs grounded, all other inputs  $\geq$  4.0V and the output open.

- 8. Minimum required to guarantee a Write into the slowest bit.

- 9. Applied to the 8X305 based system with the data and address pins tied to the IV Bus.

- 10. SC + ME = 1 to avoid bus conflict.

- 11. WC + ME = 1 to avoid bus conflict.

- 12. The SC and WC outputs from the 8X305 are never at 1 simultaneously.

- 13. Guaranteed, but not tested.

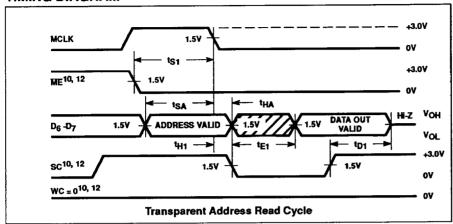

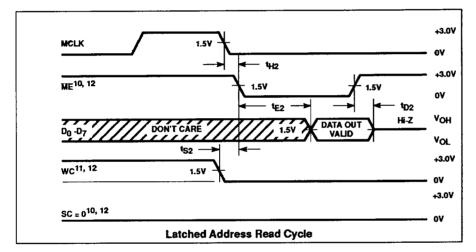

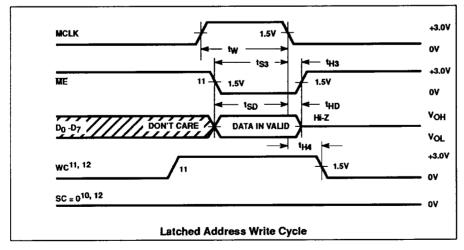

#### **TIMING DIAGRAM**

| MEMO            | RY TIMING DEFINITIONS                                                                                       |

|-----------------|-------------------------------------------------------------------------------------------------------------|

| t <sub>S1</sub> | Required delay between beginning of Master Enable Low and falling edge of Master Clock.                     |

| tsa             | Required delay between beginning of valid address and falling edge of Master Clock.                         |

| te i            | Delay between beginning of Select<br>Command Low and beginning of<br>valid data output on the IV Bus.       |

| t <sub>E2</sub> | Delay between when Master En-<br>able becomes Low and beginning<br>of valid data output on the IV Bus.      |

| t <sub>HA</sub> | Required delay between falling edge of Master Clock and end of valid Address.                               |

| t <sub>D1</sub> | Delay between when Select Command becomes High and end of valid data output on the IV Bus.                  |

| t <sub>D2</sub> | Delay between when Master En-<br>able becomes High and end of val-<br>id data output on the IV Bus.         |

| <b>t</b> H1     | Required delay between falling edge of Master Clock and when Select Command becomes Low.                    |

| <sup>‡</sup> H2 | Required delay between falling edge of Master Clock and when Master Enable becomes Low.                     |

| t <sub>S2</sub> | Required delay between when Select Command or Write Command becomes Low and when Master Enable becomes Low. |

| t <sub>W</sub>  | Minimum width of the Master<br>Clock pulse.                                                                 |

| tso             | Required delay between beginning of valid data input on the IV Bus and falling edge of Master Clock.        |

| t <sub>S3</sub> | Required delay between when<br>Master Enable becomes Low and<br>falling edge of Master Clock.               |

| <sup>‡</sup> HD | Required delay between beginning of valid data input on the IV Bus.                                         |

| <b>1</b> нз     | Required delay between falling edge of Master Clock and when Master Enable becomes High.                    |

| t <sub>H4</sub> | Required delay between falling edge of Master Clock and when Write Command becomes Low.                     |

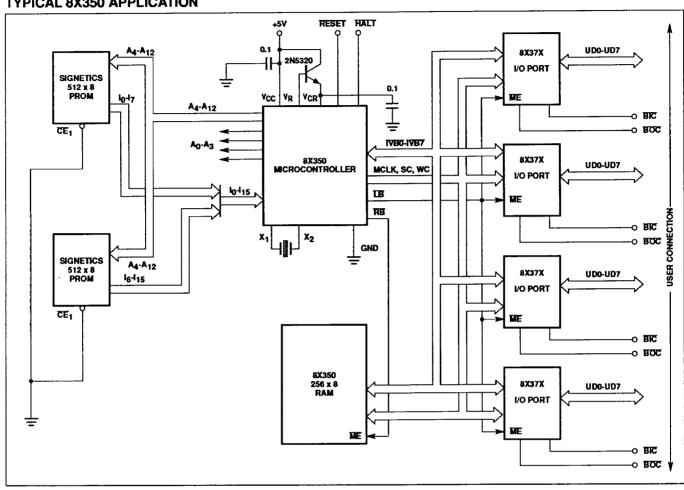

#### **TYPICAL 8X350 APPLICATION**

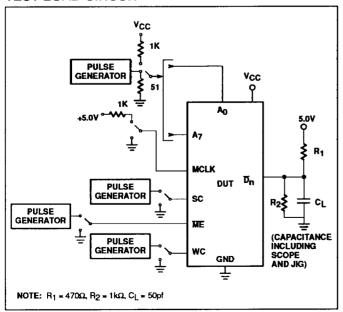

#### **TEST LOAD CIRCUIT**

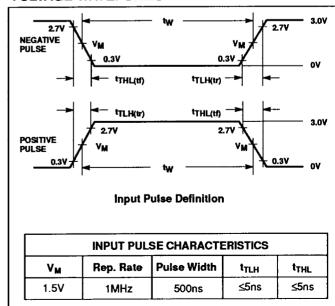

### **VOLTAGE WAVEFORMS**

8X350

| DEFINITIONS               |                        |                                                                                                                                                                                                                                               |  |  |

|---------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Data Sheet Identification | Product Status         | Definition                                                                                                                                                                                                                                    |  |  |

| Objective Specification   | Formative or in Design | This data sheet contains the design target or goal specifications for product development. Specifications may change in any manner without notice.                                                                                            |  |  |

| Preliminary Specification | Preproduction Product  | This data sheet contains preliminary data, and supplementary data will be published at a later date. Signetics reserves the right to make changes at any time without notice in order to improve design and supply the best possible product. |  |  |

| Product Specification     | Full Production        | This data sheet contains Final Specifications. Signetics reserves the right to make changes at any time without notice, in order to improve design and supply the best possible product.                                                      |  |  |

Signetics reserves the right to make changes without notice in the products, including circuits, standard cells, and/or software, described or contained herein, in order to improve design and/or performance. Signetics assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work infringement, unless otherwise specified. Applications that are described herein for any of these products are for illustrative purposes only. Signetics makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### LIFE SUPPORT APPLICATIONS

Signetics Products are not designed for use in life support appliances, devices, or systems where malfunction of a Signetics Product can reasonably be expected to result in a personal injury. Signetics customers using or selling Signetics Products for use in such applications do so at their own risk, and agree to fully indemnify Signetics for any damages resulting from such improper use or sale.

6

Signetics Company 811 East Arques Avenue P.O. Box 3409 Sunnyvale, California 94088–3409 Telephone 800-227-1817 Ext. 900 Signetics registers eligible circuits under the Semiconductor Chip Protection Act. © 1992 Signetics Company All rights reserved. Printed in U.S.A.