# M66256FP

# 5120 × 8-Bit Line Memory (FIFO)

REJ03F0250-0200 Rev.2.00 Sep 14, 2007

#### **Description**

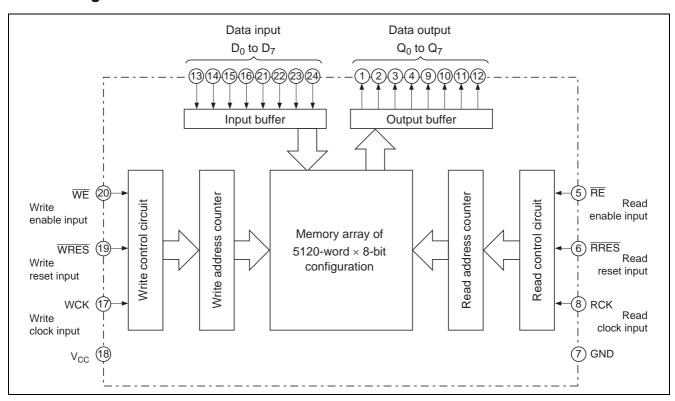

The M66256FP is a high-speed line memory with a FIFO (First In First Out) structure of 5120-word  $\times$  8-bit configuration which uses high-performance silicon gate CMOS process technology.

It has separate clock, enable and reset signals for write and read, and is most suitable as a buffer memory between devices with different data processing throughput.

#### **Features**

Memory configuration: 5120 words × 8 bits (dynamic memory)

High-speed cycle: 25 ns (Min)

High-speed access: 18 ns (Max)

Output hold: 3 ns (Min)

• Fully independent, asynchronous write and read operations

Variable length delay bit

• Output: 3 states

#### **Application**

Digital photocopiers, high-speed facsimile, laser beam printers.

#### **Block Diagram**

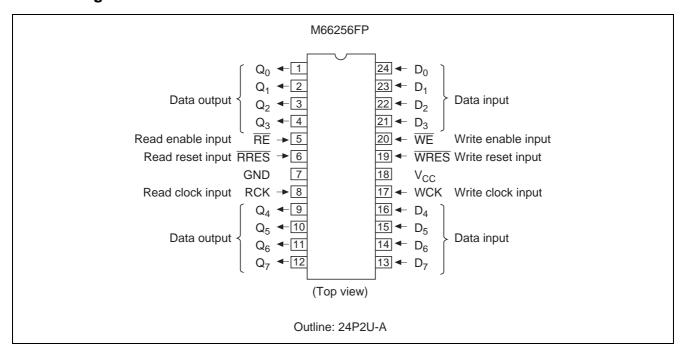

### **Pin Arrangement**

### **Absolute Maximum Ratings**

(Ta = 0 to  $70^{\circ}$ C, unless otherwise noted)

| Item                | Symbol          | Ratings                  | Unit | Conditions       |

|---------------------|-----------------|--------------------------|------|------------------|

| Supply voltage      | V <sub>CC</sub> | −0.5 to +7.0             | V    | A value based on |

| Input voltage       | VI              | $-0.5$ to $V_{CC}$ + 0.5 | V    | GND pin          |

| Output voltage      | Vo              | $-0.5$ to $V_{CC}$ + 0.5 | V    |                  |

| Power dissipation   | Pd              | 440                      | mW   | Ta = 25°C        |

| Storage temperature | Tstg            | -65 to 150               | °C   |                  |

### **Recommended Operating Conditions**

| Item                          | Symbol | Min | Тур | Max | Unit |

|-------------------------------|--------|-----|-----|-----|------|

| Supply voltage                | Vcc    | 4.5 | 5   | 5.5 | V    |

| Supply voltage                | GND    | _   | 0   | _   | V    |

| Operating ambient temperature | Topr   | 0   | _   | 70  | °C   |

#### **Electrical Characteristics**

$(Ta = 0 \text{ to } 70^{\circ}\text{C}, V_{CC} = 5 \text{ V} \pm 10\%, \text{GND} = 0 \text{ V})$

| Item                               | Symbol           | Min                   | Тур | Max  | Unit | Tes                                   | st Conditions                                                                                                                    |

|------------------------------------|------------------|-----------------------|-----|------|------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| "H" input voltage                  | V <sub>IH</sub>  | 2.0                   | _   | _    | V    |                                       |                                                                                                                                  |

| "L" input voltage                  | $V_{IL}$         | _                     | _   | 0.8  | V    |                                       |                                                                                                                                  |

| "H" output voltage                 | V <sub>OH</sub>  | V <sub>CC</sub> – 0.8 | _   | _    | V    | $I_{OH} = -4 \text{ m}$               | Α                                                                                                                                |

| "L" output voltage                 | V <sub>OL</sub>  | _                     | _   | 0.55 | V    | $I_{OL} = 4 \text{ mA}$               |                                                                                                                                  |

| "H" input current                  | Іін              |                       | _   | 1.0  | μΑ   | V <sub>I</sub> = V <sub>CC</sub>      | WE, WRES, WCK, RE, RRES, RCK, D <sub>0</sub> to D <sub>7</sub>                                                                   |

| "L" input current                  | I <sub>IL</sub>  |                       | _   | -1.0 | μΑ   | V <sub>I</sub> = GND                  | $\overline{\text{WE}}$ , $\overline{\text{WRES}}$ , WCK, $\overline{\text{RE}}$ , $\overline{\text{RRES}}$ , RCK, $D_0$ to $D_7$ |

| Off state "H" output current       | l <sub>OZH</sub> | _                     | _   | 5.0  | μА   | $V_{O} = V_{CC}$                      |                                                                                                                                  |

| Off state "L" output current       | l <sub>OZL</sub> | _                     | _   | -5.0 | μА   | V <sub>O</sub> = GND                  |                                                                                                                                  |

| Operating mean current dissipation | Icc              | _                     | _   | 80   | mA   | $V_1 = V_{CC}$ , GND, Output open     |                                                                                                                                  |

| Input conscitance                  | C                |                       |     | 10   | nE   | $t_{WCK}$ , $t_{RCK} = 25 \text{ ns}$ |                                                                                                                                  |

| Input capacitance                  | Cı               |                       |     |      | pF   | f = 1 MHz                             |                                                                                                                                  |

| Off state output capacitance       | Co               |                       |     | 15   | pF   | f = 1 MHz                             |                                                                                                                                  |

#### **Function**

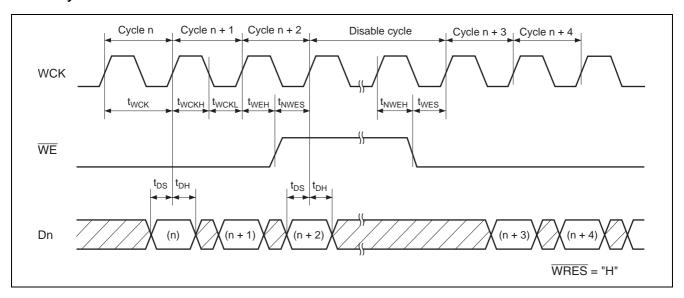

When write enable input  $\overline{WE}$  is "L", the contents of data inputs  $D_0$  to  $D_7$  are written into memory in synchronization with rise edge of write clock input WCK. At this time, the write address counter is also incremented simultaneously.

The write function given below are also performed in synchronization with rise edge of WCK.

When WE is "H", a write operation to memory is inhibited and the write address counter is stopped.

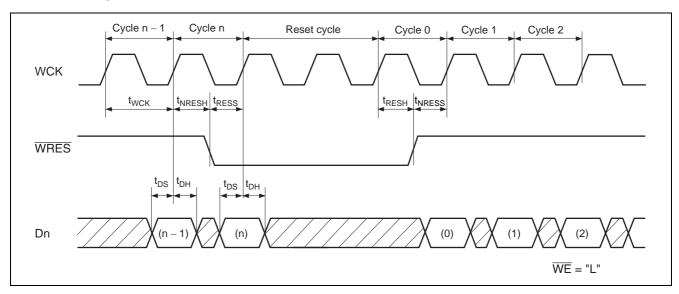

When write reset input  $\overline{WRES}$  is "L", the write address counter is initialized.

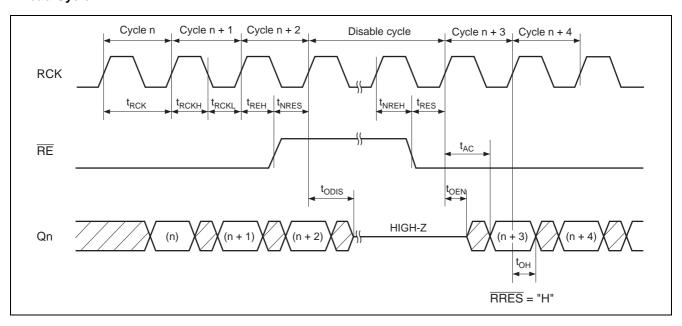

When read enable input  $\overline{RE}$  is "L", the contents of memory are output to data outputs  $Q_0$  to  $Q_7$  in synchronization with rise edge of read clock input RCK. At this time, the read address counter is also incremented simultaneously.

The read functions given below are also performed in synchronization with rise edge of RCK.

When RE is "H", a read operation from memory is inhibited and the read address counter is stopped. The outputs are in the high impedance state.

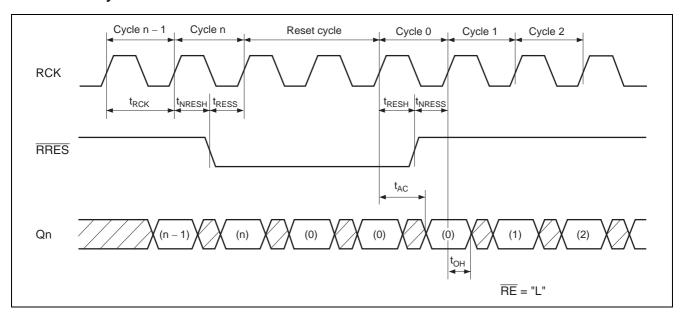

When read reset input RRES is "L", the read address counter is initialized.

# **Switching Characteristics**

$(Ta = 0 \text{ to } 70^{\circ}\text{C}, V_{CC} = 5 \text{ V} \pm 10\%, \text{GND} = 0 \text{ V})$

| Item                | Symbol           | Min | Тур | Max | Unit |

|---------------------|------------------|-----|-----|-----|------|

| Access time         | t <sub>AC</sub>  | _   | _   | 18  | ns   |

| Output hold time    | t <sub>OH</sub>  | 3   | _   | _   | ns   |

| Output enable time  | t <sub>OEN</sub> | 3   | _   | 18  | ns   |

| Output disable time | todis            | 3   | _   | 18  | ns   |

# **Timing Conditions**

(Ta = 0 to 70°C,  $V_{CC}$  = 5 V  $\pm$  10%, GND = 0 V, unless otherwise noted)

| ltem                                     | Symbol             | Min | Тур | Max | Unit |

|------------------------------------------|--------------------|-----|-----|-----|------|

| Write clock (WCK) cycle                  | t <sub>WCK</sub>   | 25  | _   | _   | ns   |

| Write clock (WCK) "H" pulse width        | t <sub>WCKH</sub>  | 11  |     |     | ns   |

| Write clock (WCK) "L" pulse width        | t <sub>WCKL</sub>  | 11  |     |     | ns   |

| Read clock (RCK) cycle                   | t <sub>RCK</sub>   | 25  |     |     | ns   |

| Read clock (RCK) "H" pulse width         | t <sub>RCKH</sub>  | 11  | _   | _   | ns   |

| Read clock (RCK) "L" pulse width         | t <sub>RCKL</sub>  | 11  |     |     | ns   |

| Input data setup time to WCK             | t <sub>DS</sub>    | 7   | _   | _   | ns   |

| Input data hold time to WCK              | t <sub>DH</sub>    | 3   |     |     | ns   |

| Reset setup time to WCK or RCK           | t <sub>RESS</sub>  | 7   | _   | _   | ns   |

| Reset hold time to WCK or RCK            | t <sub>RESH</sub>  | 3   |     |     | ns   |

| Reset nonselect setup time to WCK or RCK | t <sub>NRESS</sub> | 7   | _   | _   | ns   |

| Reset nonselect hold time to WCK or RCK  | t <sub>NRESH</sub> | 3   | _   | _   | ns   |

| WE setup time to WCK                     | t <sub>WES</sub>   | 7   | _   | _   | ns   |

| WE hold time to WCK                      | t <sub>WEH</sub>   | 3   | _   | _   | ns   |

| WE nonselect setup time to WCK           | t <sub>NWES</sub>  | 7   | _   | _   | ns   |

| WE nonselect hold time to WCK            | t <sub>NWEH</sub>  | 3   | _   | _   | ns   |

| RE setup time to RCK                     | t <sub>RES</sub>   | 7   | _   | _   | ns   |

| RE hold time to RCK                      | t <sub>REH</sub>   | 3   | _   | _   | ns   |

| RE nonselect setup time to RCK           | t <sub>NRES</sub>  | 7   |     |     | ns   |

| RE nonselect hold time to RCK            | t <sub>NREH</sub>  | 3   | _   | _   | ns   |

| Input pulse rise/fall time               | tr, tf             | _   |     | 20  | ns   |

| Data hold time*                          | t <sub>H</sub>     | _   |     | 20  | ms   |

Notes: Perform reset operation after turning on power supply.

<sup>\*</sup> For 1-line access, the following should be satisfied:  $\overline{\text{WE}}$  "H" level period  $\leq$  20 ms - 5120 t<sub>WCK</sub> -  $\overline{\text{WRES}}$  "L" level period  $\overline{\text{RE}}$  "H" level period  $\leq$  20 ms - 5120 t<sub>RCK</sub> -  $\overline{\text{RRES}}$  "L" level period

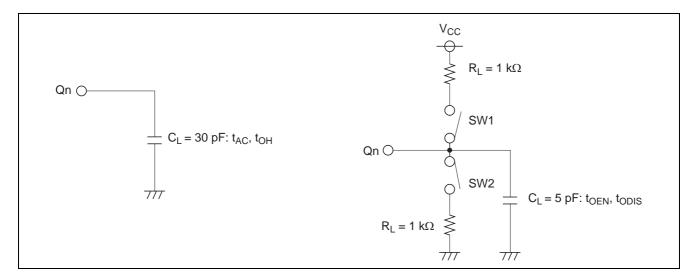

### **Test Circuit**

Input pulse level: 0 to 3V

Input pulse rise/fall time: 3 ns

Decision voltage input: 1.3 V

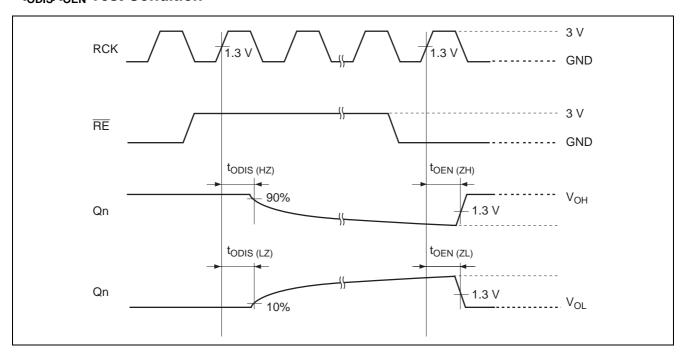

Decision voltage output: 1.3 V (However, t<sub>ODIS (LZ)</sub> is 10% of output amplitude and t<sub>ODIS (HZ)</sub> is 90% of that for

decision)

The load capacitance  $C_L$  includes the floating capacitance of connection and the input capacitance of probe.

| Parameter              | SW1    | SW2    |

|------------------------|--------|--------|

| t <sub>ODIS (LZ)</sub> | Closed | Open   |

| t <sub>ODIS (HZ)</sub> | Open   | Closed |

| t <sub>OEN (ZL)</sub>  | Closed | Open   |

| t <sub>OEN (ZH)</sub>  | Open   | Closed |

# todis/toen Test Condition

# **Operating Timing**

### **Write Cycle**

### **Write Reset Cycle**

#### **Matters that Needs Attention when WCK Stops**

Input data of n cycle is read at the rising edge after WCK of n cycle and writing operation starts in the WCK low-level period of n + 1 cycle. The writing operation is complete at the falling edge after n + 1 cycle.

To stop reading write data at n cycle, enter WCK before the rising edge after n+1 cycle.

When the cycle next to n cycle is a disable cycle, WCK for a cycle requires to be entered after the disable cycle as well.

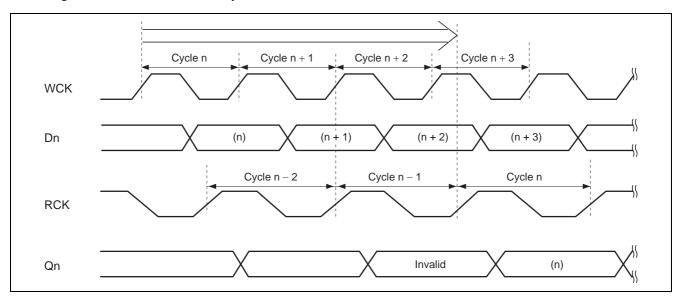

### **Read Cycle**

### **Read Reset Cycle**

## Variable Length Delay Bits

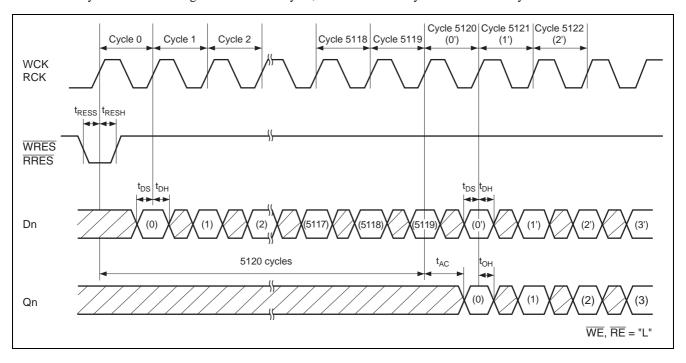

### 1-line (5120 Bits) Delay

A write input data is written into memory at the second rise edge of WCK in the cycle, and a read output data is output from memory at the first rise edge of RCK in the cycle, so that 1-line delay can be made easily.

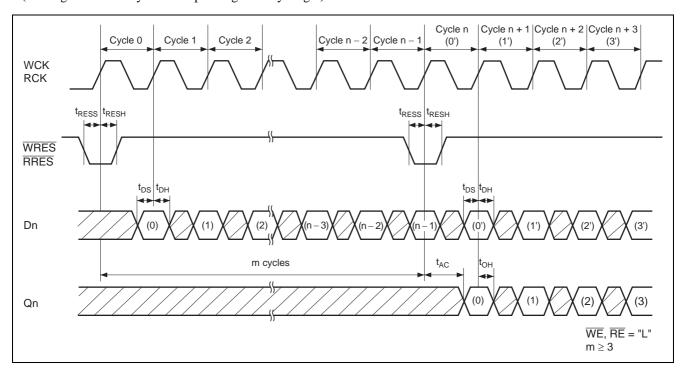

### N-bit Delay Bit

(Making a reset at a cycle corresponding to delay length)

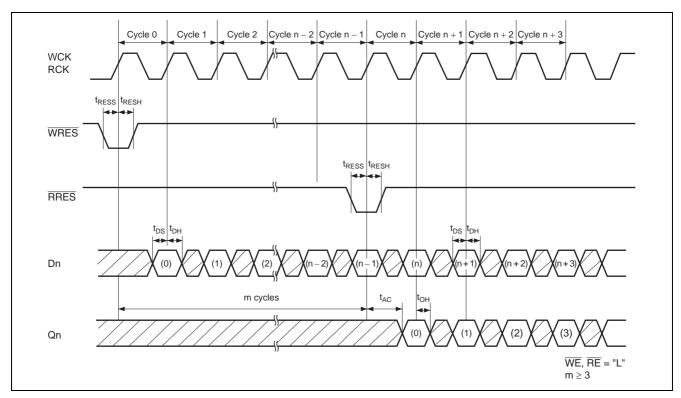

### N-bit Delay 2

(Sliding  $\overline{WRES}$  and  $\overline{RRES}$  at a cycle corresponding to delay length)

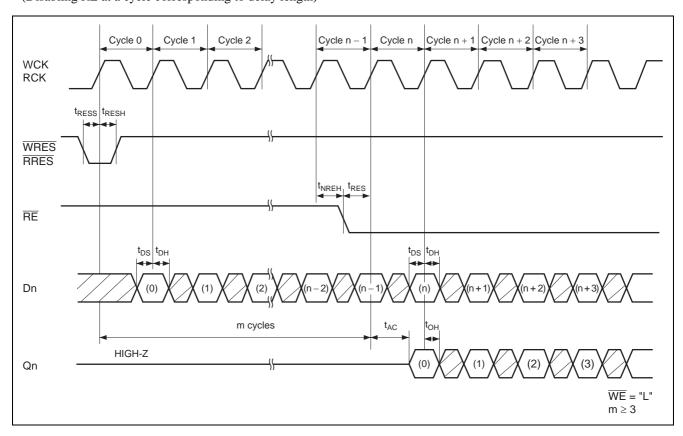

### N-bit Delay 3

(Disabling RE at a cycle corresponding to delay length)

#### Shortest Read of Data "n" Written in Cycle n

(Cycle n - 1 on read side should be started after end of cycle n + 1 on write side)

When the start of cycle n-1 on read side is earlier than the end of cycle n+1 on write side, output Qn of cycle n becomes invalid.

In the figure shown below, the read of cycle n-1 is invalid.

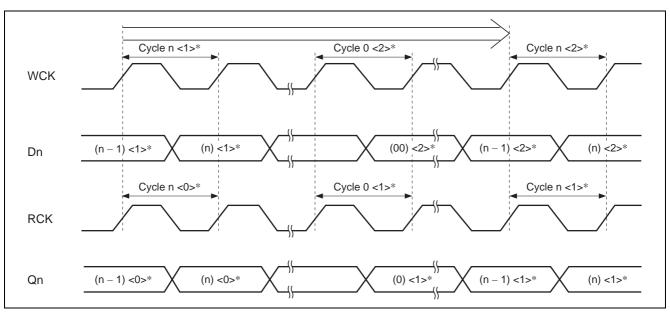

#### Longest Read of Data "n" Written in Cycle n: 1-line Delay

(Cycle n <1>\* on read side should be started when cycle n <2>\* on write is started)

Output Qn of n cycle <1>\* can be read until the start of reading side n cycle <1>\* and the start of writing side n cycle <2>\* overlap each other.

Note: <0>\*, <1>\* and <2>\* indicates a line value.

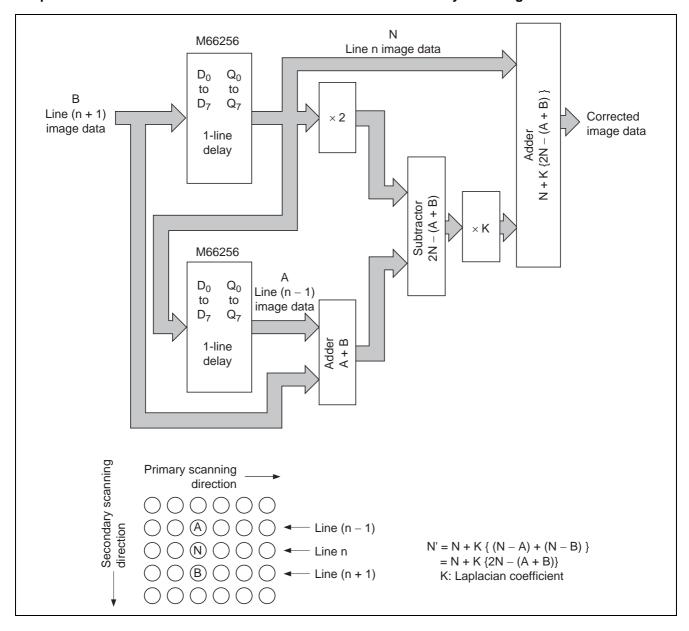

# **Application Example**

### Laplacian Filter Circuit for Correction of Resolution in the Secondary Scanning Direction

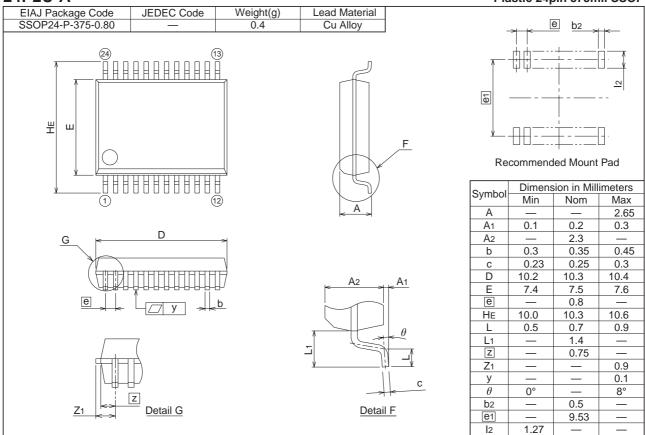

# **Package Dimensions**

# 24P2U-A

Plastic 24pin 375mil SSOP

12

Renesas Technology Corp. sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

- Renesas lechnology Corp. Sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan Notes:

1. This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warrantes or representations with respect to the accuracy or completeness of the information in this document nor grants any license to any intellectual property girbs to any other rights of representations with respect to the information in this document in this document of the purpose of the respect of the information in this document in the product data, diagrams, charts, programs, algorithms, and application circuit examples.

3. You should not use the products of the technology described in this document for the purpose of military use. When exporting the products or technology described herein, you should follow the applicable export control laws and regulations, and procedures required by such laws and regulations, and procedures required to change without any plan protein. Before purchasing or using any Renesas products listed in this document, in the development is satisfied. The procedure is a such as that disclosed through our website, (http://www.renesas.com)

3. Renesas has a used reasonable care in compling the information included in this document, but requires a subject to the procedure of the procedure of the procedure of t

#### **RENESAS SALES OFFICES**

http://www.renesas.com

Refer to "http://www.renesas.com/en/network" for the latest and detailed information.

#### Renesas Technology America, Inc.

450 Holger Way, San Jose, CA 95134-1368, U.S.A Tel: <1> (408) 382-7500, Fax: <1> (408) 382-7501

Renesas Technology Europe Limited

Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K.

Tel: <44> (1628) 585-100, Fax: <44> (1628) 585-900

Renesas Technology (Shanghai) Co., Ltd.

Unit 204, 205, AZIACenter, No.1233 Lujiazui Ring Rd, Pudong District, Shanghai, China 200120 Tel: <86> (21) 5877-1818, Fax: <86> (21) 6887-7898

Renesas Technology Hong Kong Ltd.

7th Floor, North Tower, World Finance Centre, Harbour City, 1 Canton Road, Tsimshatsui, Kowloon, Hong Kong Tel: <852> 2265-6688, Fax: <852> 2730-6071

**Renesas Technology Taiwan Co., Ltd.** 10th Floor, No.99, Fushing North Road, Taipei, Taiwan Tel: <886> (2) 2715-2888, Fax: <886> (2) 2713-2999

Renesas Technology Singapore Pte. Ltd.

1 Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632 Tel: <65> 6213-0200, Fax: <65> 6278-8001

Renesas Technology Korea Co., Ltd. Kukje Center Bldg. 18th Fl., 191, 2-ka, Hangang-ro, Yongsan-ku, Seoul 140-702, Korea Tel: <82> (2) 796-3115, Fax: <82> (2) 796-2145

Renesas Technology Malaysia Sdn. Bhd

Unit 906, Block B, Menara Amcorp, Amcorp Trade Centre, No.18, Jalan Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Tel: <603> 7955-9390, Fax: <603> 7955-9510