# **Multiport Register File**

# **ADSP-3128A**

# FEATURES

128×16 or 64×32 Register File Organization Flexible "Crossbar" Data Routing via Five Ports

Two Input

Two Output

One Bidirectional

Cascadable Horizontally and Vertically

Supports 20MHz Operation from Single 1×Clock 18ns Clock-to-Valid Output (Registered)

35ns Address-to-Valid Output (Transparent)

Flexible Latching Modes at Address and Data Ports:

Transparent, Latched, Registered

**Prioritized Write Ports**

Write Inhibit Control on Each Write Port

Automatically Pipelined Bank Select and Port Select

Register-to-Register Transfers Three-State Outputs

Fully Static Operation

145-Pin Grid Array

# **APPLICATIONS**

High Speed Temporary Data Storage in Digital Signal Processing Numeric ProcessingGraphics

# GENERAL DESCRIPTION

Floating-Point and Fixed-Point

The ADSP-3128A Multiport Regif er Fig. 1 a seartife data storage component that can greatly expand the computations

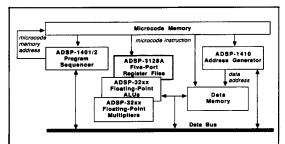

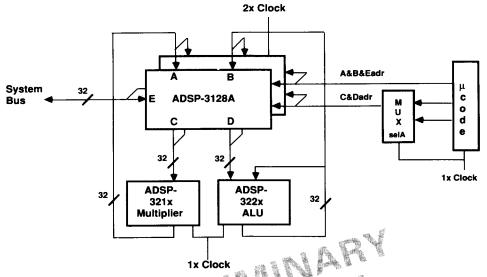

Word-Slice® Floating-Point Microcoded System with ADSP-3128A Multiport Register Files

bandwidth of a fast-arithmetic processor. (See Figure 1 for the ADSP-3128A's Functional Block Diagram.) The ADSP-3128A also simplifies processor design by permitting flexible data routing through its five 16-bit data ports: two input ports, two output ports and a sid ectional port. This register file complements the floating-point and fixed-point multipliers and ALUs available from Analy Devices. Because of its flexibility, however, it is application in a broad range of processor designs. The ADSP-31 son is a higher speed, pin-compatible upgrade from the ADSP-3128.

Figure 1. ADSP-3128A Multiport Register File Functional Block Diagram

This information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future manufacture unless otherwise agreed to in writing.

The ABSP-3138A is a support of the Single-Precision 128×16 configuration, the ADSP-3128A is best suited for fixed-point and single-precision (32-bit) floating-point data storage. For single-precision floating-point, two register files should be used "horizontally" yielding 128 words of 32-bit storage. The 64×32 Double-Precision configuration is intended for double-precision (64-bit) floating-point, again with two register files in a horizontal architecture. In this Double-Precision mode, the register files will each transfer 16-bits in each phase of the clock, 32-bits of data per port in a one-cycle write or read operation. Microcode need only be applied to the register file at the system's 1×clock rate.

To accommodate critical system timing requirements, the ADSP-3128A offers a variety of latching modes on both data and address ports. The prioritized write data ports have control lines that define the input data latching mode for Single-Precision as (a) latched on clock HI, (b) transparent or (c) registered on the clock's falling edge. However loaded, data can also be held at the input latches for subsequent cycles.

In Single-Precision mode, the Multiport Register File's five ports allow five 16-bit data transfer operations per cycle. The input and output latches transfer data to and from the ADSP-3128A's RAM using 16-bit internal buses. The bidirectional Edata-Port can be directly controlled to either write or read. Normal operation allows up to three 16-bit writes in clock HI and three 16-bit reads in clock LO per cycle. Register-to-register transfers are made via the bidirectional Edata-Port (which can be accomplished in two sequential clock phases by following a read with a write). See the Applications Note, "Register-to-Register Transfers with the ADSP-3128A."

In Double-Precision mode, the Multiport Register File's five possallow five 32-bit data transfer operations per cycle for a total bandwidth of 160 bits per cycle. The input and output latches transfer data to and from the RAM via 32-bit internal buses. The input data latching modes allow either an early input or a late input mode. With early input, the Y\_Word (Y\_W) is presented to the input data latches in clock HI and the X\_Word (X\_W) in clock LO. With late input, the Y\_Word is presented to the input latches in clock LO and the X\_Word in clock HI of the next cycle. For data transfers with a slower system bus, the Edata-Port allows both input and output values to be transferred more slowly than the ADSP-3128A's clock rate (Edata Slow Input and Edata Slow Read). Register-to-register transfers are made via the bidirectional Edata-Port.

Each write data port of the ADSP-3128A has an independent write-inhibit control that disables the write operation that normally occurs during clock HI. Write-inhibit allows cancelling a write based on an external condition.

The read data ports have control lines that define the output data latching mode for Single-Precision as (a) registered on the clock's rising edge or (b) transparent. In Double-Precision mode, the output data latching modes allow either an early read or a late read. With early read, the Y\_Word can be output in clock LO and the X\_Word in clock HI of the next cycle. With late read, the Y\_Word can be output in clock HI and the X\_Word in clock LO of the same cycle. Each read data port has an independent tristate control that allows putting that output port into a high impedance state.

can be mutually defined to latch addresses in one of two ways. Either (a) write addresses are latched to the address latches on clock HI, or (b) the address latches are transparent. The 7-bit read address latches can be mutually defined to latch addresses in one of two different ways. Either (a) read addresses are registered to the address latches on the clock's rising edge, or (b) the address latches are transparent. In Double-Precision mode, there are half as many words that are twice as wide. For Double-Precision addressing, the (unneeded) highest order address bits function as Port Select lines. Port Select (the most significant address bit) enables or disables individual ports consistent with their pipelines.

Bank Select enables or disables an entire ADSP-3128A consistent with all read and write pipelines. Bank Select and Port Select allow the user to expand register file storage "vertically" for more than 128 single-precision or 64 double-precision data words.

The ADSP-3128A is fabricated in double-metal 1.0µm CMOS. Each chip consumes significantly less power than comparable bipolar solutions.

The ADSP-3128A is available for both commercial and extended temperature ranges. Extended temperature range parts are available processed fully to MIL-STD-883, Class B. The ADSP-3128A is packaged in a ceramic 145-lead pin grid array.

| TABLE OF CONTENTS                                 | PAGE |

|---------------------------------------------------|------|

| GENERAL DESCRIPTION                               | 345  |

| ADSP-3128A MULTIPORT REGISTER                     | 3-47 |

| PIN LIST (Positive True Logic Convention)         | 3-47 |

| FUNCTIONAL DESCRIPTION                            | 3-47 |

| CONTROLS                                          | 3-48 |

| ADDRESS LATCHES FOR BOTH SINGLE-                  |      |

| AND DOUBLE-PRECISION MODES                        | 3-51 |

| SINGLE-PRECISION OPERATION                        | 3-51 |

| SP Reads                                          | 3-51 |

| SP Writes                                         | 3-52 |

| SP Bidirectional Edata-Port                       | 3-52 |

| SP Input to Input Latches and Hold                | 3-52 |

| SP Bank Select                                    | 3-52 |

| DOUBLE-PRECISION OPERATION                        | 3–53 |

| DP Normal Reads                                   | 3-53 |

| DP Writes                                         | 3–54 |

| DP Edata-Port Slow Input and Slow Read            | 3-54 |

| DP Input to A&B Data-Port Input Latches and Hold. | 3–54 |

| DP Bank Select and Port Select                    | 3-54 |

| DP/SP Changeover                                  | 3–55 |

| DESIGN CONSIDERATIONS                             | 3–55 |

| Power Up                                          | 3–5: |

| Power Supply Decoupling                           | 3–55 |

| ADDENDUM: KEY CHANGES FROM JUNE 1988              |      |

| ADSP-3128 PRELIMINARY DATA SHEET                  |      |

| SPECIFICATIONS                                    | 3–57 |

| TIMING DIAGRAMS                                   | 360  |

| PINOUT                                            | 3–7  |

|                                                   |      |

This information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future manufacture unless otherwise agreed to in writing.

3-46 MICROCODED SUPPORT COMPONENTS

### ADSP-3128A MULTIPORT REGISTER FILE PIN LIST (POSITIVE TRUE LOGIC CONVENTION)

| Pin Name              | Description                                      |

|-----------------------|--------------------------------------------------|

| DATA PORT             | S                                                |

| Adata <sub>15-0</sub> | Write Adata-Port Input Data                      |

| Bdata <sub>15-0</sub> | Write Bdata-Port Input Data                      |

| Cdata <sub>15-0</sub> | Read Cdata-Port Output Data                      |

| Ddata <sub>15-0</sub> | Read Ddata-Port Output Data                      |

| Edata <sub>15-0</sub> | Bidirectional Edata-Port Input and Output Data   |

| ADDRESS P             |                                                  |

| Aadr <sub>6-0</sub>   | Address Port for Adata-Port Writes               |

| Badr <sub>6-0</sub>   | Address Port for Bdata-Port Writes               |

| Cadr <sub>6-0</sub>   | Address Port for Cdata-Port Reads                |

| Dadr <sub>6-0</sub>   | Address Port for Ddata-Port Reads                |

| Eadr <sub>6-0</sub>   | Address Port for Edata-Port Writes and Reads     |

|                       | and for Register-to-Register Transfers           |

| GENERAL C             |                                                  |

| BS                    | Bank Select (registered or asynchronous,         |

|                       | depending on address port Latches)               |

| DP                    | Double-Precision Mode (registered)               |

| ADDRESS L             | ATCH CONTROLS                                    |

| Wadtrn                | Write Address Latch Transparent (registered)     |

| Radtrn                | Read Address Latch Transparent (registered)      |

| DATA INPU             | T AND WRITE CONTROLS                             |

| ABlt, ABht            | Input Latch Controls for Both Adata-Port and     |

| ,                     | Bdata-Port (registered)                          |

| Elt, Eht              | Input Latch Controls for Edata-Port (registered) |

| Awinh                 | Inhibit Write to RAM from Adata-Port Input       |

|                       | Latches (asynchronous)                           |

| Bwinh                 | Inhibit Write to RAM from Bdata-Port Input       |

|                       | Latches (asynchronous)                           |

| Ewinh                 | Inhibit Write to RAM from Edata-Port Input       |

|                       | Latches (asynchronous)                           |

| DATA REAL             | AND OUTPUT CONTROLS                              |

| CDtran                | Output Latch Controls (Make Transparent) for     |

|                       | Both Cdata-Port and Ddata-Port (registered)      |

| Etran                 | Output Latch Controls (Make Transparent) for     |

|                       | Edata-Port (registered)                          |

| Rfltran               | Clock-On-Rising/Falling Select for Slow Inputs   |

|                       | in Double-Precision Mode (registered)            |

| Eio                   | Edata-Port Slow Read Control in                  |

|                       | Double-Precision Mode (registered)               |

| Ctri                  | Cdata-Port Three-State Control (asynchronous)    |

| Dtri                  | Ddata-Port Three-State Control (asynchronous)    |

| Etri                  | Edata-Port Three-State Control (asynchronous)    |

| MISCELLAN             |                                                  |

| CLK                   | Clock                                            |

Ground (Eight Lines)

+5V Power Supply (Three Lines)

GND

$V_{\mathbf{D}\mathbf{D}}$

#### FUNCTIONAL DESCRIPTION

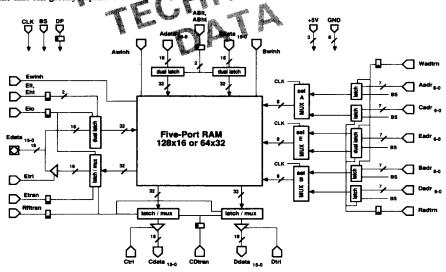

The ADSP-3128A Multiport Register File consists of a high speed static RAM (configurable as either  $128 \times 16$  or  $64 \times 32$ ) surrounded by the latches and control logic needed for simple system interfacing (see Figure 1). Six internal data paths, all 32-bits wide, connect this RAM with multiplexers (muxes) and latches. Three are read data paths; three are write data paths. Three 7-bit internal address paths connect this RAM with muxes and address latches. These three address paths are internally timemultiplexed to allow the presentation of six addresses to the RAM per cycle.

Three addresses are presented to RAM in clock HI from the Aadr, Badr and Eadr address latches. These are RAM write addresses. They are prioritized in case of conflict. Three addresses are presented to RAM in clock LO from the Cadr, Dadr and Eadr address latches. These are RAM read addresses. Three simultaneous reads, even from the same RAM location, are possible for clock LO reads. The Eadr-Port feeds both a write (clock HI) address latch and a read (clock LO) address latch, which can be independently set to latched or transparent modes.

Writes to the RAM occur in clock HI when Awinh and/or Bwinh and/or Ewinh are LO. Note that data writen in clock HI is available to be read in the same clock cycle.

The DP control determines whether the Register File is in Double-Precision mode (HI) or Single-Precision mode (LO). In Single-Precision mode, all data paths between RAM and data latches behave as if they were 16 bits. The data latches also behave like 16-bit latches. The register file is organized 128×16 in Single-Precision mode, and each location is addressed with seven bits. DP can be changed dynamically, consistent with the constraints imposed in the timing diagrams (Figures 4 through 13).

In Double-Precision mode, the Register File is organized 64×32, and each location is addressed with six bits. In Double-Precision mode, all data paths between RAM and data latches are 32 bits, as are the data latches. Writes (32-bit) to the RAM occur in clock HI and reads (32 bit) from the RAM occur in clock LO. Multiplexers between the latches and the 16-bit data ports alternately select Y\_Word and X\_Word. Note that when ADSP-3128A Register Files are configured in horizontal pairs for Double-Precision operation, the Y\_Words from the pair will make up half the external 64-bit double-precision word and the X Words the other half. See Figures 14 and 15.

In Single-Precision mode, the input latches can be configured to latch input data at clock HI, register input data on the falling clock edge, be made transparent, or hold the most recent data. The output latches can be configured to register data from the RAM on the rising clock edge or to be transparent clock LO and latched clock HI. The bidirectional Edata-Port can be configured to do either one read or one write each cycle. Each read port has an independent three-state enable control.

This information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future manufacture unless otherwise agreed to in writing.

In Double-Precision mode, the input latches can be configured for an early input, a late input, a slow input on the Edata-Port (for transfers from slow devices), or a hold of the most recent data on the A&Bdata-Ports. Early and late inputs are distinguished by a one-half clock cycle difference between when the Y\_Word and X\_Word are written to the input latches. The output latches can be configured for an early read, a late read or a slow read on the Edata-Port (for transfers to slow devices). Early and late reads are distinguished by a one-half clock cycle difference between when the Y\_Word and X\_Word are read from the output latches. To accomplish late inputs and early reads, the latches are transparent for 16 bits of the data transfer, allowing either a direct write of the X\_Word to RAM or a direct read of the Y\_Word from RAM, respectively.

The write address latches can be made transparent or latched in clock HI. The read address latches can be made transparent or registered with the clock's rising edge. In Double-Precision

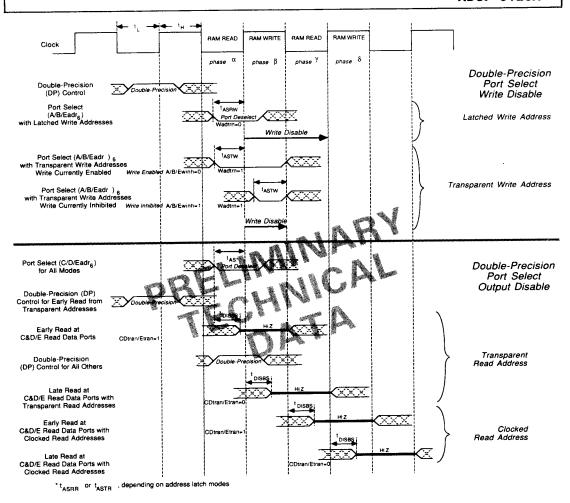

mode, the unused high-order address bit is interpreted as Port Select. Port Select and Bank Select (BS) are treated as part of the address field so that their write-disable and three-state effects properly track the selected pipeline delays.

#### CONTROLS

The ADSP-3128A Register File has 18 control lines. Their functional descriptions are summarized in mode Tables I through III.

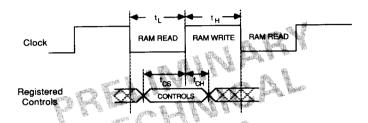

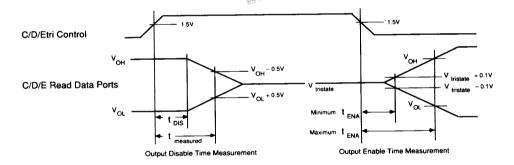

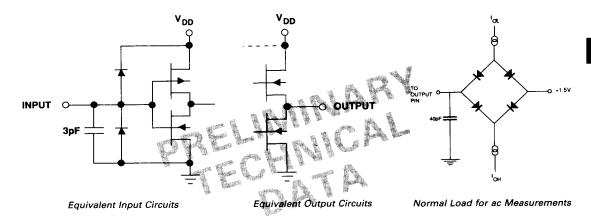

Most control lines are registered, as indicated in the "Pin List" and in Figure 1. All registered controls meet the timing requirements of Figure 2. The timing requirements for the three asynchronous three-state controls, Ctri, Dtri and Etri, are shown in Figure 3. The timing for the remaining asynchronous controls are illustrated in timing diagrams Figures 2 through 13.

Figure 2. ADSP-3128A Registered Controls Timing

Figure 3. ADSP-3128A Three-State Disable and Enable Timing

This information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future manufacture unless otherwise agreed to in writing.

#### 3-48 MICROCODED SUPPORT COMPONENTS

| BS | DP | AB&Elt            | AB&Eht              | A&B&Einh | Rfltran  | Description                                                                                                                             |

|----|----|-------------------|---------------------|----------|----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 0  | X  | X                 | X                   | X        | X        | Disable chip (consistent with pipelines) but advance pipelines with clock cycle                                                         |

| 1  | 0  | 0                 | 0                   | X        | X        | Register write data at A&B or Edata input latches on falling edge                                                                       |

| 1  | 0  | 0                 | 1                   | X        | X        | Hold most recent data at A&B or Edata input latches for the next cycle                                                                  |

| 1  | 0  | 1                 | 0                   | X        | X        | Latch write data at A&B or Edata input latches at clock HI                                                                              |

| 1  | 0  | 1                 | 1                   | X        | X        | Make transparent A&B or Edata input latches                                                                                             |

| 1  | X  | X                 | X                   | 0        | X        | Allow write to RAM from the A, B and Edata input latches                                                                                |

| 1  | X  | X                 | X                   | 1        | X        | Inhibit write to RAM from the A, B and Edata input latches                                                                              |

| 1  | 1  | 0                 | 0                   | X        | X        | Early Input to A&B or Edata input latches: register Y_W on falling edge to input latches and latch X_W to input latches in clock HI     |

| 1  | 1  | 0                 | 1                   | X        | <b>X</b> | Late Input to A&B or Edata input latches: latch Y_W to input latches in clock HI and make input latches transparent for X_W in clock HI |

| 1  | 1  | 1                 | X                   | X        | Х        | Hold most recent data at A&B input latches for the next cycle                                                                           |

| 1  | 1  | 1                 | 1 → 0               | X        | Ó        | Edata Slow Input: register Y_W to Edata input latch on next falling edge (Eht only)                                                     |

| 1  | 1  | 1                 | <b>0</b> → <b>1</b> | <b>X</b> | 0        | Edata Slow Input: register X_W to Edata input latch on next falling edge (Eht only)                                                     |

| 1  | 1  | 1 → 0             | 1                   | X        | 1        | Edata Slow Input: register Y_W to Edata input latch on next rising edge (Elt only)                                                      |

| 1  | 1  | $0 \rightarrow 1$ | 1                   | X        | 1        | Edata Slow Input: register $X_W$ to Edata input latch on next rising edge (Elt only)                                                    |

Table I. ADSP-3128A Summary of Data Input and Write Control Modes

| BS | DP | CD&Etran | Rfltran | C&D&Etri | Eio | Description                                                                                                                                                            |

|----|----|----------|---------|----------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0  | Х  | Х        | X       | X        | X   | Disable chip (consistent with pipelines) but advance pipelines with clock cycle                                                                                        |

| 1  | X  | X        | X       | 0        | X   | Drive data from output latches through C or D or Edata-Port                                                                                                            |

| 1  | X  | X        | x       | 1        | X   | Three-state (high impedance) output $C$ or $D$ or Edata-Port                                                                                                           |

| 1  | 0  | 0        | X       | X        | X   | Register data from RAM to C&D or Edata output latches on rising edge                                                                                                   |

| 1  | 0  | 1        | 0       | X        | x   | C&D or Edata output latches are transparent clock LO, latched clock HI                                                                                                 |

| 1  | 0  | x        | X       | X        | 0   | Edata-Port is configured for one read or one write per cycle                                                                                                           |

| 1  | 1  | 0        | 0       | X        | 0   | Configured for Late Read at C&D or Edata-Port: register Y_W & X_W from RAM to output latches on rising edge; output Y_W in clock HI, output X_W on next clock LO       |

| 1  | 1  | 1        | 0       | X        | 0   | Configured for Early Read at C&D or Edata-Port: output Y_W from RAM through transparent output latches in clock LO; latch X_W to output latches and output in clock HI |

| 1  | 1  | 0        | 0       | X        | 1   | Configured for Edata Slow Read: hold RAM read data at Edata output latch; output Y_W at clock HI                                                                       |

| 1  | 1  | 1        | 0       | X        | 1   | Configured for Edata Slow Read: hold RAM read data at Edata Output Latch; output X_W at clock HI                                                                       |

| 1  | 1  | X        | 1       | X        | X   | Defines Clock-On-Rising/Falling mode for Edata Slow Inputs                                                                                                             |

Table II. ADSP-3128A Summary of Data Read and Output Control Modes

| BS | DP | Wadtrn | Radtrn | A/B/C/D/Eadr <sub>6</sub> (Port Select) | Description                                                                     |

|----|----|--------|--------|-----------------------------------------|---------------------------------------------------------------------------------|

| 0  | Х  | X      | X      | X                                       | Disable chip (consistent with pipelines) but advance pipelines with clock cycle |

| 1  | X  | 0      | X      | X                                       | Latch A or B or Eadr write addresses at clock HI                                |

| 1  | X  | 1      | X      | X                                       | A or B or Eadr write address latches are transparent                            |

| 1  | X  | X      | 0      | X                                       | Register C or D or Eadr read address latches on the rising edge                 |

| ı  | X  | X      | 1      | X                                       | C or D or Eadr read address latches are transparent                             |

| x  | 1  | X      | X      | 0                                       | Disable A/B/C/D/Edata-Port                                                      |

| 1  | 1  | X      | X      | 1                                       | Enable A/B/C/D/Edata-Port                                                       |

Table III. ADSP-3128A Summary of Address Control Modes

# 3-50 MICROCODED SUPPORT COMPONENTS

# ADDRESS LATCHES FOR BOTH SINGLE- AND DOUBLE-PRECISION MODES

The three read (clock HI) address latches and three write (clock LO) address latches hold the seven bits required for Register File addressing, Port Select and Bank Select. Radtrn controls whether the three read address latches are transparent or latched; Wadtrn controls whether the three write address latches are transparent or latched. When Radtrn/Wadtrn is HI, addresses presented at the read/write address ports are transferred directly to the RAM with no pipeline delay. When Radtrn is LO, addresses presented at the read address ports are registered on the rising edge of the clock, to be used during the next clock LO. When Wadtrn is LO, addresses presented at the write address ports are latched on the rising edge of the clock, to be used immediately during the next clock HI.

Both Radtrn and Wadtrn latch controls are registered and affect the configuration of the address latches on the rising clock edge in which they are registered. They remain in effect until the next rising edge.

Transparent addresses must be valid at least  $t_{AST}$  before the end of the phase in which they are used. The setup time for latched or registered addresses is  $t_{ASR}$ . All addresses must be held valid  $t_{AH}$  after the end of the phase in which they are asserted.

Output delays for transparent data reads from transparent addresses are referenced from address valid. However, an address valid prior to the clock LO in which the RAM is read provides no additional benefit. The output delay, todt, is referenced from address valid or the clock falling edge – whichever is later. The transparent read address must be held valid throughout the RAM read phase.

#### SINGLE-PRECISION OPERATION

Single-Precision mode is determined by the registered DP control being LO. Single-Precision mode must be asserted as shown in the timing diagrams to insure that the high-order single-precision address bits are *not* misinterpreted as Double-Precision Port Select bits and that latch controls are given their proper Single-Precision interpretation. A general discussion of dynamic switching between Single- and Double-Precision modes can be found below in "DP/SP Changeover." In Single-Precision mode, the Register File is configured as 128 words that are 16 bits in width. The 128 words are addressed by 7-bit addresses from the five address ports. All data paths and data latches behave as if they were 16 bits wide.

Up to five 16-bit data transfers per cycle are possible in Single-Precision mode. These transfers can be comprised of three writes and two reads, or two writes and three reads.

#### SP Reade

The operations of transferring data from RAM to a latch and from a latch to the output pins are logically distinct with the ADSP-3128A. Transfers from RAM to latch are called "reads" in this data sheet; transfers from latch to output port are called "outputs."

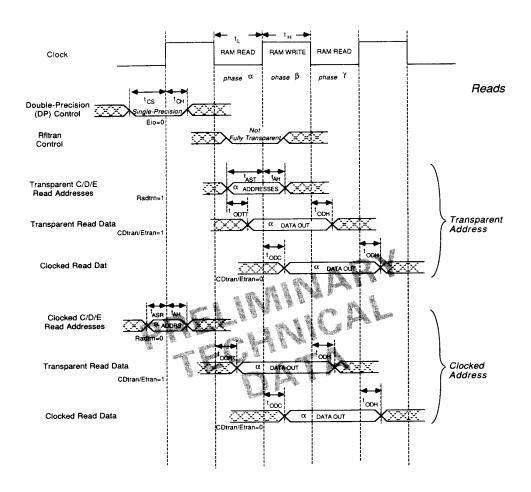

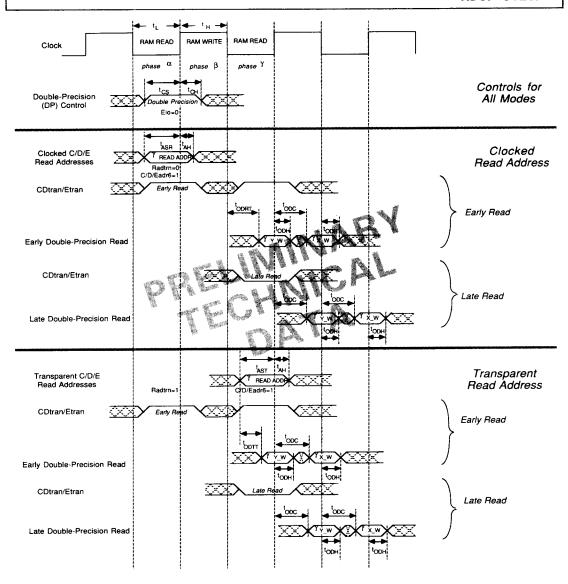

Read addresses can be transparent or registered (Figure 4). In all timing diagrams, the phase in which an address causes a RAM read or write is indicated by a Greek letter. For Figure 4's reads, all addresses shown cause a read in phase  $\alpha$ . Not all controls are shown on this or other timing diagrams as explicit waveforms. In Figure 4, for example, the expression "Radtrn = 1" at a rising edge implies that Radtrn was asserted HI before that edge and met the standard setup and hold time requirements of Figure 2 for controls.

The output latches can be set transparent via registered controls CDtran HI and/or Etran HI. Note that one control, CDtran, affects both Cdata-Port and Ddata-Port output latches. From a transparent read address (Radtrn HI), read data when the output latches are transparent will be valid todata when the output latches are transparent will be valid todata will be valid todate. From a transparent read address, read data will be valid todate after the rising clock edge when the output latches are in registered mode from the C&Ddata-Ports and/or the Edata-Port.

When the read addresses are registered (Radtrn LO), the data output timing is very similar except that the output delay for a transparent read is now referenced from a clock edge rather than address valid. The transparent read data will be valid t<sub>ODRT</sub> after the falling clock edge.

Note that in all four combinations of address and output latching modes, the read from RAM took place in phase  $\alpha.$  Specifying registered output latches simply introduces an additional clock phase of pipelining. Note also that for all Single-Precision reads, the data out is held valid throughout the phase after the data became valid. In the case of transparent data reads, the latch is actually holding the data valid for this phase. Data will be held valid  $t_{\rm ODH}$  after the clock edge for all reads (in all modes).

Each read port has its own asynchronous three-state control: Ctri, Dtri and Etri. See Figure 3 for enable and disable timing.

This information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future manufacture unless otherwise agreed to in writing.

### SP Writes

Single-Precision mode must be asserted as shown in Figure 5 to insure that the high-order single-precision address bits are not misinterpreted as Double-Precision Port Select bits and that latch controls are given their proper Single-Precision interpretation. The operations of transferring data from a port to a latch and from a latch to the RAM are logically distinct with the ADSP-3128A. Transfers from port to latch are called "inputs" in this data sheet; transfers from latch to RAM are called "writes."

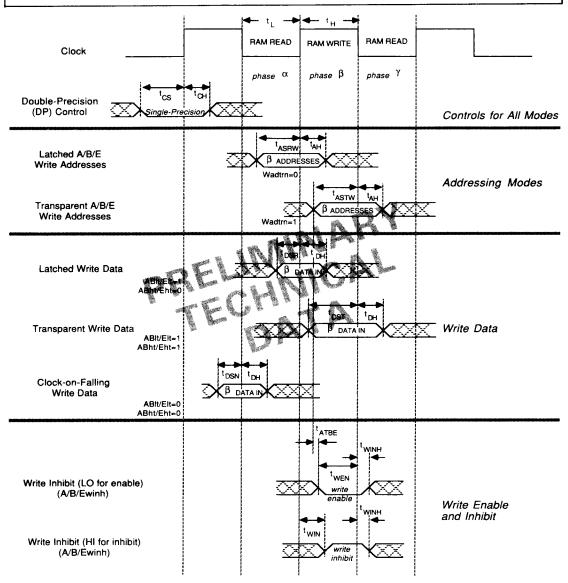

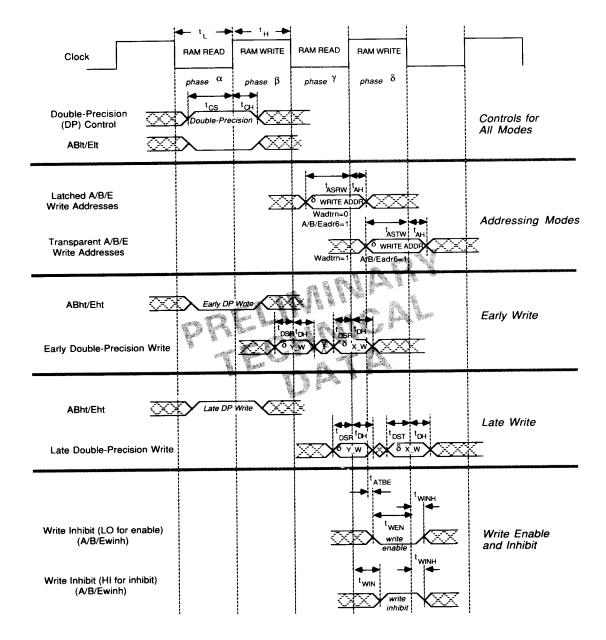

Write addresses can be transparent (Wadtrn HI) or registered (Wadtrn LO), exactly as with read addresses (Figure 5).

The Adata-Port and Bdata-Port input latches can be set to transparent, latched or clock-on-falling mode via the ABlt and ABht controls (Table I and Figure 5). The Edata-Port input latch can be set to transparent, latched or clock-on-falling mode via the Elt and Eht controls. When the "lt" and "ht" controls are both asserted HI, the latches are transparent ("t"). When only "lt" is asserted, the latches are in latched mode ("l"). When only "ht" is asserted the latches are in hold mode ("h"). When both controls are LO, the latches are in clock-on-falling mode.

Note that one set of controls, ABlt and ABht, affects both Adata-Port and Bdata-Port input latches. (These controls also permit holding the most recent write data at the input latches. See "SP Input to Input Latches and Hold" below.) These controls are always registered on the rising edge and become effective as of the next falling edge. When the input latches are transparent, write data must be valid to be below the end of the write phase. When the input latches are in latched mode, write data must be valid tobs before the beginning of the write phase. When the input latches are in clock-on-falling mode, write data must be valid tobs before the falling clock edge prior to the write phase. In all cases, the write data presented at write data ports must be held toh after the next clock edge.

The operations of inputting data to an input latch and writing data from the input latch to RAM are distinct. To write input data to the RAM, the asynchronous Write Inhibit Controls (Awinh, Bwinh, and/or Ewinh) must be LO as shown in Figure 5. Writes should be enabled no later than  $t_{\rm WEN}$  before the falling edge.

Note that a write can be enabled later than a write can be inhibited. If you might want to inhibit a write to the Register File as late as the very phase in which a write is attempted, you can keep the A/B/Ewinh controls normally HI, i.e., write inhibited, and bring them LO every time you actually want to write. Alternatively, for simplicity, the A/Bwinh controls can be wired LO (write enable) and dummy writes be performed to an unused RAM location in every clock HI. Write addresses must always be stable, however, whenever the Write Inhibit controls are LO. In general, do not hardwire Ewinh LO; any Edata-Port output data will be written back to unintended RAM locations.

The write ports are prioritized with the Edata-Port of highest priority, followed by the Adata-Port, followed by the Bdata-Port. If writes to the same RAM location are attempted in a given clock HI phase, the data presented at the higher priority enabled write data port will be the data written to RAM.

#### SP Bidirectional Edata-Port

The Edata-Port will behave like any write port if treated as such according to the timing diagrams. Alternatively, it will also behave like any read port if treated as such. The Edata-Port can be used as a write port in one cycle, a read port in the next and a write port in the third cycle, as long as the Edata-Port is disabled to high impedance before setting up write data.

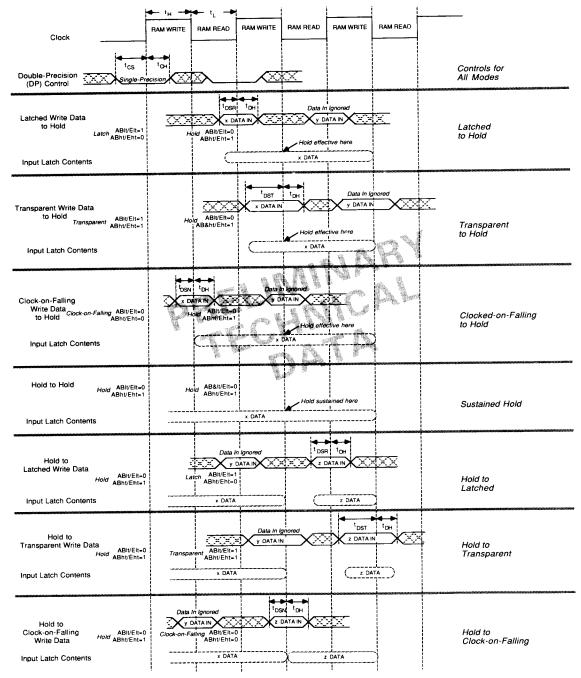

# SP Input to Input Latches and Hold

Data input to the input latches can be held at those latches with the ABlt and ABht and Elt and Eht controls (Table I). These controls are always registered on the rising edge and become effective at the next falling edge. Figure 6 shows how data written to the latches in any of the three input modes can be held at a latch as long as desired. As of the falling edge after hold is asserted, data at the write data port is ignored and will be ignored until the next falling edge after one of the three input modes is asserted. The hold feature allows the input latches to be used for temporary data storage. Examples of using this feature include delaying a write to the RAM to avoid overwriting some data currently in the RAM or writing the same data to multiple RAM locations.

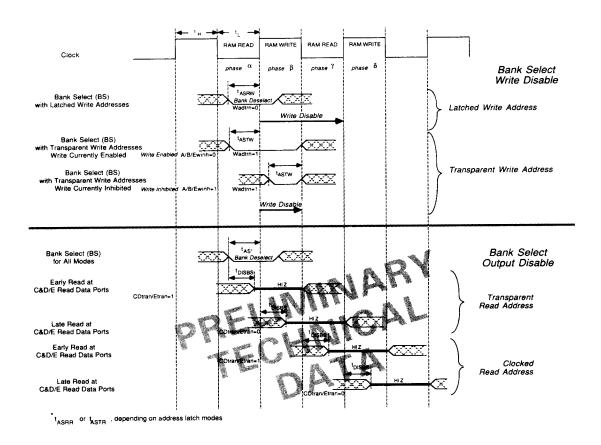

#### SP Bank Select

Bank Select is treated in exactly the same way in both Single-Precision and Double-Precision modes (Figure 12). The BS control is not registered in general but rather follows the addresses through the address latches (Figure 1). Hence, its setup requirement is tast and tast the setup requirement for read and write addresses for transparent and latched/registered modes respectively. All applicable requirements must be met. Flowing with addresses allows Bank Select to track all read and write pipelines as shown in Figure 12. When LO, writes will be disabled and output ports put in high impedance.

With Bank Select, the user's register file space can be extended "vertically" beyond 128 single-precision words to whatever register file space is desired. The user would typically use more than seven bits for addressing, decoding the high-order bits to select a horizontal row of ADSP-3128As that produce a single "word" and applying the low-order seven bits to the address ports in all rows.

The only restriction on extending the register file address space using Bank Select is that all reads and writes in a given cycle must be from the same horizontal row of ADSP-3128As. (Port Select removes this restriction for Double-Precision mode). In Single-Precision mode, the user can select/deselect individual ports, even if in different rows, using the asynchronous Write Inhibit and Three-State controls. The user would have to apply these with timing based on the latch modes currently selected to properly track the pipelines.

Note that the timing requirements for Bank Select are simple if write addresses are latched but are more complicated for transparent write addresses because of the way BS flows with the write address. For a Bank Deselect, the BS control must be LO in the clock HI write phase  $\beta$  (Figure 12). If writes are currently enabled, BS must be set up in phase  $\alpha$ ; if they're inhibited, BS is not needed LO until phase  $\beta$  to disable writes. The Write Inhibit controls for the three write data ports are independent. Therefore, if any Write Inhibit is LO (write enable) in phase  $\alpha$ , BS will have to be LO in phase  $\alpha$  to disable all writes.

This information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future manufacture unless otherwise agreed to in writing.

3-52 MICROCODED SUPPORT COMPONENTS

#### DOUBLE-PRECISION OPERATION

Double-Precision mode is determined by the registered DP control being HI. A general discussion of dynamic switching between Single- and Double-Precision modes can be found below in "DP/SP Changeover." In Double-Precision mode, the Register File is configured as 64 words that are 32 bits in width. The 64 words are addressed by 6-bit addresses from the five address ports. The seventh, high-order bit used in Single-Precision addressing becomes a Port Select bit. All data paths between RAM and data latches are true 32-bit paths. That is, all 32-bit reads from the RAM to the latches and 32-bit writes to the RAM from the latches take place in a single read or write clock phase. The ports, however, are 16-bits wide. Data transfers through the ports are time-multiplexed.

The ADSP-3128A automatically controls the multiplexing through the data ports once the DP control is HI. The user only supplies one address to reference the two 16-bit halves of the data word transferred through the data ports. In Edata-Port Slow Input and Slow Read modes, however, the user has direct control over these multiplexers to allow communication with slower devices.

Up to five 32-bit data transfers per cycle are possible in Double Precision mode. These five transfers can be comprised of three writes and two reads or two writes and hore hads, depending on whether the Edata-Port is used as a read port or a write por

Double-Precision mode is intended for interfacing to processors that use time-multiplexed 64-bit data, like analy Device ADSP-32XX Floating-Point Multipliers and ADSP-32XX Floating-Point ALUs. Normally, two ADSP-3128A Multiport Register Files would be used "horizontally" to communicate with 32-bit buses.

In the descriptions that follow, one 16-bit half of a given ADSP-3128A's 32-bit word is referenced as an "Y\_Word," the other half as an "X\_Word." Note that normally a user would put together the Y\_Words from two ADSP-3128As to create a 32-bit half of a 64-bit double-precision floating-point number. Similarly, the floating-point number's other 32-bit half would be constituted from the X\_Words of two ADSP-3128As.

What is called a "Y\_Word" in this data sheet is simply the 16-bit half of a 32-bit field that is written to the Register File first and read from the Register File first. But it is nothing more than a semantic convention; what are called here "Y\_Words" can be used used to make up either Most Significant or Least Significant Words, depending on system requirements. The key point is that whichever half is written first will be the half read first.

#### **DP Normal Reads**

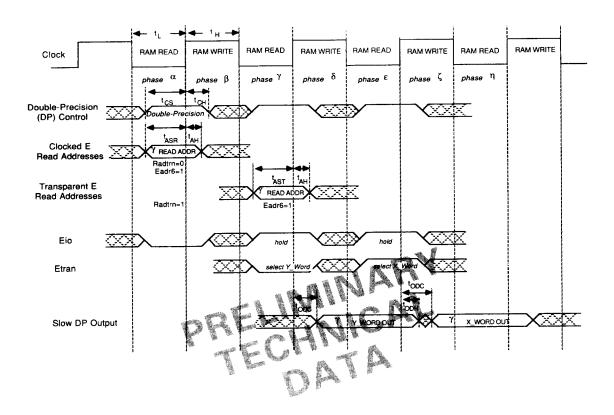

Double-Precision mode must be asserted as shown in Figure 7 to insure that the Port Select bits are *not* misinterpreted as Single-Precision address bits and that latch controls are given their proper Double-Precision interpretation. Addresses can be transparent or registered (Figure 7), just as in Single-Precision mode.

The two normal read options in Double-Precision mode are Early Read and Late Read. They are controlled via registered controls CDtran and or Etran, which can make the output latches transparent or letched. The effect in Double-Precision mode is to creat two pipelining options. Note that one control, CDtran, affects both Cdata-Port and Ddata-Port output latches.

Early Reads are generated when CDtran and/or Etran are HI. The Y Word is read transparently from the RAM in phase γ through the dutput data port with delays, t<sub>ODRT</sub> and t<sub>ODTT</sub>, corresponding to registered and transparent read addresses respectively. The X\_Word is also read from the RAM in phase γ that is seed at the 32-bit output latch to be multiplexed out the output data port in the next phase with output delay t<sub>ODC</sub>. Data hold times for Early Reads, as for all other kinds, is t<sub>ODH</sub>. As described in "Address Latches," the transparent address can be set up before the RAM read phase but t<sub>ODTT</sub> will then be referenced from the falling clock edge rather than address valid.

Late Reads are generated when CDtran and/or Etran are LO. As with Early Reads, both the Y\_Word and X\_Word are read from the RAM to the 32-bit output latches in phase  $\gamma$ . In the case of Late Read, the Y\_Word is held at the output latch until the next phase, when it is driven off chip with delay  $t_{\rm ODC}$ . The X\_Word follows in the phase after that with the same delay characteristic of registered reads.

Each read port has its own asynchronous three-state control: Ctri, Dtri and Etri. See Figure 3 for enable and disable timing.

This information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future manufacture unless otherwise agreed to in writing.

#### **DP** Writes

Double-Precision mode must be asserted as shown in Figure 8 to insure that the Port Select bits are *not* misinterpreted as Single-Precision address bits and that latch controls are given their proper Double-Precision interpretation. Addresses can be transparent or registered (Figure 8), just as with Double-Precision reads.

The two normal write options in Double-Precision mode are Early Write and Late Write. They are exactly analogous to Early Read and Late Read in that they offer two pipelining options. They are controlled via registered controls ABlt, ABht, Elt and Eht as shown in Figure 8 and Table II. Note that one set of controls, ABlt and ABht, affects both Adata-Port and Bdata-Port input latches. These controls become effective as of the falling edge after they are registered.

In Early Write, both Y\_Word and X\_Word are input to the 32-bit input latches before they are both written to RAM in phase  $\delta$ . Both Y\_Word and X\_Word have the setup time requirement,  $t_{\rm DSR}$ , characteristic of latched-mode data inputs. Data hold requirements for Early Write and all other writes is  $t_{\rm DH}$ .

With Late Write, the user can input the Y\_Word and X\_Word into the Register File latches one half cycle later for a write to RAM in the same phase  $\delta$ . The Y\_Word is latched with setup time  $t_{DSR}$ . The X\_Word, however, is transparently written to RAM in phase  $\delta$ . Note that the setup requirement on the X\_Word is therefore  $t_{DST}$ .

The actual write to RAM occurs in the single phase §. Hence the Write Inhibit controls in Double-Precision work exactly as they do in Single-Precision. To write input data to the RAM, the asynchronous Write Inhibit Controls (Awinh, Bwinh and/or Ewinh) must be LO as shown in Figure 8. Writes should be enabled no later than twen before the falling edge.

Note that a write can be enabled later than a write can be inhib<sup>3</sup> ited. If you might want to inhibit a write to the Register File as late as the very phase in which a write is attempted, you can keep the A/B/Ewinh controls normally HI, i.e., write inhibited, and bring them LO every time you actually want to write. Alternatively, for simplicity, the A/Bwinh controls can be wired LO (write enable) and dummy writes be performed to an unused RAM location in every clock HI. Write addresses must always be stable, however, whenever the Write Inhibit controls are LO. In general, do not hardwire Ewinh LO; any Edata-Port output data will be written back to unintended RAM locations.

The write ports are prioritized with the Edata-Port of highest priority, followed by the Adata-Port, followed by the Bdata-Port. If writes to the same RAM location are attempted in a given clock HI phase, the data presented at the higher priority enabled write data port will be the data written to RAM.

## DP Edata-Port Slow Input and Slow Read

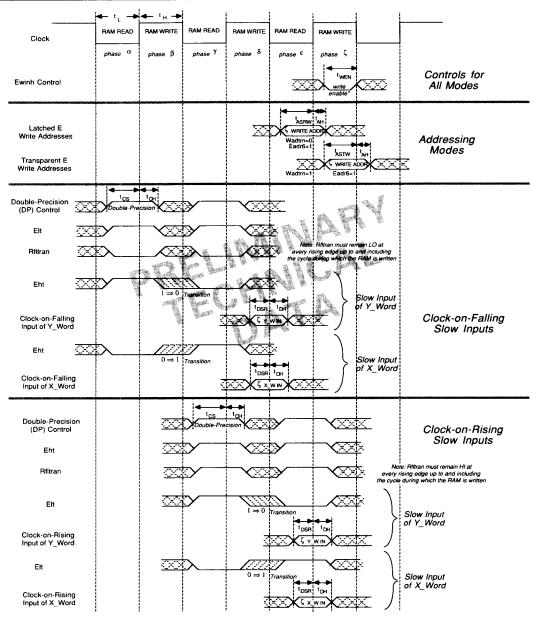

The bidirectional Edata-Port is intended to be the port interfaced to a system bus, which may run more slowly than local buses. To simplify the interface for Double-Precision, the ADSP-3128A provides a mode for loading the Y\_Word and X\_Word into the input latches over multiple ADSP-3128A clock cycles (Figure 9). Also a mode is provided for multiplexing Y\_Word and X\_Word read data from the output latches over multiple clock cycles (Figure 10).

For a Slow Input (Figure 9), the input latches are updated when there is a transition in a designated control input from one clock rising edge to the next clock rising edge. Both Clock-on-Falling and Clock-on-Rising Slow Input modes are supported. Rfltran LO indicates that data is to be loaded on the clock's falling edge, Rfltran HI indicates rising edge. In the case of Clock-on-Falling, the transition in Eht updates the latches while Elt is concurrently HI (Hold mode). Call Eht the "transition control" for Clock-on-Falling and Elt the "background control". Clock-on-Rising reverses the role of these two controls; the transition in Elt causes the latches to update while Eht is concurrently HI. In other words, for Clock-on-Rising, Elt becomes the transition control, Eht the background control. Regardless of which clock edge is loading the data, it must be set up to the input latches with set up time t<sub>DSR</sub> as shown.

When the transition control goes from HI to LO, the external data will be input to the Y\_Word position in the Edata input latch and be held there. When the transition control goes from LO to HI, the external data will be input to the X\_Word position in the Edata input latch and be held there. A write to RAM can be enabled (with Ewinh LO) at the next clock HI from either latched or transparent Eadr.

For a Slow Reist, registered control Eio, when asserted HI in conjunction with Double-Precision (DP HI), configures the Eddta-Port for a Slow Read. When Eio goes HI, data at the output latch is held. In Figure 10, this is the 32-bit data read at phase  $\gamma$ . For a Slow Read, output delays will be  $t_{\rm ODC}$ . Data will be held  $t_{\rm ODC}$  after the clock edges shown in Figure 10. When configured for Slow Read, the ADSP-3128A's registered Etran control becomes a direct, asynchronous controller of the Edata-Port's Duble Becision output multiplexer. When Etran is LO, the Y\_Word read from RAM in phase  $\gamma$  will be driven through the Edata-Port (if enabled with Etri). When Etran is HI, the X\_Word read from RAM in phase  $\gamma$  will be driven through the Edata-Port (if enabled with Etri). The outputs will be driven as long as Eio is HI and Etran doesn't change.

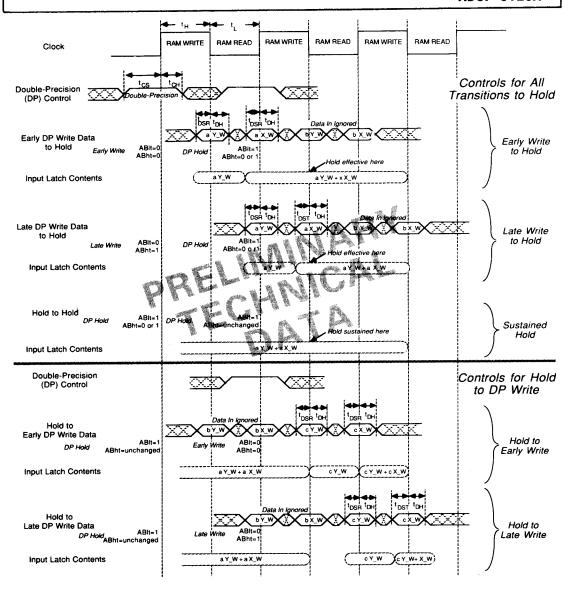

## DP Input to A&B Data-Port Input Latches and Hold

Data input to the A&Bdata-Port input latches can be held at those latches with the ABlt and ABht, controls (Table I). These controls are always registered on the rising edge and become effective as of the next falling edge. Figure 11 shows how data written to the latches in either Early Write or Late Write modes can be held at a latch as long as desired. As of the falling edge after hold is asserted with ABlt HI, data at the write data port is ignored. It will continue to be ignored until the next falling edge after ABlt goes LO. The hold feature allows the input latches to be used for temporary data storage. Note that the Edata-Port supports Input-and-Hold in SP only, since Elt is used in DP for Slow Edata-Port inputs.

#### **DP Bank Select and Port Select**

Bank Select is treated in exactly the same way in both Single-Precision and Double-Precision modes (Figure 12). The BS control is not registered in general but rather follows the addresses through the address latches (Figure 1). In Double-Precision, the seventh address bit (not needed for Double-Precision addressing) is redefined to function as Port Select for the ports being addressed. DP must be asserted HI as shown in Figure 13 to insure that these bits are interpreted as Double-Precision Port Selects and not Single-Precision address bits (and that latch controls are given their proper Double-Precision interpretation).

This information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future manufacture unless otherwise agreed to in writing.

3-54 MICROCODED SUPPORT COMPONENTS

Behaving as addresses, both BS and A/B/C/D/Eadr, have setup requirements of tASTx and tASRx, the setup requirement for read and write addresses for transparent and latched/registered modes, respectively. All applicable requirements must be met. Flowing with addresses allows Bank Select and Port Select to track all read and write pipelines as shown in Figures 12 and 13. When LO, writes will be disabled and output ports put in high

The only restriction on extending the register file address space using Bank Select is that all reads and writes in a given cycle must be from the same horizontal row of ADSP-3128As. Port Select removes this restriction for Double-Precision mode (only). Like Bank Select, the Port Select controls track the ADSP-3128A's internal pipelines. But since every port can be independently selected or deselected, reads can be made from and writes made to any combination of locations in the user's register file space. They need not be all made from the same horizontal row.

Note that the timing requirements for Bank Select and Port Select are simple if write addresses are latched but are more complicated for transparent write addresses because of the way BS and A/B/Eadr<sub>6</sub> flow with the write address. For a Bank or Port Deselect, the BS or A/B/Eadr<sub>6</sub> control must be LO in the clock HI write phase β (Figures 12 and 13). If writes are currently enabled, BS or A/B/Eadr if they're inhibited, BS or A/B/Eadr<sub>6</sub> is not needed LO until phase β to disable writes. Since the Write Inhibit controls for the three write data ports are independent, if any is enabled in phase a, BS or A/B/Eadr<sub>6</sub> will have to be LO in phase  $\alpha$  to disable all writes.

#### **DP/SP** Changeover

Many controls are interpreted and internal states affected by the DP control. The timing diagrams show when DP must be HI and when it must be LO to accomplish the operation described in each timing diagram. For times when the state of DP is not explicitly shown, it can be changed. That is, the user can dynamically reconfigure the ADSP-3128A from Single-Precision to Double-Precision and conversely as long as these restrictions are observed.

### Internal RAM Organization

It may be useful to know that a 32-bit word in Double-Precision mode consists of two 16-bit words that can be addressed in Single-Precision mode with seven bit addresses by the six bit address used in double precision mode (n) and that address plus 64 (n+64). The Y\_Word of the double-precision word will be in n; the X Word in n+64. By switching from Double- to Single-Precision, the user can independently access the Y\_Word and the X Word.

# DESIGN CONSIDERATIONS

Power Up

At power up, any or all of the three output ports, Edata-Port, Cdata-Port or Ddata-Port, may be driving off chip. Because of pipelining, Bank Select should not be used to serve a reset or "chip select" function unless no other devices on the buses driven by these ports could themselves possibly be driving. Bank Select will tristate these ports, but they cannot be guaranteed to be in a high impedance state until tDIS into the second cycle after the rising edge at which BS is LO (Fig-

Any ADSP-3128A output port that shares a buses should be forced into a high impedance state at power up using the Etri/-Ctri/Dtri controls. The bits driving these pins from microcode can be gated with the user's general system reset control.

#### Power Supply Decoupling

The ADSP-3128A register file is designed with high speed drivers on all output pins. This means that large peak currents may pass through the driver ground and  $V_{\rm DD}$  pins, particularly when all output post lines are simultaneously charging their load capacitance in transition, whether from LO to HI or vice versa. These peak currents can cause a large disturbance in the ground and supply lines. To help isolate the effects of this disturbance, the ADSP-3128A provides separate pins for driver GND and  $V_{\mathrm{DD}}$  and logic GND and  $V_{\mathrm{DD}}$ s.

The ADSP-3128A's GND and V<sub>DD</sub> pins must be tied directly to solid ground and VDDplanes and properly bypassed. Lead lengths and trace lengths should be as short as possible. The ground plane should tie to driver GND in particular with a very low inductance path. High frequency bypass capacitors (0.1μF ceramic) should be located as close as possible to the V<sub>DD</sub> pins. Low frequency bypass capacitors (20µF tantalum) should be located outside the chip perimeter (not directly under the chip). System noise immunity can be improved by careful design of VDD and GND planes. See the Applications Note, "Power and Ground Connection Guidelines for Pin Grid Arrays" for layout suggestions.

This information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future manufacture unless otherwise agreed to in writing.

#### KEY CHANGES FROM JUNE 1988 ADSP-3128A A PRELIMINARY DATA SHEET

The ADSP-3128A is a pin-compatible speed-upgrade to the ADSP-3128 with the following qualifications:

- The specification t<sub>WINH</sub> has been added and the specification t<sub>WIN</sub> has been redefined to make it easier to use. The Write Inhibit Delay (t<sub>WIN</sub>) is the maximum time after the rising edge of the clock before the A/B/Ewinh pin must be high to inhibit a write to the register file. The new specification Write Inhibit Control Hold Time (t<sub>WINH</sub>) is the minimum hold time required after the falling edge of the clock to insure that the enable write or inhibit write has occurred. New versions of Figure 5 and Figure 8 show this timing.

- 2. The Elt and Eht lines are reversed in Figure 9 and the last two entries of Table I in the June 1988 Data Sheet for Double Precision Clock-on-Rising Slow Inputs to the E-port. Figure 9 and Table I have been corrected. Paragraph two of DP Edata-Port Slow Input and Slow Read on Page 3-54 has also been changed.

- The specifications t<sub>AST</sub> and t<sub>ASR</sub> have been separated for reads and writes. The new specifications are:

Transparent Address Setup - Read Transparent Address Setup - Write Registered Address Setup - Read Registered Address Setup - Write

t<sub>ASTW</sub> t<sub>ASTW</sub>

- The low-level input voltage level on the Clock line is 0.6V maximum. On all other lines it remains 0.8V maximum.

- 5. IDD Supply Current is 600mA maximum.

- The Edata-port can function in any one cycle as either a read port or a write port. It cannot both read and write in one cycle.

- Extra reads from the C, D and Edata-ports are no longer allowed.

- 8. The following specifications have been removed:

t<sub>EDIS</sub> Three-State E Port Auto-Disable

t<sub>HIER</sub> Clock Period HI – Write Plus Extra Read

t<sub>ODRTH</sub> Clock Address-to-Transparent Delay - Extra Reads

t<sub>CLK</sub> Clock Period - Clocked Reads t<sub>CLKS</sub> Clock Period - Trans Reads

t<sub>CLKS</sub> Clock Period - Trans Reads t<sub>CLKA</sub> Clock Period - Transparent I/O

t<sub>ASTBS</sub> Trans. Clk HI Bank Select Setup t<sub>ODCE</sub> Clk-to-Data Output Delay – Eport

This information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future manufacture unless otherwise agreed to in writing.

3-56 MICROCODED SUPPORT COMPONENTS

# RECOMMENDED OPERATING CONDITIONS

|                                                                                 | ADSP-3128A                |                                        |         |  |  |  |  |

|---------------------------------------------------------------------------------|---------------------------|----------------------------------------|---------|--|--|--|--|

| Parameter                                                                       | J and K Grades<br>Min Max | S and T Grades <sup>2</sup><br>Min Max | Unit    |  |  |  |  |

| V <sub>DD</sub> Supply Voltage T <sub>AMB</sub> Operating Temperature (Ambient) | 4.75 5.25<br>0 +70        | 4.5 5.5<br>-55 +125                    | .c<br>∧ |  |  |  |  |

| ELEU                                                  | CTRICAL CHARACTERIST                                                                                | ADSP-3                                                                                                  |                           |                                        |                          |

|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|---------------------------|----------------------------------------|--------------------------|

| Parame                                                | eter                                                                                                | Test Conditions                                                                                         | J and K Grades<br>Min Max | S and T Grades <sup>2</sup><br>Min Max | Unit                     |

| V <sub>IH</sub><br>V <sub>IHA</sub>                   | High-Level Input Voltage<br>High-Level Input Voltage, CLK<br>and All Asynchronous Control<br>Inputs | @ V <sub>DD</sub> = max<br>@ V <sub>DD</sub> = max                                                      | 2.0 2.2                   |                                        | v<br>v                   |

| $V_{IL} \ V_{IL}$                                     | Low-Level Input Voltage<br>Low-Level Input Voltage (CLK)                                            | @ V <sub>DD</sub> = min<br>@ V <sub>DD</sub> = min                                                      | 0.8<br>0.6                |                                        | V<br>V<br>V              |

| V <sub>OH</sub><br>V <sub>OL</sub><br>I <sub>IH</sub> | High-Level Output Voltage Low-Level Output Voltage High-Level Input Current,                        | @ V <sub>DD</sub> = min & I <sub>OL</sub> = -1.0mA<br>@ V <sub>DD</sub> = min & I <sub>OL</sub> = 4.0mA | 0.4                       |                                        | v                        |

| I <sub>IL</sub>                                       | All Inputs Low-Level Input Current,                                                                 | @ V <sub>DD</sub> = max & V <sub>IN</sub> ≥ 5.0V                                                        | 10                        |                                        | μА                       |

| I <sub>oz</sub>                                       | All Inputs Three-State Leakage Current                                                              |                                                                                                         | 10<br>50                  |                                        | μ <b>Α</b><br>μ <b>Α</b> |

| $\mathbf{I_{DD}}$                                     | Supply Current <sup>3</sup>                                                                         | @ max Clock Rate: TTL Inputs<br>(CLK=0, 3V)                                                             | 600                       |                                        | mA                       |

| $I_{\mathbf{D}\mathbf{D}\mathbf{Q}}$                  | Supply Current-Quiescent                                                                            | All V <sub>IN</sub> = 2.4V                                                                              | 100                       |                                        | mA                       |

# ORDERING INFORMATION

|                   | Temperature   |                    |

|-------------------|---------------|--------------------|

| Part Number       | Range         | Package            |

| ADSP-3128AJG      | 0 to +70°C    | 144-Pin Grid Array |

| ADSP-3128AKG      | 0 to +70°C    | 144-Pin Grid Array |

| ADSP-3128ASG      | -55 to +125℃  | 144-Pin Grid Array |

| ADSP-3128ATG      | -55 to +125°C | 144-Pin Grid Array |

| ADSP-3128ASG/883B | -55 to +125°C | 144-Pin Grid Array |

| ADSP-3128ATG/883B | -55 to +125°C | 144-Pin Grid Array |

This information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future manufacture unless otherwise agreed to in writing.

# SWITCHING CHARACTERISTICS

#### ADSP-3128A

| Parame             | eter                                        | J Gra<br>0 to +<br>Min |        | 0 to  | rades<br>+70°C<br>Max | S Grades <sup>2</sup><br>-55 to +125°C<br>Min Max |          | rades <sup>2</sup><br>o –125°C<br>Max | Unit     |

|--------------------|---------------------------------------------|------------------------|--------|-------|-----------------------|---------------------------------------------------|----------|---------------------------------------|----------|

| t <sub>r.</sub>    | Clock LO Period                             |                        |        | 20    |                       |                                                   |          |                                       | ns       |

| t <sub>H</sub>     | Clock HI Period                             | j                      |        | 22    |                       |                                                   |          |                                       | ns       |

| t <sub>CS</sub>    | Control Setup                               | l                      |        | 10    |                       |                                                   | İ        |                                       | ns       |

| t <sub>CH</sub>    | Control Hold                                | i                      |        | 1     |                       |                                                   | ļ        |                                       | ns       |

| t <sub>ASTR</sub>  | Transparent Address Setup - Read            |                        |        | 18    |                       |                                                   |          |                                       | ns       |

| tASTW              | Transparent Address Setup - Write           |                        |        | 30    |                       |                                                   |          |                                       | ns       |

| tASTW              | Registered Address Setup - Read             |                        |        | 4     |                       |                                                   |          |                                       | ns       |

| t <sub>ASRW</sub>  | Registered Address Setup - Write            | l                      |        | 11    |                       |                                                   |          |                                       | ns       |

| t <sub>ASRW</sub>  | Address Hold                                |                        |        | 3     |                       | 1                                                 |          |                                       | ns       |

| t <sub>ENA</sub>   | Three-State Enable Delay                    |                        |        | 2     | 21                    |                                                   |          |                                       | ns       |

| t <sub>DIS</sub>   | Three-State Disable Delay                   | l                      |        |       | 11                    |                                                   |          |                                       | ns       |

| t <sub>DISBS</sub> | Three-State Disable Delay - Bank & Port Sel |                        |        |       | 24                    |                                                   |          |                                       | ns       |

| todata             | Trans Adr-to-Trans Output Delay             |                        |        | 1     | 39                    |                                                   |          |                                       | ns       |

| topc               | Cik-to-Data Output Delay - C & Dports       | 1                      |        |       | 18                    | . #                                               | 1        |                                       | ns       |

| tode               | Clkd Adr-to-Trans Output Delay              | 1                      |        | ł     | 40                    |                                                   |          |                                       | ns       |

| todki              | Output Data Hold                            |                        |        | 3     | . 10                  |                                                   |          |                                       | ns       |

| t <sub>DSR</sub>   | Latched Data Setup                          | İ                      |        | L 100 | 7                     |                                                   |          |                                       | ns       |

| t <sub>DST</sub>   | Transparent Data Setup                      |                        | ara di |       | 18                    |                                                   |          |                                       | ns       |

| t <sub>DSN</sub>   | Clock-on-Falling Data Setup                 |                        |        | 8.2   | 12                    |                                                   |          |                                       | ns       |

| t <sub>DH</sub>    | Input Data Hold                             |                        |        | lia   |                       |                                                   | 1        |                                       | ns       |

| twen               | Write Enable Setup                          | <b>4</b>               | 1      | 23    |                       |                                                   | 1        |                                       | ns       |

| twin               | Write Inhibit Delay                         | 100                    |        |       | 0                     |                                                   | l        |                                       | ns       |

| tATBE              | Trans Adr to Write Enable                   | 1                      |        | 1     | . 100.                |                                                   | 1        |                                       | ns       |

| twinh              | Write Inhibit Control Hold Time             |                        |        | 0     |                       | 4                                                 | <u> </u> |                                       | <u> </u> |

Specifications subject to change without notice.

# ABSOLUTE MAXIMUM RATINGS\*

| Supply Voltage                                      |

|-----------------------------------------------------|

| Input Voltage                                       |

| Output Voltage Swing0.3V to V <sub>DD</sub> +0.3V   |

| Operating Temperature Range (Ambient)55°C to +125°C |

| Storage Temperature Range65°C to +150°C             |

| Lead Temperature (10sec) PGA+300°C                  |

<sup>\*</sup>Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

This information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future manufacture unless otherwise agreed to in writing.

#### 3-58 MICROCODED SUPPORT COMPONENTS

All min and max specifications are over power-supply and temperature range indicated. Input levels are GND and 3.0V. Rise times are 5ns. Input timing reference levels and output reference levels are 1.5V, except for t<sub>ENA</sub>, t<sub>DIS</sub> and t<sub>DISBS</sub> which are as indicated in Figures 3, 12 and 13.

2S and T grade parts are available processed in accordance with MIL-STD-883, Class B. The processing and test methods used for S/883B and T/883B

versions of the ADSP-3128A can be found in Analog Devices' Military Data Book. Regular S and T grade parts are tested at +125°C.

<sup>&</sup>lt;sup>3</sup>Worst-case with all outputs switching twice per cycle. (Example: DP Reads)

# ESD SENSITIVITY

The ADSP-3128A features proprietary input protection circuitry. Per Method 3015 of MIL-STD-883C, the ADSP-3128A has been classified as a Class 1 device.

Proper ESD precautions are strongly recommended to avoid functional damage or performance degradation. Charges as high as 4000 volts readily accumulate on the human body and test equipment and discharge without detection. Unused devices must be stored in conductive foam or shunts, and the foam should be discharged to the destination socket before devices are removed. For further information on ESD precautions, refer to Analog Devices' ESD Prevention Manual.

This information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future manufacture unless otherwise agreed to in writing.

Figure 4. ADSP-3128A Single-Precision Read Output Timing

3-60 MICROCODED SUPPORT COMPONENTS

# **ADSP-3128A**

Figure 5. ADSP-3128A Single-Precision Write Input Timing

This information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future manufacture unless otherwise agreed to in writing.

Figure 6. ADSP-3128A Single-Precision Write to Input Latches and Hold Timing

# 3-62 MICROCODED SUPPORT COMPONENTS

Figure 7. ADSP-3128A Double-Precision Read Output Timing

Figure 8. ADSP-3128A Double-Precision Write Input Timing

### 3-64 MICROCODED SUPPORT COMPONENTS

<sup>\*</sup> See Figure 9 for the complete set of conditions for Ewinh

Figure 9. ADSP-3128A Double-Precision Slow Edata-Port Input Timing

Figure 10. ADSP-3128A Double-Precision Slow Edata-Port Read Output Timing

## 3-66 MICROCODED SUPPORT COMPONENTS

Figure 11. ADSP-3128A Double-Precision Write to Input Latches and Hold Timing (Adata-Port and Bdata-Port only)

Figure 12. ADSP-3128A Bank Select Timing

### 3-68 MICROCODED SUPPORT COMPONENTS

Figure 13. ADSP-3128A Double-Precision Port Select Timing

Figure 14. ADSP-3128A Single-Precision Application with ADSP-32XX

Muxing the read addresses allows two reads (at 1×clock) for loading the input ports of both the ASDP-321X and ADSP-322X with two 32-bit words per 32XX cycle (at 1×clock) while

still using 1×acode rates. In this application, write data is latched on clock HI and read data is registered on the rising edge. Write addresses are latched; read addresses are transparent.

Figure 15. ADSP-3128A Seven-Port Double-Precision Application with ADSP-32XX

Double-Precision mode allows transfer of both MSW and LSW in a single cycle while still using  $\mu$ code at the same cycle rate. Pairing pairs of ADSP-3128As creates a seven-port register file for unconstrained data transfers. The same data is always written to both the right and left pairs (therefore, the same A, B and Eadrs go to both pairs). In this application, Early Writes

are used at the input ports for the simplest interface to the floating-point chipset's output. The data read from the two sides is generally distinct, so the C and Dadrs for each pair are distinct. Late Reads match the input loading requirements of these chips and are, therefore, used on the rightmost pair of ADSP-3128As.

This information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future manufacture unless otherwise agreed to in writing.

## 3-70 MICROCODED SUPPORT COMPONENTS

|   |               | ADSP-3128A      |               |               |                |         |               |               |        |        |                |                   |                 |                 |       |       |   |  |       |       |   |  |  |

|---|---------------|-----------------|---------------|---------------|----------------|---------|---------------|---------------|--------|--------|----------------|-------------------|-----------------|-----------------|-------|-------|---|--|-------|-------|---|--|--|

|   | 1             | 2               | 3             | 4             | 5              | 6       | 7             | 8             | 9      | 10     | 11             | 12                | 13              | 14              | 15    |       |   |  |       |       |   |  |  |

| Q | Bdata8        | Bdata5          | Bdata2        | Bdata0        | Adata13        | Adata10 | Adata9        | Adata7        | Adata4 | Adata3 | Eht            | ABht              | ABit            | Awinh           | Aadr0 | a     |   |  |       |       |   |  |  |

| P | Bdata12       | Bdata9          | Bdata6        | Bdata4        | Bdata1         | Adata14 | Adata12       | Adata8        | Adata2 | Adata1 | Elt            | DP                | Bwinh           | internal<br>GND | Aadr3 | P     |   |  |       |       |   |  |  |

| N | Edata15       | Bdata13         | Bdata10       | Bdata7        | Bdata3         | Adata15 | Adata11       | Adata6        | Adata5 | Adata0 | Ewinh          | internal<br>GND   | internal<br>GND | Aadr2           | Aadr6 | N     |   |  |       |       |   |  |  |

| м | Edata14       | Bdata15         | Bdata11       |               |                |         |               |               |        |        |                |                   |                 | Aadr4           | Badr1 | м     |   |  |       |       |   |  |  |

| L | Edata12       | Edata13         | Bdata14       |               |                |         |               |               |        |        |                |                   |                 | Badr0           | Badr4 | L     |   |  |       |       |   |  |  |

| κ | Edata8        | Edata10         | Edata11       |               |                |         |               |               | **     |        |                |                   | Badr2           | Badr3           | Cadr0 | K     |   |  |       |       |   |  |  |

| J | Edata7        | Edata9          | Edata6        | Badr6         |                |         |               |               |        |        | BOTTOM-VIEW Ca |                   |                 |                 |       |       |   |  |       |       |   |  |  |