- Members of the Texas Instruments

Widebus+™ Family

- State-of-the-Art EPIC-IIB™ BiCMOS Design Significantly Reduces Power Dissipation

- UBE™ (Universal Bus Exchanger)

Combines D-Type Latches and D-Type

Flip-Flops for Operation in Transparent,

Latched, or Clocked Mode

- Latch-Up Performance Exceeds 500 mA Per JEDEC Standard JESD-17

- Typical V<sub>OLP</sub> (Output Ground Bounce)

< 0.8 V at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25°C

- High-Impedance State During Power Up and Power Down

- Distributed V<sub>CC</sub> and GND Pin Configuration Minimizes High-Speed Switching Noise

- High-Drive Outputs (–32-mA I<sub>OH</sub>, 64-mA I<sub>OL</sub>)

- Bus Hold on Data Inputs Eliminates the Need for External Pullup/Pulldown Resistors

- Package Options Include 80-Pin Plastic

Thin Quad Flat (PN) Package With

12 × 12-mm Body Using 0.5-mm Lead Pitch

and 84-Pin Ceramic Quad Flat (HT) Package

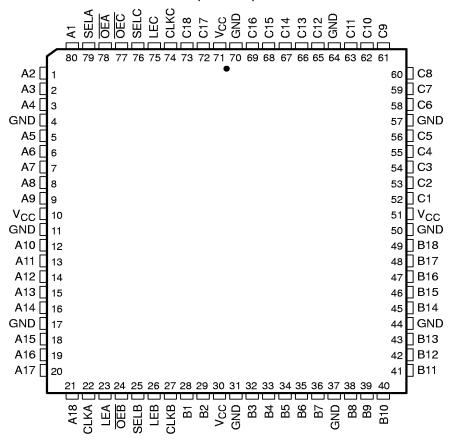

## SN74ABTH32318 . . . PN PACKAGE (TOP VIEW)

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Widebus+, EPIC-IIB, and UBE are trademarks of Texas Instruments Incorporated.

NC - No internal connection

#### description

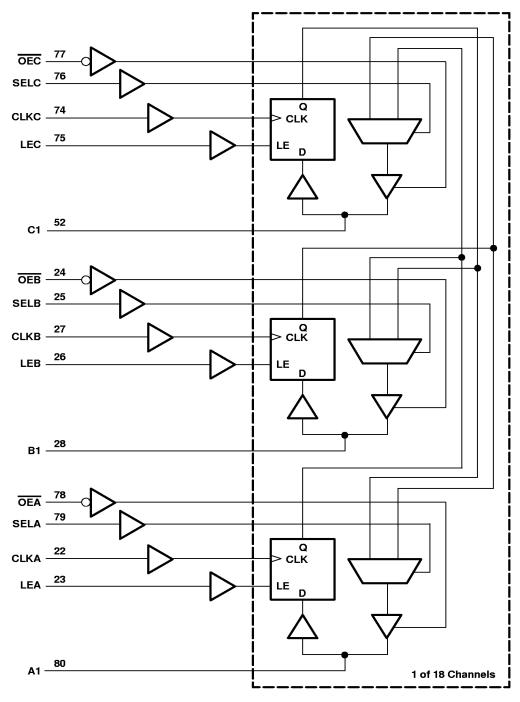

The 'ABTH32318 consist of three 18-bit registered input/output (I/O) ports. These registers combine D-type latches and flip-flops to allow data flow in transparent, latch, and clock modes. Data from one input port can be exchanged to one or more of the other ports. Because of the universal storage element, multiple combinations of real-time and stored data can be exchanged among the three ports.

Data flow in each direction is controlled by the output-enable ( $\overline{OEA}$ ,  $\overline{OEB}$ , and  $\overline{OEC}$ ), select-control (SELA, SELB, and SELC), latch-enable (LEA, LEB, and LEC), and clock (CLKA, CLKB, and CLKC) inputs. The A data register operates in the transparent mode when LEA is high. When LEA is low, data is latched if CLKA is held at a high or low logic level. If LEA is low, data is stored on the low-to-high transition of CLKA. Output data selection is accomplished by the select-control pins. All three ports have active-low output enables, so when the output-enable input is low, the outputs are active; when the output-enable input is high, the outputs are in the high-impedance state.

When  $V_{CC}$  is between 0 and 2.1 V, the device is in the high-impedance state during power up or power down. However, to ensure the high-impedance state above 2.1 V,  $\overline{OE}$  should be tied to  $V_{CC}$  through a pullup resistor; the minimum value of the resistor is determined by the current-sinking capability of the driver.

Active bus-hold circuitry is provided to hold unused or floating data inputs at a valid logic level.

## description (continued)

The SN54ABTH32318 is characterized for operation over the full military temperature range of  $-55^{\circ}$ C to 125°C. The SN74ABTH32318 is characterized for operation from  $-40^{\circ}$ C to 85°C.

### **Function Tables**

#### **STORAGET**

| I        | NPUTS | ОИТРИТ |                                      |  |  |

|----------|-------|--------|--------------------------------------|--|--|

| CLKA     | LEA   | Α      | OUIPUI                               |  |  |

| 1        | L     | L      | L                                    |  |  |

| <b>↑</b> | L     | Н      | Н                                    |  |  |

| Н        | L     | Χ      | Q <sub>0</sub> ‡<br>Q <sub>0</sub> ‡ |  |  |

| L        | L     | Χ      | Q <sub>0</sub> ‡                     |  |  |

| Х        | Н     | L      | L                                    |  |  |

| Х        | Н     | Н      | Н                                    |  |  |

<sup>†</sup>A-port register shown. B and C ports are similar but use CLKB, CLKC, LEB, and LEC.

#### **A-PORT OUTPUT**

| INP | UTS  | OUTPUT A             |  |  |  |

|-----|------|----------------------|--|--|--|

| OEA | SELA |                      |  |  |  |

| Н   | Х    | Z                    |  |  |  |

| L   | Н    | Output of C register |  |  |  |

| L   | L    | Output of B register |  |  |  |

### **B-PORT OUTPUT**

|   | INP | UTS  | OUTPUT D             |  |  |  |

|---|-----|------|----------------------|--|--|--|

|   | OEB | SELB | ОИТРИТ В             |  |  |  |

| ĺ | Н   | Х    | Z                    |  |  |  |

| I | L   | Н    | Output of A register |  |  |  |

| ı | L   | L    | Output of C register |  |  |  |

#### **C-PORT OUTPUT**

| INP | UTS  | OUTDUT O             |  |  |  |  |

|-----|------|----------------------|--|--|--|--|

| OEC | SELC | OUTPUT C             |  |  |  |  |

| Н   | Х    | Z                    |  |  |  |  |

| L   | Н    | Output of B register |  |  |  |  |

| L   | L    | Output of A register |  |  |  |  |

<sup>‡</sup>Output level before the indicated steady-state input conditions were established

<u>SCBS180E</u> – JUNE 1992 – REVISED MAY 1997

## logic diagram (positive logic)

Pin numbers shown are for the PN package.

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| Supply voltage range, V <sub>CC</sub>                                              | –0.5 V to 7 V   |

|------------------------------------------------------------------------------------|-----------------|

| Input voltage range, V <sub>I</sub> (except I/O ports) (see Note 1)                | –0.5 V to 7 V   |

| Voltage range applied to any output in the high or power-off state, V <sub>O</sub> | –0.5 V to 5.5 V |

| Current into any output in the low state, I <sub>O</sub> : SN54ABTH32318           |                 |

| SN74ABTH32318                                                                      | 128 mA          |

| Input clamp current, I <sub>IK</sub> (V <sub>I</sub> < 0)                          | –18 mA          |

| Output clamp current, I <sub>OK</sub> (V <sub>O</sub> < 0)                         | –50 mA          |

| Package thermal impedance, θ <sub>JA</sub> (see Note 2): PN package                | 62°C/W          |

| Storage temperature range, T <sub>stq</sub>                                        | –65°C to 150°C  |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### recommended operating conditions (see Note 3)

|                     |                                    |                 | SN54ABTH32318 |     | SN74ABTH32318   |     | UNIT |

|---------------------|------------------------------------|-----------------|---------------|-----|-----------------|-----|------|

|                     |                                    |                 | MIN           | MAX | MIN             | MAX | UNIT |

| Vcc                 | Supply voltage                     |                 | 4.5           | 5.5 | 4.5             | 5.5 | ٧    |

| V <sub>IH</sub>     | High-level input voltage           |                 | 2             | - B | 2               |     | ٧    |

| V <sub>IL</sub>     | Low-level input voltage            |                 |               | 0.8 |                 | 0.8 | ٧    |

| VI                  | Input voltage                      |                 | 0             | VCC | 0               | vcc | ٧    |

| IOH                 | High-level output current          |                 |               | -24 |                 | -32 | mA   |

| loL                 | Low-level output current           |                 |               | 48  |                 | 64  | mA   |

| Δt/Δν               | Input transition rise or fall rate | Outputs enabled |               | 10  |                 | 10  | ns/V |

| Δt/ΔV <sub>CC</sub> | Power-up ramp rate                 |                 | 200           |     | 200             |     | μs/V |

| TA                  | Operating free-air temperature     |                 | -55           | 125 | <del>-4</del> 0 | 85  | ô    |

NOTE 3: Unused control inputs must be held high or low to prevent them from floating.

NOTES: 1. The input and output negative-voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

<sup>2.</sup> The package thermal impedance is calculated in accordance with EIA/JEDEC Std JESD51.

## SN54ABTH32318, SN74ABTH32318 18-BIT TRI-PORT UNIVERSAL BUS EXCHANGERS

SCBS180E - JUNE 1992 - REVISED MAY 1997

## electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER          |                                                 | TEST CONDITIONS                                                                  |                                  | SN54 | ABTH3 | 2318 | SN74            | IABTH32 | 2318 | LINUT |  |

|--------------------|-------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------|------|-------|------|-----------------|---------|------|-------|--|

| PA                 | RAMETER                                         | TEST CONDITIONS                                                                  |                                  | MIN  | TYP   | MAX  | MIN             | TYP     | MAX  | UNIT  |  |

| V <sub>IK</sub>    |                                                 | V <sub>CC</sub> = 4.5 V,                                                         | I <sub>I</sub> = -18 mA          |      |       | -1.2 |                 |         | -1.2 | ٧     |  |

|                    |                                                 | V <sub>CC</sub> = 4.5 V,                                                         | I <sub>OH</sub> = –3 mA          | 2.5  |       |      | 2.5             |         |      |       |  |

| Vou                |                                                 | V <sub>CC</sub> = 5 V,                                                           | I <sub>OH</sub> = –3 mA          | 3    |       |      | 3               |         |      | v I   |  |

| Vон                |                                                 | V <sub>CC</sub> = 4.5 V                                                          | I <sub>OH</sub> = -24 mA         | 2    |       |      |                 |         |      | V     |  |

|                    |                                                 | VCC = 4.5 V                                                                      | $I_{OH} = -32 \text{ mA}$        |      |       |      | 2               |         |      |       |  |

| VOL                |                                                 | V <sub>CC</sub> = 4.5 V                                                          | $I_{OL} = 48 \text{ mA}$         |      |       | 0.55 |                 |         | 0.55 | V     |  |

| VOL                |                                                 | VCC = 4.5 V                                                                      | I <sub>OL</sub> = 64 mA          |      |       | 0.55 |                 |         | 0.55 | V     |  |

| $V_{hys}$          |                                                 |                                                                                  |                                  |      | 100   |      |                 | 100     |      | mV    |  |

| 1.                 | Control inputs                                  | $V_{CC} = 0 \text{ to } 5.5 \text{ V},$                                          | $V_I = V_{CC}$ or GND            |      | , d   | ±1   |                 |         | ±1   | μА    |  |

| l II               | A, B, or C ports                                | $V_{CC} = 2.1 \text{ V to } 5.5 \text{ V},$                                      | $V_I = V_{CC}$ or GND            |      |       | ±20  |                 |         | ±20  | μΑ    |  |

| ha is              | A, B, or C ports                                | V <sub>CC</sub> = 4.5 V                                                          | V <sub>I</sub> = 0.8 V           | 100  | 70.   |      | 100             |         |      | μΑ    |  |

| l(hold)            |                                                 |                                                                                  | V <sub>I</sub> = 2 V             | -100 | \$    |      | -100            |         |      |       |  |

| lozpu <sup>‡</sup> |                                                 | $V_{CC} = 0$ to 2.1 V, $V_{O} = 0.5$                                             | V to 2.7 V, <del>OE</del> = X    | ĺ    | 9     | ±50  |                 |         | ±50  | μΑ    |  |

| lozpd <sup>‡</sup> |                                                 | $V_{CC} = 2.1 \text{ V to } 0, V_{O} = 0.5$                                      | V to 2.7 V, <del>OE</del> = X    |      |       | ±50  |                 |         | ±50  | μΑ    |  |

| l <sub>off</sub>   |                                                 | $V_{CC} = 0$ ,                                                                   | $V_I$ or $V_O \le 4.5 \text{ V}$ |      |       | ±100 |                 |         | ±100 | μΑ    |  |

| ICEX               |                                                 | $V_{CC} = 5.5 \text{ V}, V_{O} = 5.5 \text{ V}$                                  | Outputs high                     |      |       | 50   |                 |         | 50   | μΑ    |  |

| IO§                |                                                 | $V_{CC} = 5.5 \text{ V},$                                                        | $V_0 = 2.5 \text{ V}$            | -50  | -100  | -180 | <del>-</del> 50 | -100    | -180 | mA    |  |

|                    | V <sub>CC</sub> = 5.5 V,<br>I <sub>O</sub> = 0, | Outputs high                                                                     |                                  |      | 2     |      |                 | 2       |      |       |  |

| Icc                |                                                 | Outputs low                                                                      |                                  |      | 45    |      |                 | 45      | mA   |       |  |

|                    |                                                 | V <sub>I</sub> = V <sub>CC</sub> or GND                                          | Outputs disabled                 |      |       | 1    |                 |         | 1    |       |  |

| ΔICC¶              |                                                 | V <sub>CC</sub> = 5.5 V, One input at 3<br>Other inputs at V <sub>CC</sub> or GN |                                  |      |       | 0.5  |                 |         | 0.5  | mA    |  |

| Ci                 | Control inputs                                  | V <sub>I</sub> = 2.5 V or 0.5 V                                                  |                                  |      | 3     |      |                 | 3       |      | рF    |  |

| C <sub>io</sub>    | A, B, or C ports                                | V <sub>O</sub> = 2.5 V or 0.5 V                                                  |                                  |      | 11.5  |      |                 | 11.5    |      | pF    |  |

<sup>†</sup> All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25°C.

## timing requirements over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted) (see Figure 1)

|                               |                 |                        | SN54ABTH32318 |     | SN74ABTH32318 |     | UNIT |

|-------------------------------|-----------------|------------------------|---------------|-----|---------------|-----|------|

|                               |                 |                        | MIN           | MAX | MIN           | MAX | ONIT |

| fclock                        | Clock frequency |                        |               | 150 |               | 150 | MHz  |

| t <sub>W</sub> Pulse duration | Dulas duration  | LE high                | 3.3           |     | 3.3           |     |      |

|                               | CLK high or low |                        | 3.3           | 4   | 3.3           |     | ns   |

|                               | Catura tima     | A, B, or C before CLK↑ | 2.4           | 4   | 2.4           |     |      |

| t <sub>su</sub>               | Setup time      | A, B, or C before LE↓  | 2.1           |     | 2.1           |     | ns   |

| t <sub>h</sub> Hold time      |                 | A, B, or C after CLK↑  | 1.4           |     | 1.4           |     |      |

|                               | Hold time       | A, B, or C after LE↓   | 2.1           |     | 2.1           |     | ns   |

<sup>‡</sup> This parameter is specified by characterization.

<sup>§</sup> Not more than one output should be tested at a time, and the duration of the test should not exceed one second.

<sup>¶</sup> This is the increase in supply current for each input that is at the specified TTL voltage level rather than V<sub>CC</sub> or GND.

## SN54ABTH32318, SN74ABTH32318 18-BIT TRI-PORT UNIVERSAL BUS EXCHANGERS

SCBS180E - JUNE 1992 - REVISED MAY 1997

# switching characteristics over recommended ranges of supply voltage and operating free-air temperature, $C_L = 50 \, pF$ (unless otherwise noted) (see Figure 1)

| PARAMETER        | FROM          | то         | SN54ABTH | 32318 | SN74ABTI | H32318 | UNIT  |

|------------------|---------------|------------|----------|-------|----------|--------|-------|

| FARAMETER        | (INPUT)       | (OUTPUT)   | MIN      | MAX   | MIN      | MAX    | 31411 |

| f <sub>max</sub> |               |            | 150      |       | 150      |        | MHz   |

| tPLH             | A, B, or C    | C, B, or A | 1.4      | 6.5   | 1.4      | 6.1    | ne    |

| <sup>t</sup> PHL | A, B, 01 C    | O, B, Ol A | 1.1      | 6.8   | 1.1      | 6.6    | ns    |

| t <sub>PLH</sub> | SEL           | A, B, or C | 1.4      | 6.7   | 1.4      | 6.5    | ns    |

| t <sub>PHL</sub> | SLL           |            | 1.8      | 6.8   | 1.8      | 6.5    |       |

| tPLH             | LE            | A, B, or C | 2.6      | 8     | 2.6      | 7.5    | ns    |

| tPHL             |               |            | 2.6      | 7.4   | 2.6      | 6.9    | 115   |

| tPLH             | CLK           | A D == 0   | 2.5      | 8     | 2.5      | 7.4    | ns    |

| t <sub>PHL</sub> | OLK           | A, B, or C | 2.5      | 7.2   | 2.5      | 6.7    | 115   |

| <sup>t</sup> PZH | <del>OE</del> | A, B, or C | 1.4      | 6.9   | 1.4      | 6.8    | 20    |

| t <sub>PZL</sub> | OE            | A, B, G C  | 2.4      | 7.2   | 2.4      | 7.1    | ns    |

| <sup>t</sup> PHZ | <del>OE</del> | A D == C   | 1        | 6.4   | 1        | 6.2    | nc    |

| tPLZ             | 7             | A, B, or C | 2        | 6.4   | 2        | 6      | ns    |

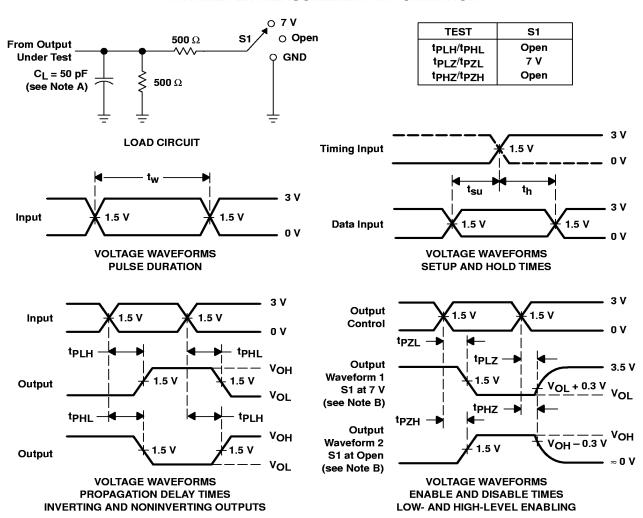

#### PARAMETER MEASUREMENT INFORMATION

NOTES: A. C<sub>L</sub> includes probe and jig capacitance.

- B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- C. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz,  $Z_Q = 50 \, \Omega$ ,  $t_f \leq 2.5 \, \text{ns}$ ,  $t_f \leq 2.5 \, \text{ns}$ .

- D. The outputs are measured one at a time with one transition per measurement.

Figure 1. Load Circuit and Voltage Waveforms